Предлагаемое изобретение относится к области вычислительной техники, автоматики и может использоваться в различных цифровых структурах и системах автоматического управления, передачи информации и связи.

В различных аналого-цифровых вычислительных и управляющих устройствах широко используются транзисторные каскады преобразования входных переменных (токов), реализованные на основе токовых зеркал [1-14]. Данные функциональные узлы, например, используются во входных каскадах операционных преобразователей сигналов с так называемой «токовой отрицательной обратной связью» [1-14], а также в качестве самостоятельных нелинейных коммутаторов входных токов без цепей обратной связи [9], реализующих функцию инвертирования входных переменных.

В работе [15], а также монографиях соавтора настоящей заявки [16-17] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока. Заявляемое устройство относится к этому типу логических элементов.

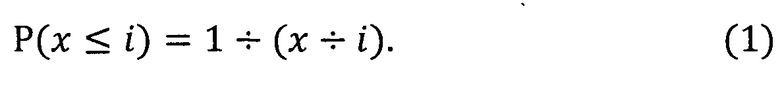

Ближайшим прототипом заявляемого устройства является логический элемент, представленный в патенте US 5.742.154, fig.1, структура которого присутствует во многих других патентах [1-14]. Он содержит токовый вход 1 устройства и токовый выход 2 устройства, первый 3 и второй 4 выходные транзисторы с объединенными базами, третий 5 и четвертый 6 выходные транзисторы другого типа проводимости с объединенными базами, причем эмиттеры первого 3 и третьего 5 выходных транзисторов объединены, а эмиттеры второго 4 и четвертого 6 выходных транзисторов связаны друг с другом, первый 7 и второй 8 источники опорного тока, первое 9 токовое зеркало, согласованное с первой 10 шиной источника питания, второе 11 токовое зеркало, согласованное со второй 12 шиной источника питания, причем коллектор третьего 5 выходного транзистора соединен со входом второго 11 токового зеркала.

Существенный недостаток известного устройства состоит в том, что он не реализует функцию логического сравнения k-значной переменной, соответствующей k уровням входного тока, с заданным пороговым значением этой переменной. Это не позволяет на его основе создать полный базис средств вычислительной техники, функционирующих на принципах преобразования многозначных токовых сигналов.

Основная задача предлагаемого изобретения состоит в создании логического элемента (ЛЭ) сравнения k-значной входной переменной с заданным пороговым значением этой переменной. При этом внутреннее преобразование информации в таком ЛЭ производится в многозначной токовой форме сигналов. В конечном итоге это позволяет повысить быстродействие средств обработки цифровой информации и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [16-17].

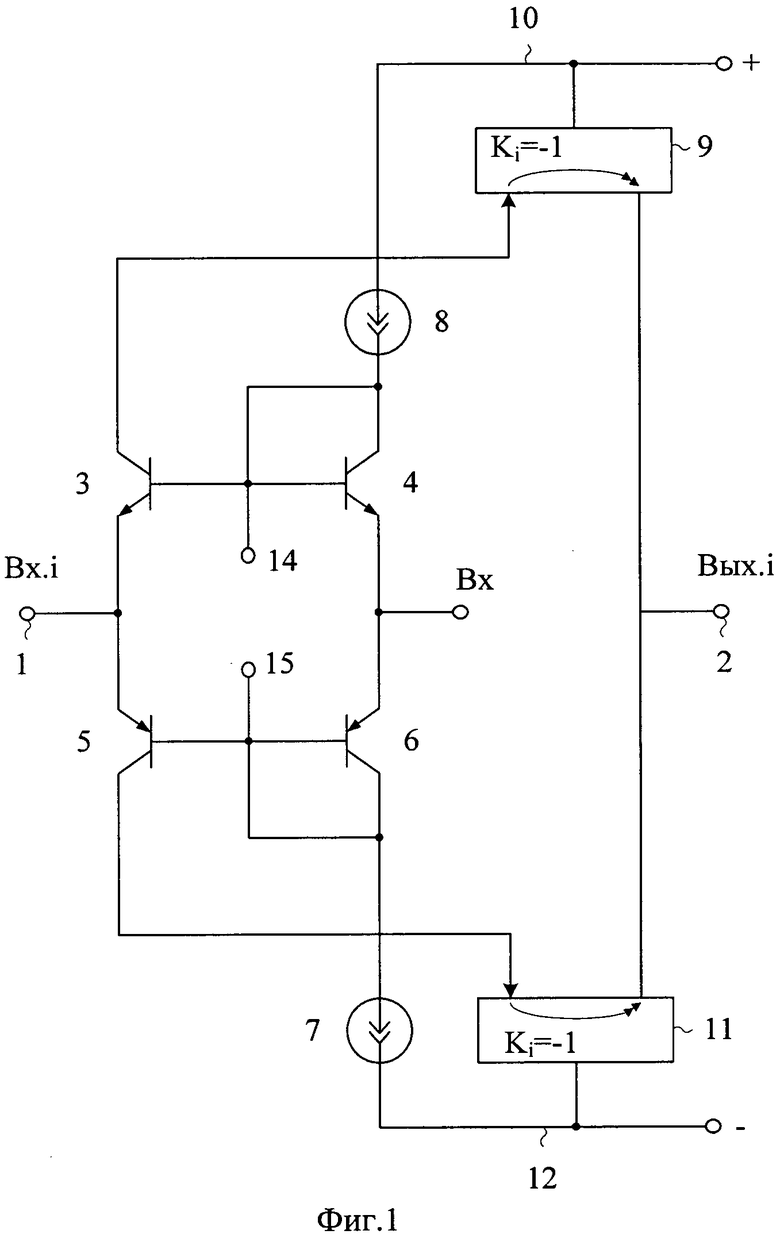

Поставленная задача решается тем, что в логическом элементе сравнения k-значной переменной с заданным пороговым значением (фиг.1), содержащем токовый вход 1 устройства и токовый выход 2 устройства, первый 3 и второй 4 выходные транзисторы с объединенными базами, третий 5 и четвертый 6 выходные транзисторы другого типа проводимости с объединенными базами, причем эмиттеры первого 3 и третьего 5 выходных транзисторов объединены, а эмиттеры второго 4 и четвертого 6 выходных транзисторов связаны друг с другом, первый 7 и второй 8 источники опорного тока, первое 9 токовое зеркало, согласованное с первой 10 шиной источника питания, второе 11 токовое зеркало, согласованное со второй 12 шиной источника питания, причем коллектор третьего 5 выходного транзистора соединен со входом второго 11 токового зеркала, предусмотрены новые элементы и связи - токовый вход 1 устройства соединен со входом первого 9 токового зеркала, выход которого подключен к объединенным эмиттерам первого 3 и третьего 5 выходных транзисторов и через первый 7 источник опорного тока связан со второй 12 шиной источника питания, коллекторы первого 3 и второго 4 выходных транзисторов соединены с первой 10 шиной источника питания, выход второго 11 токового зеркала соединен с объединенными эмиттерами второго 4 и четвертого 6 выходных транзисторов и через второй 8 источник опорного тока соединен с первой 10 шиной источника питания, коллектор четвертого 6 выходного транзистора подключен ко входу дополнительного токового зеркала 13, согласованного со второй 12 шиной источника питания, выход которого подключен к выходу 2 устройства, причем базы первого 3 и второго 4 выходных транзисторов подключены к первому 14 источнику вспомогательного напряжения, а базы третьего 5 и четвертого 6 выходных транзисторов подключены ко второму 15 источнику вспомогательного напряжения.

На фиг.1 показана схема известного устройства.

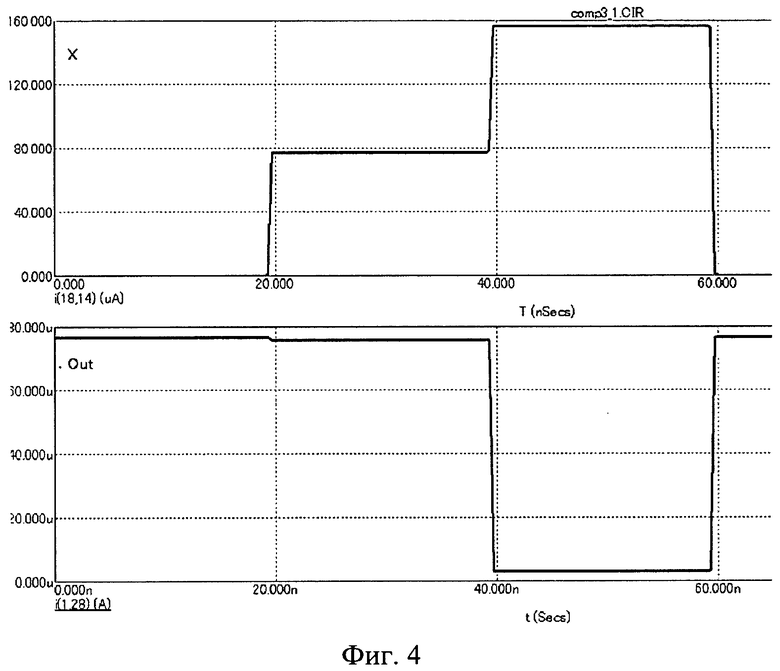

На фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

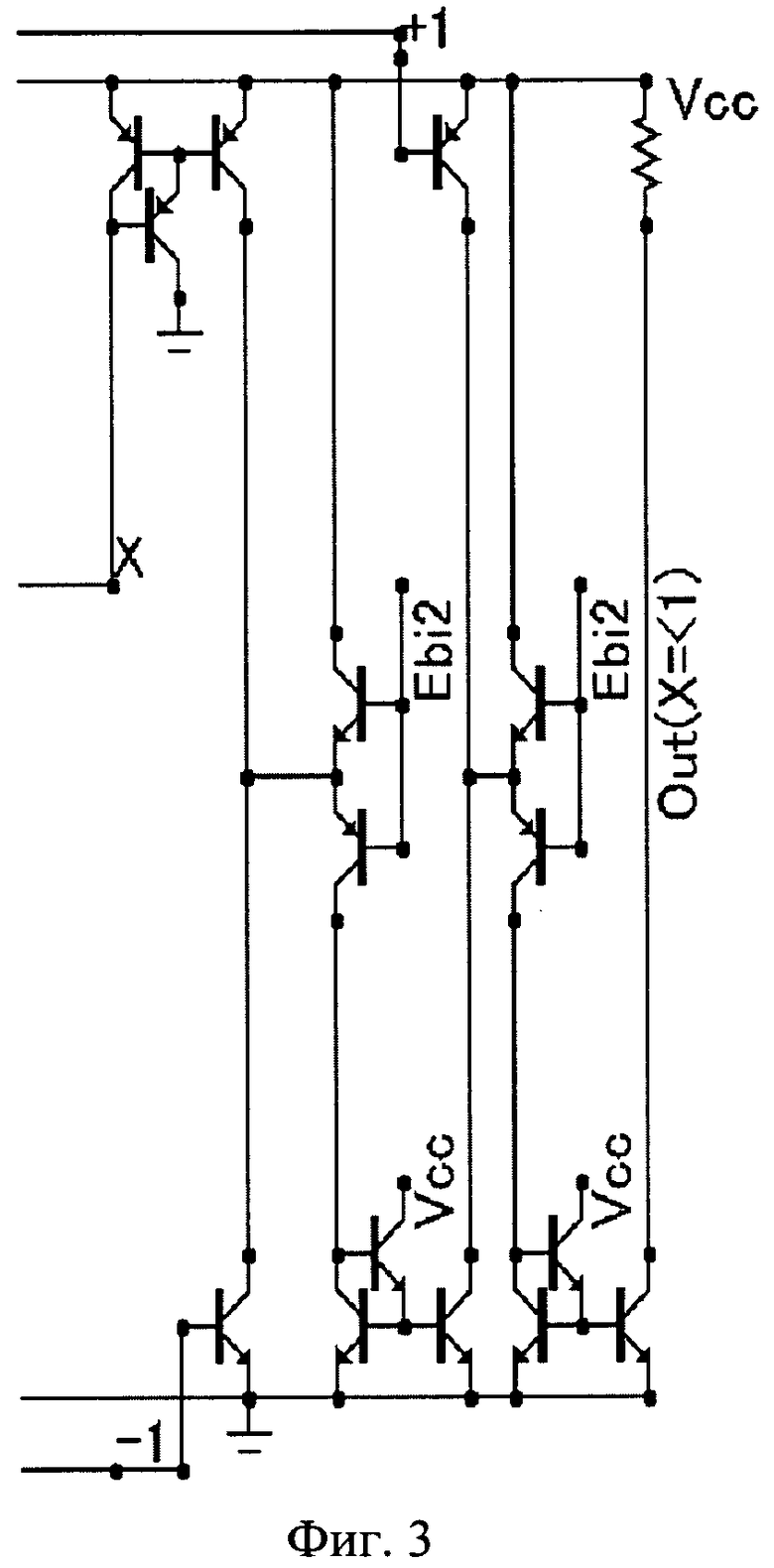

На фиг.3 приведена схема исследованного в среде МС9 заявляемого устройства фиг.2 с конкретным выполнением его функциональных узлов на биполярных транзисторах.

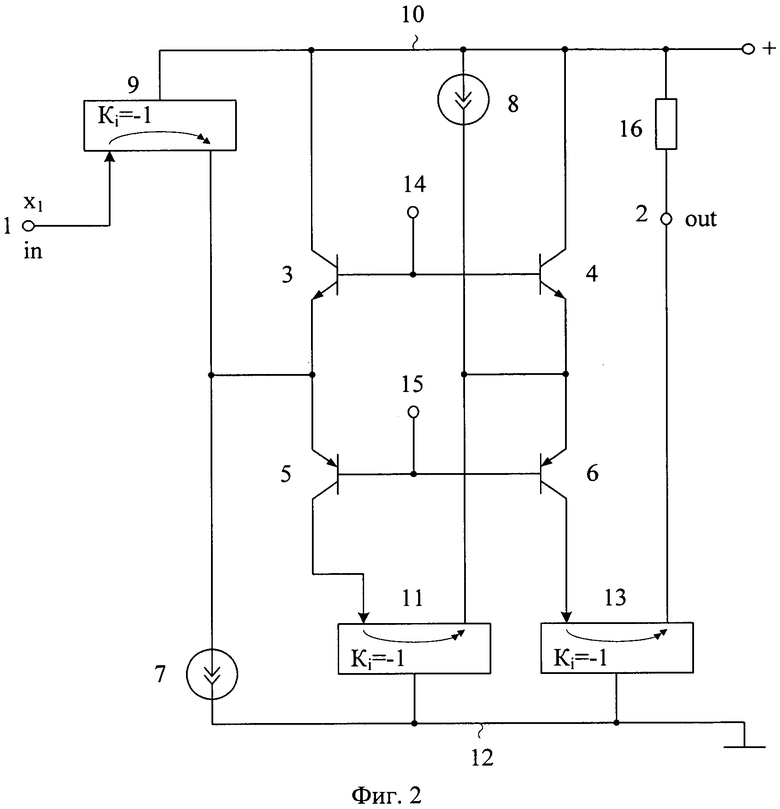

На фиг.4 приведены результаты компьютерного моделирования схемы фиг.3 для случая, когда входной многозначный токовый сигнал (входная переменная X) имеет несколько уровней.

Логический элемент сравнения k-значной переменной с заданным пороговым значением (фиг.2) содержит токовый вход 1 устройства и токовый выход 2 устройства, первый 3 и второй 4 выходные транзисторы с объединенными базами, третий 5 и четвертый 6 выходные транзисторы другого типа проводимости с объединенными базами, причем эмиттеры первого 3 и третьего 5 выходных транзисторов объединены, а эмиттеры второго 4 и четвертого 6 выходных транзисторов связаны друг с другом, первый 7 и второй 8 источники опорного тока, первое 9 токовое зеркало, согласованное с первой 10 шиной источника питания, второе 11 токовое зеркало, согласованное со второй 12 шиной источника питания, причем коллектор третьего 5 выходного транзистора соединен со входом второго 11 токового зеркала. Токовый вход 1 устройства соединен со входом первого 9 токового зеркала, выход которого подключен к объединенным эмиттерам первого 3 и третьего 5 выходных транзисторов и через первый 7 источник опорного тока связан со второй 12 шиной источника питания, коллекторы первого 3 и второго 4 выходных транзисторов соединены с первой 10 шиной источника питания, выход второго 11 токового зеркала соединен с объединенными эмиттерами второго 4 и четвертого 6 выходных транзисторов и через второй 8 источник опорного тока соединен с первой 10 шиной источника питания, коллектор четвертого 6 выходного транзистора подключен ко входу дополнительного токового зеркала 13, согласованного со второй 12 шиной источника питания, выход которого подключен к выходу 2 устройства, причем базы первого 3 и второго 4 выходных транзисторов подключены к первому 14 источнику вспомогательного напряжения, а базы третьего 5 и четвертого 6 выходных транзисторов подключены ко второму 15 источнику вспомогательного напряжения. К выходу устройства 2 подключен двухполюсник 16, моделирующий свойства нагрузки.

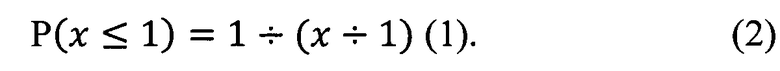

Рассмотрим работу устройства фиг.2, которое определяет факт превышения переменной входной величиной (X) некоторого установленного значения, т.е. производит сравнение текущего дискретного значения многозначной переменной х с некоторой уставкой i. Функция сравнения - двоичная функция, принимающая единичное значение, если выполняется условие

Результат выполнения этой логической операции для k-значных переменных х - двоичный предикат Р. Конкретное значение уставки i определяется предполагаемой областью использования элемента и задается при проектировании.

Например, для k=3 и i=1 последнее выражение имеет вид

Выражение в скобках реализуется следующим образом.

Входной сигнал х (х=0, 1, …, k-1, в трехзначном случае х=0, 1, 2), соответствующий значению сравниваемой переменной в форме вытекающего кванта тока, поступает на вход 1 и далее - на вход первого токового зеркала 9. Величина i порога задается величиной тока первого источника тока 7 (i=1, ..., k-1, в трехзначном случае i=1, 2). Из равного по величине входному кванту вытекающего кванта тока с выхода токового зеркала 9 вычитается ток первого источника тока 7, образуя первый разностный ток. Первый разностный ток поступает на объединенные эмиттеры выходных транзисторов 3 и 5. Режимы работы этих транзисторов задаются значениями напряжений первого 14 и второго 15 дополнительных источников напряжения и обеспечивают предотвращение насыщения транзисторов первого источника тока 7 и токового зеркала 11.

До тех пор, пока значение кванта тока входного сигнала с выхода токового зеркала 9 по величине не превышает значение тока первого источника тока 7, первый разностный ток на объединенных эмиттерах выходных транзисторов 3 и 5 равен нулю. При этом транзистор 3 открыт, а транзистор 5 закрыт. Ток источника тока 7 замыкается на цепь питания устройства через транзистор 3.

Если значение кванта тока входного сигнала с выхода токового зеркала 9 по величине превысит значение тока первого источника тока 7, первый разностный ток на объединенных эмиттерах выходных транзисторов 3 и 5 становится по величине равным разности квантов входного тока и тока источника тока 7. При этом транзистор 3 закрывается, а транзистор 5 открывается, и втекающий первый разностный ток поступает через открытый транзистор 5 на вход второго токового зеркала 11.

Остальная часть схемы реализует вычитание из 1 выражения (1) в круглых скобках. Единица моделируется вторым источником тока 8, из которого вычитается первый разностный ток с выхода второго токового зеркала 11, образуя второй разностный ток.

Режимы работы этих транзисторов задаются значениями напряжений первого 14 и второго 15 дополнительных источников напряжения и обеспечивают предотвращение насыщения транзисторов второго источника тока 8 и дополнительного токового зеркала 13.

Пока значение кванта первого разностного тока с выхода второго токового зеркала 11 превышает значение тока источника тока 8, второй разностный ток на объединенных эмиттерах выходных транзисторов 4 и 6 равен нулю. При этом транзистор 4 открыт, а транзистор 6 закрыт. Выход второго токового зеркала 11 замыкается на цепь питания через транзистор 4.

Если значение кванта тока входного сигнала с выхода токового зеркала 9 по величине меньше значения тока второго источника тока 8 второй разностный, ток на объединенных эмиттерах выходных транзисторов 4 и 6 становится по величине равным разности квантов первого разностного тока и тока источника тока 8. При этом транзистор 4 закрывается, а транзистор 6 открывается, и втекающий второй разностный ток поступает через открытый транзистор 6 на вход дополнительного токового зеркала 13.

Как видно из приведенного описания, реализация логической функции Р(х≤i) здесь производится формированием алгебраической суммы квантов тока и выделением определенных значений этой суммы токов. Все элементы приведенной схемы работают в активном режиме, предполагающем отсутствие насыщения в процессе переключений, что повышает общее быстродействие схемы. Кроме того, использование многозначного внутреннего представления сигналов повышает информативность линий связи, что уменьшает их количество при микроэлектронном исполнении. Использование стабильных значений квантов тока, а также определение выходного сигнала разностью этих токов обеспечивают малую зависимость работы схемы от внешних дестабилизирующих факторов (девиация питающего напряжения, радиационное и температурное воздействия, синфазная помеха и др.).

Показанные на фиг.4 результаты моделирования подтверждают указанные свойства заявляемой схемы. В качестве активных элементов могут применяться полевые транзисторы.

Таким образом, рассмотренное схемотехническое решение логического элемента сравнения k-значной переменной с заданным пороговым значением характеризуется многозначным состоянием внутренних сигналов, сигнала на его токовом входе и двоичным сигналом на токовом выходе и может быть положено в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US №8.159.304, fig.5.

2. Патент US №5.977.829, fig.1.

3. Патент US №5.789.982, fig.2.

4. Патент US №5.140.282.

5. Патент US №6.624.701, fig.4.

6. Патент US №6.529.078.

7. Патент US №5.734.294.

8. Патент US №5.557.220.

9. Патент US №6.624.701.

10. Патент RU №2319296.

11. Патент RU №2436224.

12. Патент RU №2319296.

13. Патент RU №2321157.

14. Патент RU №2383099.

15. Малюгин В.Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982, №4. С.84-93.

16. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

17. Чернов Н.И. Линейный синтез цифровых структур АСОИУ // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СРАВНЕНИЯ НА РАВЕНСТВО ДВУХ МНОГОЗНАЧНЫХ ПЕРЕМЕННЫХ | 2014 |

|

RU2549142C1 |

| К-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "МАКСИМУМ" | 2014 |

|

RU2549144C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НЕСТРОГОГО СРАВНЕНИЯ НА НЕРАВЕНСТВО ДВУХ МНОГОЗНАЧНЫХ ПЕРЕМЕННЫХ | 2014 |

|

RU2547233C1 |

| k-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "МАКСИМУМ" | 2014 |

|

RU2568385C1 |

| K-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "МИНИМУМ" | 2014 |

|

RU2553070C1 |

| МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОГО СДВИГА | 2014 |

|

RU2547225C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546082C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546078C1 |

| МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ОБРАТНОГО ЦИКЛИЧЕСКОГО СДВИГА | 2014 |

|

RU2553071C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ПРЯМОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693639C1 |

Изобретение относится к логическому элементу сравнения k-значной переменной с пороговым значением. Технический результат заключается в повышении быстродействия средств обработки цифровой информации за счет выполнения преобразования информации в многозначной токовой форме сигналов. Логический элемент сравнения содержит токовый вход (1) устройства и токовый выход (2) устройства, первый (3) и второй (4) выходные транзисторы с объединенными базами, третий (5) и четвертый (6) выходные транзисторы другого типа проводимости с объединенными базами, причем эмиттеры первого (3) и третьего (5) выходных транзисторов объединены, а эмиттеры второго (4) и четвертого (6) выходных транзисторов связаны друг с другом, первый (7) и второй (8) источники опорного тока, первое (9) токовое зеркало, согласованное с первой (10) шиной источника питания, второе (11) токовое зеркало, согласованное со второй (12) шиной источника питания. 4 ил.

Логический элемент сравнения k-значной переменной с пороговым значением, содержащий токовый вход (1) устройства и токовый выход (2) устройства, первый (3) и второй (4) выходные транзисторы с объединенными базами, третий (5) и четвертый (6) выходные транзисторы другого типа проводимости с объединенными базами, причем эмиттеры первого (3) и третьего (5) выходных транзисторов объединены, а эмиттеры второго (4) и четвертого (6) выходных транзисторов связаны друг с другом, первый (7) и второй (8) источники опорного тока, первое (9) токовое зеркало, согласованное с первой (10) шиной источника питания, второе (11) токовое зеркало, согласованное со второй (12) шиной источника питания, причем коллектор третьего (5) выходного транзистора соединен со входом второго (11) токового зеркала, отличающийся тем, что токовый вход (1) устройства соединен со входом первого (9) токового зеркала, выход которого подключен к объединенным эмиттерам первого (3) и третьего (5) выходных транзисторов и через первый (7) источник опорного тока связан со второй (12) шиной источника питания, коллекторы первого (3) и второго (4) выходных транзисторов соединены с первой (10) шиной источника питания, выход второго (11) токового зеркала соединен с объединенными эмиттерами второго (4) и четвертого (6) выходных транзисторов и через второй (8) источник опорного тока соединен с первой (10) шиной источника питания, коллектор четвертого (6) выходного транзистора подключен ко входу дополнительного токового зеркала (13), согласованного со второй (12) шиной источника питания, выход которого подключен к выходу (2) устройства, причем базы первого (3) и второго (4) выходных транзисторов подключены к первому (14) источнику вспомогательного напряжения, а базы третьего (5) и четвертого (6) выходных транзисторов подключены ко второму (15) источнику вспомогательного напряжения.

| SU 1676395 A1, 10.02.1996 | |||

| US 0005742154 A1, 21.04.1998 | |||

| JP 2000151381 A , 30.05.2000 | |||

| Логический элемент | 1987 |

|

SU1506542A1 |

Авторы

Даты

2015-04-10—Публикация

2014-03-27—Подача