Изобретение относится к вычислительной технике, в частности к устройствам контроля, и может быть использовано в опытно-конструкторских работах и практике эксплуатации, где требуется определять оптимальную периодичность контроля и технического обслуживания изделий и соответствующих этой периодичности значения эксплуатационных характеристик.

Существуют устройства [1, 2], позволяющие определять оптимальные периоды технического обслуживания изделия с учетом различия значений интенсивности отказов в различных режимах (рабочий и отдых) нахождения изделия. Область применения этих устройств ограничена изделиями, интенсивность отказов которых описывается экспоненциальным законом распределения.

Известны устройства [3, 4], позволяющие определять оптимальные периоды технического обслуживания изделий с возрастающей интенсивностью отказов в процессе их эксплуатации. Область применения этих устройств ограничена изделиями непрерывного применения.

Наиболее близким по технической сущности к заявляемому изобретению является устройство [5], содержащее блок деления, четыре блока умножения, четыре блока нелинейностей, два интегратора, шесть сумматоров, три вычитателя, мультивибратор, компаратор, схему ИЛИ, шесть вентилей, четыре элемента задержки, четыре элемента памяти, два триггера, блок памяти, аттенюатор, два накапливающих сумматора. Его недостатком является ограниченная область применения изделий, интенсивность отказов которых описывается так же, как в устройствах [1, 2].

Целью заявляемого технического решения является расширение области применения и повышение точности определения значений выходных параметров изделия.

Цель достигается путем реализации математической модели, позволяющей учитывать изменения во времени функции отказов изделия. Критерием оптимизации периода обслуживания является минимум коэффициента простоя.

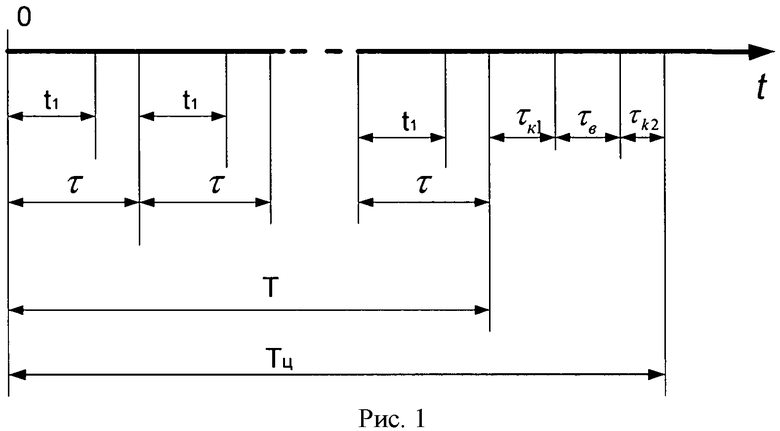

Процесс применения многих изделий имеет циклический характер, каждый цикл включает в себя работу изделия в номинальном (рабочем) режиме и в режиме отдыха от применения. На рисунке 1 представлена диаграмма процесса применения изделия, на которой τ - длительность одного цикла применения, где t1 - длительность функционирования изделия в рабочем режиме. При этом интенсивность отказов изделия имеет значение λ1. На интервале t2=τ-t1 изделие находится в режиме отдыха и его интенсивность отказов равна λ2<λ1 [6].

Для поддержания изделия в работоспособном состоянии периодически осуществляется его техническое обслуживание, на которое затрачивается время τобс. При этом выполняется комплексный контроль состояния изделия в течение времени τк1, проведение регламентных работ и восстановление работоспособности изделия в случае обнаружения отказа, на что расходуется время τв. После окончания этих работ проводится контрольная проверка работоспособности изделия в течение τк2.

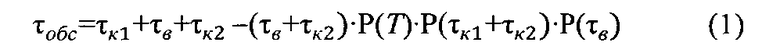

Отметим, что контроль технического состояния выполняется в условиях номинального режима работы изделия. Поэтому на интервалах времени τк1 и τк2 интенсивность отказов будет λ1. Для проведения ремонтно-восстановительных работ изделие переводится в режим отдыха, что соответствует интенсивности его отказов λ2. В связи с этим, общая продолжительность τобс технического обслуживания выражается следующей формулой:

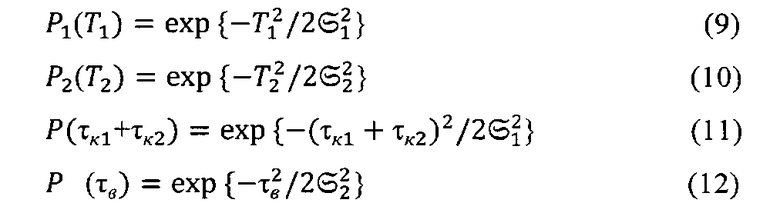

где P(T), P(τк1+τк2), P(τв) - вероятности безотказной работы изделия на соответствующих интервалах времени.

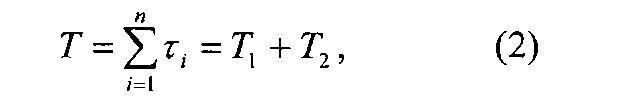

Длительность периода обслуживания T (рисунок 1) включает в себя множество

при этом суммарная продолжительность T1 работы изделия в номинальном режиме на интервале времени T будет

а продолжительность нахождения изделия в режиме отдыха

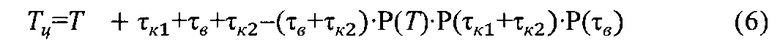

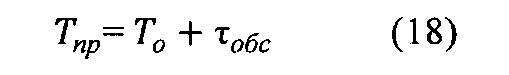

Длительность цикла обслуживания составляет

Подставив (1) в выражение (5) получим

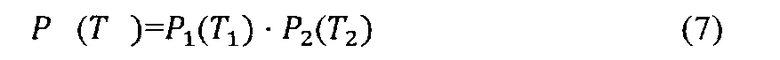

Вероятность безотказной работы изделия на интервале времени T составляет

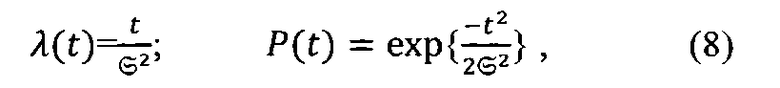

Важным параметром безотказности является интенсивность отказов λ. Теория и практика эксплуатации широкого класса обслуживаемых изделий показывает, что старение изделий сопровождается возрастанием интенсивности λ. Для определения времени безотказной работы таких изделий применим закон распределения Рэлея. При этом интенсивность отказов λ(t) и вероятность безотказной работы P(t) определяются так [7]

где  - параметр распределения Рэлея. В связи с этим имеет место следующее:

- параметр распределения Рэлея. В связи с этим имеет место следующее:

На любом интервале времени t изделие может находиться в одном из состояний:

t=tф+to, где tф - время работоспособного состояния; tо - время пребывания в отказе.

В течение одного цикла применения изделия по назначению последнее соотношение принимает вид:

Аналогично на интервале режима отдыха будет

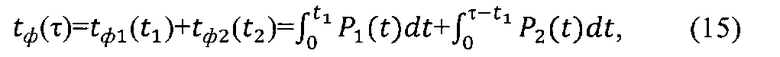

Время работоспособного состояния изделия на интервале τ определяется по формуле:

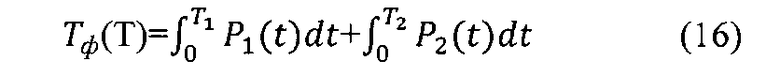

а на интервале времени T его значение будет:

С учетом изложенного, возможное время пребывания изделия на интервале времени T в состоянии отказа выражается следующим образом:

Время, в течение которого изделие не может применяться по назначению (время простоя), составляет:

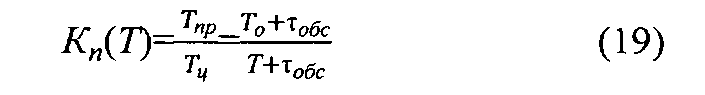

Важной количественной характеристикой качества изделия является коэффициент простоя. Его значение с учетом (5) и (18) определяется по формуле:

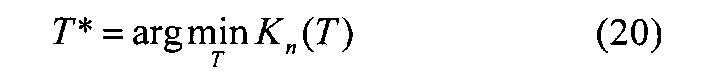

Задача определения оптимального периода технического обслуживания изделия записывается в следующем виде:

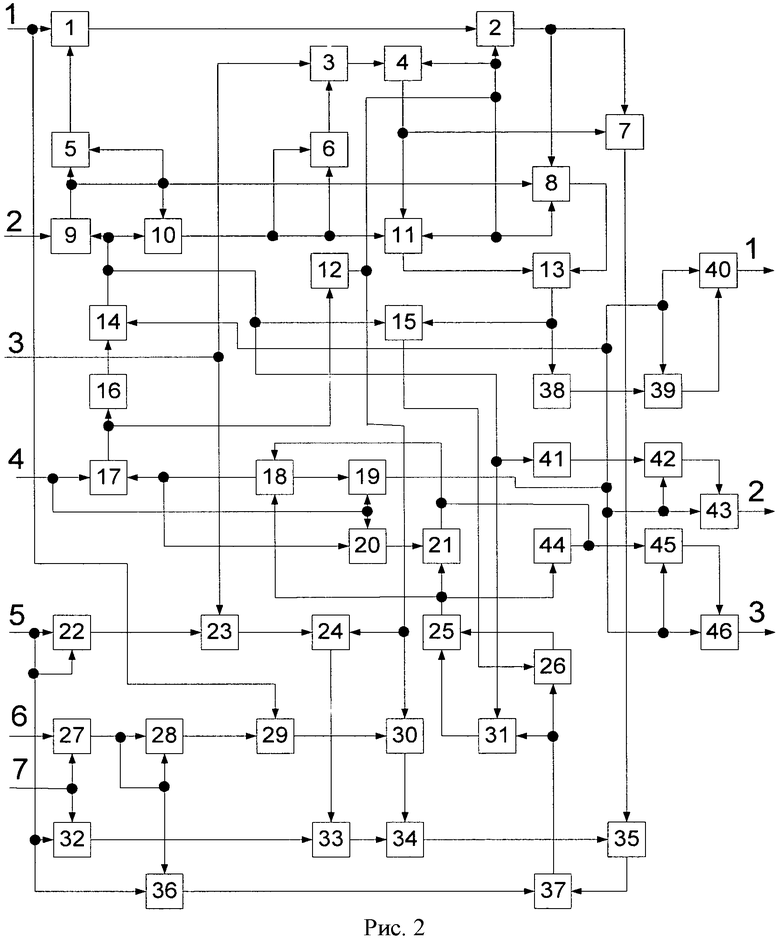

Предложенная математическая модель может быть реализована аппаратурно с помощью устройства, схема которого показана на рисунке 2.

Устройство содержит: блоки деления 1, 3, 23, 25, 29; блоки нелинейностей 2, 4, 24, 30; блоки умножения 5, 6, 7, 9, 22, 28, 33, 34, 35; интеграторы 8, 11; датчик времени (генератор ступенчатого напряжения) 14; мультивибратор 12, работающий в ждущем режиме; сумматоры 13, 26, 27, 31, 32, 36; элементы задержки 16, 38, 41, 44; вычитатели 10, 15, 37; блок сравнения 18 (компаратор); схему ИЛИ 17; элементы памяти 39, 42, 45; триггеры 19, 20; вентили 21, 40, 43, 46.

Схемы функциональных элементов устройства представлены в [8].

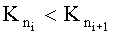

Процесс определения оптимального решения имеет итерационный характер. Последовательно в каждом i-м цикле работы устройства осуществляется дискретное увеличение периода технического обслуживания T согласно (2), значения величин T1 и T2 увеличиваются согласно (3) и (4) соответственно, а τобс вычисляется согласно (1). С учетом этого в соответствии с (19) вычисляется значение Kn(T). Процесс поиска оптимального решения прекращается при выполнении условия

Устройство работает следующим образом.

По сигналу «Пуск», поступающему с четвертого входа устройства, первый триггер 19 переключается в нулевое состояние и закрывает вентили 40, 43, 46, а второй триггер 20 переходит в единичное состояние, открывая первый вентиль 21. Кроме того, сигнал «Пуск», пройдя через схему ИЛИ 17, поступает непосредственно на вход мультивибратора 12, а через первый элемент задержки 16 - на первый вход датчика времени 14. Одиночный выходной сигнал мультивибратора 12 передается на вторые входы блоков нелинейностей 2, 4, 24, 30, а также на третьи входы первого 8 и второго 11 интеграторов, переводя их в нулевое состояние.

В первом цикле работы устройства датчик времени 14 генерирует сигнал, соответствующий величине T=τ, который передается на первый вход второго вычитателя 15, через третий элемент задержки 41 во второй элемент памяти 42, на четвертый сумматор 31 и на вторые входы четвертого блока умножения 9 и первого вычитателя 10. Со второго входа устройства на первый вход четвертого блока умножения 9 поступает значение коэффициента использования изделия Ku. Этот коэффициент отражает долю времени τ, равную t1, когда изделие должно быть готово к применению по целевому назначению, 0<Ku<1. Сигнал, соответствующий значению величины t1, с выхода четвертого блока умножения 9 передается на первые входы первого интегратора 8, первого вычитателя 10 и на оба входа первого блока умножения 5. Сигнал

. Выходной сигнал

. Выходной сигнал  первого блока деления 1 передается на первый вход первого блока нелинейности 2. Текущее значение величины P1, полученное в соответствии с (9), из блока 2 поступает на первый вход третьего блока умножения 7 и на второй вход первого интегратора 8. Разностный потенциал t2=τ-t1 из первого вычитателя 10 передается на первый вход второго интегратора 11 и на оба входа второго блока умножения 6. С третьего входа устройства на первые входы второго 3 и третьего 23 блоков деления поступает значение параметра

первого блока деления 1 передается на первый вход первого блока нелинейности 2. Текущее значение величины P1, полученное в соответствии с (9), из блока 2 поступает на первый вход третьего блока умножения 7 и на второй вход первого интегратора 8. Разностный потенциал t2=τ-t1 из первого вычитателя 10 передается на первый вход второго интегратора 11 и на оба входа второго блока умножения 6. С третьего входа устройства на первые входы второго 3 и третьего 23 блоков деления поступает значение параметра  . Выходной сигнал

. Выходной сигнал

с выхода блока деления 3 подается на первый вход второго блока нелинейности 4, в результате чего в блоке 4 вычисляется в соответствии с (10) значение величины P2 и передается на вторые входы второго интегратора 11 и третьего блока умножения 7. Выходной сигнал tф1(t1) первого интегратора 8 и выходной сигнал tф2(t2) второго интегратора 11 поступают соответственно на первый и второй входы первого сумматора 13. В сумматоре 13 в соответствии с (15) вычисляется значение величины tф(τ) и передается на второй вход второго вычитателя 15 непосредственно, а через второй элемент задержки 38 в первый элемент памяти 39. Разностный потенциал t0(τ)=τ-tф(τ) с выхода вычитателя 15 поступает на первый вход второго сумматора 26.

с выхода блока деления 3 подается на первый вход второго блока нелинейности 4, в результате чего в блоке 4 вычисляется в соответствии с (10) значение величины P2 и передается на вторые входы второго интегратора 11 и третьего блока умножения 7. Выходной сигнал tф1(t1) первого интегратора 8 и выходной сигнал tф2(t2) второго интегратора 11 поступают соответственно на первый и второй входы первого сумматора 13. В сумматоре 13 в соответствии с (15) вычисляется значение величины tф(τ) и передается на второй вход второго вычитателя 15 непосредственно, а через второй элемент задержки 38 в первый элемент памяти 39. Разностный потенциал t0(τ)=τ-tф(τ) с выхода вычитателя 15 поступает на первый вход второго сумматора 26.

Параметр τв с пятого входа устройства передается на первые входы пятого 32 и шестого 36 сумматоров, а также на оба входа пятого блока умножения 22. Выходной сигнал

Значение величины  с выхода блока деления 23 передается на первый вход третьего блока нелинейности 24, выходной сигнал которого P(τв), полученный в соответствии с (12), поступает на второй вход седьмого блока умножения 33. С шестого входа устройства значение параметра τк1 передается на первый вход третьего сумматора 27, на второй вход которого, как и на второй вход пятого сумматора 32, с седьмого входа устройства поступает значение величины τк2. Суммарный сигнал τк1+τк2 с выхода второго сумматора 27 передается на второй вход шестого сумматора 36 и на оба входа шестого блока умножения 28. Результат перемножения (τк1+τк2)2 из блока умножения 28 поступает на второй вход пятого блока деления 29, выходной сигнал которого

с выхода блока деления 23 передается на первый вход третьего блока нелинейности 24, выходной сигнал которого P(τв), полученный в соответствии с (12), поступает на второй вход седьмого блока умножения 33. С шестого входа устройства значение параметра τк1 передается на первый вход третьего сумматора 27, на второй вход которого, как и на второй вход пятого сумматора 32, с седьмого входа устройства поступает значение величины τк2. Суммарный сигнал τк1+τк2 с выхода второго сумматора 27 передается на второй вход шестого сумматора 36 и на оба входа шестого блока умножения 28. Результат перемножения (τк1+τк2)2 из блока умножения 28 поступает на второй вход пятого блока деления 29, выходной сигнал которого  передается в четвертый блок нелинейности 30. Сигнал τв+τк2 с выхода пятого сумматора 32 поступает на первый вход седьмого блока умножения 33, в котором формируется и передается на первый вход восьмого блока умножения 34 сигнал P(τв)(τв+τк2). Из четвертого блока нелинейности 30 на второй вход восьмого блока умножения 34 поступает значение P(τк1+τк2).

передается в четвертый блок нелинейности 30. Сигнал τв+τк2 с выхода пятого сумматора 32 поступает на первый вход седьмого блока умножения 33, в котором формируется и передается на первый вход восьмого блока умножения 34 сигнал P(τв)(τв+τк2). Из четвертого блока нелинейности 30 на второй вход восьмого блока умножения 34 поступает значение P(τк1+τк2).

Произведение P(τв) (τв+τк2)·P(τк1+τк2) с выхода восьмого блока умножения 34 передается на второй вход девятого блока умножения 35, на первый вход которого из третьего блока умножения 7 приходит значение произведения P1(t1)·P2(t2). Результат перемножения с выхода блока 35 передается на второй вход третьего вычитателя 37, на первый вход которого из шестого сумматора 36 поступает значение суммы τв+τк1+τк2. Выходной сигнал вычитателя 37 поступает на вторые входы второго сумматора 26 и четвертого сумматора 31. Результаты суммирования с выходов второго 26 и четвертого 31 сумматоров передаются соответственно на первый и второй входы четвертого блока деления 25. В блоке 25 формируется в соответствии с (19) текущее значение коэффициента простоя и передается непосредственно в четвертый элемент задержки 44 и на первый вход компаратора 18, а через открытый вентиль 21 - на информационный вход третьего элемента памяти 45 и на второй вход компаратора 18. В первом цикле работы устройства входные сигналы компаратора 18 равны между собой, поэтому управляющий сигнал будет на первом выходе компаратора 18. Этот сигнал переключает второй триггер 20 в нулевое состояние, в результате чего первый вентиль 21 будет закрыт. Кроме того, сигнал с первого выхода компаратора 18, пройдя через схему ИЛИ 17, поступит на вход первого элемента задержки 16, запустит мультивибратор 12 на генерацию очередного управляющего сигнала, приводящего в исходное состояние сопряженные с ним элементы схемы устройства. Выходной сигнал компаратора 18, пройдя через элемент задержки 16, поступит на управляющий вход датчика времени 14. В связи с этим, датчик времени 14 выработает сигнал, соответствующий новому значению времени T. Далее процесс вычисления функции Kn(T) повторится.

В каждом очередном цикле работы устройства будут изменяться значения переменных величин в соответствии с возрастанием значения параметра T. В блоке сравнения 18 будут сравниваться между собой значения

Положительный эффект, который дает предлагаемое техническое решение, состоит в получении расчетных значений периода технического обслуживания, обеспечивающего минимум коэффициента простоя изделия и вычисление времени безотказной работы с учетом возрастания интенсивности отказов изделия.

Значения выходных величин позволяют обоснованно планировать применение и техническую эксплуатацию изделия.

Источники информации

1. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Майданович О.В. Патент RU 2479041, МПК G07C 3/08, 2013.

2. Гришин В.Д., Зиновьев С.В., Соколов Б.В., Майданович О.В. Патент RU 2452027, МПК G07C 3/08, 2012.

3. Гришин В.Д., Павлов А.Н., Михайлов Е.П. Патент RU 2343544, МПК G07C 3/08, 2009.

4. Гришин В.Д., Кудряшов А.Н., Тимошенко Д.В. Патент RU 2347272, МПК G07C 3/08, 2009.

5. Соколов Б.В., Гришин В.Д., Зеленцов В.А., Цивирко Е.Г. Патент RU 2476934, МПК G07C 3/08, 2013.

6. Седякин Н.М. Об одном физическом принципе теории надежности. - Изв. АН СССР, ОТН, Техническая кибернетика. 1966, №3.

7. Половко A.M. Основы теории надежности. - М.: Наука, 1964.

8. Тетельбаум И.М., Шрейдер Ю.Р. 400 схем для АВМ. - М.: Энергия, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ СТРАТЕГИИ ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ СРЕДСТВ СИСТЕМЫ | 2014 |

|

RU2565890C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА КОНТРОЛЯ И УПРАВЛЕНИЯ ТЕХНИЧЕСКИМ СОСТОЯНИЕМ ИЗДЕЛИЯ | 2011 |

|

RU2479041C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОЙ ПРОГРАММЫ ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ СИСТЕМЫ | 2007 |

|

RU2358320C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНЫХ ПРОГРАММ ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ СРЕДСТВ СИСТЕМЫ | 2009 |

|

RU2429542C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОЙ ПЕРИОДИЧНОСТИ КОНТРОЛЯ СОСТОЯНИЯ ИЗДЕЛИЯ | 2011 |

|

RU2476934C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА УПРАВЛЕНИЯ ТЕХНИЧЕСКИМ СОСТОЯНИЕМ ИЗДЕЛИЯ | 2014 |

|

RU2542666C1 |

| УСТРОЙСТВО ДЛЯ УЧЕТА И КОНТРОЛЯ ВРЕМЕНИ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 1991 |

|

RU2026571C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЯ ХАРАКТЕРИСТИК ГОТОВНОСТИ ИЗДЕЛИЯ К ПРИМЕНЕНИЮ | 2014 |

|

RU2580099C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ ЭКСПЛУАТАЦИОННЫХ ХАРАКТЕРИСТИК ИЗДЕЛИЯ | 2011 |

|

RU2476935C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ ЭКСПЛУАТАЦИОННЫХ ХАРАКТЕРИСТИК ИЗДЕЛИЯ | 2010 |

|

RU2452027C2 |

Изобретение относится к устройствам контроля, в которых требуется определять оптимальные периоды контроля и технического обслуживания изделий, а также значения эксплуатационных характеристик изделия. Техническим результатом является повышение точности определения значений выходных параметров изделия. В устройстве обеспечивается для каждого очередного цикла работы в соответствии с возрастанием параметра времени контроль времени работоспособного состояния изделия, определение оптимального значения периода обслуживания, а также возможное минимальное значение коэффициента простоя для соответствия оптимальному периоду обслуживания. 1 ил.

Устройство для определения эксплуатационно-технических характеристик изделия при оптимальном периоде его технического обслуживания, содержащее первый и второй блоки умножения, первый элемент задержки, первый блок нелинейности, выход которого соединен со вторым входом первого интегратора и с первым входом третьего блока умножения, выход которого подключен к первому входу девятого блока умножения, а второй вход - к выходу второго блока нелинейности и ко второму входу второго интегратора, первый вход которого соединен с выходом первого вычитателя, а выход - со вторым входом первого сумматора, первый вход которого подключен к выходу первого интегратора, а выход связан непосредственно со вторым входом второго вычитателя и через второй элемент задержки с информационным входом первого элемента памяти, выход которого подключен к входу второго вентиля, выход которого является первым выходом устройства, вторым выходом которого является выход третьего вентиля, информационный вход которого соединен с выходом второго элемента памяти, информационный вход которого связан с выходом третьего элемента задержки, третьим выходом устройства является выход четвертого вентиля, информационный вход которого соединен с выходом третьего элемента памяти, информационный вход которого связан с выходом четвертого элемента задержки, а управляющий вход вместе с управляющими входами первого и второго элементов памяти, второго, третьего и четвертого вентилей подключен к выходу первого триггера, второй вход которого соединен со вторым выходом компаратора, а первый вход вместе со вторым входом второго триггера связан с четвертым входом устройства и с первым входом схемы ИЛИ, выход которой соединен с входом мультивибратора, а второй вход с первым выходом компаратора, первый вход которого связан с входом четвертого элемента задержки и с выходом четвертого блока деления, второй вход которого подключен к выходу четвертого сумматора, а первый вход к выходу второго сумматора, первый вход которого соединен с выходом второго вычитателя, а второй вход со вторым входом четвертого сумматора и с выходом третьего вычитателя, второй вход которого связан с выходом девятого блока умножения, а первый вход с выходом шестого сумматора, второй вход которого подключен к выходу третьего сумматора, второй вход которого соединен со вторым входом пятого сумматора, выход второго триггера подключен к управляющему входу первого вентиля, второй вход третьего блока нелинейности связан со вторым входом четвертого блока нелинейности, отличающееся тем, что в него введены датчик времени, первый, второй, третий и пятый блоки деления, четвертый, пятый, шестой, седьмой и восьмой блоки умножения, причем первый вход устройства соединен с первыми входами пятого блока деления и первого блока деления, второй вход которого связан с выходом первого блока умножения, а выход подключен к первому входу первого блока нелинейности, второй вход которого вместе со вторыми входами третьего и четвертого блоков нелинейностей и третьими входами первого и второго интеграторов соединен со вторым входом второго блока нелинейности, первый вход которого подключен к выходу второго блока деления, первый вход которого соединен с третьим входом устройства и первым входом третьего блока деления, а второй вход с выходом второго блока умножения, первый и второй входы которого подключены к выходу первого вычитателя, первый вход которого соединен с первым входом первого интегратора, с первым и вторым входами первого блока умножения и с выходом четвертого блока умножения, первый вход которого является вторым входом устройства, а второй выход вместе со вторым входом первого вычитателя подключен к входу третьего элемента задержки, к первому входу четвертого сумматора, к первому входу второго вычитателя и к выходу датчика времени, второй вход которого соединен с выходом первого триггера, а первый вход подключен к выходу первого элемента задержки, вход которого связан с выходом схемы ИЛИ, второй вход которой соединен с первым входом второго триггера, выход первого вентиля подключен к выходу четвертого элемента задержки и ко второму входу компаратора, а второй вход к выходу четвертого блока деления, пятый вход устройства соединен с первыми входами шестого сумматора и пятого сумматора, а также с первым и вторым входами пятого блока умножения, выход которого подключен ко второму входу третьего блока деления, выход которого соединен с первым входом третьего блока нелинейности, выход которого соединен со вторым входом седьмого блока умножения, первый вход которого связан с выходом пятого сумматора, а выход с первым входом восьмого блока умножения, выход которого соединен со вторым входом девятого блока умножения, а второй вход с выходом четвертого блока нелинейности, первый вход которого связан с выходом пятого блока деления, второй вход которого соединен с выходом шестого блока умножения, первый и второй входы которого подключены к выходу третьего сумматора, первым входом которого является шестой вход устройства, седьмой вход которого подключен к вторым входам третьего и пятого сумматоров.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2007 |

|

RU2343544C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА КОНТРОЛЯ И УПРАВЛЕНИЯ ТЕХНИЧЕСКИМ СОСТОЯНИЕМ ИЗДЕЛИЯ | 2011 |

|

RU2479041C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО ПЕРИОДА ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ ИЗДЕЛИЯ | 2007 |

|

RU2343544C1 |

| Фильтр для воды | 1974 |

|

SU573171A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

Авторы

Даты

2015-06-10—Публикация

2014-02-19—Подача