ПРЕДПОСЫЛКИ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

[0001] Один или более аспектов изобретения относится, в общем, к многопроцессорным вычислительным средам, и в частности, к транзакционной обработке внутри таких вычислительных сред.

[0002] Постоянной проблемой в многопроцессорном программировании являются обновления одной и той же ячейки памяти несколькими центральными процессорными устройствами (ЦП). Многие команды, обновляющие ячейки памяти, включая даже простые логические операции, такие как И (AND), производят это с множественным доступом к ячейке. Например, сначала считывается содержимое ячейки памяти, а потом обновленный результат возвращается обратно.

[0003] Для безопасного обновления одной и той же ячейки памяти несколькими процессорами, доступ к ячейке сделан сериализированным. Одна из команд, команда ПРОВЕРИТЬ И УСТАНОВИТЬ (TEST AND SET), введенная в архитектуре S/360, ранее предлагаемой корпорацией International Business Machines, обеспечивает взаимоблокированное обновление ячейки памяти. Взаимная блокировка обновления означает, что с точки зрения других процессоров и подсистемы ввода/вывода (I/O) (напр., подсистемы каналов), весь доступ к памяти для команды оказывается неделимым. Позже, в архитектуре S/370, предложенной корпорацией International Business Machines, были введены команды СРАВНИТЬ И ОБМЕНЯТЬ (COMPARE AND SWAP) и СРАВНИТЬ ДВАЖДЫ И ОБМЕНЯТЬ (COMPARE DOUBLE AND SWAP), предоставляющие более усложненные средства осуществления обновления с взаимоблокировкой, и делающие возможным реализацию того, что теперь известно как блокировочное слово (или семафор). Недавно введенные команды предоставили дополнительные возможности обновления с взаимоблокировкой, включая СРАВНИТЬ И ОБМЕНЯТЬ И ОЧИСТИТЬ (COMPARE AND SWAP AND PURGE) и СРАВНИТЬ И ОБМЕНЯТЬ И СОХРАНИТЬ (COMPARE AND SWAP AND STORE). Однако все эти команды обеспечивают взаимоблокировку только для единичной ячейки памяти.

[0004] Более сложные методы программирования могут потребовать взаимно блокированного обновления многих ячеек памяти, такие как добавление элемента к двусвязанному списку. При такой операции как прямой, так и обратный указатель должны выглядеть обновляемыми одновременно с точки зрения других процессоров и подсистемы ввода-вывода. Для того чтобы произвести такое обновление многих ячеек, программа вынуждена использовать отдельную, единичную точку сериализации, такую как блокировочное слово. Однако блокировочные слова могут предусматривать более грубый уровень сериализации, чем гарантированный; например, блокировочные слова могут перевести в последовательный режим целую очередь из миллионов элементов, хотя только два элемента обновляются. Программа может структурировать данные для использования более тонкой сериализации (напр., иерархии точек блокировки), но это вносит дополнительные трудности, такие как возможность тупиковой ситуации при нарушении иерархии, и проблемы с восстановлением, если программа сталкивается с ошибкой, удерживая одну или более блокировок, или блокировка не может быть запрошена.

[0005] В дополнение к вышесказанному, существует множество сценариев, в которых программа может выполнять последовательность команд, которые могут или не могут привести к ситуации исключения. Если ситуация исключения не наступает, программа продолжается; однако, если обнаружено исключение, программа может предпринять корректирующее действие для устранения ситуации исключения. Java, к примеру, может использовать такое выполнение для, например, упреждающего выполнения, частичного встраивания функции, и/или изменения последовательности проверки нуля указателя.

[0006] В средах классических операционных систем, таких как z/OS и ее предшественники, предложенные корпорацией International Business Machines, программа создает среду восстановления для перехвата любой ситуации программного исключения, которая может встретиться. Если программа не перехватывает исключение, операционная система обычно аварийно завершает программу для исключений, которые операционная система не готова обработать. Создание и использование такой среды затратно и сложно.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

[0007] Для устранения недостатков уровня техники предложен машиночитаемый носитель данных, считываемый обрабатывающим устройством и хранящий команды, выполняемые обрабатывающим устройством для осуществления способа обеспечения диагностической информации после сброса транзакции, включающего: обнаружение, с помощью процессора, сброса транзакции, причем указанная транзакция включает одну или более команд и эффективно задерживает фиксацию транзакционных сохранений в главной памяти до тех пор, пока не завершится выбранная транзакция; определение, с помощью процессора, на основе сброса, должна ли диагностическая информация быть сохранена в блок диагностики транзакций (TDB); и на основе определения, указывающего, что диагностическая информация должна быть сохранена, сохранение в блоке диагностики транзакций диагностической информации, включающей адрес команды, соответствующей сброшенной транзакции, который зависит от причины сброса, представляемой кодом сброса, причем если код сброса имеет первое значение из одного или нескольких первых значений, диагностическая информация включает адрес команды, выполнявшейся при обнаружении сброса, если код сброса имеет второе значение из одного или нескольких вторых значений, диагностическая информация включает адрес команды, находящейся после команды, выполнявшейся при обнаружении сброса, и если код сброса имеет третье значение из одного илинескольких третьих значений, диагностическая информация включает адрес команды, более ранней или более поздней, чем команда, выполнявшаяся при обнаружении сброса.

[0008] Объектами изобретения являются также соответствующие компьютерная система и способ для обеспечения диагностической информации после сброса транзакции.

[0009] Реализуются другие особенности и преимущества. Другие варианты воплощения изобретения и аспекты излагаются здесь подробно и считаются частью формулы изобретения.

КРАТКОЕ ОПИСАНИЕ И НЕСКОЛЬКО ПРЕДСТАВЛЕНИЙ ЧЕРТЕЖЕЙ

[0010] Один или более аспектов выделены особо и явно объявлены как примеры в формуле изобретения в конце описания. Вышеуказанные и другие объекты, особенности и преимущества понятны из следующего подробного описания с помощью сопровождающих чертежей, в которых:

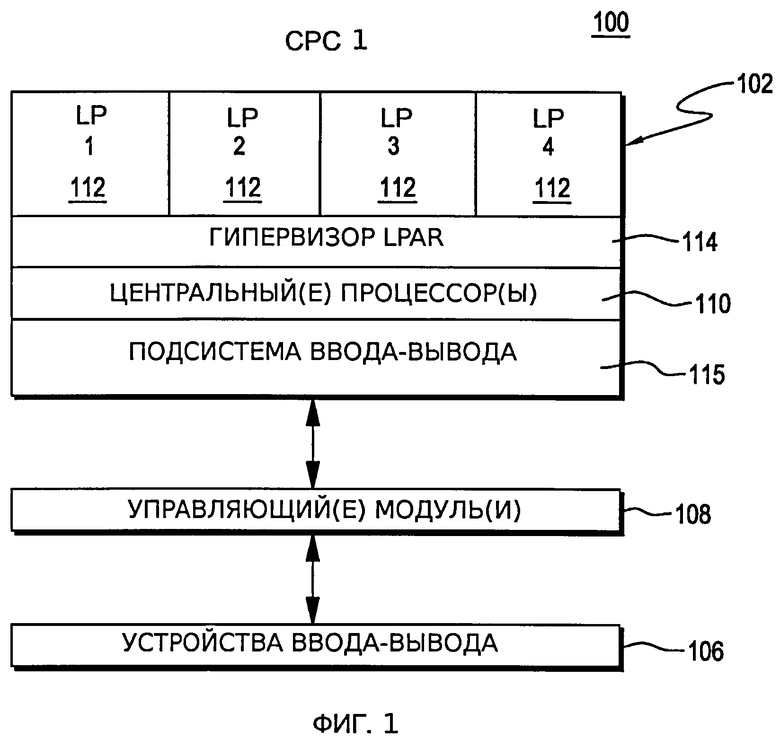

На ФИГ. 1 изображен один из вариантов вычислительной среды.

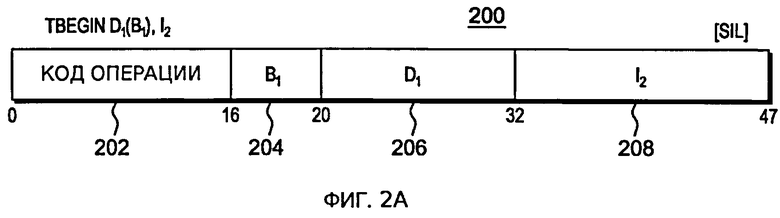

На ФИГ. 2А изображен один из примеров команды НАЧАТЬ ТРАНЗАКЦИЮ (TRANSACTION BEGIN) (TBEGIN).

На ФИГ. 2Б изображен в дальнейших подробностях один из вариантов поля команды TBEGIN согласно ФИГ. 2А.

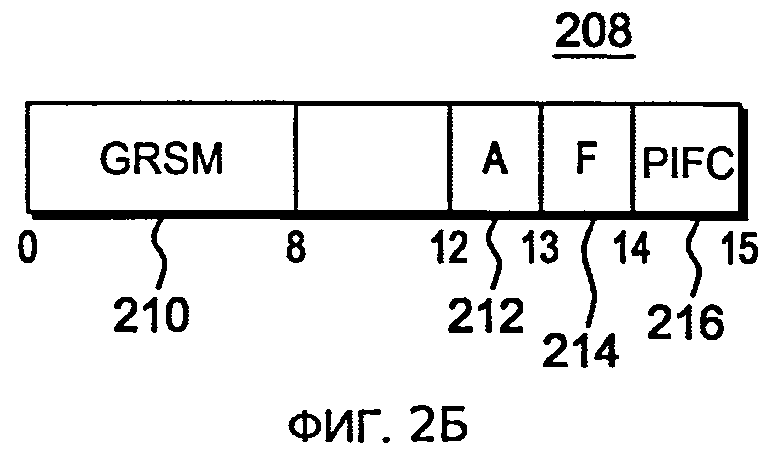

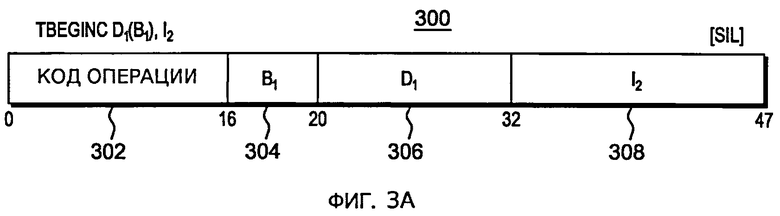

На ФИГ. 3А изображен один из примеров команды НАЧАТЬ ТРАНЗАКЦИЮ ВЫНУЖДЕННО (TRANSACTION BEGIN CONSTRAINED) (TBEGINC).

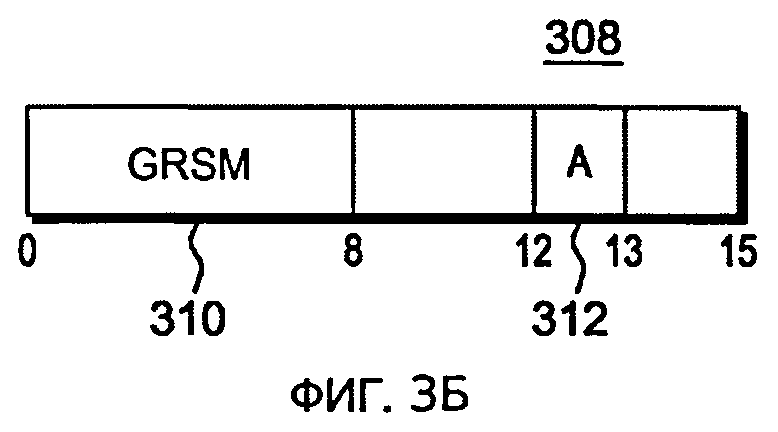

На ФИГ. 3Б изображен в дальнейших подробностях один из вариантов поля команды TBEGINC согласно ФИГ. 3А.

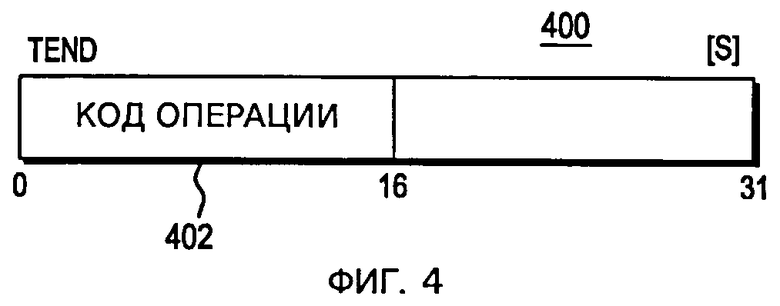

На ФИГ. 4 изображен один из примеров команды ЗАКОНЧИТЬ ТРАНЗАКЦИЮ (TRANSACTION END) (TEND).

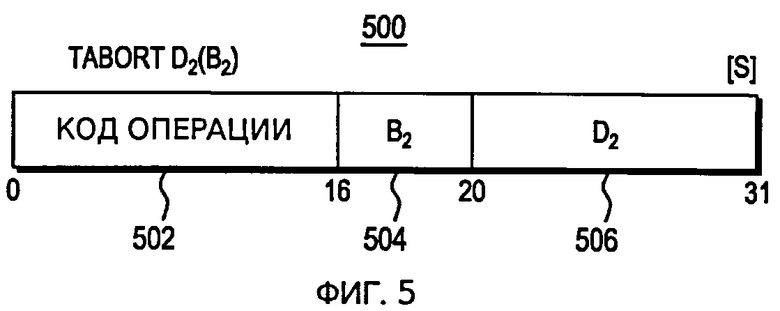

На ФИГ. 5 изображен один из примеров команды СБРОСИТЬ ТРАНЗАКЦИЮ (TRANSACTION ABORT) (TABORT).

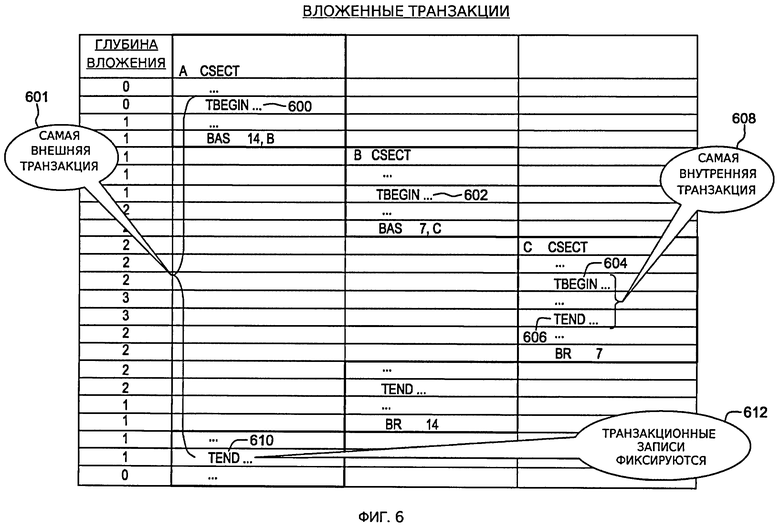

На ФИГ. 6 изображен один из примеров вложенных транзакций.

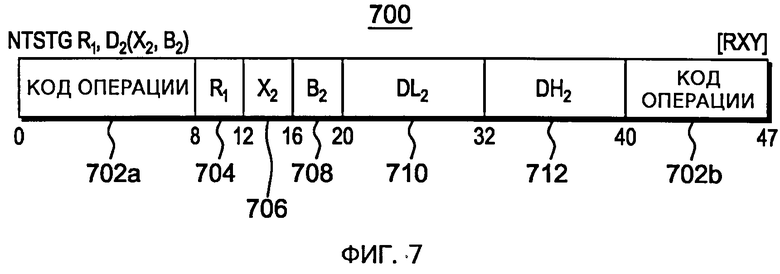

На ФИГ. 7 изображен один из примеров команды НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ (NONTRANSACTIONAL STORE) (NTSTG).

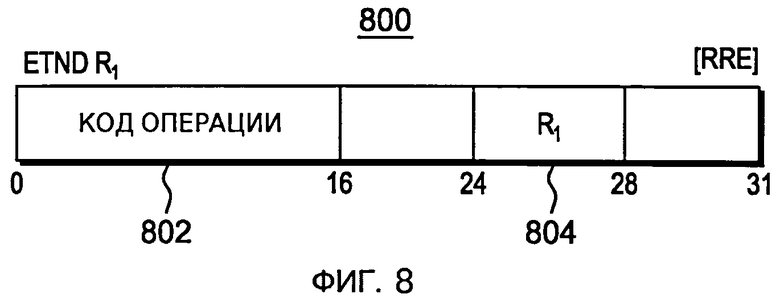

На ФИГ. 8 изображен один из примеров команды ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИИ (EXTRACT TRANSACTION NESTING DEPTH) (ETND).

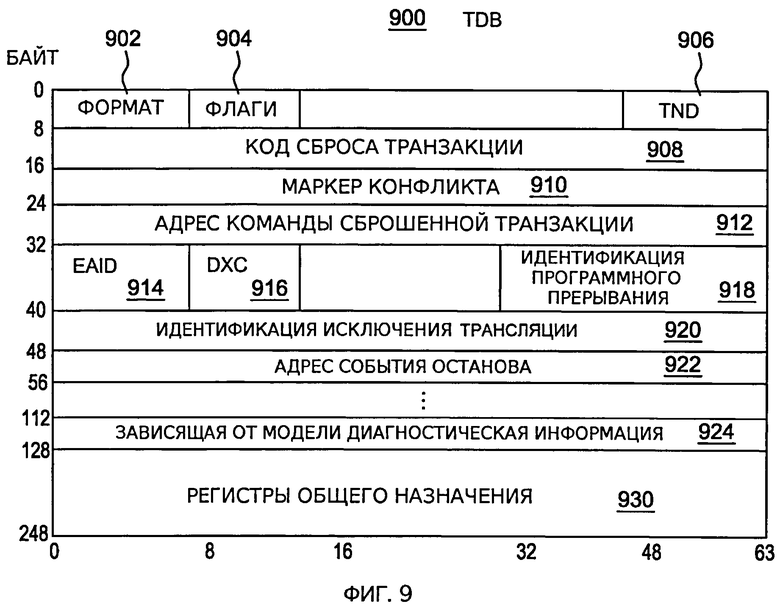

На ФИГ. 9 изображен один из примеров блока диагностики транзакций.

На ФИГ.10 изображены примеры причин сброса, вместе с соответствующими кодами сброса и кодами состояния.

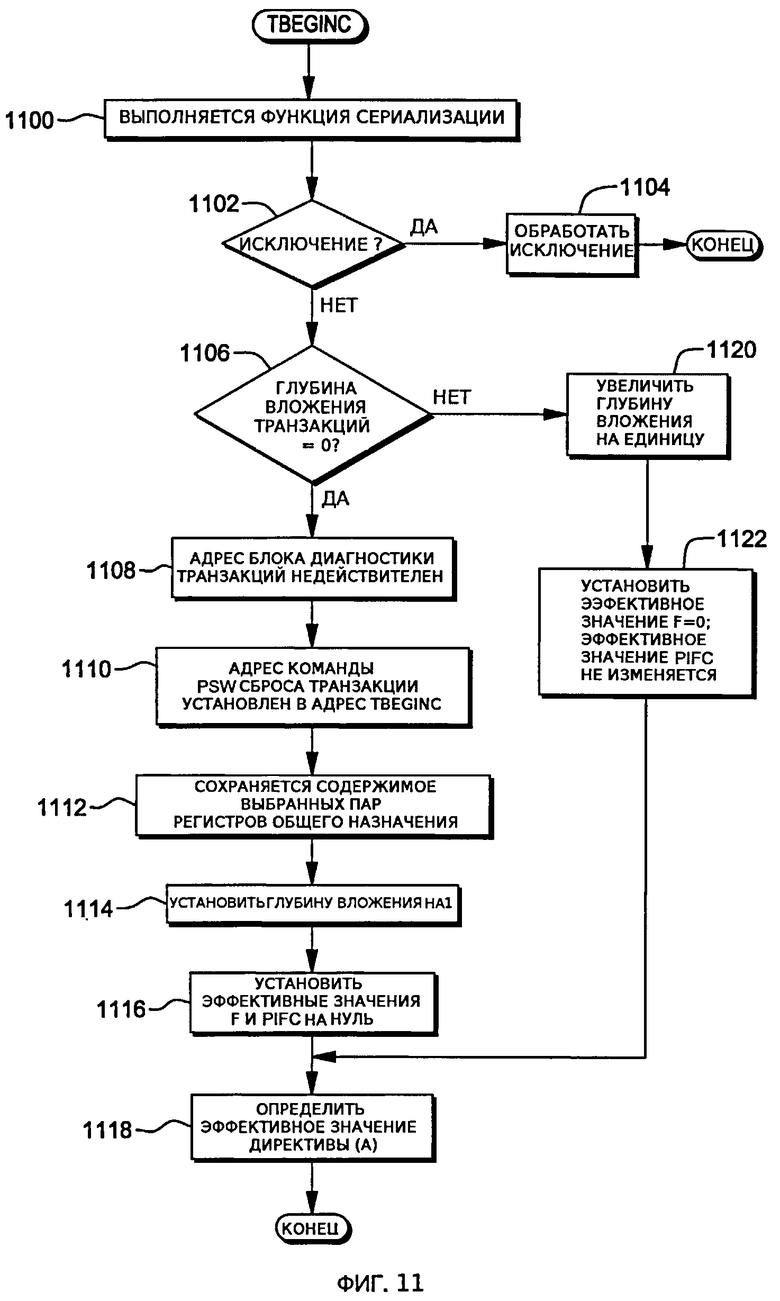

На ФИГ.11 изображен один из вариантов логики, связанной с выполнением команды TBEGINC.

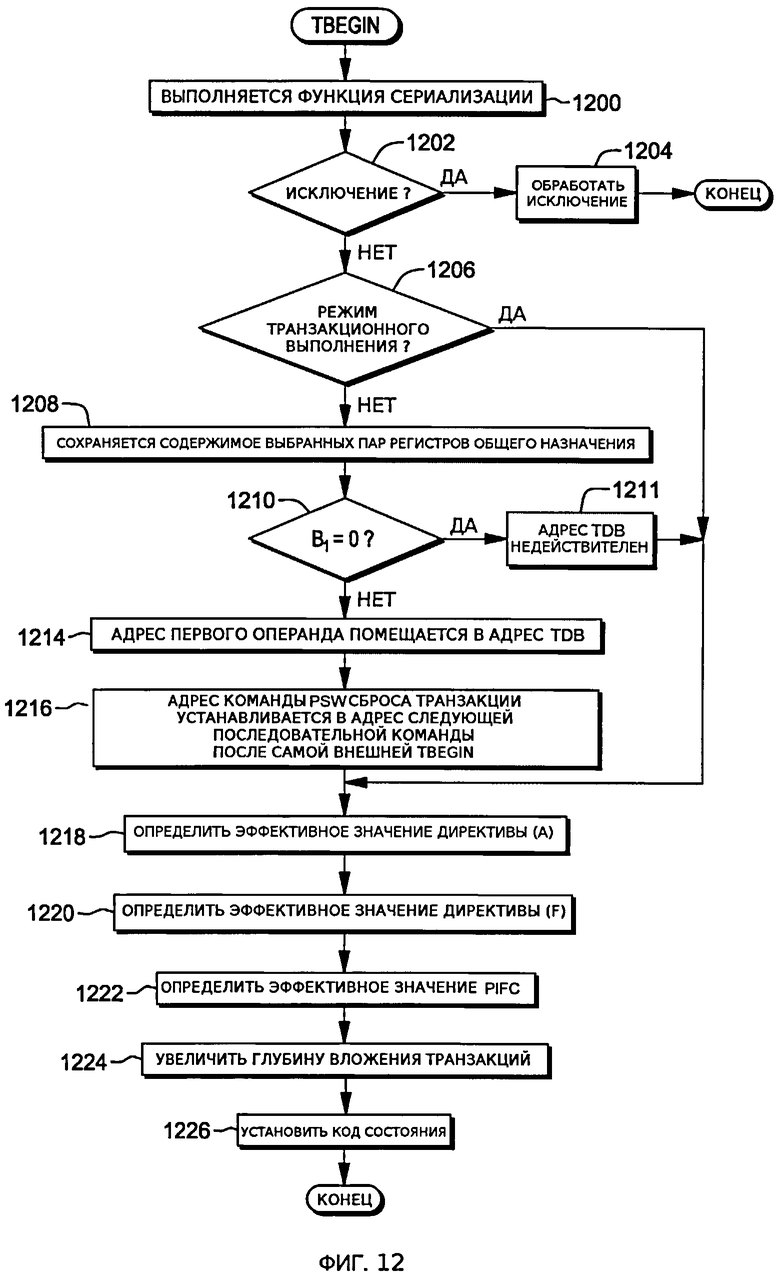

На ФИГ.12 изображен один из вариантов логики, связанной с выполнением команды TBEGIN.

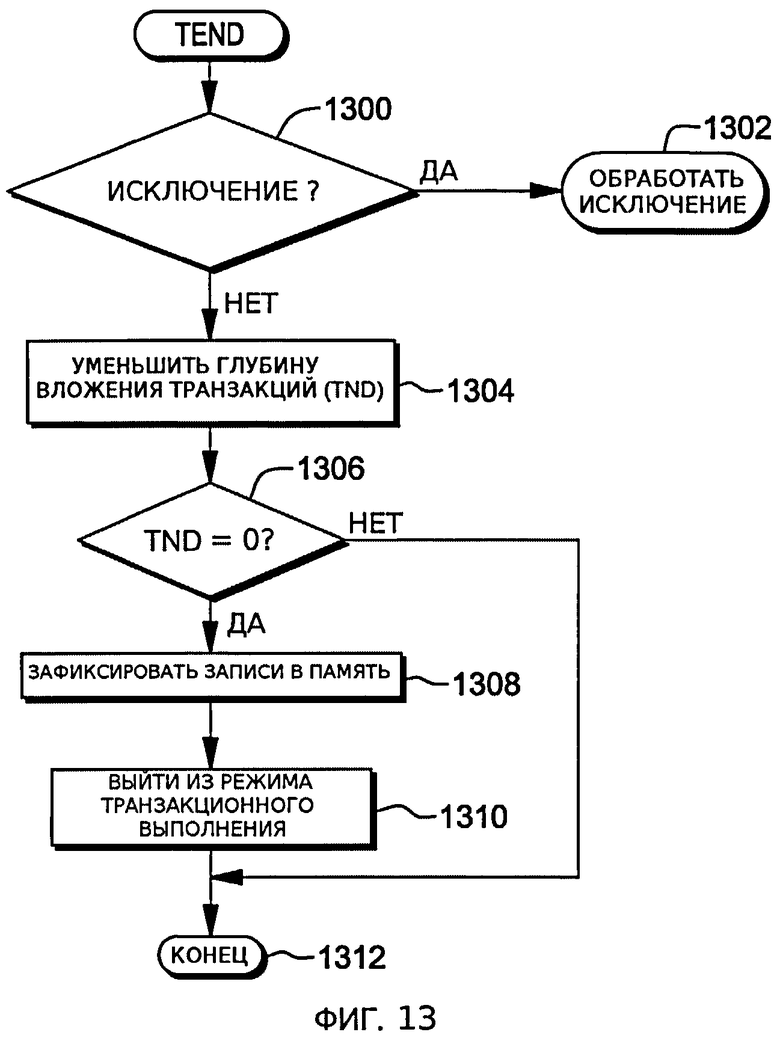

На ФИГ.13 изображен один из вариантов логики, связанной с выполнением команды TEND.

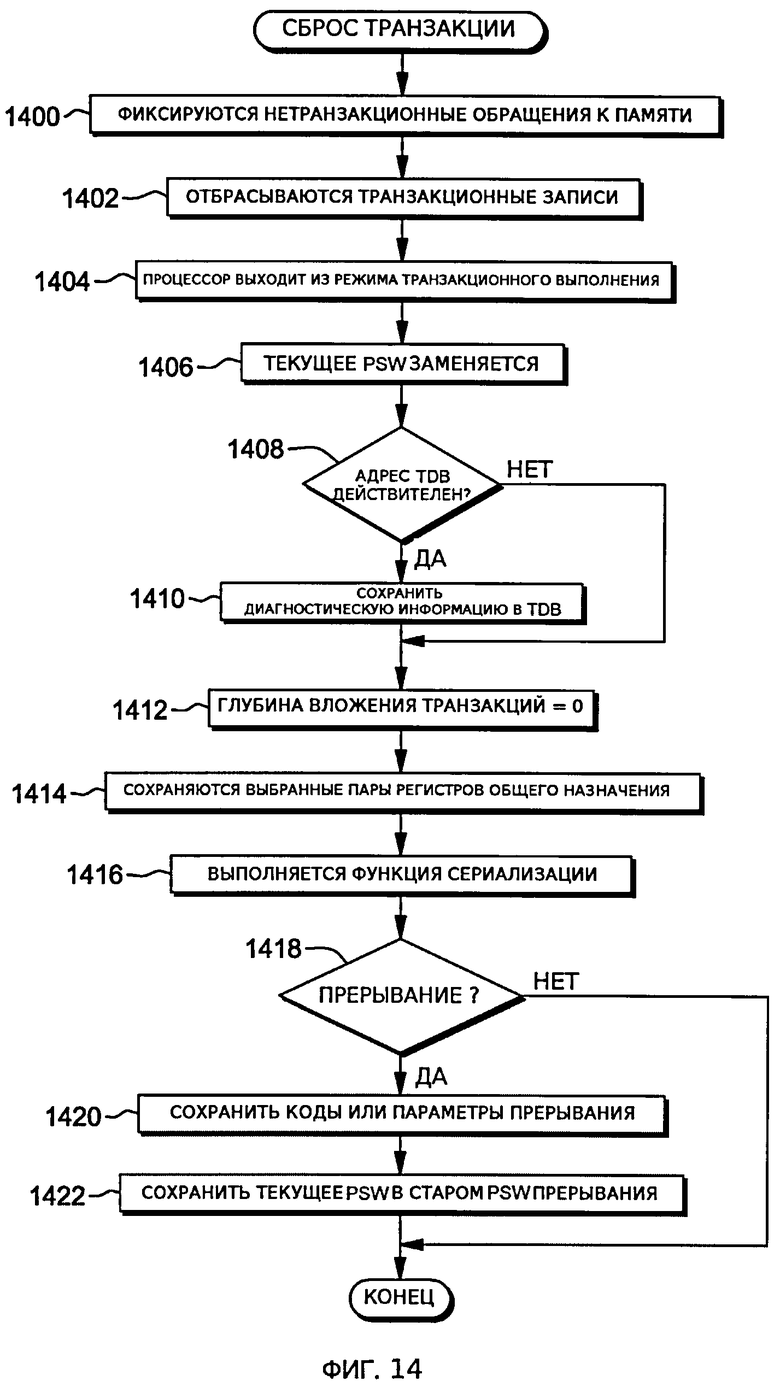

На ФИГ.14 изображен один из вариантов логики, связанной с обработкой сброса транзакции.

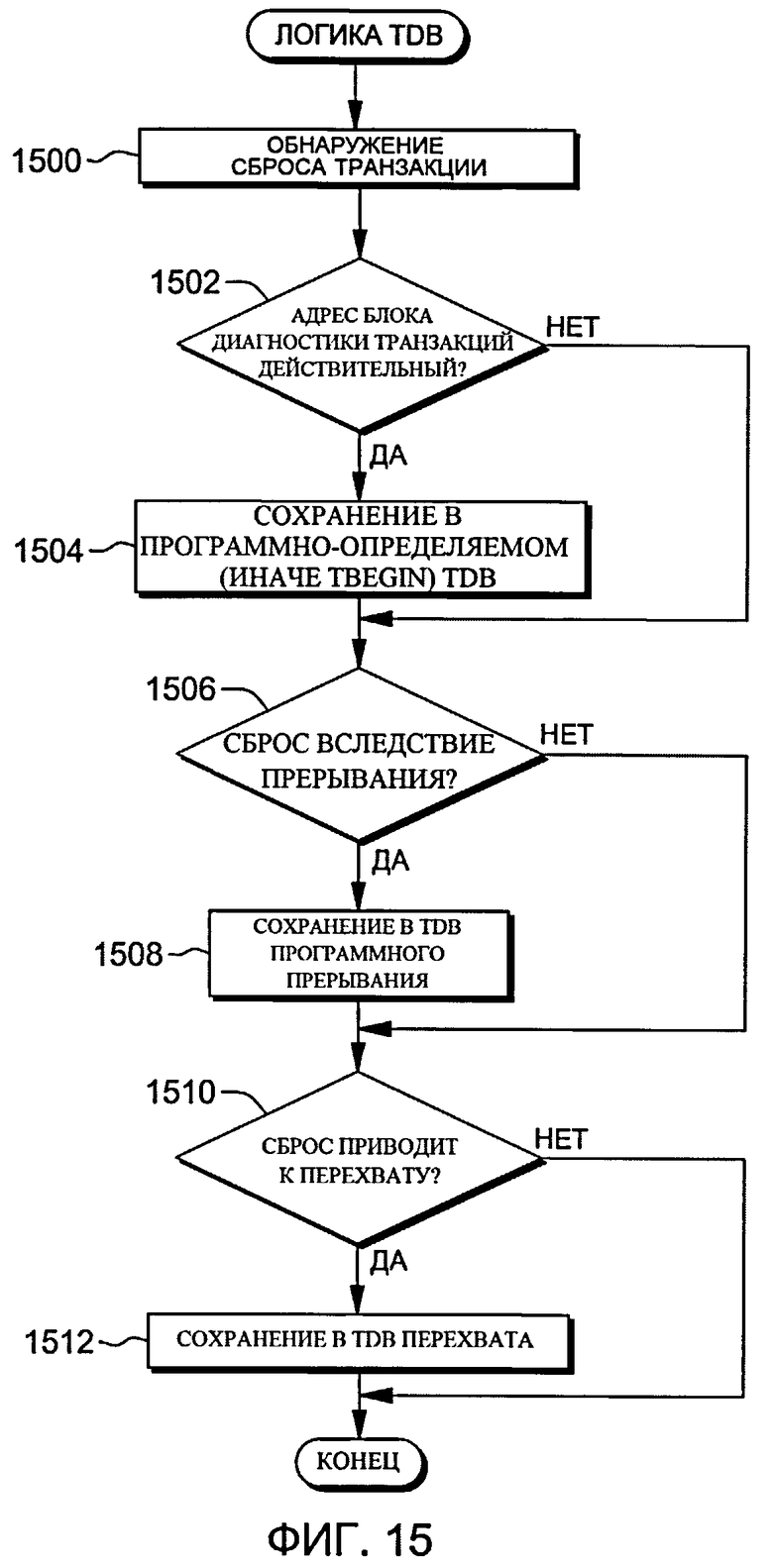

На ФИГ.15 изображен один из вариантов логики, связанной с выборочным сохранением информации в одном или более блоках диагностики транзакций.

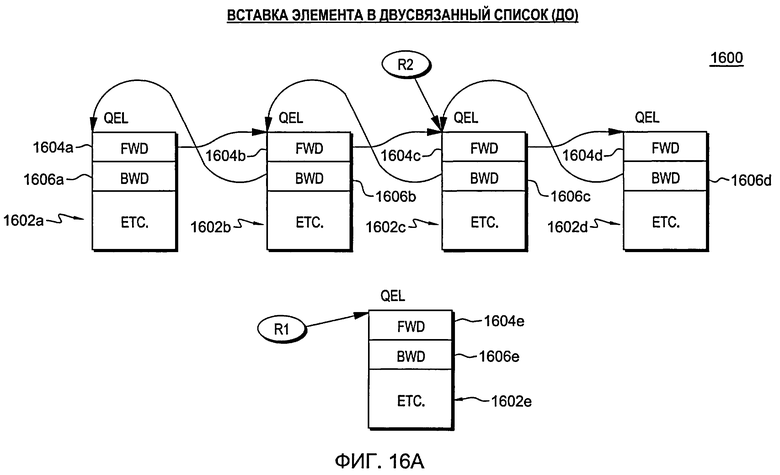

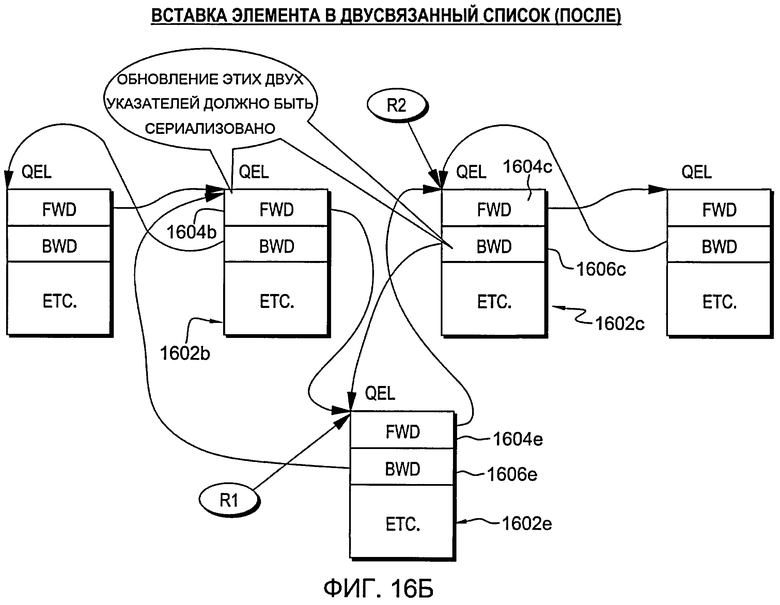

На ФИГ.16А-16Б изображен пример вставки элемента очереди в двусвязанный список элементов очереди.

На ФИГ.17 изображен один из вариантов компьютерного программного продукта.

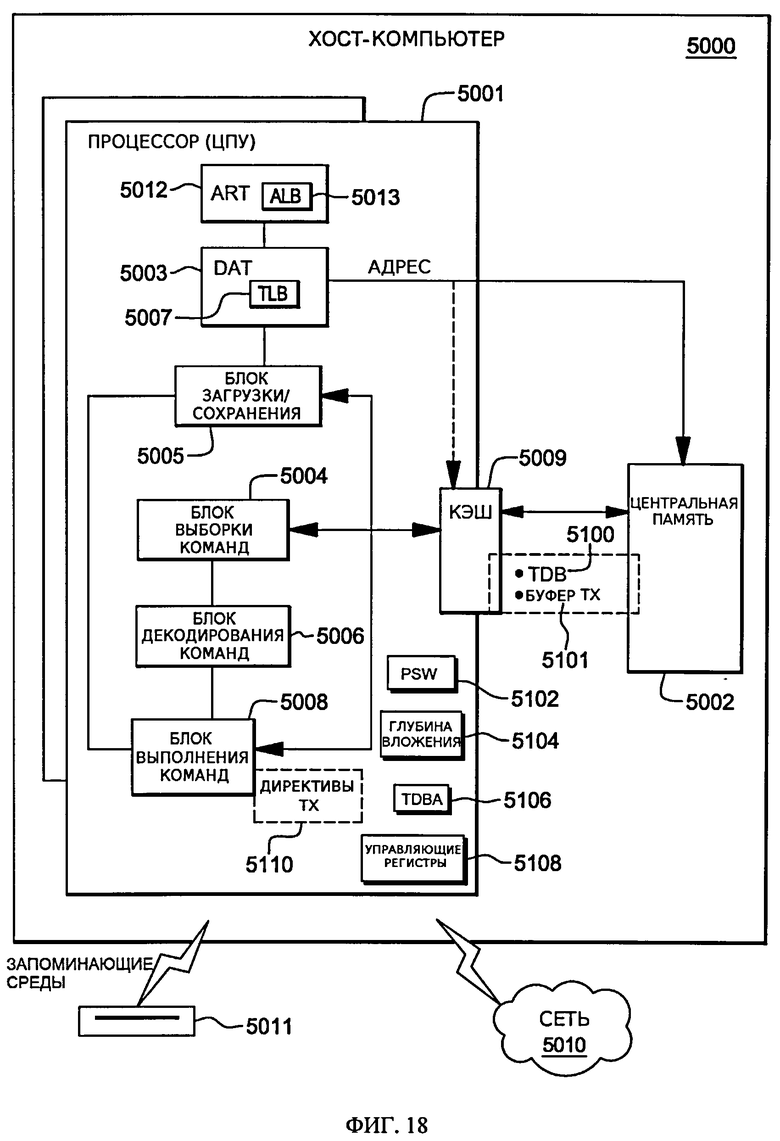

На ФИГ.18 изображен один из вариантов хост-компьютерной системы.

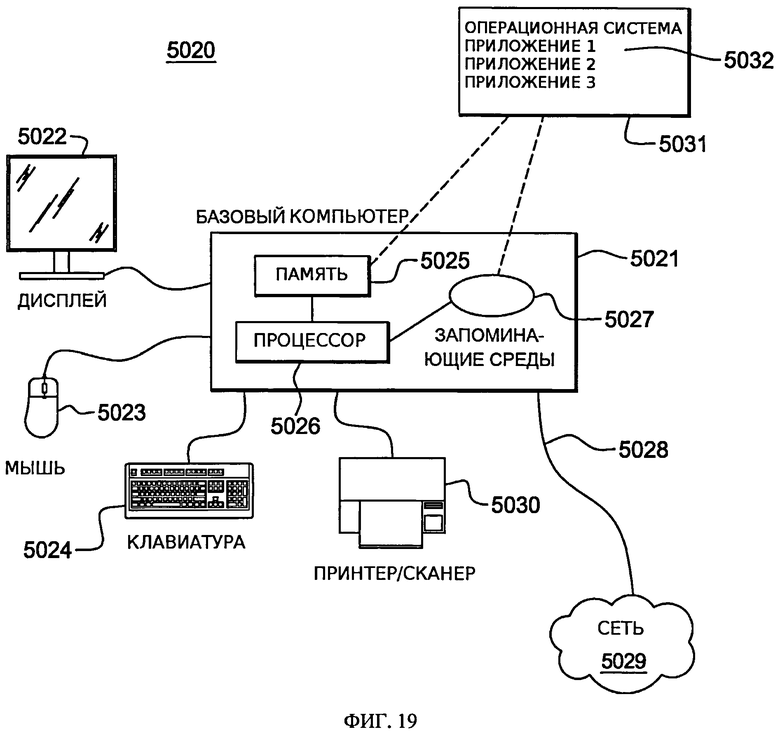

На ФИГ.19 изображен другой пример компьютерной системы.

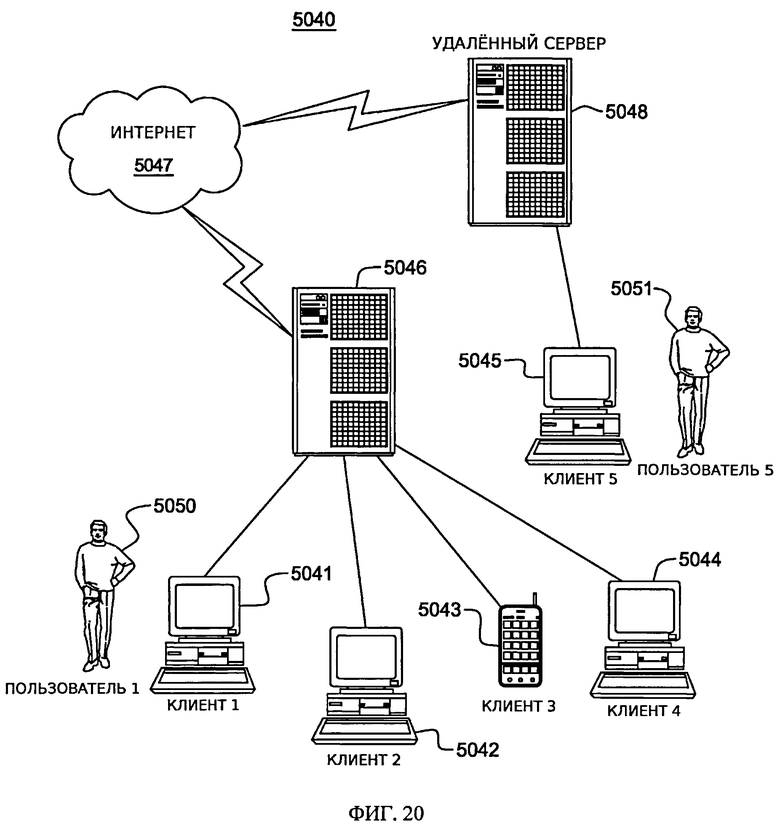

На ФИГ.20 изображен еще один пример компьютерной системы, содержащий компьютерную сеть.

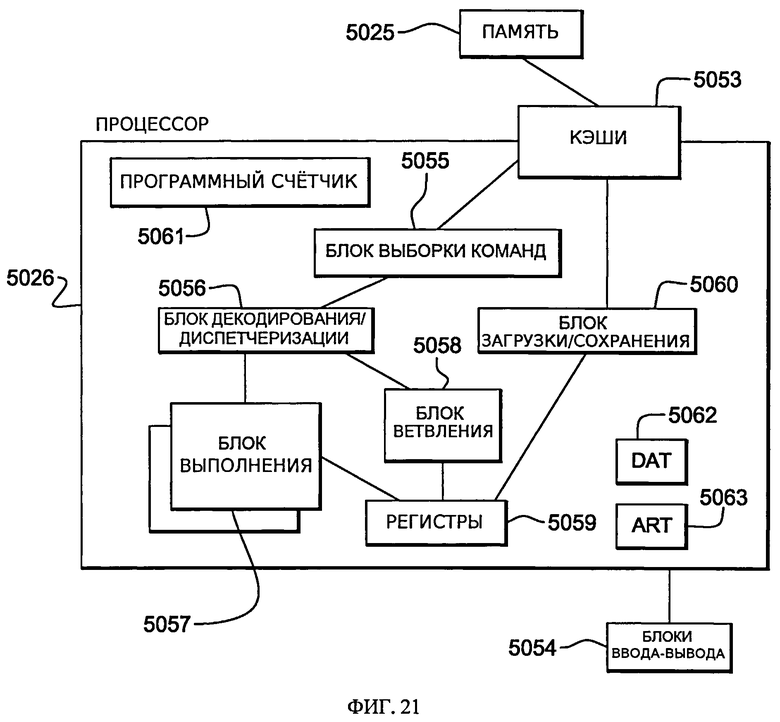

На ФИГ.21 изображен один из вариантов различных элементов компьютерной системы.

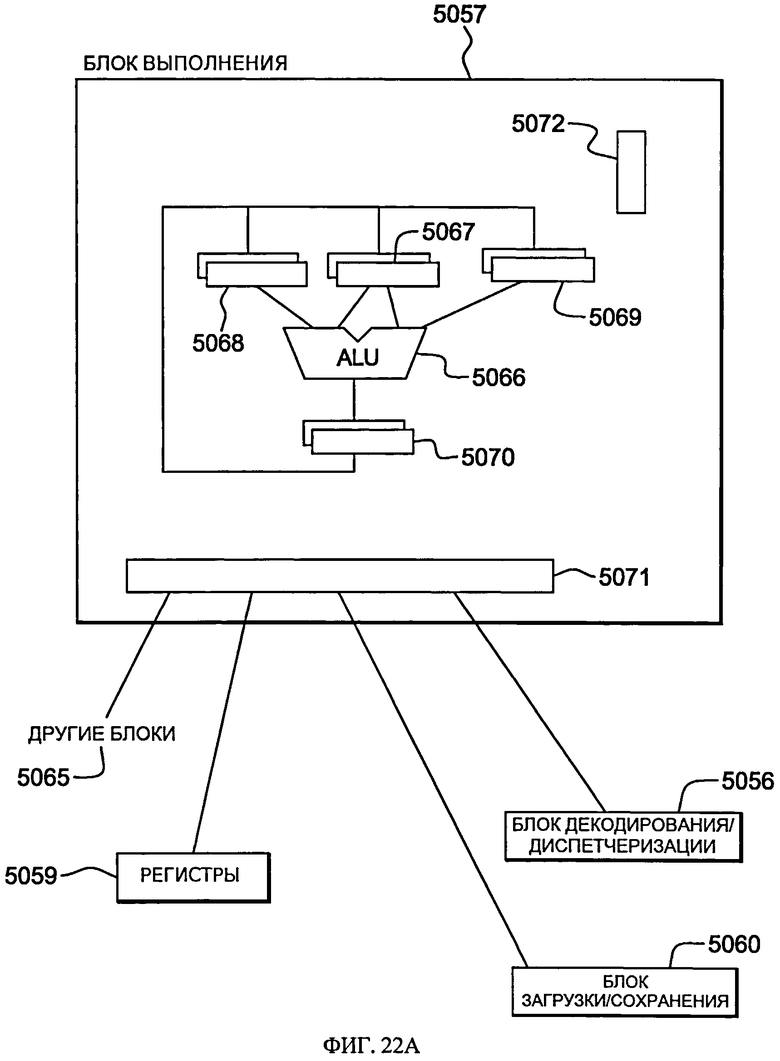

На ФИГ.22А изображен один из вариантов исполнительного устройства компьютерной системы согласно ФИГ.21.

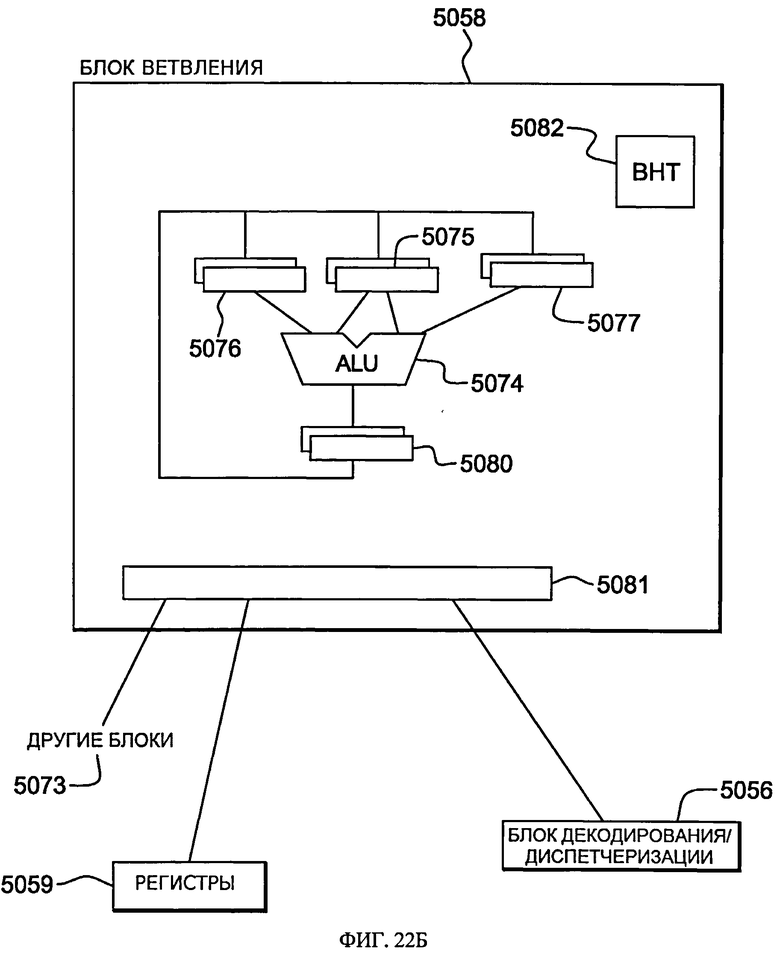

На ФИГ.22Б изображен один из вариантов устройства ветвления компьютерной системы согласно ФИГ.21.

На ФИГ.22В изображен один из вариантов устройства загрузки/сохранения компьютерной системы согласно ФИГ.21.

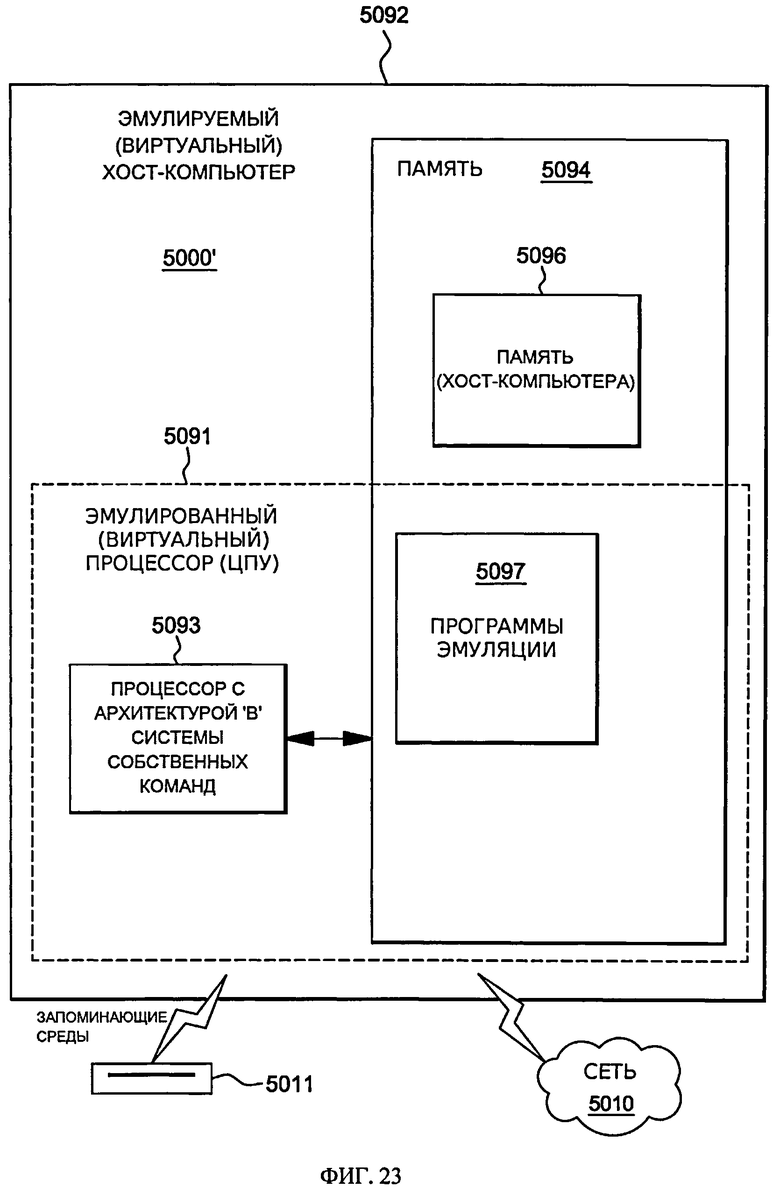

На ФИГ.23 изображен один из вариантов эмулированной хост-компьютерной системы.

ПОДРОБНОЕ ОПИСАНИЕ

[0011] В соответствии с одним аспектом, предоставляется средство транзакционного выполнения (ТХ). Это средство обеспечивает транзакционную обработку команд, и в одном или более вариантов, предоставляет разные режимы выполнения, как описывается ниже, а также вложенные уровни транзакционной обработки.

[0012] Средство транзакционного выполнения вводит состояние процессора, называемое режимом транзакционного выполнения (ТХ). Сразу после перезагрузки процессора, процессор не находится в режиме ТХ. Процессор входит в режим ТХ по команде НАЧАТЬ ТРАНЗАКЦИЮ. Процессор выходит из режима ТХ или (а) по самой внешней команде ЗАКОНЧИТЬ ТРАНЗАКЦИЮ (подробности о внутреннем и внешнем следуют), или (б) если транзакция была сброшена. В режиме ТХ обращения процессора к памяти выглядят блочно-параллельными с точки зрения других процессоров и подсистемы ввода-вывода. Обращения к памяти или (а) фиксируются в памяти, если самая внешняя транзакция заканчивается без сброса (т.е., напр., обновления в кэше или буферах, локальных для процессора, распространяются и сохраняются в реальной памяти и видимы для других процессоров), или (б) отбрасываются, если транзакция сброшена.

[0013] Транзакции могут быть вложенными. То есть, пока процессор находится в режиме ТХ, он может выполнить другую команду НАЧАТЬ ТРАНЗАКЦИЮ. Команда, которая вызывает вход процессора в режим ТХ, называется самой внешней командой НАЧАТЬ ТРАНЗАКЦИЮ; аналогично говорят, что программа находится в самой внешней транзакции. Последующие выполнения команды НАЧАТЬ ТРАНЗАКЦИЮ называются внутренними командами; и программа выполняет внутреннюю транзакцию. Эта модель предусматривает минимальную глубину вложения и зависимую от модели максимальную глубину вложения. Команда ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ возвращает текущее значение глубины вложения, и, в последующем варианте, может возвращать максимальное значение глубины вложения. Эта методика использует модель, называемую "выровненное вложение", в которой состояние сброса при любой глубине вложения вызывает сброс всех уровней транзакции, и управление возвращается к команде, следующей за самой внешней НАЧАТЬ ТРАНЗАКЦИЮ.

[0014] Во время обработки транзакции считается, что транзакционное обращение, выполняемое одним процессором, конфликтует с (а) транзакционным или нетранзакционным обращением, выполняемым другим процессором, и (б) нетранзакционным обращением, выполняемым системой ввода-вывода, если оба обращения находятся в любом месте внутри одной строки кэша, и одно или оба обращения являются сохранением. Другими словами, для того чтобы транзакционное выполнение было продуктивным, не должно быть видно, что процессор совершает транзакционные обращения, пока они не зафиксируются. Эта модель программирования может быть очень эффективна в определенных средах; например, обновление двух точек в двусвязанном списке из миллиона элементов. Однако она может быть менее эффективна, если существует значительная конкуренция за позиции памяти, к которым производится транзакционное обращение.

[0015] В одной модели транзакционного выполнения (называемой здесь невынужденной транзакцией), когда транзакция сбрасывается, программа может или попытаться перезапустить транзакцию в надежде, что состояния сброса больше нет, или программа может "откатиться" на эквивалентный нетранзакционный путь. В другой модели транзакционного выполнения (называемой здесь вынужденной транзакцией), сброшенная транзакция автоматически перезапускается процессором; в отсутствие нарушения ограничений, вынужденная транзакция гарантированно завершается в итоге.

[0016] Инициируя транзакцию, программа может задать различные проверки, такие как: (а) какие регистры общего назначения восстанавливают их изначальное содержимое в случае сброса транзакции, (б) разрешено ли транзакции изменять контекст регистров с плавающей точкой, включая, например, регистры с плавающей точкой и контрольный регистр с плавающей точкой, (в) разрешено ли транзакции изменять регистры доступа (AR), и (г) должны ли некоторые ситуации программного исключения быль блокированы от вызова прерывания. Если невынужденная транзакция сбрасывается, может быть предоставлена различная диагностическая информация. Например, самая внешняя команда TBEGIN, которая запускает невынужденную транзакцию, может задать программно определяемый блок диагностики транзакции (TDB). Далее, TDB в префиксной зоне процессора или заданный описанием состояния хоста, также может использоваться, если транзакция сброшена из-за программного прерывания или состояния, которое вызывает завершение интерпретирующего выполнения, соответственно.

[0017] Выше указаны различные типы регистров. Далее они объясняются подробно. Регистры общего назначения могут использоваться как накопители в общих арифметических и логических операциях. В одном варианте каждый регистр содержит 64 двоичных разряда, и есть 16 регистров общего назначения. Регистры общего назначения идентифицируются по номерам 0-15 и обозначаются в команде четырехбитным полем R. Некоторые команды обеспечивают адресацию к нескольким регистрам общего назначения, имея несколько полей R. Для некоторых команд подразумевается использование особого регистра общего назначения вместо прямого указания в поле R команды.

[0018] Кроме использования в качестве накопителей в общих арифметических и логических операциях, 15 из 16 регистров общего назначения используются также как регистры базового адреса и индексные регистры для формирования адреса. В этих случаях регистры обозначаются в команде четырехбитным полем В или полем X. Нулевое значение в поле В или X означает, что база или индекс не применяется, и таким образом, регистр общего назначения 0 не должен использоваться как содержащий базовый адрес или индекс.

[0019] Команды с плавающей точкой используют ряд регистров с плавающей точкой. Процессор имеет 16 регистров с плавающей точкой, в одном варианте. Регистры с плавающей точкой идентифицируются по номерам 0-15 и обозначаются в командах с плавающей точкой четырехбитным полем R. Каждый регистр с плавающей точкой является 64-битным и может содержать или короткий (32 бит) или длинный (64 бит) операнд с плавающей точкой.

[0020] Регистр управления плавающей точкой (FPC) - 32-битный регистр, который содержит биты маски, бит флага, код исключения данных и биты режима округления, и используется во время обработки операций с плавающей точкой.

[0021] Далее, в одном варианте, процессор имеет 16 управляющих регистров (CR), каждый из которых имеет 64 двоичных разряда. Двоичные разряды в регистрах закреплены за отдельными средствами в системе, такими как Запись Программных Событий (PER) (обсуждается ниже), и используются или для определения, какая операция может происходить, или для предоставления специальной информации, необходимой средству. В одном варианте для транзакционного средства используются CR0 (биты 8 и 9) и CR2 (биты 61-63), как описано ниже.

[0022] Процессор имеет, например, 16 регистров доступа, пронумерованных 0-15. Регистр доступа состоит из 32 двоичных разрядов, содержащих косвенное определение элемента контроля пространства адресов (ASCE). Элемент контроля пространства адресов - параметр, используемый механизмом динамической трансляции адреса (DAT) для перевода ссылок в соответствующее пространство адресов. Когда процессор находится в режиме, называемом режимом регистра доступа (управляющимся битами в слове состояния программы (PSW)), поле В команды, использующееся для определения логического адреса для ссылки в операнде хранения, назначает регистр доступа, а элемент контроля пространства адресов, заданный регистром доступа, используется DAT для данной ссылки. Для некоторых команд используется поле R вместо поля В. Предоставляются команды для загрузки и сохранения содержимого регистров доступа и для перемещения содержимого одного регистра доступа в другой.

[0023] Каждый из регистров доступа 1-15 может определять любое пространство адресов. Регистр доступа 0 определяет первичное пространство команд. Когда один из регистров доступа 1-15 используется для определения пространства адресов, процессор выясняет, которое пространство адресов определяется, переводя содержимое регистра доступа. Когда регистр доступа 0 используется для определения пространства адресов, процессор рассматривает регистр доступа как определяющий первичное пространство команд, и не проверяет действительное содержание регистра доступа. Таким образом, 16 регистров доступа могут определять одновременно первичное пространство команд и максимум 15 других пространств.

[0024] В одном из вариантов существует несколько типов пространств адресов. Пространство адресов - непрерывная последовательность целых чисел (виртуальных адресов), вместе со специфическими параметрами трансляции, позволяющими связать каждое число с расположением байта в памяти. Последовательность начинается с нуля и продолжается слева направо.

[0025] В z/Architecture, например, когда виртуальный адрес используется процессором для обращения к главному запоминающему устройству (оно же главная память), он сперва превращается, с помощью динамической трансляции адреса (DAT), в реальный адрес, а затем, при помощи префиксации, в абсолютный адрес. DAT может использовать от одного до пяти уровней таблиц (страница, сегмент, регион третий, регион второй и регион первый) в качестве параметров трансляции. Определение (происхождение и длина) таблицы наивысшего уровня для отдельного пространства адресов называется элементом контроля пространства адресов, и находится для использования в DAT в управляющем регистре или определено регистром доступа. Иначе, элемент контроля пространства адресов для пространства адресов может быть обозначением реального пространства, которое указывает, что DAT должно транслировать виртуальный адрес, просто рассматривая его как реальный адрес без использования каких-либо таблиц.

[0026] DAT в разное время использует элементы контроля пространства адресов в разных управляющих регистрах или заданные регистрами доступа. Выбор определяется режимом трансляции, заданным в текущем PSW. Доступны четыре режима трансляции: режим первичного пространства, режим вторичного пространства, режим регистра доступа и режим домашнего пространства. Разные пространства адресов адресуются в зависимости от режима трансляции.

[0027] В любой момент, когда процессор находится в режиме первичного пространства или режиме вторичного пространства, процессор может транслировать виртуальные адреса, относящиеся к двум пространствам адресов - первичному пространству адресов и вторичному пространству адресов. В любой момент, когда процессор находится в режиме регистра доступа, он может транслировать виртуальные адреса вплоть до 16 пространств адресов - первичное пространство адресов и вплоть до 15 пространств адресов, заданных AR. В любой момент, когда процессор находится в режиме домашнего пространства, он может транслировать виртуальные адреса домашнего пространства адресов.

[0028] Первичное пространство адресов обозначается так, потому что оно состоит из первичных виртуальных адресов, которые транслируются с помощью первичного элемента контроля пространства адресов (ASCE). Аналогично, вторичное пространство адресов состоит из вторичных виртуальных адресов, транслирующихся с помощью вторичного ASCE; пространства адресов, заданные AR, состоят из виртуальных адресов, заданных AR, транслирующихся при помощи ASCE, заданных AR; и домашнее пространство адресов состоит из домашних виртуальных адресов, транслирующихся при помощи домашнего ASCE. Первичные и вторичные ASCE находятся в управляющих регистрах 1 и 7 соответственно. ASCE, заданные AR, находятся в пунктах второй таблицы НПА, которые находятся с помощью процесса, называемого трансляцией регистра доступа (ART) при помощи управляющего регистра 2,5 и 8. Домашний ASCE находится в управляющем регистре 13.

[0029] Один из вариантов вычислительной среды, включающий и использующий один или более аспектов описываемого здесь транзакционного средства, описывается при помощи ФИГ.1.

[0030] Согласно ФИГ.1, в одном примере, вычислительная среда 100 основывается на архитектуре z/Architecture, предлагаемой корпорацией International Business Machines (IBM®), Армонк, штат Нью-Йорк. z/Architecture описана в публикации IBM, озаглавленной "z/Architecture - Principles of Operation," публикация № SA22-7932-08, 9 издание, август 2010, которая включается сюда по ссылке во всей ее целостности.

[0031] Z/ARCHITECTURE, IBM, Z/OS и Z/VM (упоминаемые ниже) являются зарегистрированными торговыми марками корпорации International Business Machines, Армонк, штат Нью-Йорк. Другие названия, использованные здесь, могут быть зарегистрированными торговыми марками, торговыми марками или названиями изделий корпорации International Business Machines или других компаний.

[0032] В качестве примера, вычислительная среда 100 включает центральный процессорный комплекс (СРС) 102, соединенный с одним или более устройств ввода-вывода 106 через один или более управляющих модулей 108. Центральный процессорный комплекс 102 включает, например, один или более центральных процессоров ПО, один или более разделов 112 (напр., логических разделов (LP)), гипервизор логических разделов 114 и подсистему ввода-вывода 115, каждый из которых описывается ниже.

[0033] Центральные процессоры ПО являются ресурсами физического процессора, выделенные логическим разделам. В частности, каждый логический раздел 112 имеет один или более логических процессоров, каждый из которых представляет собой весь или часть физического процессора ПО, выделенную разделу. Логические процессоры отдельного раздела 112 могут быть или закреплены за разделом, так что лежащий в основе ресурс процессора НО зарезервирован за этим разделом; или разделены с другим разделом, так что лежащий в основе ресурс процессора потенциально доступен для другого раздела.

[0034] Логический раздел функционирует как отдельная система и имеет одно или несколько приложений и, опционально, резидентную операционную систему внутри, которая может отличаться для каждого логического раздела. В одном варианте операционной системой является операционная система z/OS, операционная система z/VM, операционная система z/Linux или операционная система TPF, предлагаемая корпорацией International Business Machines, Армонк, штат Нью-Йорк.

Логические разделы 112 управляются гипервизором 114 логических разделов, который реализуется микропрограммой, выполняющейся на процессорах 110. В данном контексте, микропрограмма включает, напр., микрокод и/или милликод процессора. Она включает, например, команды аппаратного уровня и/или структуры данных, используемые в реализации машинного кода высокого уровня. В одном варианте она включает, например, проприетарный код, который обычно поставляется как микрокод, который включает достоверное программное обеспечение или микрокод, специфичный для нижележащего аппаратного обеспечения, и управляет доступом операционной системы к системному аппаратному обеспечению.

[0035] Каждый из логических разделов и гипервизор логических разделов включают одну или более программ, постоянно находящихся в соответствующих разделах центрального запоминающего устройства, связанного с центральными процессорами. Одним из примеров гипервизора 114 логических разделов является Администратор Системы/Ресурсов Процессора (Processor Resource/System Manager (PR/SM)), предлагаемый корпорацией International Business Machines, Армонк, штат Нью-Йорк.

[0036] Подсистема 115 ввода-вывода направляет поток информации между устройствами 106 ввода-вывода и главным запоминающим устройством (оно же главная память). Она соединяется с центральным процессорным комплексом, в котором она может быть частью центрального процессорного комплекса, или отделена от него. Подсистема ввода-вывода облегчает центральным процессорам задачу прямой связи с устройствами ввода-вывода и позволяет производить обработку данных параллельно с обработкой ввода-вывода. Для обеспечения связи подсистема ввода-вывода использует адаптеры связи ввода-вывода. Существуют различные типы адаптеров связи, включая, например, каналы, адаптеры ввода-вывода, платы PCI, платы Ethernet, платы Интерфейса Малого Компьютерного Хранилища (SCSI) и т.д. В отдельном примере, описанном здесь, адаптерами связи ввода-вывода являются каналы, и, таким образом, подсистема ввода-вывода называется здесь канальной подсистемой. Однако это лишь один из примеров. Могут использоваться другие типы подсистем ввода-вывода.

[0037] Подсистема ввода-вывода использует один или более путей ввода-вывода в качестве линий связи, управляя потоком информации к устройствам 106 или от них. В этом отдельном примере эти пути называются канальными путями, так как адаптеры связи являются каналами.

[0038] Вычислительная среда, описанная выше, является лишь одним примером вычислительной среды, которая может использоваться. Могут использоваться другие среды, включая, но не ограничиваясь, неразделенные среды, другие разделенные среды и/или эмулированные среды; варианты не ограничиваются любой одной средой.

[0039] В соответствии с одним или более аспектами, средство транзакционного выполнения является усовершенствованием процессора, которое предоставляет средства, с помощью которых процессор может выполнить последовательность команд (известную как транзакция), которая может обращаться ко многим ячейкам памяти, включая обновление этих ячеек. С точки зрения других процессоров и подсистемы ввода-вывода, транзакция или (а) завершается во всей целостности как единичная атомарная операция, или (б) сбрасывается, потенциально не оставляя никаких свидетельств того, что она вообще выполнялась (за исключением некоторых ситуаций, описанных здесь). Таким образом, успешно завершенная транзакция может обновить множество ячеек памяти без какой-либо особой блокировки, которая нужна в классической многопроцессорной модели.

[0040] Средство транзакционного выполнения включает, например, одну или более директив; одну или более команд; обработку транзакций, включая вынужденное и невынужденное выполнение; и обработку сброса, каждая из которых далее описывается ниже.

[0041] В одном варианте воплощения изобретения, для управления средством транзакционного выполнения используются три директивы специального назначения, включая Слово Состояния Программы (PSW) сброса транзакции, адрес блока диагностики транзакций (TDB) и глубину вложения транзакций; пять бит управляющего регистра; и шесть общих команд, включая НАЧАТЬ ТРАНЗАКЦИЮ (вынужденную и невынужденную), ЗАКОНЧИТЬ ТРАНЗАКЦИЮ, ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ и НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ. Когда средство инсталлируется, оно инсталлируется, например, на все процессоры в конфигурации. Обозначение средства, бит 73 в одной реализации, будучи единицей, указывает, что установлено средство транзакционного выполнения.

[0042] Когда установлено средство транзакционного выполнения, конфигурация предоставляет средство невынужденного транзакционного выполнения и, опционально, средство вынужденного транзакционного выполнения, каждое из которых описывается ниже. Если обозначения средства 50 и 73, к примеру, оба равны единице, установлено средство вынужденного транзакционного выполнения. Оба обозначения средства хранятся в памяти в определенных позициях.

[0043] В данном контексте название команды НАЧАТЬ ТРАНЗАКЦИЮ относится к командам с сокращениями TBEGIN (Начать Транзакцию для невынужденной транзакции) и TBEGINC (Начать Транзакцию для вынужденной транзакции). Рассуждения, касающиеся специфических команд, обозначаются названием команды с последующим сокращением в скобках, или только сокращением.

[0044] Один из вариантов формата команды НАЧАТЬ ТРАНЗАКЦИЮ (TBEGIN) изображен на ФИГ.2А-2Б. К примеру, команда TBEGIN 200 включает поле кода операции 202, которое включает код операции, определяющий невынужденную операцию начала транзакции; базовое поле (B1) 204; поле смещения (D1) 206; и непосредственное поле (I2) 208. Если поле B1 не нуль, содержимое регистра общего назначения, определенного B1 204, складывается с D1 206 для получения адреса первого операнда.

[0045] Если поле B1 не нуль, применяется следующее:

[0046] * Если глубина вложения транзакции изначально нуль, адрес первого операнда определяет положение 256-байтного блока диагностики транзакций, называемого TDB, заданный TBEGIN (далее описан ниже), в котором может сохраняться различная диагностическая информация, если транзакция сбрасывается. Если процессор находится в режиме первичного пространства или в режиме регистра доступа, адрес первого операнда определяет позицию в первичном пространстве адресов. Если процессор находится в режиме вторичного пространства или в режиме домашнего пространства, адрес первого операнда определяет позицию во вторичном или домашнем пространстве адресов соответственно. Если DAT выключено, адрес блока диагностики транзакций (TDBA) определяет позицию в реальном запоминающем устройстве.

[0047] Определяется доступность памяти для первого операнда. Если доступно, логический адрес операнда помещается в адрес блока диагностики транзакций (TDBA), и TDBA действителен.

[0048] * Если процессор уже находится в режиме невынужденного транзакционного выполнения, TDBA не изменяется, и нельзя предсказать, проверен ли первый операнд на доступность.

[0049] Если поле B1 равно нулю, не обнаруживаются исключения доступа для первого операнда и, для самой внешней команды TBEGIN, TDBA недействителен.

[0050] Биты поля I2 определяются следующим образом, к примеру:

[0051] Маска Сохранения Регистров Общего Назначения (General Register Save Mask) (GRSM) 210 (ФИГ.2Б): Биты 0-7 поля I2 содержат маску сохранения регистров общего назначения (GRSM). Каждый бит GRSM представляет четно-нечетную пару регистров общего назначения, где бит 0 представляет регистры 0 и 1, бит 1 представляет регистры 2 и 3 и так далее. Если бит в GRSM самой внешней команды TBEGIN равен нулю, соответствующая пара регистров не сохраняется. Если бит в GRSM самой внешней команды TBEGIN равен единице, соответствующая пара регистров сохраняется в зависящем от модели месте, которое недоступно программе напрямую.

[0052] Если транзакция сбрасывается, сохраненные пары регистров восстанавливают свое содержимое на момент, когда выполнялась самая внешняя команда TBEGIN. Содержимое всех других (несохраненных) регистров общего назначения не восстанавливается, если транзакция сбрасывается.

[0053] Маска сохранения регистров общего назначения игнорируется всеми TBEGIN, за исключением самой внешней.

[0054] Разрешить Изменение AR (Allow AR Modification) (А) 212: Директива А, бит 12 поля I2, контролирует, разрешено ли транзакции изменять регистр доступа. Эффективная директива разрешения изменения AR является логическим И (AND) директивы А в команде TBEGIN для текущего уровня вложения и для всех внешних уровней.

[0055] Если эффективная директива А равна нулю, транзакция будет сброшена с кодом сброса 11 (недопустимая команда), если будет сделана попытка изменить любой регистр доступа. Если эффективная директива А равна единице, транзакция не будет сброшена, если регистр доступа будет изменен (в отсутствие любых других причин сброса).

[0056] Разрешить Операцию с Плавающей Точкой (Allow Floating Point Operation) (F) 214: Директива F, бит 13 поля I2, контролирует, разрешено ли транзакции выполнять определенные команды с плавающей точкой. Эффективная директива разрешения операции с плавающей точкой является логическим И (AND) директивы F в команде TBEGIN для текущего уровня вложения и для всех внешних уровней.

[0057] Если эффективная директива F равна нулю, то (а) транзакция будет сброшена с кодом сброса 11 (недопустимая команда), если будет сделана попытка выполнить команду с плавающей точкой, и (б) код исключения данных (DXC) в байте 2 управляющего регистра с плавающей точкой (FPCR) не будет установлен никаким состоянием исключения программы исключения данных. Если эффективная директива F равна единице, то (а) транзакция не будет сброшена, если будет сделана попытка выполнить команду с плавающей точкой (в отсутствие любых других причин сброса), и (б) DXC в FPCR может быть установлен состоянием исключения программы исключения данных.

[0058] Директива Фильтрации Программного Прерывания (Program Interruption Filtering Control) (PIFC) 216: Биты 14-15 поля Ь являются директивой фильтрации программного прерывания (PIFC). PIFC контролирует, вызывают ли прерывание некоторые классы ситуаций программного исключения (напр., исключение адресации, исключение данных, исключение операций, исключение защиты и т.д.), которые происходят, пока процессор находится в режимы транзакционного выполнения.

[0059] Эффективная PIFC является наивысшей величиной PIFC в команде TBEGIN для текущего уровня вложения и для всех внешних уровней. Если эффективная PIFC равна нулю, все ситуации программного исключения вызывают прерывание. Если эффективная PIFC равна единице, ситуации программного исключения, имеющие класс транзакционного выполнения 1 и 2, вызывают прерывание. (Каждой ситуации программного прерывания назначен как минимум один класс транзакционного выполнения, зависящий от серьезности исключения. Важность основывается на вероятности восстановления во время повторного выполнения транзакции, и нужно ли операционной системе видеть прерывание). Если эффективная PIFC равна двум, ситуации программного исключения, имеющие класс транзакционного выполнения 1, вызывают прерывание. PIFC, равный 3, зарезервирован.

[0060] Биты 8-11 поля I2 (биты 40-43 команды) зарезервированы и должны содержать нули; иначе, программа не сможет совместимо работать в будущем.

[0061] Один из вариантов формата инструкции НАЧАТЬ ТРАНЗАКЦИЮ ВЫНУЖДЕННО (TBEGINC) описан при помощи ФИГ.3А-3Б. В одном примере команда TBEGINC 300 включает поле кода операции 302, которое включает код операции, определяющий вынужденную операцию начала транзакции; базовое поле (В1) 304; поле смещения (D1) 306; и непосредственное поле (I2) 308. Содержимое регистра общего назначения, определенного B1 304 складывается с D1 306 для получения адреса первого операнда. Однако при команде вынужденного начала транзакции адрес первого операнда не используется для обращения к памяти. Вместо этого поле B1 команды включает нули; иначе обнаруживается исключение определения.

[0062] В одном из вариантов поле I2 включает различные директивы, пример которых изображен на ФИГ.3Б.

[0063] Биты поля I2 определяются следующим образом, к примеру:

[0064] Маска Сохранения Регистров Общего Назначения (GRSM) 310: Биты 0-7 поля I2 содержат маску сохранения регистров общего назначения (GRSM). Каждый бит GRSM представляет четно-нечетную пару регистров общего назначения, где бит 0 представляет регистры 0 и 1, бит 1 представляет регистры 2 и 3 и так далее. Если бит в GRSM равен нулю, соответствующая пара регистров не сохраняется. Если бит в GRSM равен единице, соответствующая пара регистров сохраняется в зависящем от модели месте, которое недоступно программе напрямую.

[0065] Если транзакция сбрасывается, сохраненные пары регистров восстанавливают свое содержимое на момент, когда выполнялась самая внешняя команда НАЧАТЬ ТРАНЗАКЦИЮ. Содержимое всех других (несохраненных) регистров общего назначения не восстанавливается, если вынужденная транзакция сбрасывается.

[0066] Если TBEGINC используется для продолжения выполнения в режиме выполнения невынужденной транзакции, маска сохранения регистров общего назначения игнорируется.

[0067] Разрешить Изменение AR (А) 312: Директива А, бит 12 поля I2, контролирует, разрешено ли транзакции изменять регистр доступа. Эффективная директива разрешения изменения AR является логическим И (AND) директивы А в команде TBEGINC для текущего уровня вложения и для любых внешних команд TBEGIN или TBEGINC.

[0068] Если эффективная директива А равна нулю, транзакция будет сброшена с кодом сброса 11 (недопустимая команда), если будет сделана попытка изменить любой регистр доступа. Если эффективная директива А равна единице, транзакция не будет сброшена, если регистр доступа будет изменен (в отсутствие любых других причин сброса).

[0069] Биты 8-11 и 13-15 поля I2 (биты 40-43 и 45-47 команды) зарезервированы и должны содержать нули.

[0070] Окончание команды НАЧАТЬ ТРАНЗАКЦИЮ задается командой ЗАКОНЧИТЬ ТРАНЗАКЦИЮ (TEND), формат которой изображен на ФИГ.4. К примеру, команда TEND 400 включает поле кода операции 402, которое включает код операции, определяющий операцию конца транзакции.

[0071] Касательно средства транзакционного выполнения используется ряд терминов, и поэтому, только для удобства, ниже приводится список терминов в алфавитном порядке. В одном из вариантов эти термины имеют следующие определения:

[0072] Сброс (Abort): Транзакция сбрасывается, если она заканчивается ранее команды ЗАКОНЧИТЬ ТРАНЗАКЦИЮ, которая приводит к нулевой глубине вложения транзакций. Когда транзакция сбрасывается, происходит следующее, в одном из вариантов:

[0073] * Транзакционные обращения к памяти, совершенные любым и всеми уровнями транзакции, отбрасываются (то есть, не фиксируются).

[0074] * Нетранзакционные обращения к памяти, совершенные любым и всеми уровнями транзакции, фиксируются.

[0075] * Регистры, определенные маской сохранения регистров общего назначения (GRSM) самой внешней команды НАЧАТЬ ТРАНЗАКЦИЮ, восстанавливают их содержимое на момент до выполнения транзакции (то есть, содержимое при выполнении самой внешней команды НАЧАТЬ ТРАНЗАКЦИЮ). Регистры общего назначения, не определенные маской сохранения регистров общего назначения (GRSM) самой внешней команды НАЧАТЬ ТРАНЗАКЦИЮ, не восстанавливаются.

[0076] * Регистры доступа, регистры с плавающей точкой и управляющий регистр с плавающей точкой не восстанавливаются. Любые изменения, внесенные в эти регистры во время выполнения транзакции, остаются при сбросе транзакции.

[0077] Транзакция может быть сброшена из-за множества причин, включая попытку выполнения недопустимой команды, попытку изменения недопустимого ресурса, конфликт транзакций, превышение различных ресурсов процессора, любую ситуацию прерывания интерпретационного выполнения, любое прерывание, команду СБРОСИТЬ ТРАНЗАКЦИЮ и другие причины. Код сброса транзакции предоставляет конкретные причины, почему транзакция может быть сброшена.

[0078] Один из примеров формата команды СБРОСИТЬ ТРАНЗАКЦИЮ (TABORT) описан при помощи ФИГ.5. К примеру, команда TABORT 500 включает поле кода операции 502, которое включает код операции, определяющий операцию сброса транзакции; базовое поле (В2) 504; и поле смещения (D2) 506. Если поле В2 не нуль, содержимое регистра общего назначения, определенного В2 504, складывается с D2 506 для получения адреса второго операнда; иначе адрес второго операнда создается только из поля D2, а поле В2 игнорируется. Адрес второго операнда не используется для адресации данных; вместо этого адрес создает код сброса транзакции, который помещается в блок диагностики транзакции во время обработки сброса. Вычисление адреса для адреса второго операнда следует правилам адресной арифметики: в режиме 24-битной адресации биты 0-29 устанавливаются в нуль; в режиме 31-битной адресации биты 0-32 устанавливаются в нуль.

[0079] Фиксация (Commit): При завершении самой внешней команды ЗАКОНЧИТЬ ТРАНЗАКЦИЮ, процессор фиксирует обращения к памяти, совершенные транзакцией (т.е., самой внешней транзакцией и любыми вложенными уровнями), так что они становятся видимы другим процессорам и подсистеме ввода-вывода. С точки зрения других процессоров и подсистемы ввода-вывода, все обращения считывания и записи, совершенные всеми вложенными уровнями транзакции, выглядят как происходящие как единичная параллельная операция при осуществлении фиксации.

[0080] Содержимое регистров общего назначения, регистров доступа, регистров с плавающей точкой и управляющего регистра с плавающей точкой не изменяется в процессе фиксации. Любые изменения, внесенные в эти регистры во время выполнения транзакции, остаются при фиксации сохранений транзакции.

[0081] Конфликт (Conflict): Транзакционное обращение, выполняемое одним процессором, конфликтует или (а) с транзакционным или нетранзакционным обращением, выполняемым другим процессором, или (б) с нетранзакционным обращением, выполняемым системой ввода-вывода, если оба обращения находятся в любом месте внутри одной строки кэша, и одно или оба обращения являются сохранением.

[0082] Конфликт может быть обнаружен при упреждающем выполнении команд процессором, даже если конфликт не может быть обнаружен в концептуальной последовательности.

[0083] Вынужденная Транзакция (Constrained Transaction): Вынужденная транзакция является транзакцией, которая выполняется в режиме вынужденного транзакционного выполнения и подвержена следующим ограничениям:

[0084] * Доступно лишь подмножество основных команд.

[0085] * Может выполняться ограниченное число команд.

[0086] * Может быть доступно ограниченное число мест хранения операнда.

[0087] * Транзакция ограничена единственным уровнем вложения.

[0088] В отсутствие повторяющихся прерываний или конфликтов с другими процессорами и подсистемой ввода-вывода вынужденная транзакция в итоге завершается, таким образом, не требуется подпрограмма-обработчик сброса. Вынужденные транзакции подробно описываются ниже.

[0089] Если инструкция НАЧАТЬ ТРАНЗАКЦИЮ вынужденно (TBEGINC) выполняется, когда процессор уже находится в режиме невынужденного транзакционного выполнения, выполнение продолжается как вложенная невынужденная транзакция.

[0090] Режим Вынужденного Транзакционного Выполнения (Constrained Transactional Execution Mode): Если глубина вложения транзакций равна нулю, а транзакция запускается командой TBEGINC, процессор входит в режим вынужденного транзакционного выполнения. Пока процессор находится в режиме вынужденного транзакционного выполнения, глубина вложения транзакций равна единице.

[0091] Вложенная Транзакция (Nested Transaction): Если команда НАЧАТЬ ТРАНЗАКЦИЮ поступает, когда процессор находится в режиме невынужденного транзакционного выполнения, транзакция становится вложенной.

[0092] Средство транзакционного выполнения использует модель, называемую выровненным вложением. В режиме выровненного вложения сохранения, произведенные внутренней транзакцией, невидимы для других процессоров и подсистемы ввода-вывода, пока самая внешняя транзакция не зафиксирует эти сохранения. Аналогично, если транзакция сбрасывается, все вложенные транзакции сбрасываются, и все транзакционные сохранения всех вложенных транзакций отбрасываются.

[0093] Один из примеров вложенных транзакций изображен на ФИГ.6. Как видно, первая команда TBEGIN 600 начинает самую внешнюю транзакцию 601, TBEGIN 602 начинает первую вложенную транзакцию, a TBEGIN 604 начинает вторую вложенную транзакцию. В этом примере TBEGIN 604 и TEND 606 определяют самую внутреннюю транзакцию 608. Когда выполняется TEND 610, фиксируются транзакционные сохранения 612 для самой внешней транзакции и всех внутренних транзакций.

[0094] Невынужденная Транзакция (Nonconstrained Transaction): Невынужденная транзакция является транзакцией, которая выполняется в режиме невынужденного транзакционного выполнения. Хотя невынужденная транзакция не ограничена наподобие вынужденной транзакции, она все еще может быть сброшена из-за множества причин.

[0095] Режим Невынужденного Транзакционного Выполнения (Nonconstrained Transactional Execution Mode): Если транзакция запускается командой TBEGIN, процессор входит в режим невынужденного транзакционного выполнения. Пока процессор находится в режиме невынужденного транзакционного выполнения, глубина вложения транзакций может изменяться от единицы до максимальной глубины вложения транзакций.

[0096] Нетранзакционное Обращение (Non-Transactional Access): Нетранзакционные обращения являются обращениями к операндам памяти, совершаемые процессором, не находящимся в режиме транзакционного выполнения, (то есть, классические обращения к памяти вне транзакции). Далее, обращения, совершаемые подсистемой ввода-вывода, являются нетранзакционными обращениями. Кроме того, команда НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ может использоваться для вызова нетранзакционного обращения к памяти, когда процессор находится в режиме невынужденного транзакционного выполнения.

[0097] Один из вариантов формата команды НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ описан при помощи ФИГ.7. К примеру, команда НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ 700 включает множество полей кода операции 702a, 702b, определяющих код операции, который задает нетранзакционную операцию с памятью: поле регистра (R1) 704, определяющее регистр, содержимое которого называется первым операндом; индексное поле (X2) 706; базовое поле (B2) 708; первое поле смещения (DL2) 710 и второе поле смещения (DH2) 712. Содержимое регистра общего назначения, определенного полями X2 и B2, складывается с результатом конкатенации содержимого полей DH2 и DL2 для образования адреса второго операнда. Если одно или оба поля X2 или B2 равны нулю, соответствующий регистр не принимает участия в сложении.

[0098] Первый 64-битный операнд нетранзакционно помещается без изменений на место второго операнда.

[0099] Смещение, полученное конкатенацией полей DH2 и DL2, обрабатывается как двоичное целое 20-разрядное число со знаком.

[00100] Второй операнд должен быть выровнен по границе двойного слова; иначе обнаруживается исключение определения, и операция подавляется.

[00101] Внешняя/Самая Внешняя Транзакция (Outer/Outermost Transaction): Транзакция с низшей величиной глубины вложения транзакций является внешней транзакцией. Транзакция с величиной глубины вложения транзакций, равной единице, является самой внешней транзакцией.

[00102] Самая внешняя НАЧАТЬ ТРАНЗАКЦИЮ является командой, которая выполняется, когда глубина вложения транзакций изначально равна нулю. Самая внешняя ЗАКОНЧИТЬ ТРАНЗАКЦИЮ является командой, которая вызывает переход глубины вложения транзакций от единицы к нулю. Вынужденная транзакция является самой внешней транзакцией в этом варианте.

[00103] Фильтрация Программного Прерывания (Program Interruption Filtering): Если транзакция сбрасывается из-за некоторых условий программного исключения, программа опционально может предотвращать вызов прерывания. Эта методика называется фильтрацией программного прерывания. Фильтрация программного прерывания управляется транзакционным классом прерывания, эффективной директивой программного прерывания из команды НАЧАТЬ ТРАНЗАКЦИЮ и переопределением фильтрации программного прерывания транзакционного выполнения в управляющем регистре 0.

[00104] Транзакция (Transaction): Транзакция включает обращения к операндам памяти и изменения выбранных регистров общего назначения, совершенные, когда процессор находится в режиме транзакционного выполнения. Для невынужденной транзакции обращения к операндам памяти могут включать как транзакционные обращения, так и нетранзакционные обращения. Для вынужденной транзакции обращения к операндам памяти ограничены транзакционными обращениями. С точки зрения других процессоров и подсистемы ввода-вывода, все обращения к операндам памяти, совершенные процессором в режиме транзакционного выполнения, выглядят как происходящие как единичная параллельная операция. Если транзакция сбрасывается, транзакционные обращения к памяти отбрасываются, а любые регистры, заданные маской сохранения регистров общего назначения (МСРОТ) самой внешней команды НАЧАТЬ ТРАНЗАКЦИЮ, восстанавливают содержимое на момент до выполнения транзакции.

[00105] Транзакционные Обращения (Transactional Accesses): Транзакционные обращения являются обращениями к операндам памяти, совершаемые, когда процессор находится в режиме транзакционного выполнения, за исключением обращений, совершенных командой НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ.

[00106] Режим Транзакционного Выполнения (Transactional Execution Mode): Термин "режим транзакционного выполнения" (он же режим выполнения транзакций) описывает общее функционирование обоих режимов невынужденного и вынужденного транзакционного выполнения. Поэтому при описании функционирования используются термины "невынужденный" и "вынужденный" для обозначения режима транзакционного выполнения.

[00107] Если глубина вложения транзакций равна нулю, процессор не находится в режиме транзакционного выполнения (эта ситуация называется также режимом нетранзакционного выполнения).

[00108] С точки зрения процессора, считывание и запись, совершенные в режиме транзакционного выполнения, не отличаются от совершенных не в режиме транзакционного выполнения.

[00109] В одном из вариантов z/Architecture средство транзакционного выполнения находится под управлением битов 8-9 управляющего регистра 0, битов 61-63 управляющего регистра 2, глубины вложения транзакций, адреса блока диагностики транзакций и слова состояния программы (PSW) сброса транзакции.

[00110] Сразу после начального обнуления процессора содержимое двоичных разрядов 8-9 управляющего регистра 0, двоичных разрядов 62-63 управляющего регистра 2 и глубина вложения транзакций устанавливаются в нуль. Если директива транзакционного выполнения, бит 8 управляющего регистра 0, равна нулю, процессор не может быть переведен в режим транзакционного выполнения.

[00111] Дальнейшие подробности касательно различных директив описываются ниже.

[00112] Как упоминалось, средство транзакционного выполнения управляется двумя битами в управляющем регистре нуль и тремя битами в управляющем регистре два. Например:

[00113] Биты Управляющего Регистра 0 (Control Register 0 Bits): Назначение битов следующее, в одном варианте:

[00114] Директива Транзакционного Выполнения (ТХС): Бит 8 управляющего регистра нуль является директивой транзакционного выполнения. Этот бит предоставляет механизм, при помощи которого управляющая программа (напр., операционная система) может выяснить, употребляется или нет программой средство транзакционного выполнения. Бит 8 должен быть равен единице для успешного входа в режим транзакционного выполнения.

[00115] Если бит 8 управляющего регистра 0 равен нулю, попытка выполнения команд ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ, НАЧАТЬ ТРАНЗАКЦИЮ и ЗАКОНЧИТЬ ТРАНЗАКЦИЮ вызывает выполнение специальной операции.

[00116] Один из вариантов формата команды ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ описан при помощи ФИГ. 8. К примеру, команда ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ 800 включает поле кода операции 802, которое определяет код операции, которое обозначает операцию извлечения глубины вложения транзакций; и поле регистра R1 804, которое определяет регистр общего назначения.

[00117] Текущая глубина вложения транзакций помещается в биты 48-63 регистра общего назначения R1. Биты 0-31 регистра остаются неизменными, а биты 32-47 регистра устанавливаются в нуль.

[00118] В другом варианте максимальная глубина вложения транзакций также помещается в главный регистр R1, например в биты 16-31.

[00119] Переопределение Фильтрации Программного Прерывания Транзакционного Выполнения (Transaction Execution Program Interruption Filtering Override) (PIFO): Бит 9 управляющего регистра нуль является переопределением фильтрации программного прерывания транзакционного выполнения. Этот бит предоставляет механизм, с помощью которого управляющая программа может убедиться, что любая ситуация программного исключения, которая происходит, когда процессор находится в режиме транзакционного выполнения, вызывает прерывание безотносительно к эффективной директиве фильтрации программного прерывания, определенной или подразумеваемой командой (командами) НАЧАТЬ ТРАНЗАКЦИЮ.

[00120] Биты Управляющего Регистра 2 (Control Register 2 Bits): Назначение битов следующее, в одном варианте:

[00121] Область Диагностики Транзакций (TDS): Бит 61 управляющего регистра 2 управляет применимостью директивы диагностики транзакций (transaction diagnosis control) (TDC) в битах 62-63 регистра следующим образом:

[00122] TDS

[00123] Директива Диагностики Транзакций (TDC): Биты 62-63 управляющего регистра 2 являются 2-разрядным целым числом без знака, которое может использоваться для вызова случайного сброса транзакций в диагностических целях. Кодировка TDC следующая, к примеру:

[00124] TDC

[00125] Если транзакция сбрасывается из-за ненулевого TDC, то может происходить что-то из следующего:

[00126] * Код сброса устанавливается в любой из кодов 7-11, 13-16 или 255, с величиной кода, случайно выбранной процессором; код состояния устанавливается соответствующим коду сброса. Коды сброса далее описываются ниже.

[00127] * Для невынужденной транзакции код состояния устанавливается равным единице. В этом случае код сброса не применяется.

[00128] Реализована ли величина TDC 1, зависит от модели. Если не реализована, величина 1 действует, как если бы было задано 2.

[00129] Для вынужденной транзакции величина TDC 1 обрабатывается, как если бы было задано 2.

[00130] Если задана величина TDC 3, результаты непредсказуемы.

[00131] Адрес Блока Диагностики Транзакций (Transaction Diagnostic Block Address) (TDBA)

[00132] Действительный адрес блока диагностики транзакций (TDBA) устанавливается из адреса первого операнда самой внешней команды НАЧАТЬ ТРАНЗАКЦИЮ (TBEGIN), если поле B1 команды не нуль. Если процессор находится в режиме первичного пространства или регистра доступа, TDBA определяет положение в первичном пространстве адресов. Если процессор находится в режиме вторичного пространства или домашнего пространства, TDBA определяет положение во вторичном или домашнем пространстве адресов соответственно. Если DAT (Динамическая Трансляция Адресов) выключена, TDBA определяет положение в реальном запоминающем устройстве.

[00133] TDBA используется процессором для нахождения блока диагностики транзакций, называемого TDB, заданный TBEGIN, если транзакция впоследствии сбрасывается. Три самых правых бита TDBA равны нулю, что означает, что TDB, заданный TBEGIN, находится на границе двойного слова.

[00134] Если поле B1 самой внешней команды НАЧАТЬ ТРАНЗАКЦИЮ (TBEGIN) равно нулю, адрес блока диагностики транзакций недействителен, и не сохраняется никаких TDB, заданных TBEGIN, если транзакция впоследствии сбрасывается.

[00135] PSW Сброса Транзакции (Transaction Abort PSW) (TAPSW)

[00136] Во время выполнения команды НАЧАТЬ ТРАНЗАКЦИЮ (TBEGIN), когда глубина вложения изначально нуль, PSW сброса транзакции устанавливается равным содержимому текущего PSW; а адрес команды PSW сброса транзакции определяет следующую последовательную команду (то есть, команду, следующую за самой внешней TBEGIN). Во время выполнения команды НАЧАТЬ ТРАНЗАКЦИЮ вынужденно (TBEGINC), когда глубина вложения изначально нуль, PSW сброса транзакции устанавливается равным содержимому текущего PSW, кроме случаев когда адрес команды PSW сброса транзакции определяет команду TBEGINC (а не следующую последовательную команду, следующую за TBEGINC).

[00137] Если транзакция сбрасывается, код состояния в PSW сброса транзакции заменяется кодом, обозначающим серьезность состояния сброса. Впоследствии, если транзакция была сброшена из-за причин, которые не вызвали прерывание, PSW загружается из PSW сброса транзакции; если транзакция была сброшена из-за причин, которые вызвали прерывание, PSW сброса транзакции сохраняется как старое PSW прерывания.

[00138] PSW сброса транзакции не изменяется во время выполнения любой внутренней команды НАЧАТЬ ТРАНЗАКЦИЮ.

[00139] Глубина Вложения Транзакций (Transaction Nesting Depth) (TND)

[00140] Глубина вложения транзакций является, например, 16-разрядным числом без знака, которое увеличивается на единицу каждый раз, когда команда НАЧАТЬ ТРАНЗАКЦИЮ завершается с кодом состояния 0, и уменьшается на единицу, когда команда ЗАКОЧИТЬ ТРАНЗАКЦИЮ завершается. Глубина вложения транзакций возвращается в нуль, если транзакция сбрасывается, или обнулением процессора.

[00141] В одном из вариантов реализована максимальная TND 15.

[00142] В одной из реализаций, когда процессор находится в режиме вынужденного транзакционного выполнения, глубина вложения транзакций равна единице. Кроме того, хотя максимальная TND может быть представлена 4-битной величиной, TND определена 16-битной величиной для облегчения ее проверки в блоке диагностики транзакций.

[00143] Блок Диагностики Транзакций (Transaction Diagnostic Block) (TDB)

[00144] Если транзакция сбрасывается, различная статусная информация может быть сохранена в блоке диагностики транзакций (TDB).

[00145] 1. TDB, заданный TBEGIN (TBEGIN-specified TDB): Для невынужденной транзакции, если поле B1 самой внешней команды TBEGIN не нуль, адрес первого операнда команды определяет TDB, заданный TBEGIN. Это положение задается прикладной программой и может быть проверено обработчиком сброса приложения.

[00146] 2. TDB Программного Прерывания (PI) (Program-Interruption (PI) TDB): Если невынужденная транзакция сбрасывается из-за неотфильтрованной ситуации программного исключения, или если вынужденная транзакция сбрасывается из-за любой ситуации программного исключения (то есть, любой ситуации, которая вызывает обнаружение программного прерывания), TDB PI сохраняется в ячейках в префиксной зоне. Он доступен для операционной системы для проверки и регистрации в любой диагностической отчетности, которую она может предоставлять.

[00147] 3. TDB Перехвата (Interception TDB): Если транзакция сбрасывается из-за любой ситуации программного исключения, вызывающей перехват (то есть, ситуация вызывает прекращение интерпретационного выполнения и возврат управления к главной программе), TDB сохраняется в месте, определенном в блоке описания состояния для гостевой операционной системы.

[00148] TDB, заданный TBEGIN, сохраняется, в одном варианте, только если адрес TDB действителен (то есть, когда поле B1 самой внешней команды TBEGINC не нуль).

[00149] Для сбросов из-за ситуаций неотфильтрованного программного исключения будет сохранен лишь один из TDB PI или TDB Перехвата. Таким образом, могут сохраняться нуль, один или два TDB на один сброс.

[00150] Дальнейшие подробности касательно одного примера каждого из TDB описываются ниже.

[00151] TDB, заданный TBEGIN (TBEGIN-specified TDB): 256-байтная ячейка, заданная действительным адресом блока диагностики транзакций. Если адрес блока диагностики транзакций действителен, TDB, заданный TBEGIN, сохраняется при сбросе транзакции. TDB, заданный TBEGIN, подчиняется всем механизмам защиты памяти, которые действуют при выполнении самой внешней команды НАЧАТЬ ТРАНЗАКЦИЮ. Событие изменения памяти PER (Запись Программных Событий) для любой части TDB, заданного TBEGIN, обнаруживается во время выполнения самой внешней TBEGIN, но не во время обработки сброса транзакции.

[00152] Одной из целей PER является содействие отладке программ. Она позволяет предупреждать программу о следующих типах событий, к примеру:

[00153] * Выполнение успешной команды ветвления. Предоставляется опция наступления события только если положение цели ветвления находится в пределах заданной области памяти.

[00154] * Выборка команды из заданной области памяти.

[00155] * Изменение содержимого заданной области памяти. Предоставляется опция наступления события только если область памяти находится в пределах заданных пространств адресов.

[00156] * Выполнение команды СОХРАНИТЬ ПРИ ПОМОЩИ РЕАЛЬНОГО АДРЕСА (STORE USING REAL ADDRESS).

[00157] * Выполнение команды ЗАКОНЧИТЬ ТРАНЗАКЦИЮ.

[00158] Программа может выборочно задать, чтобы распознавался один или более типов событий, за исключением того, что событие для СОХРАНИТЬ ПРИ ПОМОЩИ РЕАЛЬНОГО АДРЕСА может быть задано только вместе с событием изменения памяти. Информация касательно события PER предоставляется программе при помощи программного прерывания, с вызовом прерывания, идентифицируемого по коду прерывания.

[00159] Если адрес блока диагностики транзакций недействителен, TDB, заданный TBEGIN, не сохраняется.

[00160] TDB Программного Прерывания (Program-Interruption TDB): Реальное расположение 6144-6399 (шестнадцатеричные 1800-18FF). TDB программного прерывания сохраняется, если транзакция сбрасывается из-за программного прерывания. Если транзакция сбрасывается из-за других причин, содержимое TDB программного прерывания непредсказуемо.

[00161] TDB программного прерывания не подчиняется никакому механизму защиты. События изменения памяти PER не обнаруживаются для TDB программного прерывания, если он сохраняется во время программного прерывания.

[00162] TDB Перехвата (Interception TDB): Реальная 256-байтная ячейка главного компьютера, заданная ячейками 488-495 описания состояния. TDB перехвата сохраняется, когда сброшенная транзакция вызывает перехват прерывания гостевой программы (то есть, код перехвата 8). Если транзакция сбрасывается из-за других причин, содержимое TDB перехвата непредсказуемо. TDB перехвата не подчиняется никакому механизму защиты.

[00163] Как показано на ФИГ.9, поля блока диагностики транзакций 900 следующие, в одном варианте:

[00164] Формат 902: Байт 0 содержит обозначение действительности и формата, то есть:

[00165]

[00166] TDB, в котором поле формата равно нулю, называется нулевым TDB.

[00167] Флаги 904: Байт 1 содержит различные обозначения, то есть:

[00168] Достоверность Маркера Конфликта (CTV): Если транзакция сбрасывается из-за конфликта считывания или записи (то есть, коды сброса 9 или 10 соответственно), бит 0 байта 1 является обозначением достоверности маркера конфликта. Если обозначение CTV равно единице, маркер конфликта 910 в байтах 16-23 TDB содержит логический адрес, на котором был обнаружен конфликт. Если обозначение CTV равно нулю, биты 16-23 TDB непредсказуемы.

[00169] Если транзакция сбрасывается из-за любой причины, иной нежели конфликт считывания или записи, бит 0 байта 1 сохраняется как нуль.

[00170] Обозначение Вынужденной Транзакции (CTI): Если процессор находится в режиме вынужденного транзакционного выполнения, бит 1 байта 1 установлен равным единице. Если процессор находится в режиме невынужденного транзакционного выполнения, бит 1 байта 1 установлен равным нулю.

[00171] Зарезервировано: Биты 2-7 байта 1 зарезервированы и сохраняются равными нулю.

[00172] Глубина Вложения Транзакций (TND) 906: Байты 6-7 содержат глубину вложений транзакций, когда транзакция была сброшена.

[00173] Код Сброса Транзакции (ТАС) 908: Байты 8-15 содержат 64-битный беззнаковый код сброса транзакции. Каждый пункт кода указывает причину, по которой транзакция сбрасывается.

[00174] Сохраняется ли код сброса транзакции в TDB программного прерывания, когда транзакция сбрасывается из-за причин, отличных от программного прерывания, зависит от модели.

[00175] Маркер Конфликта 910: Для транзакций, которые сбрасываются из-за конфликта считывания или записи (то есть, коды сброса 9 или 10 соответственно), байты 16-23 содержат логический адрес ячейки памяти, на которой был обнаружен конфликт. Маркер конфликта имеет смысл, если бит CTV, бит 0 байта 1, равен единице.

[00176] Если бит CTV равен нулю, биты 16-23 непредсказуемы.

[00177] Из-за упреждающего выполнения процессором маркер конфликта может задавать ячейку памяти, которая не обязательно будет достигнута в последовательности концептуального выполнения транзакции.

[00178] Адрес Команды Сброшенной Транзакции (ATIA) 912: Байты 24-31 содержат адрес команды, которая идентифицирует команду, которая выполнялась, когда был обнаружен сброс. Если транзакция сбрасывается из-за кодов сброса 2, 5, 6, 11, 13 или 256 и выше, или если транзакция сбрасывается из-за кодов сброса 4 или 13, а ситуация программного исключения обнуляет, ATIA указывает прямо на команду, которая выполнялась. Если транзакция сбрасывается из-за кодов сброса 4 или 12, а ситуация программного исключения не обнуляет, ATIA указывает после команды, которая выполнялась.

[00179] Если транзакция сбрасывается из-за кодов сброса 7-10, 14-16 или 255, ATIA не обязательно указывает на действительную команду, вызвавшую сброс, а может указывать на более раннюю или позднюю команду в пределах транзакции.

[00180] Если транзакция сбрасывается из-за команды, которая является целью команды исполнительного типа, ATIA идентифицирует команду исполнительного типа, указывая на эту команду или же после нее в зависимости от кода сброса, как описано выше. ATIA не указывает на цель команды исполнительного типа.

[00181] ATIA подчиняется режиму адресации, когда транзакция сбрасывается. В 24-битном режиме адресации биты 0-40 поля содержат нули. В 31-битном режиме адресации биты 0-32 поля содержат нули.

[00182] Сохраняется ли адрес команды сброшенной транзакции в TDB программного прерывания, когда транзакция сбрасывается из-за причин, отличных от программного прерывания, зависит от модели.

[00183] Если транзакция сбрасывается из-за кодов сброса 4 или 12, а ситуация программного исключения не обнуляет, ATIA не указывает на команду, вызвавшую сброс. Вычитая количество полуслов, определенное кодом длины прерывания (ILC), из ATIA, можно идентифицировать команду, вызвавшую сброс, в условиях которые подавляют или обрывают, или для событий не-PER, которые завершаются. Если транзакция сбрасывается из-за события PER, и не присутствуют другие ситуации программного исключения, ATIA непредсказуем.

[00184] Если адрес блока диагностики транзакций действителен, ILC может быть проверен в идентификации программного прерывания (PIID) в байтах 36-39 TDB, заданного TBEGIN. Если фильтрация не применяется, ILC может быть проверен в PIID в ячейках 140-143 реальной памяти.

[00185] Идентификация Обращения Исключения (EAID) 914: Для транзакций, сброшенных из-за некоторых ситуаций фильтрованного программного исключения, байт 32 TDB, заданного TBEGIN, содержит идентификацию обращения исключения. В одном из примеров z/Architecture формат EAID и случаи, в которых она сохраняется, такие же, как описанные в реальной ячейке 160, когда ситуация исключения вызывает прерывание, как описано в выше включенных по ссылке "Принципах Работы".

[00186] Для транзакций, сброшенных по другим причинам, включая любые ситуации исключения, которые вызывают программное прерывание, байт 32 непредсказуем. Байт 32 непредсказуем в TDB программного прерывания.

[00187] Это поле сохраняется только в TDB, заданном адресом блока диагностики транзакций; иначе, это поле зарезервировано. EAID сохраняется только для ситуаций программного исключения защиты DAT или управляемой списком доступа, типа ASCE, трансляции страниц, трансляции региона первого, трансляции региона второго, трансляции региона третьего и трансляции сегментов.

[00188] Код Исключения Данных (Data Exception Code) (DXC) 916: Для транзакций, сброшенных из-за ситуаций программного исключения фильтрованного исключения данных, байт 33 TDB, заданного TBEGIN, содержит код исключения данных. В одном из примеров z/Architecture формат DXC и случаи, в которых он сохраняется, такие же, как описанные в реальной ячейке 147, когда ситуация исключения вызывает прерывание, как описано в выше включенных по ссылке "Принципах Работы". В одном из примеров ячейка 147 включает DXC.

[00189] Для транзакций, сброшенных по другим причинам, включая любые ситуации исключения, которые вызывают программное прерывание, байт 33 непредсказуем. Байт 33 непредсказуем в TDB программного прерывания.

[00190] Это поле сохраняется только в TDB, заданном адресом блока диагностики транзакций; иначе, это поле зарезервировано. DXC сохраняется только для ситуаций программного исключения данных.

[00191] Идентификация Программного Прерывания (Program Interruption Identification) (PHD) 918: Для транзакций, сброшенных из-за некоторых ситуаций фильтрованного программного исключения, байты 36-39 TDB, заданного TBEGINC, содержат идентификацию программного прерывания. В одном из примеров z/Architecture формат PIID и случаи, в которых она сохраняется, такие же, как описанные в реальных ячейках 140-143, когда ситуация исключения вызывает прерывание (как описано в выше включенных по ссылке "Принципах Работы"), кроме случая, когда код длины команды в битах 13-14 PIID соответствует команде, на которой была обнаружена ситуация исключения.

[00192] Для транзакций, сброшенных по другим причинам, включая любые ситуации исключения, которые вызывают программное прерывание, байты 36-39 непредсказуемы. Байты 36-39 непредсказуемы в TDB программного прерывания.

[00193] Это поле сохраняется только в TDB, заданном адресом блока диагностики транзакций; иначе, это поле зарезервировано. Идентификация программного прерывания сохраняется только для ситуаций программного исключения.

[00194] Идентификация Исключения Трансляции (TEID) 920: Для транзакций, сброшенных из-за любой из следующих ситуаций фильтрованного программного исключения, байты 40-47 TDB, заданного TBEGIN, содержат идентификацию исключения трансляции.

[00195] * Защита DAT или управляемая списком доступа

[00196] * Тип ASCE

[00197] * Трансляция страниц

[00198] * Трансляция региона первого

[00199] * Трансляция региона второго

[00200] * Трансляция региона третьего

[00201] * Исключение трансляции сегментов

[00202] В одном из примеров zlArchitecture формат TEID и случаи, в которых она сохраняется, такие же, как описанные в реальных ячейках 168-175, когда ситуация исключения вызывает прерывание, как описано в выше включенных по ссылке "Принципах Работы".

[00203] Для транзакций, сброшенных по другим причинам, включая любые ситуации исключения, которые вызывают программное прерывание, байты 40-47 непредсказуемы. Байты 40-47 непредсказуемы в TDB программного прерывания.

[00204] Это поле сохраняется только в TDB, заданном адресом блока диагностики транзакций; иначе, это поле зарезервировано.

[00205] Адрес События Останова (Breaking Event Address) 922: Для транзакций, сброшенных из-за некоторых ситуаций фильтрованного программного исключения, байты 48-55 TDB, заданного TBEGIN, содержат адрес события останова. В одном из примеров z/Architecture формат адреса события останова такой же, как описанный в реальных ячейках 272-279, когда ситуация вызывает прерывание, как описано в выше включенных по ссылке "Принципах Работы".

[00206] Для транзакций, сброшенных по другим причинам, включая любые ситуации исключения, которые вызывают программное прерывание, байты 48-55 непредсказуемы. Байты 48-55 непредсказуемы в TDB программного прерывания.

[00207] Это поле сохраняется только в TDB, заданном адресом блока диагностики транзакций; иначе, это поле зарезервировано.

[00208] Дальнейшие подробности касательно событий останова описываются ниже.

[00209] В одном из вариантов z/Architecture, если установлено средство PER-3, оно предоставляет программе адрес последней команды, которая вызовет останов при последовательном выполнении процессором. Запись адреса события останова может использоваться как средство отладки для обнаружения неуправляемого ветвления. Это средство предоставляет, например, 64-битный регистр в процессоре, называемый регистром адреса события останова. Каждый раз, когда команда, отличная от СБРОСИТЬ ТРАНЗАКЦИЮ, вызывает останов последовательного выполнения команд (то есть, адрес команды в PSW замещается, а не увеличивается на длину команды), адрес этой команды помещается в регистр адреса события останова. Когда бы ни произошло программное прерывание, указана или нет PER, текущее содержимое регистра адреса события останова помещается в ячейки 272-279 реальной памяти.

[00210] Если команда, вызывающая событие останова, является целью команды исполнительного типа (ВЫПОЛНИТЬ или ВЫПОЛНИТЬ ОТНОСИТЕЛЬНО ДЛИННОЕ), то адрес команды, использованный для выборки команды исполнительного типа, помещается в регистр адреса события останова.

[00211] В одном из вариантов z/Architecture считается, что событие останова происходит всегда, когда одна из следующих команд вызывает ветвление: РАЗВЕТВИТЬ И СВЯЗАТЬ (BAL, BALR); РАЗВЕТВИТЬ И СОХРАНИТЬ (BAS, BASR); РАЗВЕТВИТЬ И СОХРАНИТЬ И УСТАНОВИТЬ РЕЖИМ (BASSM); РАЗВЕТВИТЬ И УСТАНОВИТЬ РЕЖИМ (BSM); РАЗВЕТВИТЬ И ПОМЕСТИТЬ В СТЕК (BAKR); РАЗВЕТВИТЬ ПО УСЛОВИЮ (ВС, BCR); РАЗВЕТВИТЬ ПО СЧЕТЧИКУ (ВСТ, BCTR, BCTG, BCTGR); РАЗВЕТВИТЬ ПО ИНДЕКСУ ВЫШЕ (ВХН, BXHG); РАЗВЕТВИТЬ ПО ИНДЕКСУ НИЖЕ ИЛИ РАВНО (BXLE, BXLEG); РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО ПО УСЛОВИЮ (BRC); РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО ПО УСЛОВИЮ ДЛИННОЕ (BRCL); РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО ПО СЧЕТЧИКУ (BRCT, BRCTG); РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО ПО ИНДЕКСУ ВЫШЕ (BRXH, BRXHG); РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО ПО ИНДЕКСУ НИЖЕ ИЛИ РАВНО (BRXLE, BRXLG); СРАВНИТЬ И РАЗВЕТВИТЬ (CRB, CGRB); СРАВНИТЬ И РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО (CRJ, CGRJ); СРАВНИТЬ НЕПОСРЕДСТВЕННО И РАЗВЕТВИТЬ (CIB, CGIB); СРАВНИТЬ НЕПОСРЕДСТВЕННО И РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО (СП, CGIJ); СРАВНИТЬ ЛОГИЧЕСКИ И РАЗВЕТВИТЬ (CLRB, CLGRB); СРАВНИТЬ ЛОГИЧЕСКИ И РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО (CLRJ, CLGRJ); СРАВНИТЬ ЛОГИЧЕСКИ НЕПОСРЕДСТВЕННО И РАЗВЕТВИТЬ (CLIB, CLGIB) и СРАВНИТЬ ЛОГИЧЕСКИ НЕПОСРЕДСТВЕННО И РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО (CLIJ, CLGIJ).

[00212] Также считается, что событие останова происходит всегда, когда одна из следующих команд завершается: РАЗВЕТВИТЬ И УСТАНОВИТЬ ПОЛНОМОЧИЯ (BSA); РАЗВЕТВИТЬ В ПОДПРОСТРАНСТВЕННОЙ ГРУППЕ (BSG); РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО И СОХРАНИТЬ (BRAS); РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО И СОХРАНИТЬ ДЛИННОЕ (BRASL); ЗАГРУЗИТЬ PSW (LPSW); ЗАГРУЗИТЬ PSW РАСШИРЕННО (LPSWE); ВЫЗОВ ПРОГРАММЫ (PC); ВОЗВРАТ ПРОГРАММЫ (PR); ПЕРЕНОС ПРОГРАММЫ (РТ); ПЕРЕНОС ПРОГРАММЫ С КОПИЕЙ (PTI); ПРОДОЛЖЕНИЕ ПРОГРАММЫ (RP) и ЛОВУШКА (TRAP2, TRAP4).

[00213] Не считается, что происходит событие останова в результате сброса транзакции (или неявно, или в результате команды СБРОСИТЬ ТРАНЗАКЦИЮ).

[00214] Диагностическая Информация, Зависящая от Модели 924: Байты 112-127 содержат диагностическую информацию, зависящую от модели.

[00215] Для всех кодов сброса, кроме 12 (фильтрованное программное прерывание), диагностическая информация, зависящая от модели, сохраняется в каждом TDB, который сохраняется.

[00216] В одном из вариантов диагностическая информация, зависящая от модели, включает следующее:

[00217] * Байты 112-119 содержат вектор из 64 бит, называемых индикаторами ветвления транзакционного выполнения (TXBI). Каждый из первых 63 бит вектора обозначает результаты выполнения команды ветвления, когда процессор находится в режиме транзакционного выполнения, то есть:

[00218] Величина Значение

[00219] 0 Команда завершилась без ветвления.

[00220] 1 Команда завершилась с ветвлением.

[00221] Бит 0 представляет результат первой такой команды ветвления, бит 1 представляет результат второй такой команды ветвления, и так далее.

[00222] Если были выполнены менее чем 63 инструкции ветвления, пока процессор находился в режиме транзакционного выполнения, крайние правые биты, которые не соответствуют командам ветвления, устанавливаются в нули (включая бит 63). Если были выполнены более чем 63 команды ветвления, бит 63 TXBI устанавливается в единицу.

[00223] Биты в TXBI устанавливаются командами, способными вызывать событие останова, как перечислено выше, за исключением следующего:

[00224] - Любая недопустимая команда не вызывает установку бита в TXBI.

[00225] - Для команд, например, z/Architecture, если поле Mi команды РАЗВЕТВИТЬ ПО УСЛОВИЮ, РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО ПО УСЛОВИЮ или РАЗВЕТВИТЬ ОТНОСИТЕЛЬНО ПО УСЛОВИЮ ДЛИННОЕ равно нулю, или если поле R2 следующей команды равно нулю, вызывает ли выполнение команды установку бита в TXBI, зависит от модели.

[00226] * РАЗВЕТВИТЬ И СВЯЗАТЬ (BALR); РАЗВЕТВИТЬ И СОХРАНИТЬ (BASR); РАЗВЕТВИТЬ И СОХРАНИТЬ И УСТАНОВИТЬ РЕЖИМ (BASSM); РАЗВЕТВИТЬ И УСТАНОВИТЬ РЕЖИМ (BSM); РАЗВЕТВИТЬ ПО УСЛОВИЮ (BCR) и РАЗВЕТВИТЬ ПО СЧЕТЧИКУ (BCTR, BCTGR)

[00227] * Для ситуаций сброса, которые были вызваны исключением доступа главного компьютера, двоичный разряд 0 байта 127 устанавливается в единицу. Для всех других ситуаций сброса двоичный разряд 0 байта 127 устанавливается в нуль.

[00228] * Для ситуаций сброса, которые были обнаружены устройством загрузки/сохранения (load/store unit) (LSU), пять крайних правых бит байта 127 содержат обозначение причины. Для ситуаций сброса, которые не были обнаружены LSU, байт 127 зарезервирован.

[00229] Регистры общего назначения 930: Байты 128-255 содержат содержимое регистров общего назначения 0-15 на момент, когда транзакция была сброшена. Регистры сохраняются в восходящем порядке, начиная с регистра общего назначения 0 в байтах 128-135, регистра общего назначения 1 в байтах 136-143, и так далее.

[00230] Зарезервировано: Все другие поля зарезервированы. Если не указано иное, содержимое зарезервированных полей непредсказуемо.

[00231] С точки зрения других процессоров и подсистемы ввода-вывода, сохранение TDB во время сброса транзакции является множественным обращением, происходящим после любых нетранзакционных сохранений.

[00232] Транзакция может быть сброшена из-за причин, которые находятся вне области непосредственной конфигурации, в которой она выполняется. Например, переходные процессы, обнаруженные гипервизором (таким как LPAR или z/VM), могут вызвать сброс транзакции.

[00233] Информация, предоставляемая в блоке диагностики транзакций, предназначена для диагностических целей и преимущественно верна. Однако, так как сброс может быть вызван событием вне области непосредственной конфигурации, информация, такая как код сброса или идентификация программного прерывания, может неточно отражать ситуацию внутри конфигурации, и таким образом, не должна использоваться для определения действия программы.

[00234] В дополнение к диагностической информации, сохраняющейся в TDB, если транзакция сбрасывается из-за любой ситуации программного исключения данных, а как директива регистра AFP, бит 45 управляющего регистра 0, так и эффективная директива разрешения операции с плавающей точкой (F) равны единице, код исключения данных (DXC) помещается в байт 2 управляющего регистра с плавающей точкой (FPCR), безотносительно к тому, применяется ли фильтрация к ситуации программного исключения. Если транзакция сбрасывается, а одна или обе директива регистра AFP и эффективная директива разрешения операции с плавающей точкой равны нулю, DXC не помещается в FPCR.

[00235] В одном из вариантов, как указано здесь, если установлено средство транзакционного выполнения, предоставляются следующие основные команды.

[00236] * ИЗВЛЕЧЬ ГЛУБИНУ ВЛОЖЕНИЯ ТРАНЗАКЦИЙ

[00237] * НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ

[00238] * СБРОСИТЬ ТРАНЗАКЦИЮ

[00239] * НАЧАТЬ ТРАНЗАКЦИЮ

[00240] * ЗАКОНЧИТЬ ТРАНЗАКЦИЮ