Изобретение относится к промышленной электронике, импульсной технике и схемотехнике. Оно, в частности, может быть использовано для интегрирования последовательностей импульсных сигналов различной формы и для формирования импульсов с изменением напряжения в течение их длительности по закону степенных функций (импульсов линейно изменяющегося напряжения, квадратичных импульсов, кубичных импульсов и т.д.).

Известен интегратор на операционном усилителей (Гусев В. Г., Гусев Ю. М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр.514, рис. 6.16, а), содержащий операционный усилитель, первый резистор, один вывод которого соединен с инвертирующим входом операционного усилителя, а другой образует вход интегратора, второй резистор, включенный между неинвертирующим входом операционного усилителя и общей шиной ("землей"), конденсатор, включенный между инвертирующим входом и выходом операционного усилителя, выход последнего образует выход интегратора, операционный усилитель питается от блока источников постоянных напряжений, один из этих источников имеет положительное постоянное напряжение относительно общей шины ("земли"), другой - отрицательное постоянное напряжение относительно общей шины ("земли").

Недостаток его заключается в том, что с уменьшением погрешности интегрирования возрастает время восстановления интегратора - время, за которое схема приходит в исходное состояние. Это время разряда конденсатора после окончания импульса. В частности, при воздействии прямоугольного импульса на вход интегратора на выходе его получается импульс линейно изменяющегося напряжения. Коэффициент нелинейности его (относительная погрешность интегрирования в данном случае) определяется известной формулой

ξ=tи

, (1)

, (1)

где

τэ=RC(K+1),

τэ - эквивалентная постоянная времени, tи - длительность импульса, R - сопротивление первого резистора, C - электрическая емкость конденсатора и K - коэффициент усиления операционного усилителя. Для обеспечения малой погрешности интегрирования ξ (1) значение эквивалентной постоянной времени τэ (2) следует выбрать большим (часто за счет коэффициента усиления K), тогда большое τэ предопределяет очень и очень большое время восстановления схемы. В результате пауза между интегрируемыми входными импульсами должна быть очень и очень большой, а частота повторения - очень и очень низкой.

Наиболее близкой по технической сущности и достигаемому результату является выбранная в качестве прототипа схема интегратора с цепью обнуления (Опадчий Ф.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника. - М.: Горячая линия - Телеком, 2003, с. 306, рис. 2.18, б), содержащая операционный усилитель, первый резистор, один из выводов которого подключен к инвертирующему входу операционного усилителя, а другой образует вход интегратора, второй резистор, включенный между неинвертирующим входом операционного усилителя и «землей», конденсатор, включенный между инвертирущим входом и выходом операционного усилителя, выход последнего образует выход интегратора, включенный параллельно конденсатору управляемый ключ на полевом транзисторе, на вход которого подаются сигналы с формирователя импульсов управления ключом, операционный усилитель питается от блока источников постоянных напряжений, один из источников имеет положительное постоянное напряжение относительно «земли», другой - отрицательное напряжение относительно «земли».

Недостатком ее является повышение погрешности интегрирования, вызванное обратным сопротивлением управляемого ключа на полевом транзисторе. При воздействии, например, прямоугольного импульса эквивалентная постоянная времени τэ определяется выражением

τэ= , (3)

, (3)

где Rобр - обратное сопротивление ключа на полевом транзисторе (сопротивление его в разомкнутом состоянии). Даже при очень больших значениях коэффициента усиления K эквивалентная постоянная времени τэ не может быть больше значения

τэ=CRобр. (4)

Тогда не удается получить малое значение погрешности интегрирования ξ(1).

Задача, на решение которой направлено изобретение, состоит в уменьшении погрешности интегрирования при использовании последовательностей импульсных входных сигналов.

Это достигается тем, что в аналоговом интеграторе последовательности импульсных сигналов, содержащем операционный усилитель, первый резистор, один из выводов которого соединен с инвертирующим входом операционного усилителя, а другой образует вход интегратора относительно «земли», второй резистор, включенный между неинвертирующим входом операционного усилителя и «землей», конденсатор, включенный между инвертирующим входом и выходом операционного усилителя, выход последнего образует выход интегратора относительно «земли», управляемый ключ, первый вывод которого соединен с общим выводом первого резистора, конденсатора и инвертирующего входа операционного усилителя, вывод входа управления этого ключа соединен с выходом формирователя управляющих импульсов, общая шина которого заземлена, а вход соединен со входом интегратора, блок двух источников постоянных напряжений, общий вывод которого заземлен, первый выход блока источников постоянных напряжений является выходом источника положительного постоянного напряжения относительно «земли», второй выход этого блока - выход источника отрицательного постоянного напряжения относительно «земли», изменено включение элементов, введены три дополнительных управляемых ключа и инвертор, свободный второй вывод имеющегося управляемого ключа соединен с «землей», первый дополнительный управляемый ключ включен между первым выходом блока двух источников постоянных напряжений и выводом операционного усилителя для подключения положительного питающего напряжения, второй дополнительный управляемый ключ включен между вторым выходом блока двух источников постоянных напряжений и выводом операционного усилителя для подключения отрицательного питающего напряжения, третий дополнительный управляемый ключ включен между выходом операционного усилителя и «землей», вход управления третьего дополнительного управляемого ключа соединен с выходом формирователя управляющих импульсов, вход инвертора соединен с выходом формирователя управляющих импульсов, выход инвертора соединен с управляющими входами первого и второго дополнительных управляющих ключей, а общая шина инвертора заземлена.

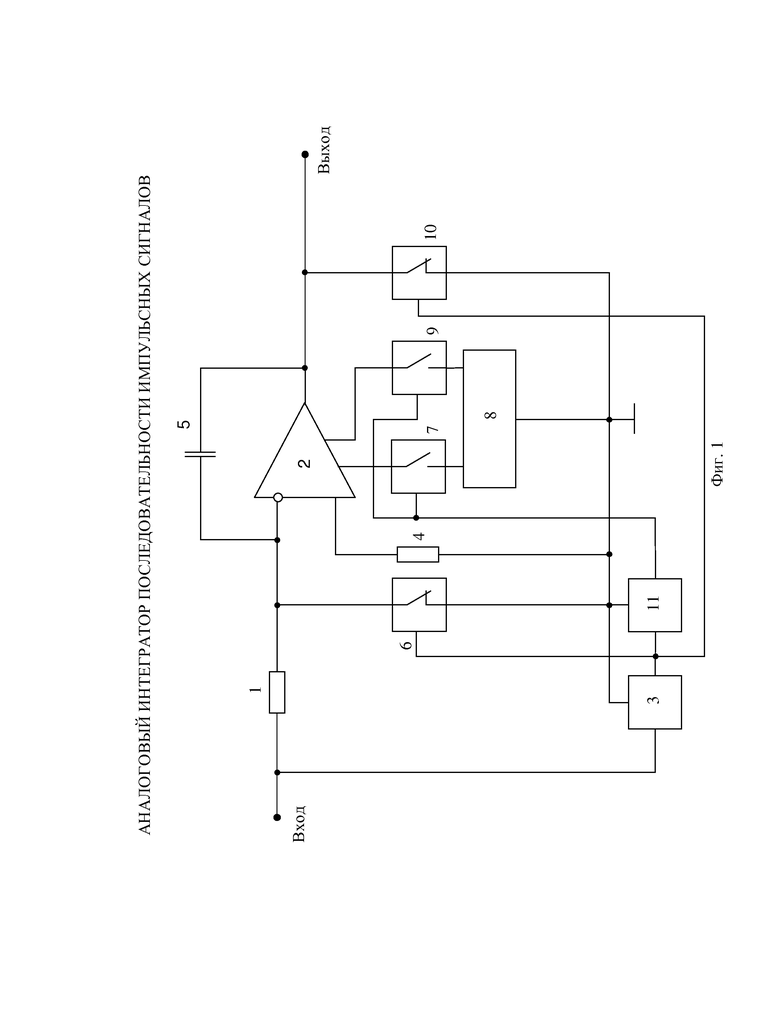

Сущность изобретения поясняется чертежом (Фиг. 1).

Один вывод резистора 1 соединен с инвертирующим входом операционного усилителя 2, второй вывод резистора 1 служит входом интегратора и соединен со входом блока управления ключами 3. Один вывод резистора 4 соединен с неинвертирующим входом операционного усилителя 2, второй вывод резистора 4 заземлен. Один вывод конденсатора 5 соединен с инвертирующим входом операционного усилителя 2, другой вывод конденсатора 5 соединен с выходом операционного усилителя 2, который служит выходом интегратора. Один вывод ключа 6 подключен к инвертирующему входу операционного усилителя 2, второй вывод ключа 6 заземлен. Управляющий вход ключа 6 соединен с выходом блока управления ключами 3. Один вывод ключа 7 соединен с выводом операционного усилителя 2 для подключения положительного питающего напряжения, второй вывод ключа 7 соединен с блоком источников питающих напряжений 8 (с выходом источника положительного напряжения относительно «земли»). Общая шина блока источников питающих напряжений 8 заземлена. Один вывод ключа 9 соединен с выводом операционного усилителя 2 для подключения отрицательного питающего напряжения, второй вывод ключа 9 соединен с выходом блока источников питающих напряжений 8 (с выходом источника отрицательного напряжения относительно «земли»). Один вывод ключа 10 соединен с выходом операционного усилителя 2, а второй вывод ключа 10 заземлен. Управляющие входы ключей 6 и 10 соединены с выходом блока управления ключами 3. Общая шина блока управления ключами 3 заземлена. Управляющие входы ключей 7 и 9 соединены с выходом инвертора 11. Вход инвертора 9 соединен с выходом блока управления ключами 3. Общая шина инвертора 11 заземлена.

Аналоговый интегратор последовательности импульсных сигналов работает следующим образом. В исходном состоянии сигнал на входе интегратора отсутствует. Ключи 6 и 10 замкнуты, ключи 7 и 9 разомкнуты. Конденсатор 5 разряжен. Питающие напряжения с блока питающих напряжений 8 на операционный усилитель 2 не поступают, поскольку ключи 7 и 9 разомкнуты. Напряжение на выходе интегратора (выход операционного усилителя 2) равно нулю. При подаче на вход интегратора импульса напряжения этот импульс поступает также на вход блока управления ключами 3. При поступлении на вход блока управления ключами 3 импульса напряжения блок управления ключами 3 формирует управляющий ключами импульс, поступающий на управляющие входы ключей 6 и 10 непосредственно с блока управления ключами 3, а на управляющие входы ключей 7 и 9 - через инвертор 11. В результате ключи 6 и 10 размыкаются, а ключи 7 и 9 замыкаются. Инвертирующий вход и выход операционного усилителя 2 отключаются от «земли», а на питающие входы операционного усилителя 2 подается положительное (через ключ 7) и отрицательное (через ключ 9) постоянные питающие напряжения с блока питающих напряжений 10. Конденсатор 5 начинает заряжаться, на выходе интегратора появляется напряжение, форма которого определяется формой импульса на входе интегратора. По окончании входного импульса блок управления ключами 3 замыкает ключи 6 и 10, а через инвертор 11 размыкает ключи 7 и 9. Питающие входы операционного усилителя 2 отключаются от выходов блока питающих напряжений 8 разомкнутыми ключами 7 и 9. Конденсатор 5 быстро разряжается через последовательно соединенные малые прямые сопротивления замкнутых ключей 6 и 10, и схема приходит в исходное состояние: ключи 6 и 10 замкнуты, ключи 7 и 9 разомкнуты. Конденсатор 5 разряжен, питающие напряжения с блока питающих напряжений 8 на питающие входы операционного усилителя 2 не поступают, напряжение на выходе интегратора (выход операционного усилителя 2) равно нулю.

Таким образом, в аналоговом интеграторе последовательности импульсных сигналов после окончания входного импульса конденсатор 5 быстро разряжается (время восстановления схемы) через малые прямые сопротивления замкнутых ключей 6 и 10. Постоянная времени восстановления определяется выражением

τВ=C5(Rпр6+Rпр10),

где C5 - электрическая емкость конденсатора 5, Rпр6 и Rпр10 - прямые сопротивления замкнутых управляемых ключей 6 и 10. Малые значения сопротивлений последних предопределяют малые значения постоянной времени восстановления τВ (5). При этом во время действия входного импульса обратное сопротивление разомкнутого управляемого ключа 10 подключено к выходу операционного усилителя 2 (включено между выходом и «землей»). Обратное сопротивление разомкнутого управляемого ключа 6 включено между инвертирующим входом операционного усилителя 2 и «землей». По сути, обратное сопротивление управляемых ключей здесь не включается параллельно конденсатору 5, как в прототипе, не уменьшает эквивалентную постоянную времени τэ (2) и не повышает погрешность интегрирования ξ (1).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый интегратор последовательности импульсных сигналов | 2017 |

|

RU2699410C2 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 1996 |

|

RU2127887C1 |

| Интегратор | 1979 |

|

SU834715A1 |

| Устройство для моделирования электромагнитных процессов в асинхронных машинах | 1989 |

|

SU1681315A1 |

| ИЗМЕРИТЕЛЬ ПОТЕРЬ МОЩНОСТИ (ВАРИАНТЫ) | 2011 |

|

RU2467337C2 |

| Цифро-аналоговый преобразователь | 2017 |

|

RU2648579C1 |

| Импульсный стабилизатор напряжения с плавным запуском | 1987 |

|

SU1464150A1 |

| ФИЛЬТР ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 2001 |

|

RU2204883C1 |

| Устройство для измерения амплитуды импульсных усилий | 1986 |

|

SU1352254A1 |

| Стробирующее устройство | 1981 |

|

SU999113A1 |

Изобретение относится к промышленной электронике, импульсной технике и может быть использовано для интегрирования последовательностей импульсных сигналов различной формы. Технический результат - уменьшение погрешности интегрирования при использовании последовательностей импульсных входных сигналов. Аналоговый интегратор последовательности импульсных сигналов содержит операционный усилитель, формирователь управляющих импульсов, блок источников постоянных напряжений, четыре управляемых электронных ключа, резисторы, конденсатор и инвертор. 1 ил.

Аналоговый интегратор последовательности импульсных сигналов, содержащий операционный усилитель, первый резистор, один из выводов которого соединен с инвертирующим входом операционного усилителя, а другой образует вход интегратора относительно «земли», второй резистор, включенный между неинвертирующим входом операционного усилителя и «землей», конденсатор, включенный между инвертирующим входом и выходом операционного усилителя, выход последнего образует выход интегратора относительно «земли», управляемый ключ, первый вывод которого соединен с общим выводом первого резистора, конденсатора и инвертирующего входа операционного усилителя, вывод входа управления этого ключа соединен с выходом формирователя управляющих импульсов, общая шина которого заземлена, блок двух источников постоянных напряжений, общий вывод которого заземлен, первый выход блока источников постоянных напряжений является выходом источника постоянного напряжения относительно «земли», второй выход этого блока - выход источника отрицательного напряжения относительно «земли», отличающийся тем, что изменено включение элементов, введены три дополнительных управляемых ключа и инвертор, второй вывод управляемого ключа соединен с «землей», первый дополнительный управляемый ключ включен между первым выходом блока двух источников постоянных напряжений и выводом операционного усилителя для подключения положительного питающего напряжения, второй дополнительный управляемый ключ включен между вторым выходом блока двух источников постоянных напряжений и выводом операционного усилителя для подключения отрицательного питающего напряжения, третий дополнительный управляемый ключ включен между выходом операционного усилителя и «землей», вход управления третьего дополнительного управляемого ключа соединен с выходом формирователя управляющих импульсов, вход инвертора соединен с выходом формирователя управляющих импульсов, выход инвертора соединен с управляющими входами первого и второго дополнительных управляющих ключей, а общая шина инвертора заземлена.

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 1993 |

|

RU2088966C1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 2000 |

|

RU2188452C2 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ С КОМПЕНСАЦИЕЙ ПОГРЕШНОСТЕЙ | 2013 |

|

RU2523939C1 |

| US 4734598 A1, 29.03.1988. | |||

Авторы

Даты

2016-11-20—Публикация

2015-09-23—Подача