(54) ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Интегратор | 1979 |

|

SU811284A1 |

| ИНТЕГРАТОР С БОЛЬШИМ ВРЕМЕНЕМ ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2034331C1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Интегратор | 1985 |

|

SU1287195A1 |

| Аналоговый интегратор | 1979 |

|

SU834714A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| Интегратор разности напряжений | 1983 |

|

SU1151996A1 |

| Интегратор | 1983 |

|

SU1198546A1 |

1

Изобретение относится к вычислительной и импульсной технике, предназначено для выполнения интегрирования и других линейных операций в аналоговых вычислительных машинах и может быть использовано в измерительной технике.

Известны интеграторы, содержащие интегрирующую RC-цепь и инвертирующий усилитель, выход которого подключен к конденсатору, а вход - к точке соединения R и С. В таком устройстве выходное напряжение пропорционально интегралу входного. Наличие в интеграторе усилителя с коэффициентом усиления К позволяет уменьщить погрешность интегрирования приблизительно в К раз 1.

Недостаток его заключается в относительно низкой точности интегрирования, которое выполняется с погрешностью от единиц процентов по десятых долей процента.

Наиболее близким по технической сущности является интегратор, состоящий из дифференциального операционного усилителя, инвертирующий вход которого подключен ко входу RC-цепи, а неинвертирующий заземлен через резистор. Выход усилителя подключен к другому выводу конденсатора.

Параллельно конденсатору подсоединен электронный ключ. Источник входного сигнала U«x.(t) подключается на вход интегратора со стороны резистора RC-цепи.

На точность интегрирования оказывает влияние нелинейность передаточной функции интегратора, которая определяется двумя факторами: напряжение на конденсаторе при его заряде через резистор изменяется по экспоненте, а не по прямой; параллельно конденсатору подключено сопротивление ключа, наличие которого изменяет велину и форму передаточной функции, усугубляя ее нелинейность.

Передаточная функция с учетом шунтирующего влияния сопротивления ключа RK описывается выражением, представленным в виде разложения в ряд Маклорена

-к|:|,-Йг-- Й- -Ь

где 2 (1 + К) RC,

где к - коэффициент передачи.

Первый член этого выражения представляет собой идеально линейную прямую, а второй - параболическое отклонение от этой прямой. Члены высших порядков весьма малы. Их влиянием пренебрегают 2.

Недостаток такого интегратора заключается в том, что его параметры Т, (1 + -«ЮНС, R к ограничивают точность интегрирования, а влияние параметра R принципиально не устранимо.

Цель изобретения - повышение точности интегрирования за счет значительного ослабления влияния постоянной времени (за счет ее увеличения) и полного исключения влияния шунтирующего действия сопротивления ключа.

Поставленная цель достигается тем, что в интегратор, содержащий последовательно соединенные первый масштабный резистор и интегрирующий конденсатор, включенные между входом и выходом интегратора, дифференциальный операционный усилитель, инвертирующий вход которого подключен к общему выводу первого масщтабного резистора и интегрирующего конденсатора, а неинвертирующий вход через второй резистор подключен к щине нулевого потенциала, и ключ, вход которого подключен к -выходной обкладке интегрирующего конденсатора, введены усилитель тока и токовый повторитель, управляющий потенциальный вход которого подключен к выходу дифференциального операционного усилителя, а токовый вход соединен с общим выводом интегрирующего конденсатора и ключа, второй вывод которого подключен к щине нулевого потенциала, токовые выходы токового повторителя соединены со входами токового усилителя, выход которого подключен к инвертирующему входу дифференциального операционного усилителя.

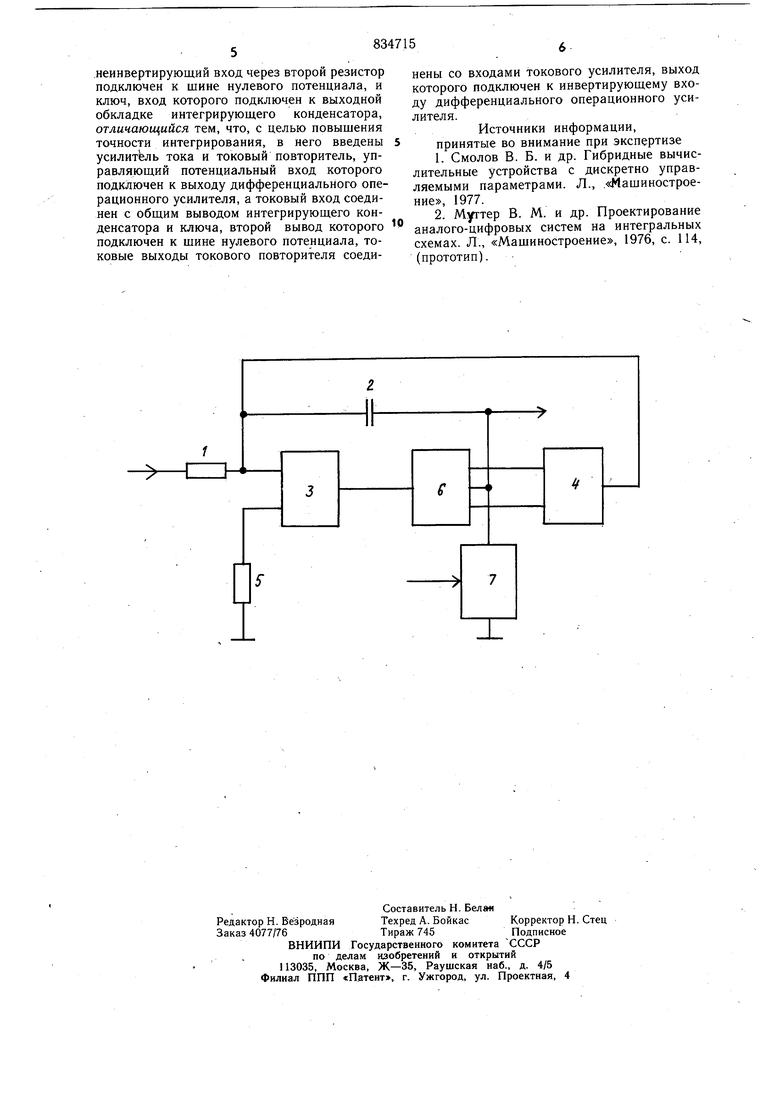

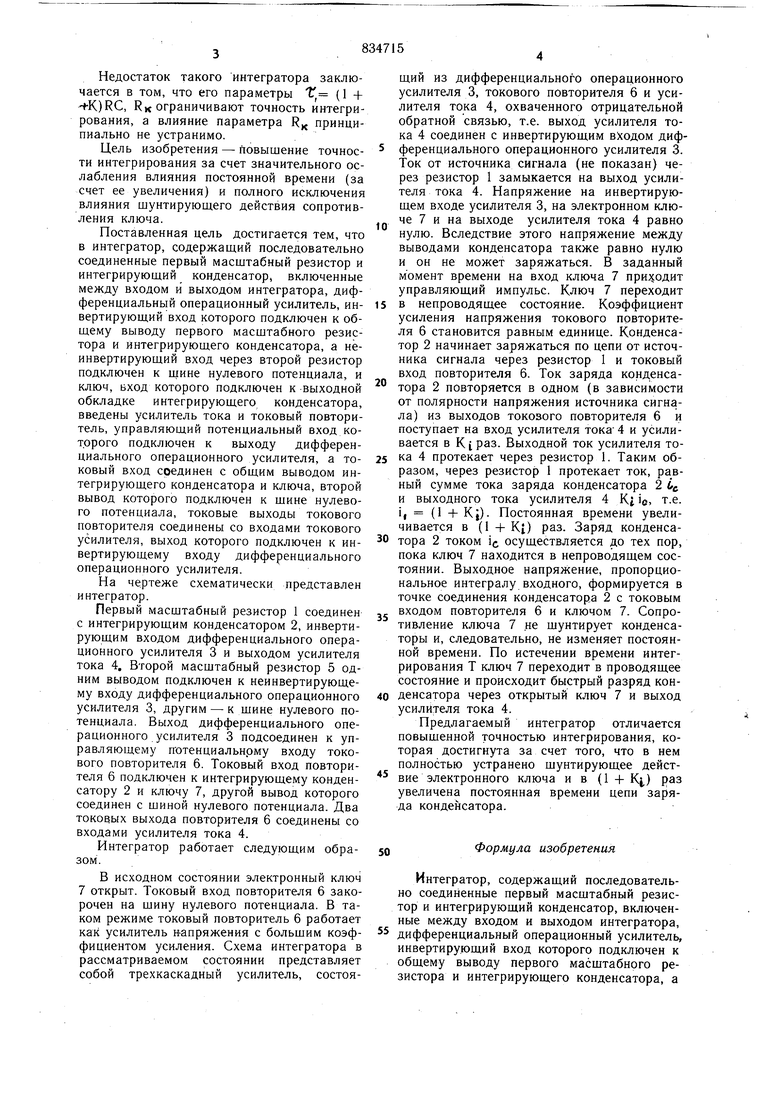

На чертеже схематически представлен интегратор.

Первый масщтабный резистор 1 соединен с интегрирующим конденсатором 2, инвертирующим входом дифференциального операционного усилителя 3 и выходом усилителя тока 4. Второй масштабный резистор 5 одним выводом подключен к неинвертирующему входу дифференциального операционного усилителя 3, другим - к щине нулевого потенциала. Выход дифференциального операционного усилителя 3 подсоединен к управляющему потенциальнрму входу токового повторителя 6. Токовый вход повторителя 6 подключен к интегрирующему конденсатору 2 и ключу 7, другой вывод которого соединен с шиной нулевого потенциала. Два токовых выхода повторителя 6 соединены со входами усилителя тока 4.

Интегратор работает следующим образом.

В исходном состоянии электронный ключ 7 открыт. Токовый вход повторителя 6 закорочен на щину нулевого потенциала. В таком режиме токовый повторитель 6 работает как усилитель н-апряжения с большим коэффициентом усиления. Схема интегратора в рассматриваемом состоянии представляет собой трехкаскадный усилитель, состоящий из дифференциального операционного усилителя 3, токового повторителя 6 и усилителя тока 4, охваченного отрицательной обратной связью, т.е. выход усилителя тока 4 соединен с инвертирующим входом дифференциального операционного усилителя 3. foK от источника сигнала (не показан) через резистор 1 замыкается на выход усилителя тока 4. Напряжение на инвертирующем входе усилителя 3, на электронном ключе 7 и на выходе усилителя тока 4 равно нулю. Вследствие этого напряжение между выводами конденсатора также равно нулю и он не может заряжаться. В заданный момент времени на вход ключа 7 приводит управляющий импульс. Ключ 7 переходит

в непроводящее состояние. Коэффициент усиления напряжения токового повторителя 6 становится равным единице. Конденсатор 2 начинает заряжаться по цепи от источника сигнала через резистор 1 и токовый вход повторителя 6. Ток заряда конденсатора 2 повторяется в одном (в зависимости от полярности напряжения источника сигнала) из выходов токового повторителя 6 и поступает на вход усилителя тока-4 и усиливается в К i раз. Выходной ток усилителя тока 4 протекает через резистор 1. Таким образом, через резистор 1 протекает ток, ра вный сумме тока заряда конденсатора 2 6 и выходного тока усилителя 4 Ki io, т.е. i, (1 + Kj). Постоянная времени увеличивается в (1 + KI) раз. Заряд конденсатора 2 током i осуществляется до тех пор, пока ключ 7 находится в непроводящем состоянии. Выходное напряжение, пропорциональное интегралу входного, формируется в точке соединения конденсатора 2 с токовым входом повторителя 6 и ключом 7. Сопротивление ключа 7 не щунтирует конденсаторы и, следовательно, не изменяет постоянной времени. По истечении времени интегрирования Т ключ 7 переходит в проводящее состояние и происходит быстрый разряд конденсатора через открытый ключ 7 и выход усилителя тока 4.

Предлагаемый интегратор отличается повыщенной точностью интегрирования, которая достигнута за счет того, что в нем полностью устранено шунтирующее действие электронного ключа и в (1 Ч- Kj,) раз увеличена постоянная времени цепи заряда конденсатора.

Формула изобретения

Интегратор, содержащий последовательно соединенные первый масштабный резистор и интегрирующий конденсатор, включенные между входом и выходом интегратора, дифференциальный операционный усилитель, инвертирующий вход которого подключен к общему выводу первого масштабного резистора и интегрирующего конденсатора, а

.неинвертирующий вход через второй резистор подключен к шине нулевого потенциала, и ключ, вход которого подключен к выходной обкладке интегрирующего конденсатора, отличающийся тем, что, с целью повыщения точности интегрирования, в него введены усилитЬль тока и токовый повторитель, управляющий потенциальный вход которого подключен к выходу дифференциального операционного усилителя, а токовый вход соединен с общим выводом интегрирующего конденсатора и ключа, второй вывод которого подключен к шине нулевого потенциала, токовые выходы токового повторителя соединены со входами токового усилителя, выход которого подключен к инвертирующему входу дифференциального операционного усилителя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-05-30—Публикация

1979-12-28—Подача