ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение имеет отношение к методике кодирования изображения и методике декодирования изображения для арифметического кодирования или арифметического декодирования.

УРОВЕНЬ ТЕХНИКИ

Растет количество приложений для предоставления услуг через Интернет (например, услуг видеоконференций, цифрового видеовещания и передачи видео по запросу, включающих в себя потоковую передачу видео). Эти приложения полагаются на передачу видеоданных. Когда приложения передают видеоданные, большинство видеоданных передается через традиционный канал передачи, имеющий ограниченную пропускную способность. Кроме того, когда приложения записывают видеоданные, большинство видеоданных записывается на традиционном носителе записи, имеющем ограниченную емкость. Чтобы передать видеоданные через традиционный канал передачи или записать видеоданные на традиционном носителе записи, необходимо сжать или уменьшить объем видеоданных.

С этой целью было разработано много стандартов кодирования видео для сжатия видеоданных. Этими стандартами кодирования видео являются, например, стандарты ITU-T, обозначенные как H.26x, и стандарты ISO/IEC, обозначенные как MPEG-x. В настоящий момент последним и наиболее усовершенствованным стандартом кодирования видео является стандарт, обозначенный как H.264/MPEG-4 AVC (см. не патентную литературу (NPL) 1 и не патентную литературу (NPL) 2).

Подход к кодированию, лежащий в основе большинства этих стандартов кодирования видео, основан на кодировании с предсказанием, которое включает в себя следующие основные этапы (a)-(d): (a) разделить каждый видеокадр на блоки, каждый из которых имеет пиксели, для сжатия данных видеокадра блок за блоком, (b) предсказать каждый блок на основе ранее кодированных видеоданных, чтобы идентифицировать временную и пространственную избыточность, (c) вычесть предсказанные данные из видеоданных, чтобы удалить идентифицированную избыточность, (d) сжать оставшиеся данные (остаточные блоки) посредством преобразования Фурье, квантования и энтропийного кодирования.

Что касается этапа (a), текущий стандарт кодирования видео обеспечивает различные режимы предсказания в зависимости от макроблока, который должен быть предсказан. В соответствии с большинством стандартов кодирования видео оценка движения и компенсация движения используются для предсказания видеоданных на основе ранее кодированного и декодированного кадра (межкадровое (inter) предсказание). В качестве альтернативы, данные блока могут быть экстраполированы из смежного блока того же самого кадра (внутрикадровое (intra) предсказание).

На этапе (d) квантованные коэффициенты, включенные в текущий блок, который должен быть кодирован, сканируются в предопределенном порядке (порядке сканирования). Затем кодируется информация (SignificantFlag), указывающая, являются ли сканированные коэффициенты нулевыми коэффициентами или ненулевыми коэффициентами (например, двоичная информация (символ), указывающая ненулевой коэффициент как 1 и нулевой коэффициент как 0).

Кроме того, информация, указывающая позицию последнего ненулевого коэффициента в порядке сканирования (информация последней позиции), преобразовывается в двоичную форму, кодируется посредством контекстно-адаптивного двоичного арифметического кодирования и декодируется посредством контекстно-адаптивного двоичного арифметического декодирования.

СПИСОК ЛИТЕРАТУРЫ

НЕПАТЕНТНАЯ ЛИТЕРАТУРА

[NPL 1] ITU-T Recommendation H.264 "Advanced video coding for generic audiovisual services", March 2010.

[NPL 2] JCT-VC "WD4: Working Draft 4 of High-Efficiency Video Coding", JCTVC-F803, July 2011.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ТЕХНИЧЕСКАЯ ПРОБЛЕМА

Однако в традиционной методике надлежащее переключение среди контекстов является трудным при контекстно-адаптивном двоичном арифметическом кодировании и контекстно-адаптивном двоичном арифметическом декодировании информации последней позиции. Например, когда один и тот же контекст используется для двоичных символов, которые существенно отличаются по вероятности появления, точность предсказания вероятности появления символа уменьшается, и, таким образом, также уменьшается эффективность кодирования.

С этой целью один неограничивающий и иллюстративный вариант осуществления обеспечивает способ кодирования изображения и способ декодирования изображения для арифметического кодирования и арифметического декодирования информации последней позиции с использованием контекста, который надлежащим образом переключен среди множества контекстов.

РЕШЕНИЕ ПРОБЛЕМЫ

Способ кодирования изображения в соответствии с аспектом настоящего изобретения представляет собой способ кодирования изображения для кодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть кодирован, способ кодирования изображения содержит этапы, на которых: преобразовывают в двоичную форму информацию последней позиции для формирования (i) двоичного сигнала, который включает в себя первый сигнал, имеющий длину, меньшую или равную предопределенной максимальной длине, и не включает в себя второй сигнал или (ii) двоичного сигнала, который включает в себя первый сигнал, имеющий предопределенную максимальную длину, и второй сигнал; выполняют первое кодирование для арифметического кодирования каждого из двоичных символов, включенных в первый сигнал, с использованием контекста, переключенного среди множества контекстов в соответствии с битовой позицией двоичного символа; и выполняют второе кодирование для арифметического кодирования второго сигнала с использованием фиксированной вероятности, когда двоичный сигнал включает в себя второй сигнал, причем при первом кодировании двоичный символ в последней битовой позиции первого сигнала арифметически кодируется с использованием контекста, особого для последней битовой позиции, когда первый сигнал имеет предопределенную максимальную длину.

Следует отметить, что этот общий аспект может быть реализован с использованием системы, устройства, интегральной схемы, компьютерной программы или считываемого компьютером носителя записи, такого как компакт-диск (CD-ROM), или любой комбинации систем, устройств, интегральных схем, компьютерных программ или считываемых компьютером носителей записи.

ПОЛЕЗНЫЕ ЭФФЕКТЫ ИЗОБРЕТЕНИЯ

С помощью способа кодирования изображения в соответствии с аспектом настоящего изобретения возможно арифметически кодировать информацию последней позиции с использованием контекста, который надлежащим образом переключен среди множества контекстов.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - блок-схема, показывающая пример конфигурации устройства декодирования изображения в соответствии с основополагающим знанием.

Фиг.2 - блок-схема последовательности операций, показывающая пример способа декодирования изображения в соответствии с основополагающим знанием.

Фиг.3A - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 4×4.

Фиг.3B - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 8×8.

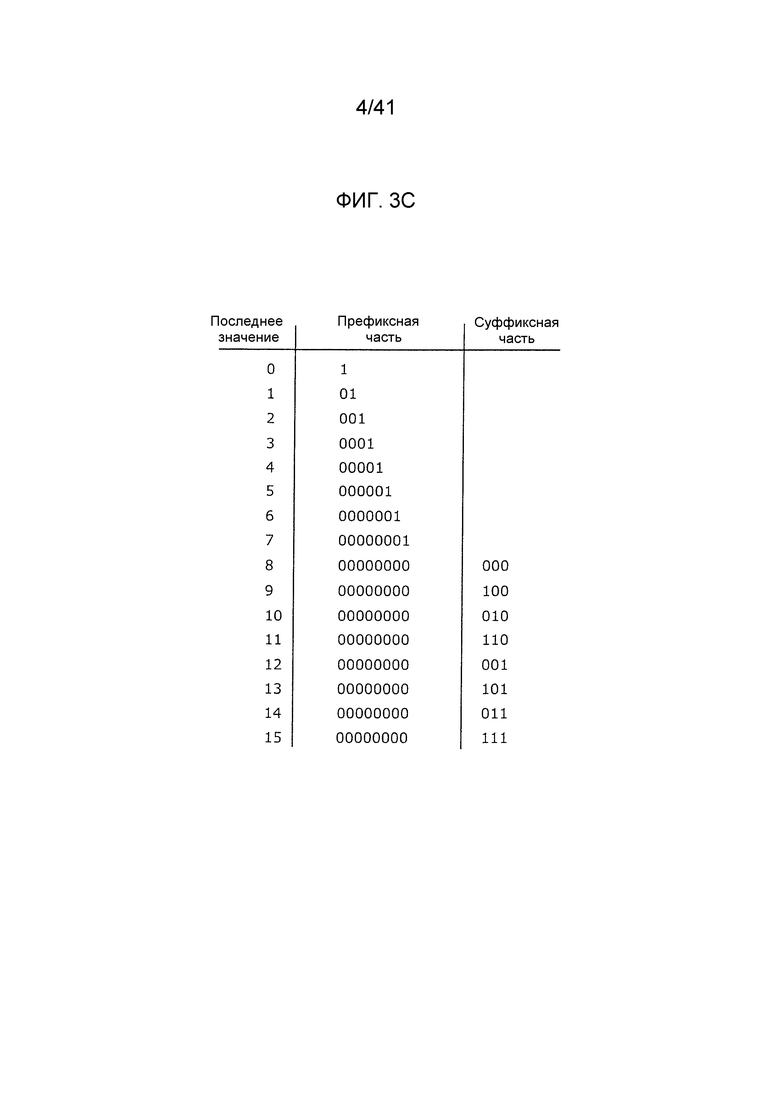

Фиг.3C - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 16×16.

Фиг 3D - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 32×32.

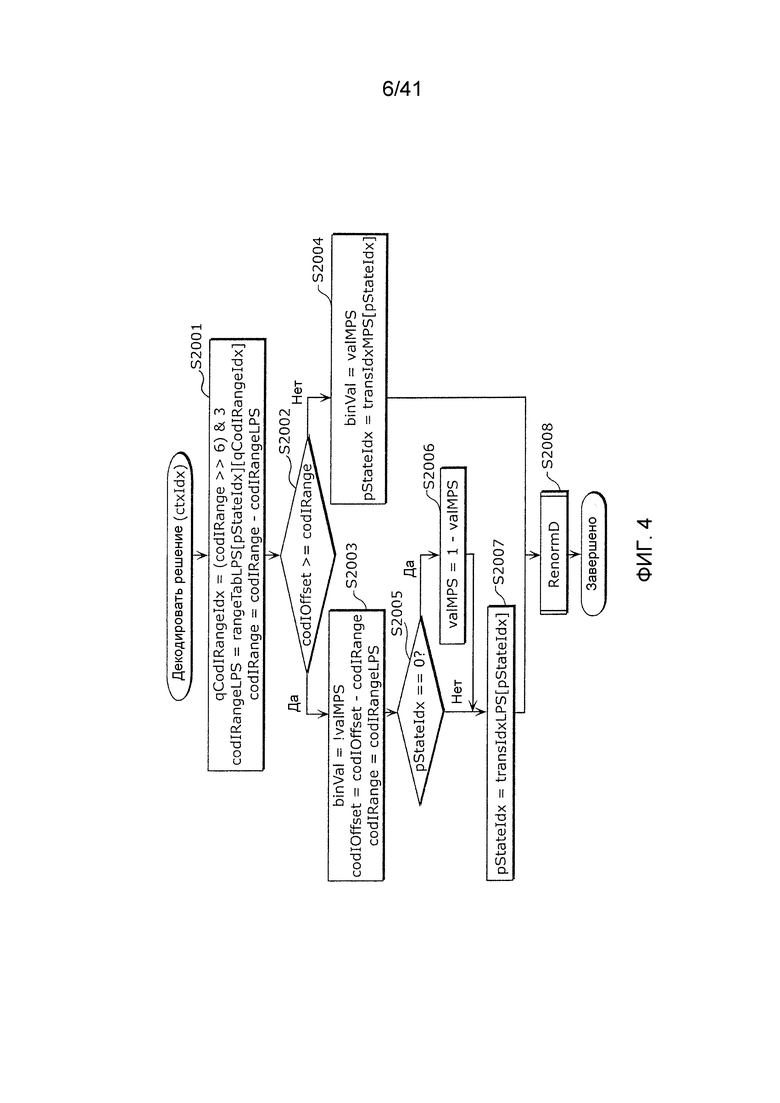

Фиг.4 - блок-схема последовательности операций, показывающая контекстно-адаптивное двоичное арифметическое декодирование.

Фиг.5 - блок-схема последовательности операций, показывающая обходное декодирование.

Фиг.6 - блок-схема последовательности операций, показывающая нормализацию.

Фиг.7 - блок-схема, показывающая функциональную конфигурацию устройства декодирования изображения в соответствии с вариантом осуществления 1.

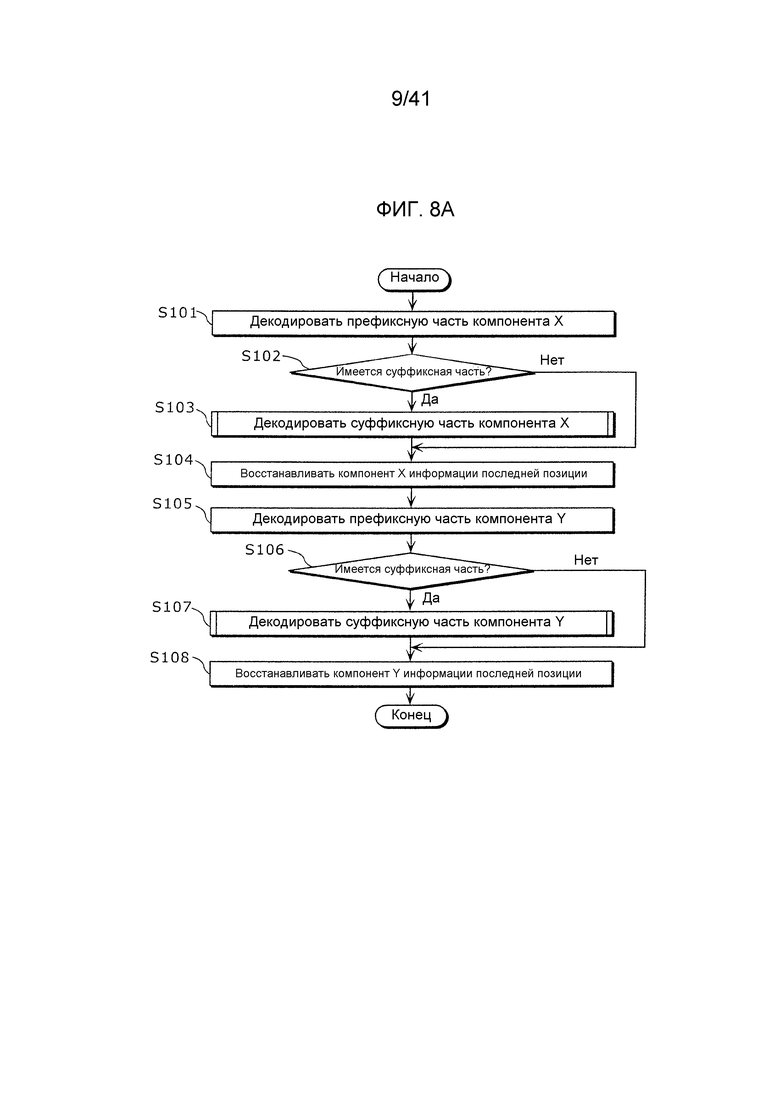

Фиг.8A - блок-схема последовательности операций, показывающая пример операций обработки устройства декодирования изображения в соответствии с вариантом осуществления 1.

Фиг.8B - блок-схема последовательности операций, показывающая другой пример операций обработки устройства декодирования изображения в соответствии с вариантом осуществления 1.

Фиг.9A - блок-схема последовательности операций, показывающая пример операций обработки второго блока декодирования в соответствии с вариантом осуществления 1.

Фиг.9B - схема, показывающая пример соотношения между размером блока и максимальной длиной префиксной части в соответствии с вариантом осуществления 1.

Фиг.9C - схема, показывающая другой пример соотношения между размером блока и максимальной длиной префиксной части в соответствии с вариантом осуществления 1.

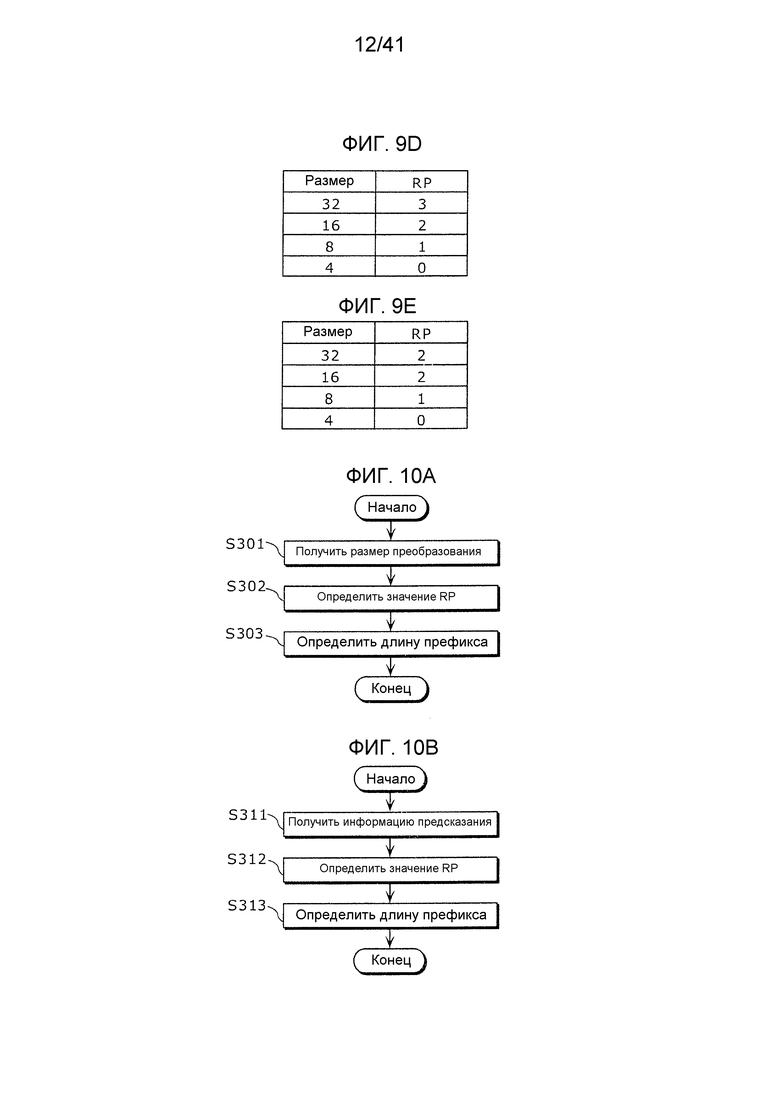

Фиг.9D - схема, показывающая пример соотношения между размером блока и параметром Райса в соответствии с вариантом осуществления 1.

Фиг.9E - схема, показывающая другой пример соотношения между размером блока и параметром Райса в соответствии с вариантом осуществления 1.

Фиг.10A - блок-схема последовательности операций, показывающая пример способа определения значения RP и максимальной длины префиксной части.

Фиг.10B - блок-схема последовательности операций, показывающая другой пример способа определения значения RP и максимальной длины префиксной части.

Фиг.10C - блок-схема последовательности операций, показывающая другой пример способа определения значения RP и максимальной длины префиксной части.

Фиг.10D - блок-схема последовательности операций, показывающая другой пример способа определения значения RP и максимальной длины префиксной части.

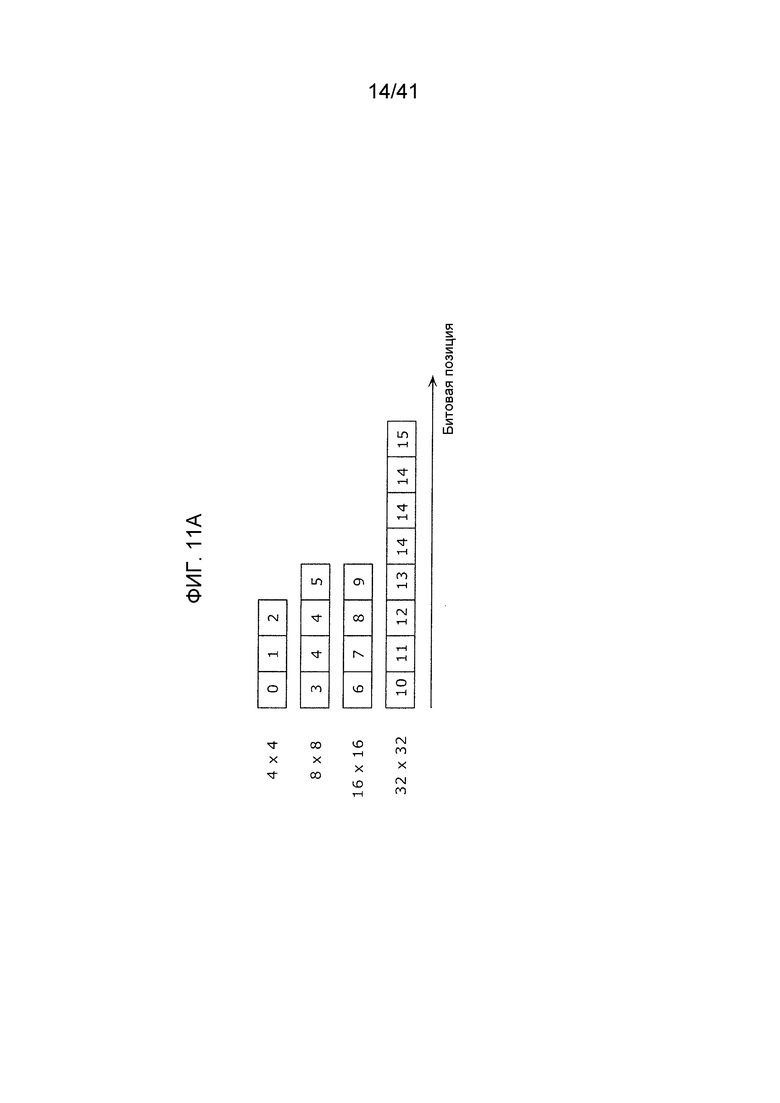

Фиг.11A - схема для описания соотношения между битовыми позициями и контекстами в соответствии с вариантом осуществления 1.

Фиг.11B - схема для описания соотношения между битовыми позициями и контекстами в соответствии со сравнительным примером.

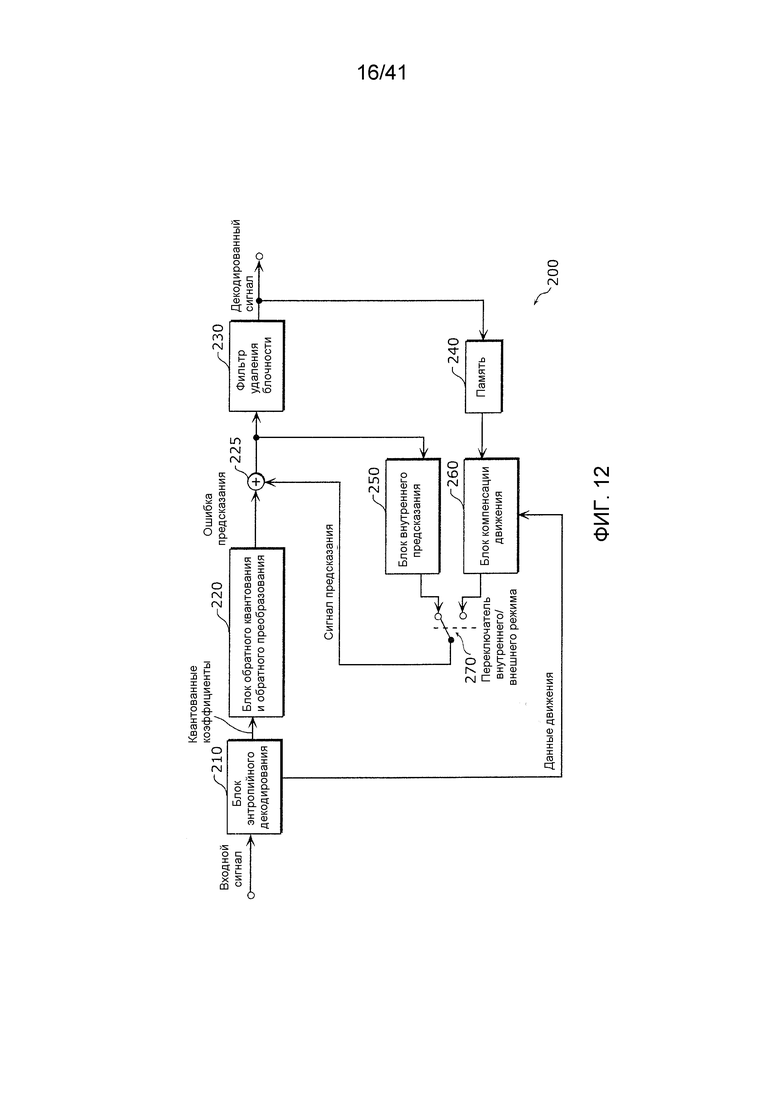

Фиг.12 - блок-схема, показывающая пример конфигурации устройства декодирования изображения в соответствии с изменением варианта осуществления 1.

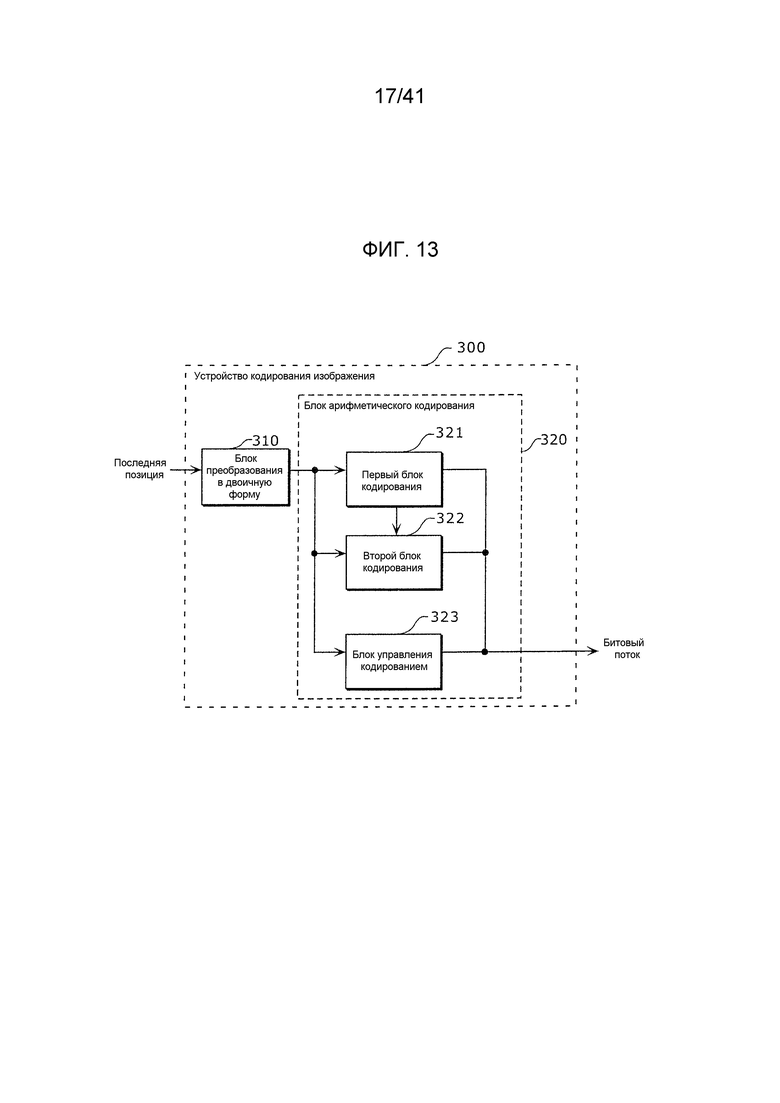

Фиг.13 - блок-схема, показывающая функциональную конфигурацию устройства кодирования изображения в соответствии с вариантом осуществления 2.

Фиг.14A - блок-схема последовательности операций, показывающая пример операций обработки устройства кодирования изображения в соответствии с вариантом осуществления 2.

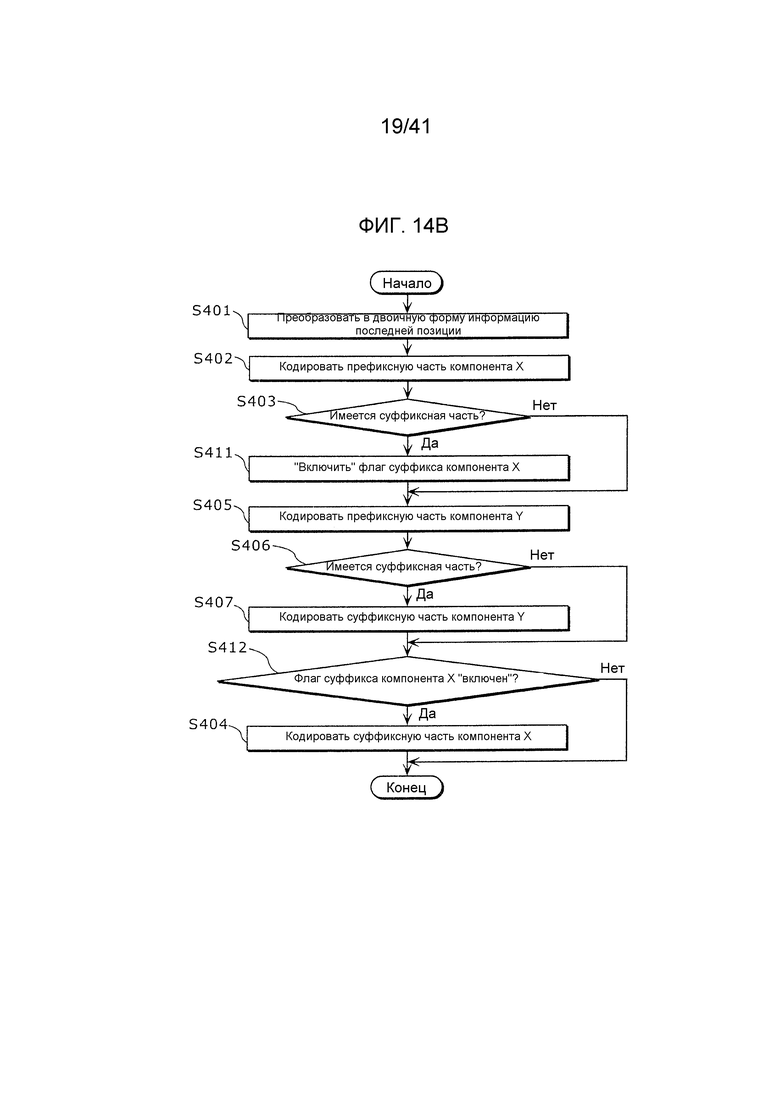

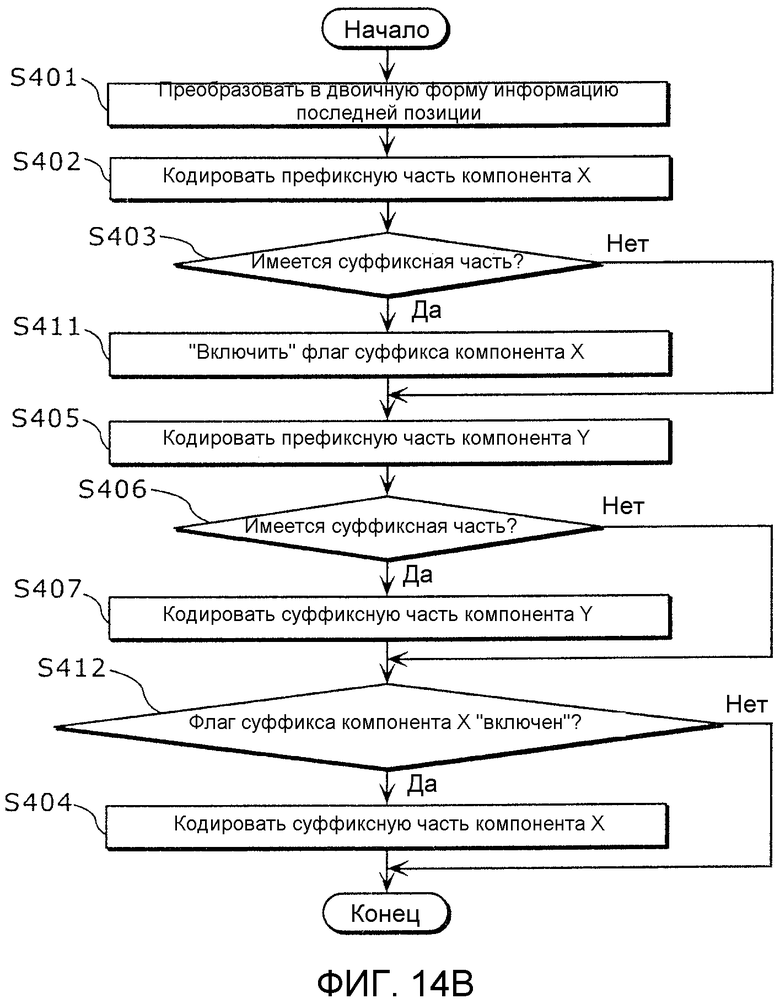

Фиг.14B - блок-схема последовательности операций, показывающая другой пример операций обработки устройства кодирования изображения в соответствии с вариантом осуществления 2.

Фиг.15 - схема, показывающая пример двоичных сигналов информации последней позиции, когда размер блока составляет 16x16.

Фиг.16 - блок-схема, показывающая пример конфигурации устройства кодирования изображения в соответствии с вариантом осуществления 2.

Фиг.17 показывает общую конфигурацию системы обеспечения информационного содержания для реализации службы распространения информационного содержания.

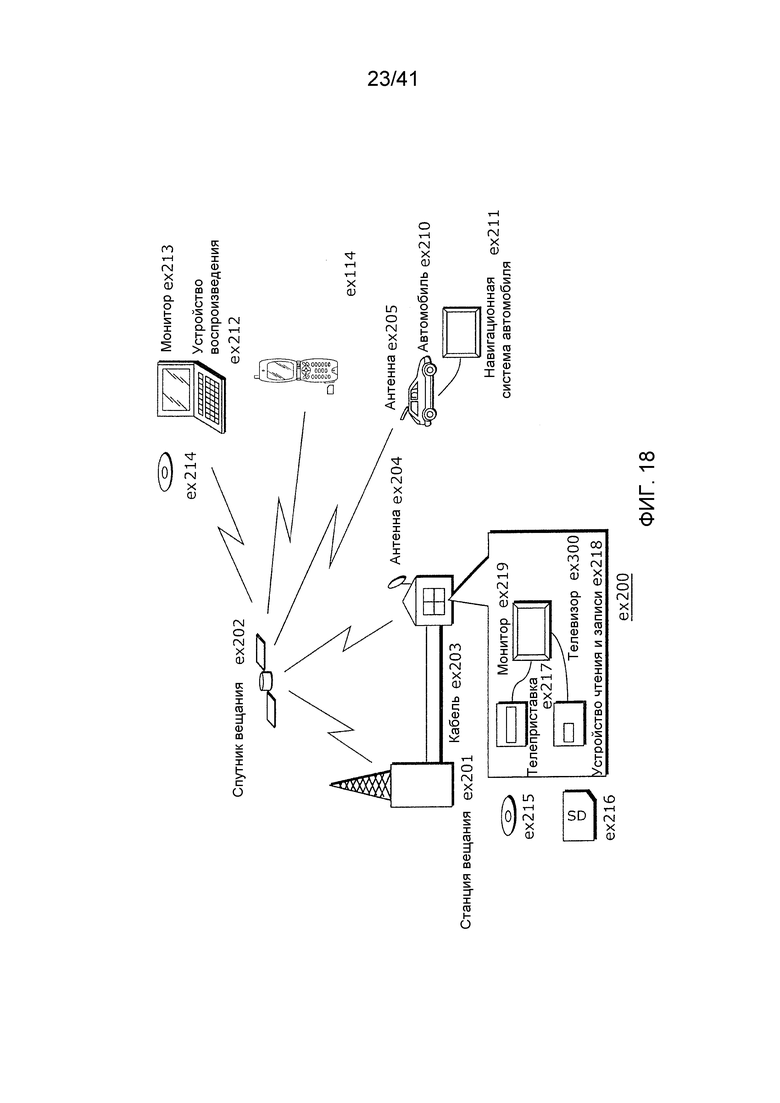

Фиг.18 показывает общую конфигурацию системы цифрового вещания.

Фиг.19 показывает блок-схему, иллюстрирующую пример конфигурации телевизора.

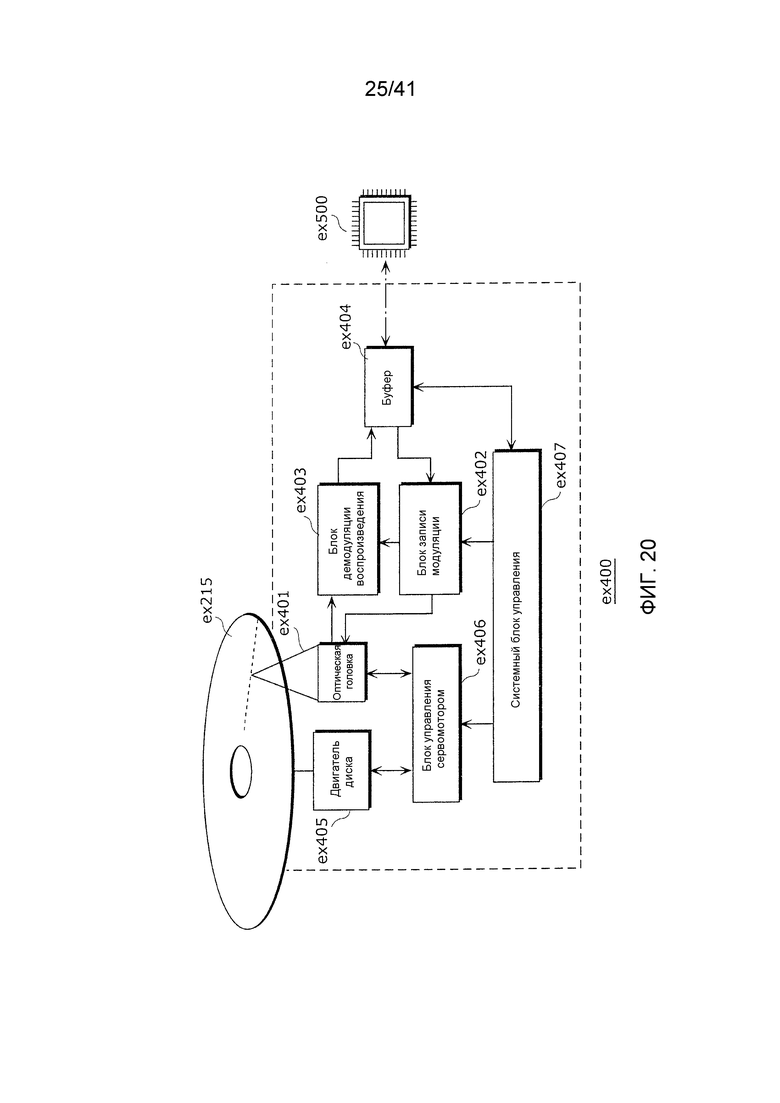

Фиг.20 показывает блок-схему, иллюстрирующую пример конфигурации блока воспроизведения/записи информации, который считывает информацию с носителя записи и записывает информацию на носитель записи, являющийся оптическим диском.

Фиг.21 показывает пример конфигурации носителя записи, являющегося оптическим диском.

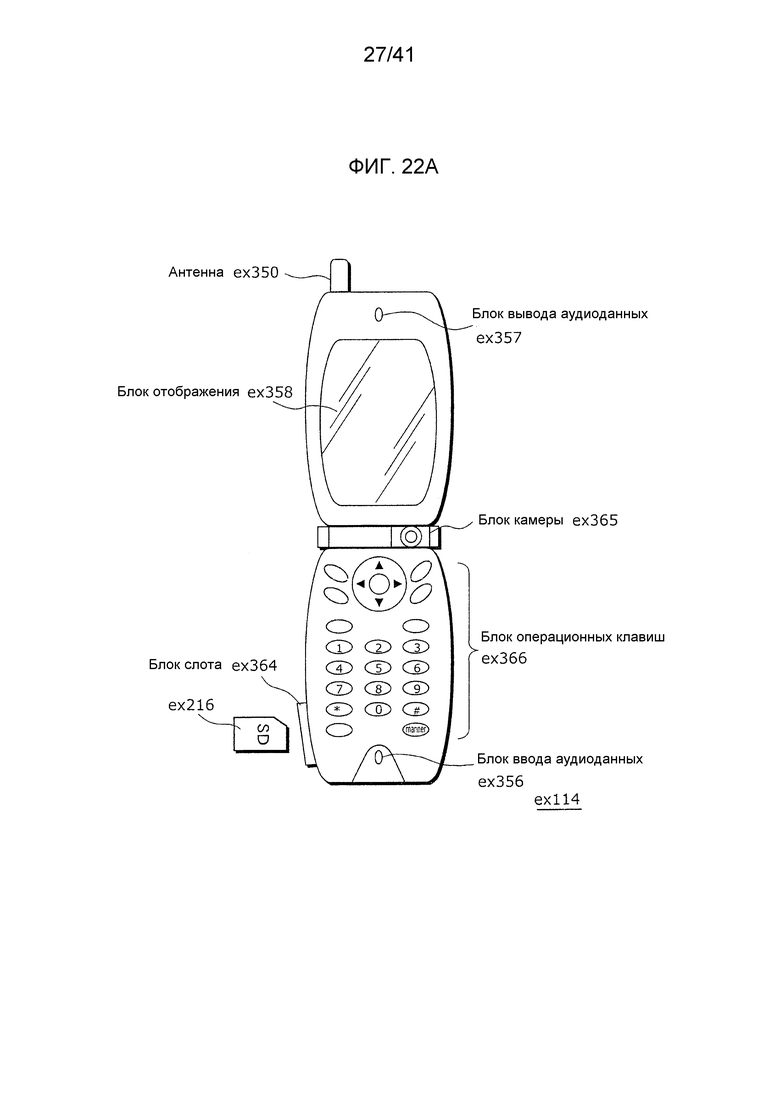

Фиг.22A показывает пример сотового телефона.

Фиг.22B - блок-схема, показывающая пример конфигурации сотового телефона.

Фиг.23 иллюстрирует структуру мультиплексированных данных.

Фиг.24 схематично показывает, каким образом каждый поток мультиплексирован в мультиплексированных данных.

Фиг.25 более подробно показывает, каким образом видеопоток сохранен в потоке пакетов PES.

Фиг.26 показывает структуру пакетов TS и пакетов источника в мультиплексированных данных.

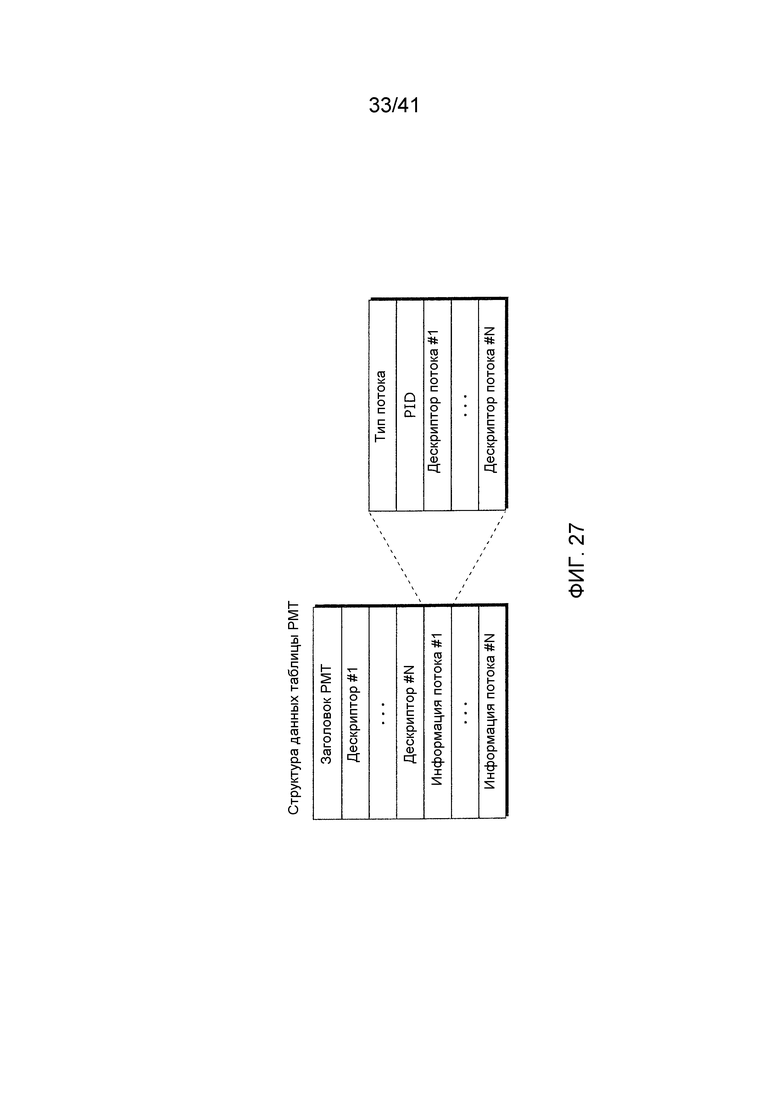

Фиг.27 показывает структуру данных таблицы PMT.

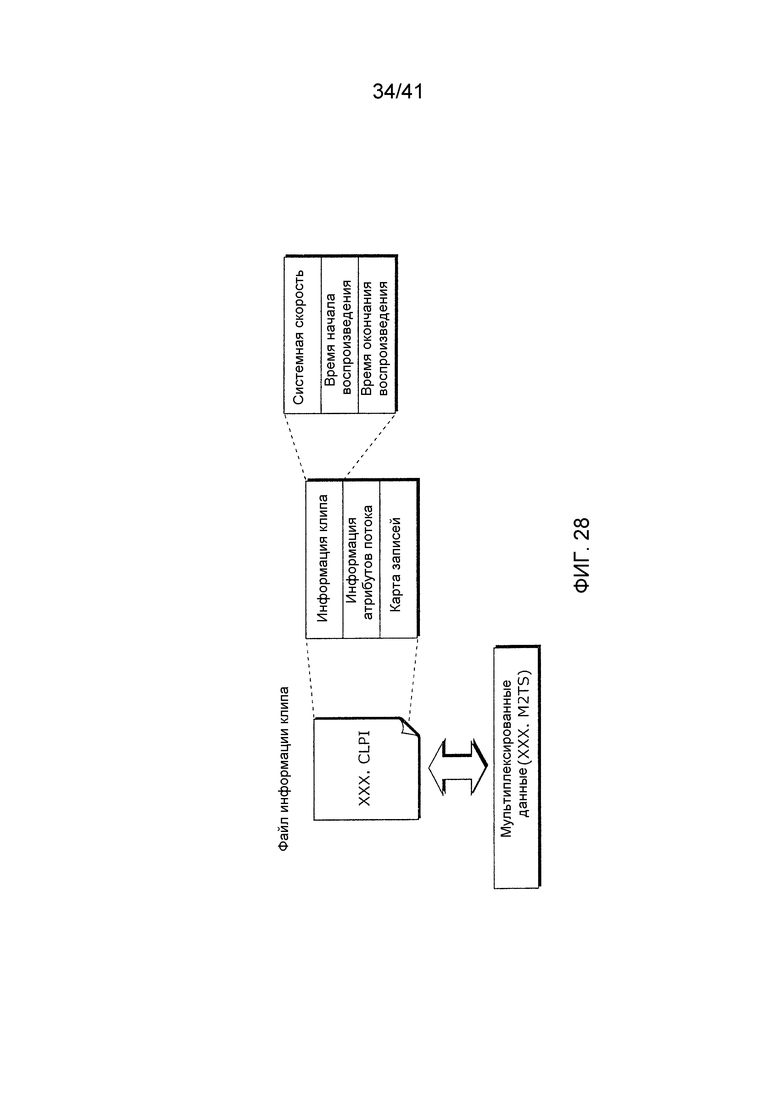

Фиг.28 показывает внутреннюю структуру информации мультиплексированных данных.

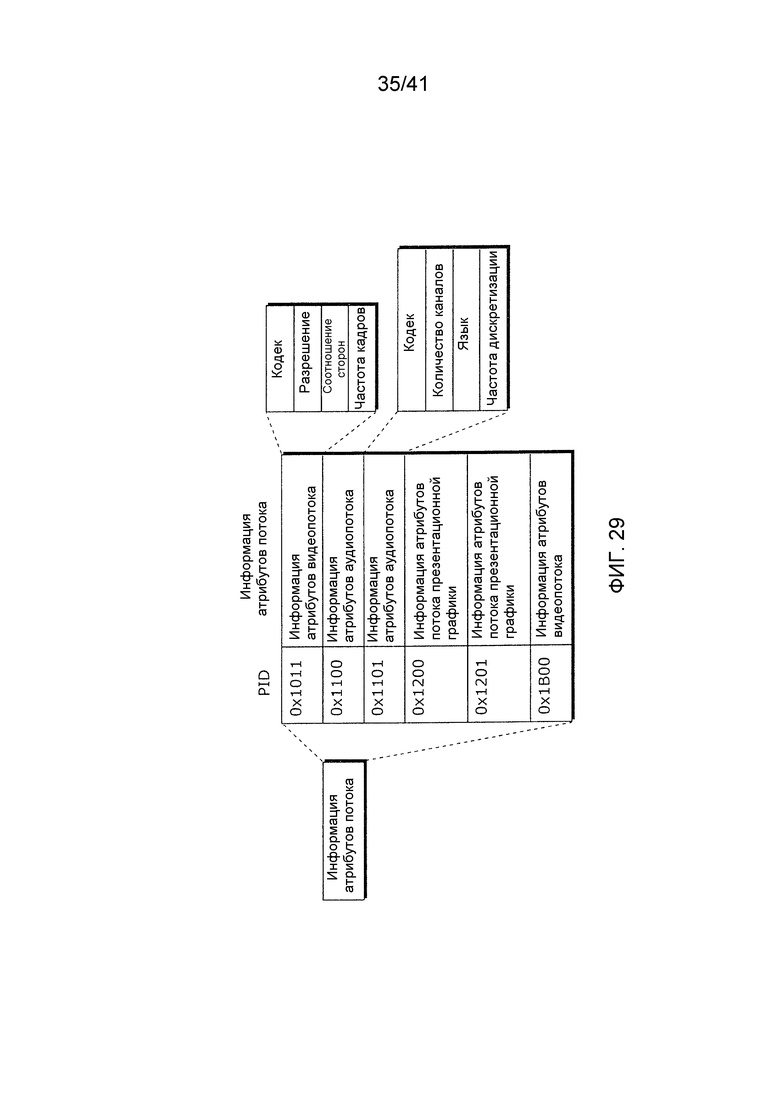

Фиг.29 показывает внутреннюю структуру информации атрибутов потока.

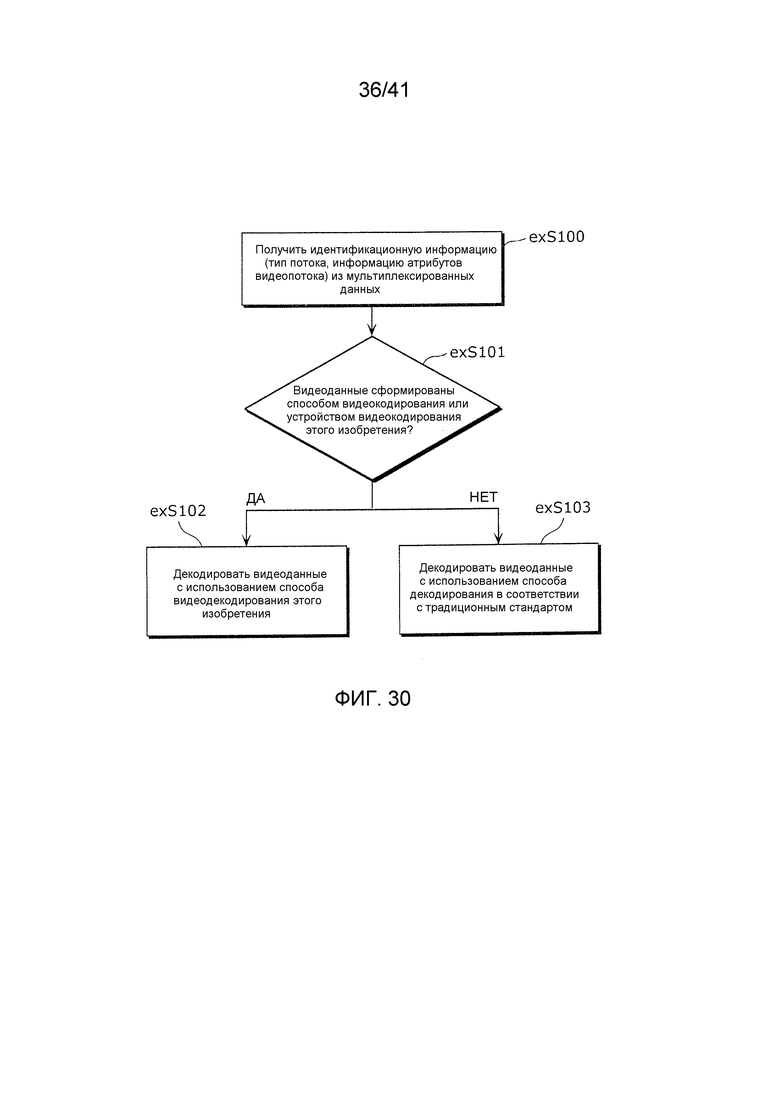

Фиг.30 показывает этапы для идентификации видеоданных.

Фиг.31 показывает пример конфигурации интегральной схемы для реализации способа кодирования движущегося изображения и способа декодирования движущегося изображения в соответствии с каждым из вариантов осуществления.

Фиг.32 показывает конфигурацию для переключения между задающими частотами.

Фиг.33 показывает этапы для идентификации видеоданных и переключения между задающими частотами.

Фиг.34 показывает пример таблицы поиска, в которой стандарты видеоданных соответствуют задающим частотам.

Фиг.35A - схема, показывающая пример конфигурации для совместного использования модуля блока обработки сигналов.

Фиг.35B - схема, показывающая другой пример конфигурации для совместного использования модуля блока обработки сигналов.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

(Основополагающие знания, формирующие базис настоящего изобретения)

Авторы изобретения изложили следующий вопрос относительно арифметического кодирования и арифметического декодирования информации последней позиции в разделе "Уровень техники".

Следует отметить, что в последующем описании информация последней позиции указывает позицию по горизонтали и позицию по вертикали последнего ненулевого коэффициента в предопределенном порядке в текущем блоке. При этом информация последней позиции включает в себя горизонтальную компоненту (именуемую в дальнейшем "компонентой X") и вертикальную компоненту (именуемую в дальнейшем "компонентой Y"). Компонента X указывает позицию по горизонтали в текущем блоке. Компонента Y указывает позицию по вертикали в текущем блоке.

Фиг.1 является блок-схемой, показывающей пример конфигурации устройства 1000 декодирования изображения в соответствии с основополагающим знанием. Фиг.2 является блок-схемой последовательности операций, показывающей пример способа декодирования изображения в соответствии с основополагающим знанием. Как показано, на Фиг.1, устройство 1000 декодирования изображения включает в себя первый блок 1001 декодирования, второй блок 1002 декодирования, блок 1003 управления декодированием и блок 1004 восстановления.

Устройство 1000 декодирования изображения получает битовый поток (BS), который включает в себя информацию последней позиции. Затем устройство 1000 декодирования изображения вводит битовый поток BS в первый блок 1001 декодирования, второй блок 1002 декодирования и блок 1003 управления декодированием.

Блок 1003 управления декодированием выполняет определение, является ли каждый сигнал в полученном битовом потоке BS компонентой X или компонентой Y информации последней позиции.

Первый блок 1001 декодирования арифметически декодирует префиксную часть компоненты X информации последней позиции, включенной в битовый поток BS (этап S1001). Более определенно, первый блок 1001 декодирования арифметически декодирует префиксную часть компоненты X посредством контекстно-адаптивного двоичного арифметического декодирования. При этом префиксная часть является частью двоичного сигнала компоненты X или компоненты Y, которая кодирована посредством контекстно-адаптивного двоичного арифметического кодирования.

Затем первый блок 1001 декодирования определяет, содержит ли двоичный сигнал компоненты X суффиксную часть (этап S1002). Суффиксная часть является частью двоичного сигнала компоненты X или компоненты Y, которая кодирована посредством обходного кодирования.

Префиксная часть и суффиксная часть определяются в соответствии с каждым значением (в дальнейшем называемым также "последним значением") компоненты X и компоненты Y, как показано, например, на Фиг.3A-3D. Таким образом, с помощью предопределенного способа первый блок 1001 декодирования может определить, содержит ли двоичный сигнал компоненты X суффиксную часть.

Более определенно, когда размер блока преобразования (именуемый в дальнейшем "размером преобразования"), например, составляет 4×4, двоичный сигнал компоненты X содержит только префиксную часть и не содержит суффиксную часть независимо от последнего значения, как показано на Фиг.3A. Таким образом, первый блок 1001 декодирования определяет, что двоичный сигнал компоненты X не содержит суффиксную часть, когда размер блока, который должен быть декодирован, составляет 4×4.

В случае, когда размер преобразования составляет 8x8, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X не содержит суффиксную часть, когда какое-либо из значений двоичных символов вплоть до значения двоичного символа 4-го бита двоичного сигнала компоненты X равно "1", как показано на Фиг.3B. С другой стороны, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X содержит суффиксную часть, имеющую фиксированную длину 2 бита, когда значения двоичных символов вплоть до двоичного значения символа 4-го бита двоичного сигнала компоненты X все равны "0".

В случае, когда размер преобразования составляет 16×16, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X не содержит суффиксную часть, когда какое-либо из значений двоичных символов вплоть до значения двоичного символа 8-го бита двоичного сигнала компоненты X равно "1", как показано на Фиг.3C. С другой стороны, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X содержит суффиксную часть, имеющую фиксированную длину 3 бита, когда значения двоичных символов вплоть до значения двоичного символа 8-го бита двоичного сигнала компоненты X все равны "0".

В случае, когда размер преобразования составляет 32x32, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X не содержит суффиксную часть, когда какое-либо из значений двоичных символов вплоть до значения двоичного символа 16-го бита двоичного сигнала компоненты X равно "1", как показано на Фиг.3D. С другой стороны, первый блок 1001 декодирования определяет, что декодируемый двоичный сигнал компоненты X содержит суффиксную часть, имеющую фиксированную длину 4 бита, когда значения двоичного символа вплоть до значения двоичного символа 16-го бита двоичного сигнала компоненты X все равны "0".

При этом, когда двоичный сигнал компоненты X содержит суффиксную часть ("Да" на этапе S1002), второй блок 1002 декодирования арифметически декодирует суффиксную часть, имеющую предопределенную фиксированную длину в битах (этап S1003). Более определенно, второй блок 1002 декодирования декодирует суффиксную часть компоненты X посредством обходного декодирования. С другой стороны, когда двоичный сигнал компоненты X не содержит суффиксную часть ("Нет" на этапе S1002), процесс декодирования для суффиксной части пропускается.

Блок 1004 восстановления восстанавливает компонент X информации последней позиции с использованием префиксной части и суффиксной части, которые декодированы (этап S1004). Более определенно, когда двоичный сигнал компоненты X содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент X посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть и суффиксную часть. С другой стороны, когда двоичный сигнал компоненты X не содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент X посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть.

Затем первый блок 1001 декодирования арифметически декодирует префиксную часть компоненты Y информации последней позиции, как на этапе S1001 (этап S1005). После этого первый блок 1001 декодирования определяет, содержит ли двоичный сигнал компоненты Y суффиксную часть, как на этапе S1002 (этап S1006).

При этом, когда двоичный сигнал компоненты Y содержит суффиксную часть ("Да" на этапе S1006), второй блок 1002 декодирования арифметически декодирует суффиксную часть, имеющую предопределенную фиксированную длину, как на этапе S1003 (этап S1007). С другой стороны, когда двоичный сигнал компоненты Y не содержит суффиксную часть ("Нет" на этапе S1006), процесс декодирования для суффиксной части пропускается.

Наконец, блок 1004 восстановления восстанавливает компонент Y информации последней позиции, как на этапе S1004 (этап S1008). Более определенно, когда двоичный сигнал компоненты Y содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент Y посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть и суффиксную часть. С другой стороны, когда двоичный сигнал компоненты Y не содержит суффиксную часть, блок 1004 восстановления восстанавливает компонент Y посредством преобразования из двоичной формы двоичного сигнала, содержащего декодированную префиксную часть.

Таким образом, восстанавливаются компонент X и компонент Y, содержащиеся в информации последней позиции.

Затем будет описано кодирование переменной длины и декодирование переменной длины. Стандарт H.264 использует контекстно-адаптивное двоичное арифметическое кодирование (CABAC) как один из способов кодирования переменной длины. Префиксная часть кодируется посредством CABAC. Напротив, суффиксная часть кодируется посредством обходного кодирования, которое является арифметическим кодированием, в котором используется фиксированная вероятность (например, "0,5"). Далее контекстно-адаптивное двоичное арифметическое декодирование и обходное декодирование будут описаны с использованием Фиг.4-6.

Фиг.4 является блок-схемой последовательности операций, показывающей контекстно-адаптивное двоичное арифметическое декодирование. Следует отметить, что Фиг.4 была взята из непатентной литературы 1. Если не указано иначе, описание Фиг.4 является таким, которое дано в непатентной литературе 1.

В арифметическом декодировании сначала вводится контекст (ctxIdx), который определяется на основе типа сигнала текущего сигнала, который должен быть декодирован.

Затем на этапе S2001 выполняется следующий процесс.

Сначала вычисляется qCodIRangeIdx из первого параметра codIRange, указывающего текущее состояние арифметического декодирования. Кроме того, получается pStateIdx, который является значением состояния, соответствующим ctxIdx. Затем посредством ссылки на таблицу (rangeTableLPS) получается codIRangeLPS, соответствующий двум значениям (qCodIRangeIdx и pStateIdx).

Следует отметить, что codIRangeLPS указывает состояние арифметического декодирования, когда LPS возник в состоянии арифметического декодирования, указанном первым параметром codIRange. LPS определяет один из символов "0" и "1", который имеет меньшую вероятность возникновения.

Кроме того, codIRange устанавливается равным значению, полученному посредством вычитания упомянутого выше codIRangeLPS из текущего codIRange.

Затем на этапе S2002 выполняется сравнение между codIRange и вторым параметром codIOffset, который указывает состояние арифметического декодирования.

При этом, когда codIOffset больше или равен codIRange ("Да" на этапе S2002), выполняется следующий процесс на этапе S2003.

Сначала определяется, что возник LPS, и binVal, которое является выходным значением декодирования, устанавливается равным значению, отличающемуся от valMPS ("0", когда valMPS = 1, и "1", когда valMPS = 0). Значение valMPS указывает заданное значение MPS ("0" или "1"). Символ MPS определяет одно из значений "0" и "1" двоичного символа, который имеет более высокую вероятность возникновения.

Кроме того, второй параметр codIOffset, который указывает состояние арифметического декодирования, устанавливается равным значению, полученному посредством вычитания codIRange из текущего codIOffset. Кроме того, первый параметр codIRange, который указывает состояние арифметического декодирования, устанавливается равным значению codIRangeLPS, которое было установлено на этапе S2001.

Затем на этапе S2005 определяется, является ли значение pStateIdx равным "0".

При этом, когда значение pStateIdx равно "0" ("Да" на этапе S2005), это означает, что вероятность LPS больше вероятности MPS. Таким образом, значение valMPS переключается (то есть устанавливается "0", когда valMPS = 1, и устанавливается "1", когда valMPS = 0) (этап S2006). С другой стороны, когда значение pStateIdx не равно "0" ("Нет" на этапе S2005), значение pStateIdx обновляется на основе таблицы преобразования transIdxLPS, к которой обращаются, когда возникает символ LPS (этап S2007).

Кроме того, когда codIOffset меньше codIRange ("Нет" на этапе S2002), определяется, что возник символ MPS. Таким образом, значение binVal, которое является выходным значением декодирования, устанавливается равным valMPS, и значение pStateIdx обновляется на основе таблицы преобразования transIdxMPS, к которой обращаются, когда возникает символ MPS (этап S2004).

Наконец, выполняется нормализация (RenormD) (этап S2008), и арифметическое декодирование заканчивается.

Как показано выше, в контекстно-адаптивном двоичном арифметическом декодировании множественные вероятности возникновения символов, которые являются вероятностями возникновения двоичных символов, поддерживаются в связи с индексами контекста. Контексты переключены в соответствии с условием (например, значением смежного блока), и, таким образом, необходимо поддерживать порядок обработки.

Фиг.5 является блок-схемой последовательности операций, показывающей обходное декодирование. Следует отметить, что Фиг.5 была взята из непатентной литературы 1. Если не указано иначе, описание Фиг.5 является таким, которое дано в непатентной литературе 1.

Сначала второй параметр codlOffset, который указывает текущее состояние арифметического декодирования, смещается влево (удваивается). Кроме того, один бит считывается из битового потока, и когда считанный бит равен "1", единица добавляется к codIOffset (этап S3001).

Затем, когда codIOffset больше или равен первому параметру codIRange, который указывает состояние арифметического декодирования ("Да" на этапе S3002), значение binVal, которое является выходным значением декодирования, устанавливается равным "1", и codIOffset устанавливается равным значению, полученному посредством вычитания codIRange из текущего codIOffset (этап S3003). С другой стороны, когда codIOffset меньше первого параметра codIRange, который указывает состояние арифметического декодирования ("Нет" на этапе S3002), значение binVal, которое является выходным значением декодирования, устанавливается равным "0" (этап S3004).

Фиг.6 является блок-схемой последовательности операций для подробного описания нормализации (RenormD), показанной на этапе S2008 на Фиг.4. Фиг.6 была взята из непатентной литературы 1. Если не указано иначе, описание Фиг.6 является таким, которое дано в не патентной литературе 1.

Когда первый параметр codIRange, который указывает состояние арифметического декодирования, стал меньше 0x100 (в шестнадцатеричной системе; 256 в десятичной системе) ("Да" на этапе S4001), codIRange смещается влево (удваивается). Кроме того, второй параметр codIOffset, который указывает состояние арифметического декодирования, смещается влево (удваивается). Кроме того, один бит считывается из битового потока, и когда считанный бит равен "1", единица добавляется к codIOffset (этап S4002).

Когда codIRange в конечном счете достигает 256 или большего значения посредством этого процесса на этапе S4002 ("Нет" на этапе S4001), нормализация заканчивается.

Таким образом выполняется арифметическое декодирование.

Однако соответствующее переключение среди контекстов (моделей контекстов) является трудным при кодировании или декодировании префиксной части посредством контекстно-адаптивного двоичного арифметического кодирования или контекстно-адаптивного двоичного арифметического декодирования. Например, при арифметическом кодировании и арифметическом декодировании префиксной части контексты переключаются в соответствии с битовой позицией в двоичном сигнале. В это время, если контекст является общим для множества битовых позиций для уменьшения требуемой емкости памяти и уменьшения доступа к памяти, идентичный контекст в некоторых случаях используется для битовых позиций, которые существенно отличаются по вероятности возникновения символа. В таком случае точность предсказания вероятности возникновения символа уменьшается, и, таким образом, также уменьшается эффективность кодирования.

С этой целью способ кодирования изображения в соответствии с аспектом настоящего изобретения представляет собой способ кодирования изображения для кодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть кодирован, способ кодирования изображения содержит этапы, на которых: преобразовывают в двоичную форму информацию последней позиции для формирования (i) двоичного сигнала, который включает в себя первый сигнал, имеющий длину, меньшую или равную предопределенной максимальной длине, и не включает в себя второй сигнал или (ii) двоичного сигнала, который включает в себя первый сигнал, имеющий предопределенную максимальную длину, и второй сигнал; выполняют первое кодирование для арифметического кодирования каждого из двоичных символов, включенных в первый сигнал, с использованием контекста, переключенного среди множества контекстов в соответствии с битовой позицией двоичного символа; и выполняют второе кодирование для арифметического кодирования второго сигнала с использованием фиксированной вероятности, когда двоичный сигнал включает в себя второй сигнал, причем при первом кодировании двоичный символ в последней битовой позиции первого сигнала арифметически кодируется с использованием контекста, особого для последней битовой позиции, когда первый сигнал имеет предопределенную максимальную длину.

Двоичный символ в последней битовой позиции первого сигнала указывает, содержит ли двоичный сигнал второй сигнал. Это означает, что двоичный символ в последней битовой позиции первого сигнала имеет большое влияние на эффективность кодирования. Таким образом, двоичный символ в последней битовой позиции первого сигнала имеет признак при возникновении символа, отличающийся от признака двоичных символов в других битовых позициях. С учетом этого возможно увеличить эффективность кодирования посредством арифметического кодирования двоичного символа в последней битовой позиции первого сигнала с использованием контекста, особого для последней битовой позиции.

Например, при первом кодировании каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически кодирован с использованием контекста, общего для этих двух или более битовых позиций.

При этом каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически кодирован с использованием контекста, общего для этих двух или более битовых позиций. Это сокращает количество контекстов по сравнению со случаем использования разных контекстов для каждой битовой позиции, и тем самым может быть уменьшена требуемая емкость памяти.

Например, преобразование в двоичную форму может включать в себя изменение предопределенной максимальной длины в соответствии с размером текущего блока.

При этом максимальная длина первого сигнала может быть различной в соответствии с размером текущего блока, который должен быть кодирован. Это позволяет должным образом установить максимальную длину первого сигнала, тем самым увеличивая эффективность кодирования.

Например, способ кодирования изображения может дополнительно содержать этапы, на которых: переключают процесс кодирования либо на первый процесс кодирования, совместимый с первым стандартом, либо на второй процесс кодирования, совместимый со вторым стандартом; и добавляют к битовому потоку идентификационную информацию, указывающую либо первый стандарт, либо второй стандарт, с которым совместим процесс кодирования, на который выполнено переключение, причем когда процесс кодирования переключен на первый процесс кодирования, преобразование в двоичную форму, первое кодирование и второе кодирование могут быть выполнены как первый процесс кодирования.

Это позволяет переключаться между первым процессом кодирования, совместимым с первым стандартом, и вторым процессом кодирования, совместимым со вторым стандартом.

Кроме того, способ декодирования изображения в соответствии с аспектом настоящего изобретения представляет собой способ декодирования изображения для декодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть декодирован, способ декодирования изображения содержит этапы, на которых: выполняют первое декодирование для арифметического декодирования каждого из двоичных символов, включенных в первый сигнал, с использованием контекста, переключенного среди множества контекстов в соответствии с битовой позицией двоичного символа, первый сигнал включен в двоичный сигнал информации последней позиции и имеет длину, меньшую или равную предопределенной максимальной длине; и выполняют второе декодирование, когда двоичный сигнал информации последней позиции включает в себя второй сигнал, для арифметического декодирования второго сигнала с использованием фиксированной вероятности, причем при первом декодировании двоичный символ в последней битовой позиции первого сигнала арифметически декодируется с использованием контекста, особого для последней битовой позиции, когда первый сигнал имеет предопределенную максимальную длину.

Двоичный символ в последней битовой позиции первого сигнала указывает, содержит ли двоичный сигнал второй сигнал. Это означает, что двоичный символ в последней битовой позиции первого сигнала имеет большое влияние на эффективность кодирования. Таким образом, двоичный символ в последней битовой позиции первого сигнала имеет признак возникновения значения, отличающийся от признака двоичных символов в других битовых позициях. С учетом этого возможно увеличить эффективность кодирования посредством арифметического декодирования двоичного символа в последней битовой позиции первого сигнала с использованием контекста, особого для последней битовой позиции.

Например, при первом декодировании каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически декодирован с использованием контекста, общего для этих двух или более битовых позиций.

При этом каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции, первого сигнала может быть арифметически декодирован с использованием контекста, общего для этих двух или более битовых позиций. Это сокращает количество контекстов по сравнению со случаем использования разного контекста для каждой битовой позиции, и тем самым может быть уменьшена требуемая емкость памяти.

Например, предопределенная максимальная длина может изменяться в соответствии с размером текущего блока.

При этом максимальная длина первого сигнала может быть различной в соответствии с размером текущего блока, который должен быть декодирован. Это позволяет должным образом установить максимальную длину первого сигнала, тем самым увеличивая эффективность кодирования.

Например, способ декодирования изображения может дополнительно содержать этап, на котором переключают процесс декодирования либо на первый процесс декодирования, совместимый с первым стандартом, либо на второй процесс декодирования, совместимый со вторым стандартом, в соответствии с идентификационной информации, которая добавлена к битовому потоку и указывает либо первый стандарт, либо второй стандарт, причем когда процесс декодирования переключен на первый процесс декодирования, первое декодирование и второе декодирование могут быть выполнены как первый процесс декодирования.

Это позволяет переключаться между первым процессом декодирования, совместимым с первым стандартом, и вторым процессом декодирования, совместимым со вторым стандартом.

Следует отметить, что эти общие и частные аспекты могут быть реализованы с использованием системы, устройства, интегральной схемы, компьютерной программы или считываемого компьютером носителя записи, такого как компакт-диск (CD-ROM), или любой комбинации систем, устройств, интегральных схем, компьютерных программ или считываемых компьютером носителей записи.

Далее будут подробно описаны варианты осуществления с использованием чертежей.

Следует отметить, что каждый из описанных ниже вариантов осуществления показывает общий или частный пример. Численные значения, формы, материалы, структурные элементы, размещение и соединение структурных элементов, этапов, порядок обработки этапов и т.д., показанный в следующих вариантах осуществления, являются лишь примерами и, таким образом, не предназначены для ограничения объема формулы изобретения. Кроме того, среди структурных элементов в следующих вариантах осуществления структурные элементы, не упомянутые в каком-либо из независимых пунктов формулы изобретения, представляющих наиболее универсальные концепции, описаны как произвольные структурные элементы.

(Вариант осуществления 1)

Фиг.7 является блок-схемой, показывающей функциональную конфигурацию устройства 100 декодирования изображения в соответствии с вариантом осуществления 1. Устройство декодирования 100 изображения декодирует информацию последней позиции.

Как показано на Фиг.7, устройство 100 декодирования изображения включает в себя блок 110 арифметического декодирования и блок 104 восстановления. Блок 110 арифметического декодирования включает в себя первый блок 101 декодирования, второй блок 102 декодирования и блок 103 управления декодированием.

Устройство 100 декодирования изображения получает битовый поток BS, который включает в себя кодированную информацию последней позиции.

Первый блок 101 декодирования арифметически декодирует каждый двоичный символ, включенный в первый сигнал, который включен в двоичный сигнал информации последней позиции, с использованием контекста, переключаемого среди множества контекстов в соответствии с битовой позиции двоичного символа. Другими словами, первый блок 101 декодирования декодирует первый сигнал посредством контекстно-адаптивного двоичного арифметического декодирования.

Первый сигнал является частью двоичного сигнала информации последней позиции, которая была арифметически кодирована с использованием контекста, переключаемого среди множества контекстов. Первый сигнал имеет длину, меньшую или равную предопределенной максимальной длине. Первый сигнал, например, соответствует префиксной части.

При этом, когда первый сигнал имеет предопределенную максимальную длину, первый блок 101 декодирования арифметически декодирует двоичный символ в последней битовой позиции первого сигнала с использованием контекста, особого для последней битовой позиции. Другими словами, первый блок 101 декодирования арифметически декодирует двоичный символ в последней битовой позиции первого сигнала с использованием контекста, отличающегося от контекстов, используемых для арифметического декодирования двоичных символов в других битовых позициях.

Например, когда префиксная часть, соответствующая последнему значению "7", показанному на Фиг.3C, должно быть декодировано, первый блок 101 декодирования арифметически декодирует двоичный символ 8-ого бита с использованием контекста, особого для двоичного символа 8-ого бита. Другими словами, первый блок 101 декодирования арифметически декодирует двоичный символ 8-ого бита, используя в качестве контекста для битовой позиции 8-ого бита контекст, отличающийся от контекстов для битовых позиций с 1-ого по 7-ой биты.

Когда двоичный сигнал информации последней позиции включает в себя второй сигнал, второй блок 102 декодирования арифметически декодирует второй сигнал с использованием фиксированной вероятности. Другими словами, второй блок 102 декодирования декодирует второй сигнал посредством обходного декодирования.

Второй сигнал является частью двоичного сигнала информации последней позиции, которая была арифметически кодирована с использованием фиксированной вероятности. Второй сигнал, например, соответствует суффиксной части.

Блок 103 управления декодированием для каждой части битового потока BS определяет, является ли часть компонентой X или компонентой Y информации последней позиции. Следует отметить, что нет необходимости включать блок 103 управления декодированием в блок 110 арифметического декодирования. То есть устройство 100 декодирования изображения не обязательно должно включать в себя блок 103 управления декодированием.

Блок 104 восстановления восстанавливает горизонтальный компонент или вертикальный компонент, включенный в информацию последней позиции, посредством преобразования из двоичной формы (i) двоичного сигнала, который содержит первый сигнал и не содержит второй сигнал, или (ii) двоичного сигнала, который содержит первый сигнал и второй сигнал.

Далее с использованием Фиг.8A и Фиг.8B подробно описываются операции устройства 100 декодирования изображения, имеющего описанную выше конфигурацию. Далее описан случай, в котором первый сигнал является префиксной частью, и второй сигнал является суффиксной частью.

Фиг.8A является блок-схемой последовательности операций, показывающей пример операций обработки устройства 100 декодирования изображения в соответствии с вариантом осуществления 1. Как показано на Фиг.8A, префиксная часть компоненты X, суффиксная часть компоненты X, префиксная часть компоненты Y и суффиксная часть компоненты Y кодированы и помещены в битовый поток BS в этом порядке. Следует отметить, что в некоторых случаях суффиксная часть каждой компоненты не включена в битовый поток BS в зависимости от значения компоненты.

Сначала первый блок 101 декодирования декодирует из битового потока BS кодированную префиксную часть компоненты X посредством контекстно-адаптивного двоичного арифметического декодирования (этап S101). Например, первый блок 101 декодирования бит за битом арифметически декодирует кодированную префиксную часть, пока не будет достигнута предопределенная максимальная длина или пока не будет декодировано значение "1". Следует отметить, что переключение контекста будет описано позже.

Затем первый блок 101 декодирования определяет, содержит ли двоичный сигнал компоненты X суффиксную часть (этап S102). Например, первый блок 101 декодирования определяет, что двоичный сигнал компоненты X содержит суффиксную часть, когда префиксная части имеет предопределенную максимальную длину, и значения двоичного символа, включенные в префиксную часть, все равны "0".

Следует отметить, что максимальная длина префиксной части предопределена, например, в соответствии с размером преобразования. Например, максимальная длина префиксной части определена таким образом, как показано на Фиг.9B или Фиг.9C.

При этом, когда двоичный сигнал компоненты X содержит суффиксную часть ("Да" на этапе S102), второй блок 102 декодирования декодирует кодированную суффиксную часть компоненты X посредством обходного декодирования (этап S103). С другой стороны, когда двоичный сигнал компоненты X не содержит суффиксную часть ("Нет" на этапе S102), этап S103 пропускается.

Затем блок 104 восстановления восстанавливает компонент X информации последней позиции посредством преобразования из двоичной формы двоичного сигнала компоненты X, который содержит и префиксную часть, и суффиксную часть, или который содержит только префиксную часть (этап S104).

После этого первый блок 101 декодирования декодирует из битового потока BS кодированную префиксную часть компоненты Y посредством контекстно-адаптивного двоичного арифметического декодирования (этап S105). Более определенно, первый блок 1001 декодирования декодирует префиксную часть компоненты Y таким же образом, как при декодировании префиксной части компоненты X.

Затем первый блок 101 декодирования определяет, содержит ли двоичный сигнал компоненты Y суффиксную часть (этап S106). Более определенно, первый блок 101 декодирования определяет, содержит ли двоичный сигнал компоненты Y суффиксную часть таким же образом, как при определении того, содержит ли двоичный сигнал компоненты X суффиксную часть.

При этом, когда двоичный сигнал компоненты Y содержит суффиксную часть ("Да" на этапе S106), второй блок 102 декодирования декодирует кодированную суффиксную часть компоненты Y посредством обходного декодирования (этап S107). С другой стороны, когда двоичный сигнал компоненты Y не содержит суффиксную часть ("Нет" на этапе S106), этап S107 пропускается.

Наконец, блок 104 восстановления восстанавливает компонент Y информации последней позиции посредством преобразования из двоичной формы двоичного сигнала компоненты Y, который содержит и префиксную часть, и суффиксную часть, или который содержит только префиксную часть (этап S108).

Далее описывается случай, в котором префиксная часть и суффиксная часть каждой компоненты помещены в битовый поток в порядке, отличающемся от показанного на Фиг.8A.

Фиг.8B является блок-схемой последовательности операций, показывающей другой пример операций обработки устройства 100 декодирования изображения в соответствии с вариантом осуществления 1. Следует отметить, что на Фиг.8B процессы, выполняемые на этапах, обозначенных такими же знаками для ссылок, как на Фиг.8A, в основном являются такими же, как процессы, описанные на Фиг.8A. Кроме того, при этом предполагается, что флаг суффикса "выключен" по умолчанию. Следует отметить, что флаг суффикса является внутренним флагом, указывающим, содержит ли двоичный сигнал компоненты X информации последней позиции суффиксную часть.

Как показано на Фиг.8B, префиксная часть компоненты X, префиксная часть компоненты Y, суффиксная часть компоненты Y и суффиксная часть компоненты X кодированы и помещены в битовый поток BS в таком порядке. Следует отметить что в некоторых случаях суффиксная часть каждой компоненты не включена в битовый поток BS в зависимости от значения компоненты, как в случае на Фиг.8A.

Сначала первый блок 101 декодирования декодирует кодированную префиксную часть компоненты X посредством контекстно-адаптивного двоичного арифметического декодирования (этап S101). Затем первый блок 101 декодирования определяет, содержит ли двоичный сигнал компоненты X суффиксную часть (этап S102). При этом, когда двоичный сигнал компоненты X содержит суффиксную часть ("Да" на этапе S102), первый блок 101 декодирования устанавливает флаг суффикса в значение "включен" (этап S111).

С другой стороны, когда двоичный сигнал компоненты X не содержит суффиксную часть ("Нет" на этапе S102), первый блок 101 декодирования не устанавливает флаг суффикса равным значению "включен". Другими словами, флаг суффикса остается "выключен", что является значением по умолчанию. Следует отметить, что первый блок 101 декодирования может в этот момент установить флаг суффикса равным значению "выключен".

Затем с этапа S105 до этапа S108 процесс, относящийся к компоненте Y, выполняется таким же образом, как на Фиг.8A.

После этого второй блок 102 декодирования определяет, "включен" ли флаг суффикса (этап S112). При этом, когда флаг суффикса "включен" ("Да" на этапе S112), второй блок 102 декодирования декодирует суффиксную часть компоненты X посредством обходного декодирования (этап S103). С другой стороны, когда флаг суффикса не "включен" ("Нет" на этапе S112), этап S103 пропускается.

Наконец, блок 104 восстановления восстанавливает компонент X информации последней позиции посредством преобразования из двоичной формы двоичного сигнала компоненты X, которая содержит и префиксную часть, и суффиксную часть, или которая содержит только префиксную часть (этап S104).

Последовательное декодирование префиксных частей компоненты X и компоненты Y и последовательное декодирование суффиксных частей компоненты X и компоненты Y таким образом позволяют уменьшить количество раз, которое переключаются способы арифметического декодирования (контекстно-адаптивное двоичное арифметическое декодирование и обходное декодирование). Это позволяет блоку 110 арифметического декодирования эффективно выполнять арифметическое декодирование кодированной информации последней позиции.

Кроме того, последовательное декодирование суффиксных частей компоненты X и компоненты Y облегчает параллельное выполнение для обходного декодирования, тем самым увеличивая скорость обработки.

Кроме того, последовательное декодирование префиксной части и суффиксной части компоненты Y избавляет от необходимости устанавливать флаг суффикса для компоненты Y. Другими словами, емкость требуемой памяти может быть уменьшена по сравнению со случаем декодирования префиксной части компоненты X, префиксной части компоненты Y, суффиксной части компоненты X и суффиксной части компоненты Y в этом порядке.

Затем описывается пример процесса декодирования в отношении кодированных суффиксных частей компоненты X и компоненты Y (этапы S108 и S111). Здесь описан случай, в котором суффиксные части преобразованы в двоичную форму посредством кодирования Голомба-Райса.

В кодировании Голомба-Райса длина каждой суффиксной части не является фиксированной. Суффиксная часть может быть разделена на две части, первую половину и вторую половину.

Вторая половина является частью фиксированной длины, имеющей длину, указанную посредством параметра Райса (именуемого в дальнейшем "RP").

Первая половина может быть представлена посредством: значения "1", которое увеличивается кратно числу, представимому посредством 2 в степени RP (2RP) (например, кратно "4", когда RP=2); и значения "0", которое установлено в последней битовой позиции. Более определенно, когда RP=2, длина первой половины увеличивается на 1 бит для каждых четырех (2 в степени RP) значений следующим образом: 0, 0, 0, 0, 10, 10, 10, 10, 110, 110, 110, 110,...

Следует отметить, что при этом количество информации, которая должна быть представлена суффиксной частью, является известным, и, таким образом, возможно опустить последний "0" из первой половины, когда первая половина имеет максимальную длину. Например, когда RP=2, и максимальное количество информации равно 12, первая половина может быть представлена любым числом из 0, 0, 0, 0, 10, 10, 10, 10, 11, 11, 11 и 11. Опуская таким образом последний "0" из первой половины, количество кодированной информации двоичного сигнала может быть уменьшено на 1 бит.

Максимальное количество информации может быть представлено разницей между длиной размера преобразования и длиной префиксной части. Это сокращает избыточный бит(ы).

Достаточно, чтобы параметр RP являлся предопределенным в соответствии с размером преобразования, как показано, например, на Фиг.9D или Фиг.9E. Это позволяет представить суффиксную часть с помощью двоичного сигнала, имеющего длину, адаптированную к размеру преобразования, и, таким образом, эффективность кодирования может быть увеличена.

Далее с использованием Фиг.9A описаны операции второго блока 102 декодирования для декодирования суффиксной части, преобразованной в двоичную форму посредством кодирования Голомба-Райса, как описано выше. Фиг.9A является блок-схемой последовательности операций, показывающей пример операций обработки второго блока 102 декодирования в соответствии с вариантом осуществления 1.

Сначала второй блок 102 декодирования устанавливает значение RP (этап S201). Более определенно, второй блок 102 декодирования, например, обращается к предопределенной таблице для установки значения RP. Предопределенная таблица в этом случае является таблицей, например, показанной на Фиг.9D или Фиг.9E.

Следует отметить, что второй блок 102 декодирования может установить значение RP без обращения к таблице. Настройка значения RP будет подробно описана ниже по тексту с использованием Фиг.10A-10D.

Затем второй блок 102 декодирования устанавливает значение Max (этап S202). При этом значение Max указывает максимальное значение длины первой половины кода Голомба-Райса. Более определенно, значение Max указывает самую маленькую длину двоичного сигнала, который может представлять значение, полученное посредством вычитания максимальной длины префиксной части из максимального значения последнего значения. Таким образом, второй блок 102 декодирования получает значение Max посредством (i) вычитания длины префиксной части из максимального значения последнего значения и (ii) деления полученного в результате значения на 2 в степени RP или выполнения операции сдвига вправо в отношении полученного в результате значения на RP бит (битов).

Следует отметить, что максимальная длина префиксной части может различаться в соответствии с размером преобразования, как показано на Фиг.9B или Фиг.9C.

Затем второй блок 102 декодирования декодирует из битового потока BS сигнал, соответствующий 1 биту кода Голомба-Райса посредством обходного декодирования и увеличивает значение счетчика (по умолчанию "0") на 1 (этап S203).

При этом, когда декодированный сигнал, соответствующий 1 биту, равен "0" ("Да" на этапе S204), декодирование первой половины кода Голомба-Райса заканчивается, и процесс переходит на этап S206.

С другой стороны, когда декодированный сигнал не равен "0" (когда декодированный сигнал равен "1") ("Нет" на этапе S204), определяется, равно ли значение счетчика значению Max (этап S205). При этом, когда значение счетчика не равно значению Max ("Нет" на этапе S205), процесс возвращается на этап S203. Более определенно, второй блок 102 декодирования декодирует сигнал, соответствующий следующему 1 биту кода Голомба-Райса посредством обходного декодирования.

С другой стороны, когда значение счетчика равно значению Max ("Да" на этапе S205), декодирование первой половины суффиксной части заканчивается, и процесс переходит на этап S206.

Затем второй блок 102 декодирования декодирует вторую половину кода Голомба-Райса (двоичного сигнала, имеющего фиксированную длину бита (битов) RP) посредством обходного декодирования (этап S206).

Наконец, второй блок 102 декодирования восстанавливает значение, представленное посредством кодирования Голомба-Райса (этап S207). При этом значение восстанавливается посредством сложения второй половины кода Голомба-Райса и значения, полученного посредством смещения влево на бит (биты) RP, значения, полученного посредством вычитания 1 из значения, представленного первой половиной кода Голомба-Райса.

Следует отметить, что в некоторых случаях значение двоичного сигнала второй половины преобразовано в двоичную форму в виде инвертированного значения. В таких случаях второй блок 102 декодирования выполняет восстановление с этой принятой во внимание инверсией. Следует отметить, что достаточно, чтобы устройство декодирования и устройство кодирования определяли заранее, должно ли значение двоичного сигнала быть инвертировано. Ни на эффективность кодирования, ни на нагрузку обработки не влияет, инвертировано ли значение двоичного сигнала.

Затем с использованием Фиг.10A-10D описывается способ определения значения RP и максимальной длины префиксной части.

Фиг.10A показывает способ определения значения RP и максимальной длины префиксной части в соответствии с размером преобразования.

Сначала второй блок 102 декодирования получает размер преобразования (этап S301). Затем второй блок 102 декодирования обращается к таблице, показанной на Фиг.9D или Фиг.9E, указывающей соотношение между размером преобразования и значением RP, для определения значения RP, соответствующего полученному размеру преобразования (этап S302). Кроме того, второй блок 102 декодирования обращается к таблице, показанной на Фиг.9B или Фиг.9C, указывающей соотношение между размером преобразования и максимальной длиной префиксной части, для определения максимальной длины префиксной части (этап S303).

Фиг.10B показывает способ определения значения RP и максимальной длины префиксной части в соответствии с информацией предсказания.

Сначала второй блок 102 декодирования получает информацию предсказания (этап S311). Информация предсказания является информацией, имеющей отношение к предсказанию блока преобразования, являющегося текущим блоком, который должен быть декодирован. Например, информация предсказания указывает, должен ли блок преобразования быть декодирован посредством внутреннего предсказания или внешнего предсказания. Кроме того, например, информация предсказания может являться информацией, указывающей направление предсказания во внутреннем предсказании.

Затем второй блок 102 декодирования определяет значение RP на основе информации предсказания (этап S312). Например, известно, что в случае внешнего предсказания обычно имеется меньше высокочастотных компонент, чем во внутреннем предсказании. Таким образом, когда информация предсказания указывает внешнее предсказание, достаточно, чтобы второй блок 102 декодирования определял такое значение RP, которое позволяет компоненте X и компоненте Y, имеющим маленькие значения, быть представленным короткими двоичными сигналами. Более определенно, когда информация предсказания указывает внешнее предсказание, достаточно, чтобы второй блок 102 декодирования определял значение RP, меньшее, чем значение RP, определенное, когда информация предсказания указывает внутреннее предсказание.

Кроме того, когда направлением внутреннего предсказания является горизонтальное направление, обычно ожидается, что компонента Y информации последней позиции меньше, чем компонента X. Ввиду этого, когда направлением предсказания внутреннего предсказания является горизонтальное направление, достаточно, чтобы второй блок 102 декодирования определял в качестве значения RP компоненты Y значение RP, меньшее, чем значение RP компоненты X. Следует отметить это, когда направлением предсказания внутреннего предсказания является вертикальное направление, достаточно, чтобы второй блок 102 декодирования определял в качестве значения RP компоненты X, значение RP, меньшее, чем значение RP компоненты Y.

Наконец, второй блок 102 декодирования определяет максимальную длину префиксной части на основе информации предсказания (этап S313).

Как описано выше, второй блок 102 декодирования может изменять длину кода двоичного сигнала в соответствии с информацией предсказания, и тем самым эффективность кодирования может быть увеличена.

Фиг.10C показывает способ определения значения RP и максимальной длины префиксной части в соответствии со статистической информацией.

Сначала второй блок 102 декодирования получает статистическую информацию (этап S321). Статистическая информация является, например, информацией о статистике длины двоичного сигнала компоненты X или компоненты Y, включенных в информацию последней позиции ранее декодированного блока.

Затем второй блок 102 декодирования определяет значение RP на основе статистической информации (этап S322). Наконец, второй блок 102 декодирования определяет максимальную длину префиксной части на основе статистической информации (этап S323).

Как описано выше, второй блок 102 декодирования может изменять длину кода двоичного сигнала в соответствии со статистической информацией, и тем самым эффективность кодирования может быть дополнительно увеличена.

Фиг.10D показывает способ определения значения RP и максимальной длины префиксной части в соответствии с ранее декодированной одной из компоненты X и компоненты Y.

Сначала второй блок 102 декодирования получает ранее декодированную одну из компоненты X и компоненты Y (этап S331). Например, второй блок 102 декодирования получает ранее декодированную компоненту X при декодировании кодированной компоненты Y. Кроме того, например, второй блок 102 декодирования может получить ранее декодированную компоненту Y при декодировании кодированной компоненты X.

Затем второй блок 102 декодирования определяет с использованием ранее декодированной одной из компоненты X и компоненты Y значение RP другой, предназначенной для декодирования одной из компоненты X и компоненты Y (этап S332). Обычно вероятно, что компонента X и компонента Y имеют одинаковые или подобные значения. Поэтому, когда значение ранее декодированной компоненты X, например, меньше, чем некоторое значение (например, половина размера преобразования), второй блок 102 декодирования определяет в качестве значения RP компоненты Y значение, меньшее, чем значение RP компоненты X.

Наконец, второй блок 102 декодирования определяет с использованием ранее декодированной одной из компоненты X и компоненты Y максимальную длину префиксной части другой, предназначенной для декодирования одной из компоненты X и компоненты Y (этап S333).

Как описано выше, второй блок 102 декодирования может изменить длину кода двоичного сигнала в соответствии с ранее декодированной одной из компоненты X и компоненты Y, и тем самым эффективность кодирования может быть дополнительно увеличена.

Следует отметить, что способы определения значения RP и максимальной длины префиксной части, показанные на Фиг.10A-10D, могут использоваться в комбинации. Например, когда нет информации, к которой можно обратиться, второй блок 102 декодирования может определить значение RP на основе предопределенной таблицы, тогда как если имеется информация, к которой можно обратиться, второй блок 102 декодирования может определить значение RP в соответствии с информацией, к которой можно обратиться.

Кроме того, второй блок 102 декодирования может определить максимальную длину префиксной части таким же образом, как значение RP. Следует отметить, что когда предсказано, что значения компоненты X и компоненты Y являются большими, достаточно, чтобы второй блок 102 декодирования определил максимальную длину префиксной части более короткой, чем когда компонента X и компонента Y предсказаны маленькими. Уменьшение длины префикса таким образом сокращает количество необходимых контекстов.

Далее описываются контексты, используемые для декодирования информации последней позиции посредством контекстно-адаптивного двоичного арифметического декодирования.

Фиг.11A является схемой, показывающей пример соотношения между битовыми позициями и контекстами в соответствии с вариантом осуществления 1. Фиг.11B является схемой, показывающей пример соотношения между битовыми позициями и контекстами в соответствии со сравнительным примером.

Фиг.11A и Фиг.11B показывают соотношение между битовыми позициями и контекстами для четырех типов размера преобразования (4×4, 8×8, 16×16 и 32×32). На Фиг.11A и Фиг.11B прямоугольные блоки, расположенные в горизонтальном направлении, соответствуют битовым позициям 1-го бита, 2-го бита, 3-го бита и так далее в последовательности слева. Кроме того, числовое значение в каждом блоке представляет собой индексное значение контекста, используемого для получения вероятности, которая должна быть использована при декодировании двоичного символа в этой битовой позиции.

На Фиг.11A имеется 16 типов (от 0 до 15) контекстов, используемых при декодировании префиксной части. Кроме того, на Фиг.11A максимальная длина префиксной части составляет "3", "4", "4" и "8" для размера преобразования 4×4, 8×8, 16×16 и 32×32, соответственно.

Что касается Фиг.11A, когда размер преобразования составляет, например, 8×8, значение вероятности, полученное из контекста, идентифицированного индексным значением "3", используется в качестве значения вероятности для декодирования двоичного символа 1-го бита префиксной части. Аналогичным образом, значение вероятности, полученное из контекста, идентифицированного индексным значением "4", используется в качестве значения вероятности для декодирования двоичных символов 2-го бита и 3-го бита. Аналогичным образом, значение вероятности, полученное для контекста, идентифицированного индексным значением "5", используется в качестве значения вероятности для декодирования двоичного символа 4-го бита.

Таким образом, как показано на Фиг.11A, двоичный символ в последней битовой позиции префиксной части арифметически декодируется с использованием контекста, особого для последней битовой позиции. Другими словами, контекст для последней битовой позиции является контекстом, отличающимся от контекстов для других битовых позиций.

Двоичный символ в последней битовой позиции префиксной части указывает, содержит ли двоичный сигнал компоненты X или компоненты Y суффиксную часть. Это означает, что двоичный символ в последней битовой позиции префиксной части имеет большое влияние эффективность кодирования. Таким образом, двоичный символ в последней битовой позиции префиксной части имеет признак возникновения символа, отличающийся от такового двоичных символов в других битовых позициях. Ввиду этого эффективность кодирования может быть увеличена посредством декодирования двоичного символа в последней битовой позиции префиксной части с использованием контекста, особого для последней битовой позиции.

Кроме того, контекст может быть общим для множества битовых позиций, таких как битовые позиции 2-го бита и 3-го бита для размера преобразования 8×8 или битовые позиции с 5-го бита по 7-ой бит для размера преобразования 32×32 на Фиг.11A. Другими словами, каждый из двоичных символов в двух или более битовых позициях, отличных от последней битовой позиции префиксной части может быть арифметически декодирован с использованием контекста, общего для этих двух или более битовых позиций.

Это сокращает количество контекстов по сравнению со случаем использования разных контекстов для каждой битовой позиции, и тем самым требуемая емкость памяти может быть уменьшена.

Следует отметить, что хотя на фиг 11A двоичный символ в последней битовой позиции префиксной части декодируется с использованием контекста, особого для последней битовой позиции, для всех предопределенных размеров преобразования, двоичный символ в последней битовой позиции не обязательно должен быть декодирован таким образом для всех размеров преобразования. Другими словами, контекст может быть общим для последней битовой позиции и другой битовой позиции префиксной части для некоторых из размеров преобразования.

Например, когда суффиксная часть имеет фиксированную длину 1 бит, контекст может быть общим для последней битовой позиции префиксной части и битовой позиции, непосредственно предшествующей последней битовой позиции.

Это обеспечивает возможность устойчивой оценки вероятности, даже когда, например, битовый поток содержит несколько префиксных частей, имеющих предопределенную максимальную длину. Например, эффективность кодирования может быть увеличена в случае, когда последняя позиция динамически изменяется с длиной кода, принимаемой во внимание во время кодирования.

Как описано на данный момент, устройство 100 декодирования изображения в соответствии с настоящим вариантом осуществления может арифметически декодировать двоичный символ в последней битовой позиции первого сигнала с использованием контекста, особого для последней битовой позиции. То есть устройство 100 декодирования изображения может арифметически декодировать информацию последней позиции с использованием контекста, соответствующим образом переключенного среди множества контекстов, и тем самым эффективность кодирования может быть увеличена.

Следует отметить, что значения RP и максимальные длины префиксной части, показанные на Фиг.9B-9E, являются лишь примерами, и могут быть другие значения RP и другие максимальные длины префиксной части. Например, максимальная длина префиксной части может быть короче, и суффиксная часть может быть длиннее. Это дополнительно обеспечивает возможность параллельного арифметического декодирования и дополнительно увеличивает скорость арифметического декодирования.

Следует отметить, что каждый из структурных элементов в настоящем варианте осуществления может быть выполнен в виде отдельного аппаратного продукта или может быть реализован посредством исполнения программы, подходящей для структурного элемента. Каждый структурный элемент может быть реализован посредством исполняющего программы блока, такого как центральный процессор или процессор, считывающий и исполняющий программу программного обеспечения, записанную на носителе записи, таком как жесткий диск или полупроводниковая память. При этом программа программного обеспечения для реализации устройства декодирования изображения в соответствии с настоящим вариантом осуществления является описанной ниже программой.

Эта программа заставляет компьютер исполнять способ декодирования изображения для декодирования информации последней позиции, указывающей позицию последнего ненулевого коэффициента в предопределенном порядке в текущем блоке, который должен быть декодирован, способ декодирования изображения содержит этапы, на которых: выполняют первое декодирование для арифметического декодирования каждого из двоичных символов, включенных в первый сигнал, с использованием контекста, переключенного среди множества контекстов в соответствии с битовой позицией двоичного символа, первый сигнал включен в двоичный сигнал информации последней позиции и имеет длину, меньшую или равную предопределенной максимальной длине; и выполняют второе декодирование, когда двоичный сигнал информации последней позиции включает в себя второй сигнал, для арифметического декодирования второго сигнала с использованием фиксированной вероятности, причем при первом декодировании двоичный символ в последней битовой позиции первого сигнала арифметически декодируется с использованием контекста, особого для последней битовой позиции, когда первый сигнал имеет предопределенную максимальную длину.

(Изменение варианта осуществления 1)

Устройство 100 декодирования изображения в соответствии с вариантом осуществления 1 может быть включено в описанное ниже устройство декодирования изображения. Фиг.12 является блок-схемой, показывающей пример конфигурации устройства 200 декодирования изображения в соответствии с изменением варианта осуществления 1.

Устройство 200 декодирования изображения декодирует кодированные данные изображения, сформированные посредством кодирования со сжатием. Например, устройство 200 декодирования изображения принимает кодированные данные изображения блок за блоком как текущий сигнал, который должен быть декодирован. Устройство 200 декодирования изображения выполняет декодирование с переменной длиной слова, обратное квантование и обратное преобразование над принятым текущим сигналом для восстановления данных изображения.

Как показано на Фиг.12, устройство 200 декодирования изображения включает в себя блок 210 энтропийного декодирования, блок 220 обратного квантования и обратного преобразования, сумматор 225, фильтр 230 удаления блочности, память 240, блок 250 внутреннего предсказания, блок 260 компенсации движения и переключатель 270 внутреннего/внешнего режима.

Блок 210 энтропийного декодирования выполняет декодирование с переменной длиной слова над входным сигналом (битовым потоком) для восстановления квантованных коэффициентов. При этом входной сигнал является текущим сигналом, который должен быть декодирован, и соответствует данным блок за блоком кодированных данных изображения. Кодированные данные изображения содержат кодированную информацию последней позиции. Кроме того, блок 210 энтропийного декодирования получает данные движения из входного сигнала и выдает данные движения блоку 260 компенсации движения.

Следует отметить, что устройство 100 декодирования изображения в соответствии с вариантом осуществления 1 соответствует части блока 210 энтропийного декодирования. То есть блок 210 энтропийного декодирования декодирует кодированную информацию последней позиции.

Блок 220 обратного квантования и обратного преобразования выполняет обратное квантование над квантованными коэффициентами, восстановленными блоком 210 энтропийного декодирования, для восстановления коэффициентов преобразования. Затем блок 220 обратного квантования и обратного преобразования выполняет обратное преобразование над коэффициентами преобразования для восстановления ошибки предсказания.

Сумматор 225 складывает ошибку предсказания и сигнал предсказания для формирования декодированного изображения.

Фильтр 230 удаления блочности применяет фильтр удаления блочности к декодированному изображению. Полученное в результате декодированное изображение выдается в качестве декодированного сигнала.

Память 240 является памятью для хранения опорного изображения, используемого при компенсации движения. Более определенно, память 240 хранит декодированное изображение, к которому был применен фильтр удаления блочности.

Блок 250 внутреннего предсказания выполняет внутреннее предсказание для формирования сигнала предсказания (сигнала внутреннего предсказания). Более определенно, блок 250 внутреннего предсказания формирует сигнал внутреннего предсказания посредством выполнения внутреннего предсказания опираясь на изображение, соседствующее с текущим блоком, который должен быть декодирован (входным сигналом), в декодированном изображении, сформированном сумматором 225.

Блок 260 компенсации движения выполняет компенсацию движения на основе данных движения, выданных блоком 210 энтропийного декодирования, для формирования сигнала предсказания (сигнала внешнего предсказания).

Переключатель 270 внутреннего/внешнего режима выбирает либо сигнал внутреннего предсказания, либо сигнал внешнего предсказания, и выдает выбранный сигнал сумматору 225 в качестве сигнала предсказания.

С помощью описанной выше конфигурации устройство 200 декодирования изображения декодирует кодированные данные изображения, сформированные посредством кодирования со сжатием.

(Вариант осуществления 2)

Далее описывается устройство кодирования изображения в соответствии с вариантом осуществления 2 с использованием чертежей.

Фиг.13 является блок-схемой, показывающей функциональную конфигурацию устройства 300 кодирования изображения в соответствии с вариантом осуществления 2. Устройство 300 кодирования изображения кодирует информацию последней позиции. Устройство 300 кодирования изображения включает в себя блок 310 преобразования в двоичную форму и блок 320 арифметического кодирования. Блок 320 арифметического кодирования включает в себя первый блок 321 кодирования, второй блок 322 кодирования и блок 323 управления кодированием.

Блок 310 преобразования в двоичную форму преобразовывает в двоичную форму информацию последней позиции, чтобы сформировать (i) двоичный сигнал, который содержит первый сигнал, имеющий длину, меньшую или равную предопределенной максимальной длине, и не содержит второй сигнал, или (ii) двоичный сигнал, который содержит первый сигнал, имеющий предопределенную максимальную длину, и второй сигнал.

Первый сигнал является сигналом, арифметически кодированным с использованием контекста, переключенного среди множества контекстов. Первый сигнал, например, соответствует префиксной части.

Второй сигнал является сигналом, арифметически кодированным с использованием фиксированной вероятности. Второй сигнал, например, соответствует суффиксной части.

Первый блок 321 кодирования арифметически кодирует каждый из двоичных символов, включенных в первый сигнал, с использованием контекста, переключаемого среди множества контекстов в соответствии с битовой позицией двоичного символа. Другими словами, первый блок 321 кодирования кодирует первый сигнал посредством контекстно-адаптивного двоичного арифметического кодирования.

При этом, когда первый сигнал имеет предопределенную максимальную длину, первый блок 321 кодирования арифметически кодирует двоичный символ в последней битовой позиции первого сигнала с использованием контекста, особого для последней битовой позиции. Другими словами, первый блок 321 кодирования арифметически кодирует двоичный символ в последней битовой позиции первого сигнала, имеющего предопределенную максимальную длину, с использованием контекста, отличающегося от контекстов, используемых для двоичных символов в битовых позициях, отличных от последней битовой позиции.

Второй блок 322 кодирования арифметически кодирует второй сигнал с использованием фиксированной вероятности, когда двоичный сигнал содержит второй сигнал. Другими словами, второй блок 322 кодирования кодирует второй сигнал посредством обходного кодирования.

Далее с использованием Фиг.14A и Фиг.14B описываются операции устройства 300 кодирования изображения, имеющего описанную выше конфигурацию. Далее описывается случай, в котором первый сигнал является префиксной частью, и второй сигнал является суффиксной частью. Следует отметить, что флаг суффикса предполагается "выключенным" как значение по умолчанию.

Фиг.14A является блок-схемой последовательности операций, показывающей пример операций обработки устройства 300 кодирования изображения в соответствии с вариантом осуществления 2. Более конкретно, Фиг.14A показывает способ кодирования для формирования битового потока, который может быть декодирован посредством способа декодирования, показанного на Фиг.8A.

Сначала блок 310 преобразования в двоичную форму преобразовывает в двоичную форму каждую из компоненты X и компоненты Y информации последней позиции (этап S401). Более определенно, блок 310 преобразования в двоичную форму преобразовывает в двоичную форму каждую из компоненты X и компоненты Y (последние значения), например, как показано на Фиг.15. При этом суффиксная часть преобразовывается в двоичную форму посредством кодирования Голомба-Райса.

Затем первый блок 321 кодирования кодирует посредством контекстно-адаптивного двоичного арифметического кодирования префиксную часть компоненты X, включенную в информацию последней позиции (этап S402).

Контекстно-адаптивное двоичное арифметическое кодирование является кодированием, соответствующим контекстно-адаптивному двоичному арифметическому декодированию, показанному на Фиг.4. В контекстно-адаптивном двоичном арифметическом кодировании контексты переключаются в соответствии с условием, и получается вероятность возникновения символа, соответствующего переключенному контексту. Затем двоичный символ арифметически кодируется с использованием полученной вероятности возникновения символа. Кроме того, значение вероятности, соответствующее контексту, обновляется в соответствии со значением кодированного двоичного символа (см. непатентную литературу 1).

При этом, как в варианте осуществления 1, когда префиксная часть имеет предопределенную максимальную длину, первый блок 321 кодирования арифметически кодирует двоичный символ в последней битовой позиции префиксной части с использованием контекста, особого для последней битовой позиции.

Следует отметить, что первый блок 321 кодирования может арифметически кодировать каждый из двоичных символов в двух или более битовых позициях, кроме последней битовой позиции префиксной части, с использованием контекста, общего для этих двух или более битовых позиций. Это позволяет первому блоку 321 кодирования сокращать количество контекстов по сравнению со случаем использования разного контекста для каждой битовой позиции, и тем самым требуемая емкость памяти может быть уменьшена.

Затем первый блок 321 кодирования определяет, содержит ли двоичный сигнал компоненты X суффиксную часть (этап S403). Более определенно, первый блок 321 кодирования определяет, содержит ли двоичный сигнал компоненты X суффиксную часть, таким же образом, как на этапе S102 на Фиг.8A.