Область техники, к которой относится изобретение

Изобретение касается связи по сети и, в конкретных вариантах осуществления изобретения, касается самосинхронизирующейся тестовой последовательности.

Уровень техники

Технологии цифровой абонентской линии (DSL) обеспечивают широкую полосу пропускания для цифровой связи по существующим абонентским линиям (например, по медным парам). При передаче данных по абонентским линиям может иметь место переходное затухание сигналов, передаваемых по соседним линиям, например, в одном и том же или соседнем пучке линий. Переходное затухание, в том числе переходное затухание (NEXT) на ближнем конце, переходное затухание (FEXT) на дальнем конце, может ограничить эффективность различных DSL систем, таких как системы, определенные в существующих стандартах, в том числе асимметричной DSL 2 (ADSL2), сверхскоростной DSL (VDSL), сверхскоростной DSL 2 (VDSL2), а также стандарта G.fast, который является будущим стандартом, выпускаемым исследовательской группой 15 (SG 15) сектора (ITU-T) по стандартизации телекоммуникаций Международного совета по телекоммуникациям.

В DSL системах с векторизацией для оценки матрицы канала используют ортогональную тестовую последовательность (также иногда называется пилотной последовательностью). Возьмем в качестве примера VDSL2 систему: для инициализации VDSL2 блока (VTU-R) приемопередачи в модеме удаленной стороны, чтобы присоединиться в правильном битовом индексе исходящей тестовой последовательности, может понадобиться передать от VDSL2 блока (VTU-O) приемопередачи на стороне оператора исходящую тестовую последовательность и ее битовый индекс. Подробности, касающиеся того, как маркер исходящей тестовой последовательности передают из блока VTU-O в блок VTU-R, можно найти в стандарте G.993.5 ITU-T разделе 10.3.3.5 рекомендаций, озаглавленном «Входящий символ синхронизации и маркеры исходящей пилотной последовательности» и включенном в настоящий документ посредством ссылки.

В соответствии со стандартом G.993.5, который определяет протоколы векторизации для компенсации FEXT в VDSL2 модемах, в первую очередь могут быть обучены блоки (FEQ) частотного выравнивания для гармоник из цифрового многочастотного устройства (DMT) демодуляции. В других DSL системах с векторизацией, таких как G.fast, используемый диапазон частот может быть гораздо выше, a FEXT может быть гораздо сильнее. В результате, обучение FEQ с использованием обычных способов, в том числе способа минимальной среднеквадратичной ошибки (LMS), способа слепой LMS (BLMS) и способа усреднения, может работать менее эффективно (например, сходимость может занимать больший промежуток времени).

Раскрытие изобретения

В одном варианте осуществления, изобретение представляет собой способ, включающий в себя этапы, на которых: модулируют множество синхронизированных сигналов с помощью ортогональной тестовой последовательности (OPS), для генерирования множества модулированных синхронизированных сигналов, при этом OPS содержит нулевой элемент (0-элемент), указывающий начало или конец OPS, и параллельно передают, с использованием одного или более устройств передачи, множество модулированных синхронизированных сигналов в течение длительности некоторого количества дискретных многочастотных символов (DMT), при этом каждый из множества модулированных синхронизированных сигналов предназначен для одного из множества устройств приема, удаленно соединенных с одним или более устройствами передачи через группу абонентских линий с векторизацией, а 0-элемент вызывает то, что все множества модулированных синхронизированных сигналов обладают нулевой амплитудой во время первого или последнего DMT символа.

В другом варианте осуществления изобретение представляет собой устройство, содержащее процессор модулирования множества синхронизированных сигналов с использованием OPS, для генерирования множества модулированных синхронизированных сигналов, при этом каждый из множества модулированных синхронизированных сигналов содержит некоторое количество DMT символов, и одно или более устройств передачи, соединенных с процессором, и выполненных с возможностью параллельной передачи множества модулированных синхронизированных сигналов в течение некоторого количества временных периодов, соответствующих DMT символам, при этом каждый из множества модулированных синхронизированных сигналов предназначен для одного из множества устройств приема, удаленно соединенных с одним или более устройствами передачи через группу абонентских линий с векторизацией, и при этом все множество модулированных синхронизированных сигналов обладают нулевой амплитудой во время первого или последнего временного периода.

В еще одном варианте осуществления изобретения изобретение представляет собой устройство, содержащее устройство приема для приема сигнала от устройства передачи в течение множества временных периодов, при этом каждый из множества временных периодов соответствует длительности DMT символа, при этом каждый DMT символ модулирован элементом тестовой последовательности, при этом тестовая последовательность ортогональна другим тестовым последовательностям других устройств передачи во множество синхронизированных устройствах передачи, и процессор, соединенный с устройством приема и выполненный с возможностью определения временного периода, когда принятый сигнал обладает нулевой амплитудой во всех каналах сигнала, для синхронизации нулевого уровня (0-элемента) с временным периодом, так что 0-элемент маркирует начало эталонной тестовой последовательности, известной процессору, и для извлечения прямого канала из принятого сигнала в течение некоторого количества временных периодов, непосредственно следующих за 0-элементом, что делают с использованием эталонной тестовой последовательности.

Эти и другие признаки будут лучше ясны из последующего подробного описания изобретения, приведенного со ссылками на приложенные чертежи и с формулой изобретения.

Краткое описание чертежей

Для более полного понимания настоящего изобретения далее будет приведено краткое описание со ссылками на приложенные чертежи и подробное описание, при этом одинаковые ссылочные позиции представляют аналогичные части.

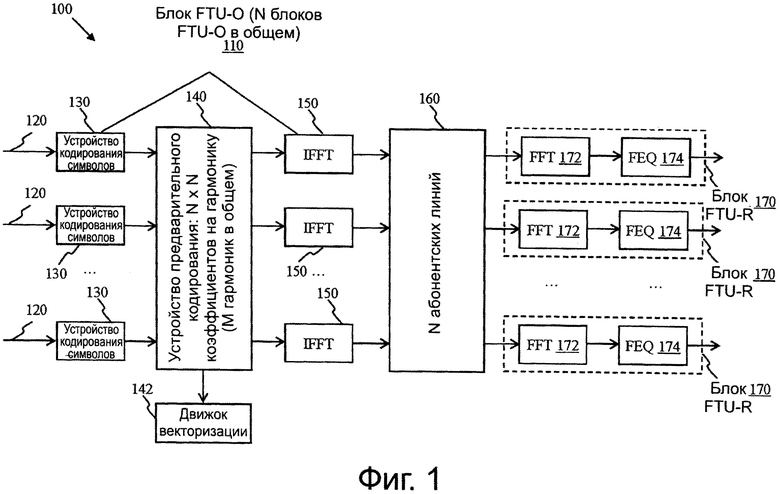

Фиг. 1 - вид, схематически показывающий один вариант секции нисходящей передачи системы (DSL) цифровой абонентской линии;

фиг. 2 - вид, схематически показывающий один вариант секции выходящей передачи DSL системы;

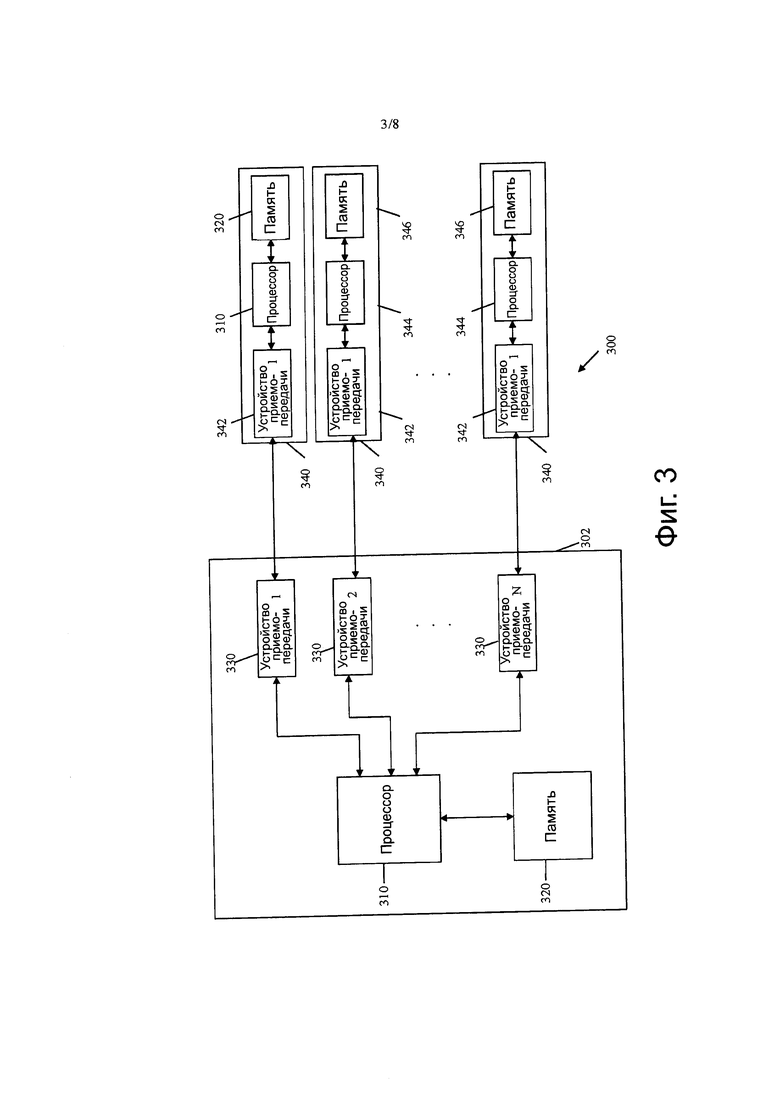

фиг. 3 - другой вид, схематически показывающий один вариант осуществления DSL системы;

фиг. 4А и 4В - виды, показывающие примеры традиционных матриц ортогональных тестовых последовательностей (OPS);

фиг. 4С-4F - виды, показывающие примеры описанных здесь вариантов осуществления OPS матриц;

фиг. 5А - вид, схематически показывающий шаблон модуляции символов, указывающий битовый индекс тестовой последовательности выходящей передачи из блока VTU-O в блок VTU-R и используемый в G.993.5;

фиг. 5В - вид, схематически показывающий пример варианта осуществления шаблона модуляции символов, который может быть использован в G.fast;

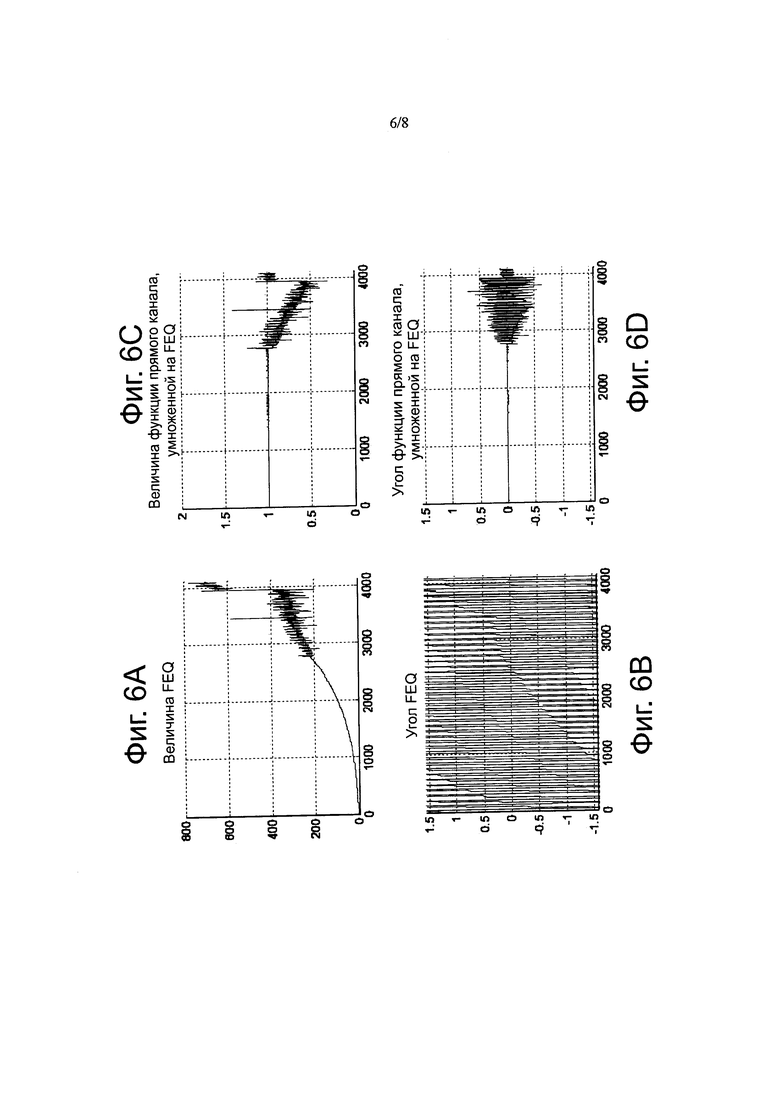

фиг. 6А-6D - виды, показывающие результаты моделирования, полученные при обучении блока (FEQ) частотного выравнивания с использованием алгоритма минимальной среднеквадратичной ошибки (LMS);

фиг. 7А-7D - виды, показывающие результаты моделирования, полученные при обучении FEQ с использованием описанного алгоритма типа множественного доступа с кодовым разделением каналов (CDMA);

фиг. 8 - блок-схема варианта осуществления способа, реализованного в DSL системе, содержащей входящую секцию и исходящую секцию.

Осуществление изобретения

Для начала нужно понимать, что, хотя ниже приведена реализация одного или более вариантов осуществления изобретения, описанные системы и/или способы могут быть реализованы с использованием любого количества известных или существующих технологий. Настоящее изобретение не должно быть ограничено приведенными ниже для иллюстрации реализациями, чертежами и технологиями, в том числе приведенными и описанными здесь приведенными для примера моделями и реализациями, а может быть модифицировано в пределах объема приложенной формулы изобретения и ее эквивалентов.

В зависимости от поддерживаемого стандарта, система (DSL) цифровой абонентской линии иногда может быть обозначена как xDSL система, где «х» может обозначать любой стандарт DSL. Например, «х» означает «А» в асимметричных DSL 2 (ADSL2) или ADSL2+ системах и означает «V» в высокоскоростных DSL (VDSL) или VDSL2 системах. Когда устройство приемопередачи расположено на конце оператора DSL системы, например, центральном офисе (СО), DSL мультиплексоре (DSLAM) доступа, шкафу или блоке (DPU) точки распределения, устройство приемопередачи может быть названо xTU-O. С другой стороны, когда устройство приемопередачи расположено на конце пользователя или удаленном конце, например, в оборудовании (СРЕ) в помещении абонента, устройство приемопередачи можно называть xTU-R. Например, для G.fast системы: устройство приемопередачи на стороне оператора может быть названо блоком (FTU-O) G.fast приемопередачи на стороне оператора, а СРЕ устройство приемопередачи может быть названо FTU на удаленном терминале (FTU-R), то есть на стороне абонента.

В стандарте G.fast при использовании DMT модуляции может понадобиться оценивать прямой канал и его инвертировать для каждой поднесущей DMT с целью получения FEQ коэффициентов с использованием набора ортогональных тестовых последовательностей, аналогично оценке FEXT канала в стандарте G.993.5. Каждый канал (порт) может использовать тестовую последовательность, длина которой совпадает с длиной тестовой последовательности других каналов (портов), но которая ортогональна каждой из упомянутых тестовых последовательностей. Каждую тестовую последовательность можно рассматривать как вектор-строку. Матрица, содержащая тестовые последовательности для каждого порта в качестве своих строк, образует матрицу ортогональных тестовых последовательностей, которую для краткости можно называть OPS. Тестовые последовательности из OPS, используемой в системе с векторизацией, могут начинаться в один момент времени, например, первый столбец OPS одновременно передают через порты. В основанном на VDSL2 стандарте G.993.5, когда может быть мал уровень FEXT по сравнению с прямым каналом, прямой канал оценивают с присутствующим FEXT. Далее вычисляют FEQ и используют результаты для оценки FEXT каналов. При оценке входящего (DS) FEXT канала в стандарте G.993.5, в блоке VTU-R не нужно обладать знанием DS OPS или ее битового индекса, так как блок VTU-R может просто сообщать о записанной ошибке назад в соответствующий блок VTU-O. Сигнал ошибки, принятый каждым блоком FTU-O, далее обрабатывают движком векторизации для оценки DS FEXT канала с целью использования в устройстве DS предварительного кодирования, в котором исключают FEXT. Тем не менее, в отличие от стандарта G.993.5, блоку FTU-R в стандарте G.fast необходимо знать битовый индекс DS OPS для осуществления оценки DS прямого канала. Оценку входящего FEXT канала можно осуществить аналогично стандарту G.993.5.

Здесь описаны системы, способы, устройства и программные продукты для самосинхронизации инициализируемого блока xTU-R с DS тестовой последовательностью, например, даже при наличии сильного FEXT. С использованием ортогональных тестовых последовательностей в DS каждого блока xTU-O, DS прямые каналы можно оценивать в соответствующих блоках xTU-R при удаленных FEXT каналах. Синхронизации достигают благодаря использованию нулевых элементов (0-элементов) в тестовых последовательностях, синхронно передаваемых каждым блоком xTU-O. Более конкретно, когда OPS используют на стороне передачи для модуляции синхронизированных сигналов, для маркировки начала или конца OPS в OPS может быть введен 0-элемент (иногда равноценно здесь называют Z-состоянием или Z-битом). DMT символ, умноженный на 0-элемент, может быть принудительно установлен равным нулю. Таким образом, 0-элемент может быть причиной того, что модулированные синхронизированные сигналы, которые передают со стороны передачи, обладают нулевой амплитудой по всем портам во время первого или последнего DMT символа. Так как сторона передачи активных и соединительных линий может использовать 0-элемент в первом или последнем DMT символе, то может не быть никакой амплитуды сигнала или никакого FEXT в группе линий с векторизацией. Следовательно, обнаружение первого или последнего DMT символа может быть осуществлено без необходимости в FEQ. Для уменьшения затрат, 0-элемент может быть введен в каждый N-й (любое целое число, большее единицы) OPS период вместо всех OPS периодов или 0-элемент может быть использован только при присоединении новой линии к группе линий с векторизацией. Благодаря созданию 0-элемента в OPS и синхронного его использования в блоках xTU-O, в блоке xTU-R может быть достигнута самосинхронизация без необходимости сначала передать битовый индекс OPS из соответствующего блока xTU-O.

На фиг. 1 схематически показан вариант осуществления DS секции 100 DSL системы. Хотя предполагаем, что DSL система соответствует стандарту G.fast, но специалист в рассматриваемой области техники поймет, что описанные здесь механизмы могут быть аналогичным образом применены в любой другой DSL системе. В DS секции или конфигурации 100, в N блоках 110 FTU-O могут принимать прошедшие предварительное кодирование DS сигналы из N абонентских линий 120, обрабатывать сигналы и передавать обработанные DS сигналы в N абонентских линий 160, где N является целым числом, большим единицы. N абонентских линий 160 можно рассматривать как группу линий с векторизацией, так как их сигналы могут быть обработаны совместно движком 142 векторизации, расположенным в точке распределения, где расположены блоки 110 FTU-O, что сделано для компенсации DS FEXT с использованием технологии предварительного кодирования. Каждый блок 110 FTU-O может содержать устройство 130 кодирования символов и блок 150 (IFFT) обратного быстрого преобразования Фурье. Таким образом, входящий поток битов для линии 120, содержащий данные из расположенного ниже сетевого источника, может быть закодирован в соответствующем устройстве 130 кодирования символов. В устройстве 130 кодирования символов могут делить входящий поток битов на небольшие группы битов, при этом каждую группу могут модулировать с помощью поднесущей цифрового многочастотного символа (DMT). Здесь количество поднесущих в каждой линии может быть обозначено через М, где M является целым числом.

Закодированные символы в группе линий можно подавать в устройство 140 предварительного кодирования, которое выполнено так, чтобы линейно объединять сигналы из каждой линии и генерировать сигналы для блоков 150 (IFFT) обратного быстрого преобразования Фурье. Устройством 140 предварительного кодирования может управлять движок 142 векторизации и в устройстве 140 предварительного кодирования могут вычислять несколько выходов по нескольким входам, таким образом, устройство 140 предварительного кодирования является системой с несколькими входами и несколькими выходами (MIMO) в частотной области. Так как может быть использовано несколько гармоник, то устройство 140 предварительного кодирования может содержать отдельную матрицу коэффициентов для каждой гармоники. В DS направлении для каждой DS гармоники матрицу канала можно извлечь из обратного канала между блоком 110 FTU-O и блоком 170 FTU-R. Матрица канала может быть использована в устройстве 140 предварительного кодирования для компенсации или уменьшения FEXT в DS. Более конкретно, фильтр предварительного искажения или матрица предварительного кодирования могут быть использованы для предварительного искажения сигналов и, таким образом, уменьшения или компенсации FEXT, которое имеет место в абонентских линиях 160, тем самым обеспечивают то, что каждое DS устройство приема в блоках 170 FTU-R достигает большей скорости передачи данных.

Каждый IFFT блок 150 может быть использован для DMT модуляции, когда M символов в частотной области преобразуют в M сигналов во временной области. Сигналы во временной области передают в N выходных абонентских линий 160, которые можно рассматривать как группу линий с векторизацией и их сигналы сгенерировано во множестве блоков 110 FTU-O и предназначены для множества блоков 170 FTU-R. Переходные затухания, в том числе NEXT и/или FEXT, могут привноситься тогда, когда сигналы перемещаются в абонентских линиях 160. Для каждого DS устройства приема может существовать соответствующая абонентская линия или медная пара, которая соединяет DS устройство приема с блоком 110 FTU-O. Абонентские линии 160 могут быть собраны вместе в пучок или связку кабелей.

Каждому специалисту в рассматриваемой области ясно, что каждое DS устройство приема в помещении абонента, то есть каждый блок 170 FTU-R может быть выполнен для приема соответствующего сигнала от одной из абонентских линий 160. Более того, каждый блок 170 FTU-R может содержать блок 172 (FFT) быстрого преобразования Фурье и блок 174 FEQ. FFT блок 172 может быть использован для DMT демодуляции, когда сигналы во временной области преобразуют в символы в частотной области. Блок 174 FEQ может быть использован для компенсации искажений сигналов, вызванных потерями прямого канала абонентской линии.

В секции 100 нисходящей передачи блок 110 FTU-O может использовать OPS, содержащую 0-элемент, в абонентских линиях 160 для синхронизации соединительной линии (может быть любой из N линий) с OPS. N блоков 110 FTU-O могут модулировать множество синхронизированных сигналов с помощью OPS, содержащей 0-элемент, с целью генерирования множества модулированных синхронизированных сигналов, и множество модулированных синхронизированных сигналов можно параллельно передавать через порты N блоков 110 FTU-O в N блоков 170 FTU-R в течение длительности DMT символов.

0-элемент также может быть использован для осуществления дополнительных функций, например, для оценки FEXT, оценки прямого канала и получения коэффициентов FEQ. Например, на раннем этапе обучения, когда коэффициенты адаптивного блока 174 FEQ еще не получены, после синхронизации соединительной линии с помощью тестовой последовательности, в описанных вариантах осуществления изобретения возможно в соединительной линии осуществить быстрое обучение FEQ даже при наличии сильного FEXT.

В стандарте G.993.5 синхронизация может быть обеспечена только на позднем этапе после получения коэффициентов FEQ, а получение коэффициентов FEQ с использованием обычного LMS может работать плохо при наличии сильного FEXT. Как следствие, при плохом обучения FEQ, эффективность векторизации, которая предназначена для компенсации FEXT, также может быть слабой. С другой стороны, описанное обучение FEQ может использовать подход типа множественного доступа с кодовым разделением каналов (CDMA) с применением OPS, что лучше LMS или других традиционных алгоритмов с точки зрения точности и скорости сходимости. Так как более современные DSL системы, такие как G.fast, могут иногда характеризоваться сравнительно сильным FEXT, описанное обучение FEQ может оказаться более эффективным.

На фиг. 2 схематически показан вариант осуществления US секции 200 DSL системы. Исходящая секция 200 может соответствовать DS секции 100, таким образом некоторые аспекты будут аналогичны. Для краткости дальнейшее описание будет концентрироваться на отличающихся или не раскрытых аспектах. В US секции 200, в N блоках FTU-O 210 могут принимать US сигналы из N входных абонентских линий 260, демодулировать сигналы с использованием FFT 250 и передавать сигналы в блок 240 компенсации FEXT, где Ν является целым числом, большим единицы.

US секция 200 содержит множество блоков 270 FTU-R, каждый из которых содержит IFFT блок или модуль 272 и устройство 274 кодирования символов для каждой абонентской линии 260. Таким образом, входящий поток битов, содержащий US данные, может быть закодирован в соответствующем устройстве 274 кодирования символов. В устройстве 274 кодирования символов могут делить входящий поток битов на небольшие группы битов, при этом каждую группу могут модулировать с помощью некоторой гармоники или поднесущей DMT символа.

Каждый IFFT блок 272 может быть использован для DMT модуляции, когда символы в частотной области преобразуют в сигналы во временной области. Сигналы во временной области передают в N выходных абонентских линий 260, которые можно рассматривать как группу линий с векторизацией, так как их сигналы генерируют во множестве блоков 270 FTU-R и они синхронизированы в блоках 210 FTU-O с помощью движка 242 векторизации. Переходные затухания, в том числе NEXT и/или FEXT, могут привноситься тогда, когда US сигналы перемещаются в абонентских линиях 260. Для каждого US устройства приема может существовать соответствующая абонентская линия или медная пара, которая соединяет US устройство приема с одним из блоков 270 FTU-R. Абонентские линии 260 могут быть собраны вместе в пучок или связку кабелей.

FFT блоки 250 могут быть использованы для DMT демодуляции, когда сигналы во временной области преобразуют в символы в частотной области. Демодулированные символы могут подавать в устройство 240 компенсации переходного затухания, которое выполнено так, чтобы линейно объединять сигналы из каждой линии, компенсировать FEXT и генерировать сигналы для блоков 230 FEQ. Устройство 240 компенсации также является MIMO системой в частотной области. Так как может быть использовано несколько гармоник, то устройство 240 компенсации может содержать отдельную матрицу коэффициентов компенсации для каждой гармоники. В US направлении для каждой US гармоники можно извлечь матрицу канала. Матрица канала может быть использована в устройстве 240 компенсации для уменьшения или компенсации FEXT в US. Блоки 230 FEQ могут быть использованы для компенсации искажений сигналов, вызванных потерями (например, потерями внедрения) прямого канала абонентских линий 260. Аналогично DS секции 100 в US секции 200 каждый блок 270 FTU-R может использовать эталонную тестовую последовательность, содержащую 0-элемент для синхронизации.

На фиг. 3 схематически показан вид, иллюстрирующий вариант осуществления DSL системы 300, которая может быть так выполнена, что реализует входящую секцию 100, исходящую секцию 200, и иллюстрирующий другие описанные здесь варианты осуществления. DSL система 300 содержит блок 302 (DPU) точки распределения и множество СРЕ 330, удаленно соединенных с DPU 302 с помощью группы абонентских линий с векторизацией. Для входящей синхронизации, блок FTU-O, расположенный в DPU 302, рассматривается как сторона передачи, и каждое СРЕ 340 рассматривается как сторона приема. Для исходящей синхронизации блок FTU-O рассматривается как сторона приема, и каждое СРЕ 340 рассматривается как сторона передачи.

DPU 302 содержит процессор 310, запоминающее устройство 320 и множество устройств 330 приемопередачи, выполненных так, как показано на фиг. 3 (может присутствовать N устройств приемопередачи, где N является целым числом, большим единицы). С другой стороны, каждое СРЕ 340 также содержит процессор 310, запоминающее устройство 320 и устройство 342 приемопередачи. В стандарте G.fast каждое из устройств 310 приемопередачи может быть блоком FTU-O, а каждое из устройств 342 приемопередачи может быть блоком FTU-R. Процессор 310 может быть реализован как одна или более интегральных схем центрального процессорного элемента (CPU), ядер (например, многоядерный процессор), программируемые пользователем матрицы логических элементов (FPGA), специализированные интегральные схемы (ASIC) и/или цифровые сигнальные процессоры (DSP). Процессор 310 может быть реализован аппаратно или с использованием сочетания аппаратного и программного обеспечения.

Запоминающее устройство 320 может содержать кэш, оперативное запоминающее устройство (RAM), постоянное запоминающее устройство (ROM), внешнее запоминающее устройство или их любое сочетание. Внешнее запоминающее устройство обычно содержит один или более дисковых запоминающих устройств или запоминающих устройств на магнитной ленте и внешнее запоминающее устройство используют как энергонезависимое запоминающее устройство для данных и как запоминающее устройство для переполнения, если RAM недостаточно велико для всех рабочих данных. Внешнее запоминающее устройство может быть использовано для хранения программ, которые загружают в RAM, когда такие программы выбирают для выполнения. ROM может быть использовано для хранения команд и возможно данных, которые считывают во время выполнения программы. ROM является энергонезависимым запоминающим устройством, объем которого относительно мал по сравнению с большим объемом внешнего запоминающего устройства. RAM может быть использовано для хранения текущих данных и, возможно, для хранения команд. Доступ как к ROM, так и к RAM, обычно осуществляется быстрее, чем доступ к внешнему запоминающему устройству

Устройства 330 приемопередачи могут быть выполнены для осуществления DMT модуляции и демодуляции. Устройства 330 приемопередачи могут служить как устройства ввода и/или вывода для DPU 302. Например, если устройство 330 приемопередачи функционирует как устройство передачи, оно может передавать данные из DPU 302. Например, если устройство 330 приемопередачи функционирует как устройство приема, оно может принимать данные для DPU 302. DPU 302 может быть выполнено для осуществления любой из описанных здесь схем, такой как передача OPS, к которой в начале или в конце добавили 0-элемент. С другой стороны, каждое СРЕ 340 может достичь самосинхронизации благодаря получению OPS, к которой в начале или в конце добавили Z-состояние, как описано в настоящем документе.

Ясно, что с помощью программирования и/или загрузки выполняемых команд в блок xTU-O или СРЕ 340, по меньшей мере или процессор 310 или память 320 изменятся, частично преобразуя блок xTU-O в специализированную машину или устройство (например, блок xTU-O, выполненный для передачи OPS, к которой в начале или в конце добавили 0-элемент) Выполнимые команды могут храниться в памяти 320 и для выполнения могут быть загружены в процессор 310. Из области проектирования электрических схем и программного обеспечения известно, что функциональные возможности, которые могут быть реализованы путем загрузки выполняемого программного обеспечения в компьютер, могут быть реализованы аппаратно с помощью хорошо известных правил проектирования. Решения о реализации концепции с помощью программного обеспечения или с помощью аппаратного обеспечения зависят от соображений стабильности модели и количества вырабатываемых блоков, а не вопросов, касающихся перехода из области программного обеспечения в область аппаратного обеспечения. В общем, модель, которая часто подвергается изменениям, может быть предпочтительно реализовать программно, так как переделка аппаратной реализации дороже переделки программной модели. В общем, стабильную модель, которую будут производить в больших объемах, может быть предпочтительно реализовать аппаратно, например, с помощью специализированной интегральной схемы (ASIC), так как большое производство аппаратной реализации может быть дешевле программной реализации. Часто модель может быть разработана и протестирована в программной форме и затем преобразована, с помощью хорошо известных правил проектирования, в эквивалентную аппаратную реализацию с помощью специализированной интегральной схемы, в которой аппаратно реализуются команды программного обеспечения. Аналогично тому, как машина, управляемая новой ASIC, является специализированной машиной или устройством, компьютер, который запрограммирован и/или в него загружены выполнимые команды, можно рассматривать как специализированную машину или устройство.

Описанные варианты осуществления изобретения могут предоставлять возможность инициализировать блок FTU-R с целью самосинхронизации его устройства приема с битовым индексом OPS входящего устройства передачи до обучения FEQ. В результате самосинхронизация может позволить проводить быстрое обучение FEQ типа CDMA, даже при наличии сильного FEXT. Далее самосинхронизация также может позволить инициализируемому устройству передачи блока FTU-R синхронизировать исходящий битовый индекс OPS.

Обучение FEQ может использовать идею, аналогичную использованной в CDMA при беспроводной связи. Упрощенная математическая модель может быть записана следующей формулой:

где Н является матрицей канала, которая содержит прямой канал и один или более FEXT каналов, X является матрицей, представляющей множество переданных сигналов, которые являются ортогональными или псевдоортогональными сигналами в символе синхронизации. Z является матрицей, представляющей шумы, такие как аддитивный белый гауссовский шум (AWGN) (заметим, что те же принципы применимы к любому другому шаблону шумов), и Y является матрицей, представляющей множество принятых сигналов.

Для вычисления Н обе стороны равенства (1) можно умножить на матрицу, обратную для Н, как показано ниже:

где XH является матрицей, сопряженной с X, а с является определителем X.

Матрица Н канала может содержать N×N элементов (N обозначает количество абонентских линий в группе с векторизацией) и элемент hii представляет прямой канал с индексом i строки и индексом i столбца. Коэффициенты FEQ могут быть вычислены как обращение прямого канала hii в матрице Н. Для вычисления hii, перепишем приведенное выше матричное равенство для диагональных элементов и получим следующее равенство:

где k представляет индекс гармоники от 1 до m, yik представляет элемент в строке i и столбце k матрицы Y, и  представляет элемент в строке i и столбце k матрицы XH.

представляет элемент в строке i и столбце k матрицы XH.

можно рассматривать как сигнал, обратный для переданного сигнала и

можно рассматривать как сигнал, обратный для переданного сигнала и  может быть использован как эталонный сигнал на приемном конце.

может быть использован как эталонный сигнал на приемном конце.  состоит из нескольких частей, как показано в равенстве (при этом здесь опущены индексы):

состоит из нескольких частей, как показано в равенстве (при этом здесь опущены индексы):

Устройство генерирования псевдослучайной двоичной последовательности (PRBS) может сгенерировать случайное или псевдослучайное значение, например, в спектре или гармониках. PRBS может быть сброшена в начале каждого DMT символа и PRBS может быть известна на стороне приема. PRBS может указывать, что скремблер квадранта поворачивает созвездие каждой гармоники от исходной точки, например, имеющей значение «1+i» или «1-i», на основе двух битов PRBS.

В равенстве (4) содержимое PRBS может быть фиксированным значением и может быть известно на удаленной стороне приема, что справедливо в G.993.5. В других применимых DSL системах, таких как G.fast, содержимое PRBS может быть передано на сторону приема (например, FTU-R в DS случае) на этапе установления связи. Далее, в G.fast для разных блоков FTU-R могут быть использованы отдельные скремблеры. Также устройство генерирования PRBS может быть одинаковым для каждого блока FTU-R, но начальное состояние может быть различным для разных блоков FTU-R. Начальное состояние может быть передано в каждый блок FTU-R на этапе установления связи.

При подходе типа CDMA при обучении FEQ, с целью извлечения прямого канала, стороне приема, такой как блок FTU-R, может быть нужен точный битовый индекс или временной маркер OPS для текущего принятого сигнала. Когда определен битовый индекс или временной маркер, на стороне приема могут осуществить надлежащее сопоставление со своей эталонной тестовой последовательностью с целью получения прямого канала из принятого сигнала или сигналов и отклонить FEXT каналы. Это возможно, так как тестовая последовательность, переданная в каждое устройство приема, ортогональна тестовой последовательности, переданной в другие устройства приема. После извлечения прямого канала, на стороне приема могут инвертировать прямой канал с целью получения коэффициентов FEQ, тем самым завершить обучение FEQ.

Описанные здесь варианты осуществления изобретения могут позволить на стороне приема обнаружить (Z)-состояние нулевого уровня, на которое указывает один или более 0-элементов. Z-состояние может позволить стороне приема синхронизировать пилотную последовательность стороны передачи до обучения FEQ. Другими словами, аналогично обучению FEQ типа CDMA, в описанных вариантах осуществления изобретения можно найти или определить символ, или позицию во времени или битовый индекс OPS. Первый или последний символ синхронизации OPS используют как маркер. Маркер может содержать один или несколько символов молчания. Этот символ молчания могут не учитывать в общей длине OPS. Например, используют OPS длиной 16, а фактический период OPS равен 17.

На фиг. 4А показан пример обычной OPS 400, используемой в существующих xDSL системах. Здесь мы считаем, что OPS 400 принимает форму матрицы размера 4×4, соответствующей четырем портам группы четырех блоков FTU-R с векторизацией. Ясно, что описанные здесь OPS могут обладать любым подходящим количеством строк и столбцов. Заметим, что обычные OPS 400 состоят только из элементов +1 и -1, без 0-элементов. OPS 400 является матрицей Адамара (обозначена как W), в которой любая строка ортогональна любой другой строке; то есть внутреннее произведение любой строки на другую строку равно нулю. Хотя здесь в основном используется термин OPS, специалисту в рассматриваемой области ясно, что те же принципы применимы к псевдослучайной тестовой последовательности или более общей тестовой последовательности.

В OPS 400 (или любой другой описанной здесь OPS) каждая строка может быть использована для некоторого порта и каждый элемент или бит в рассматриваемом случае может модулировать символ синхронизации. Каждый столбец указывает на передачу символов синхронизации по различным портам в заданный момент времени. «+1» бит оставляет точки созвездия без изменения, а «-1» инвертирует и действительную и мнимую части точек созвездия для всех гармоник и наоборот. Другими словами, «+1» бит может инвертировать как действительную, так и мнимую части точек созвездия, а «-1» бит может оставлять точки созвездия без изменения. OPS 400 могут периодически передавать с помощью символов синхронизации. Следовательно, как показано на фиг. 4В, OPS матрицу 400 можно наблюдать как повторяющуюся вправо с течением времени, и она формирует со временем множество OPS матриц. Ясно, что элемент тестовой последовательности можно рассматривать как модуляцию DMT символа с помощью фиксированных точек созвездия для каждой поднесущей, где каждая поднесущая DMT символа повернута с учетом выходного значения скремблера, элемент тестовой последовательности можно эквивалентно рассматривать как сопоставление с точкой созвездия. Например, элемент -1 может быть сопоставлен с точкой 1+i созвездия, а элемент +1 может быть сопоставлен с точкой -1-i созвездия, а 0-элемент может быть сопоставлен с точкой 0+0i созвездия (другими словами, представленный маскированной поднесущей или поднесущей с коэффициентом усиления, равным нулю) для всех поднесущих. Далее скремблер может работать по поднесущим для придания случайности созвездиям. Эти два подхода эквивалентны и в DSL стандартах могут применять любой подход (например, в G.fast могут применять второй подход).

В отличие от обычной OPS 400, показанной на 4А, на фиг. 4С показан пример описанной здесь OPS 440, которая совпадает с OPS 400 за исключением добавления в начале дополнительного столбца 0-элементов, предназначенного для указания на начало OPS 440. В реализации столбец 0-элементов указывает, что все порты всех блоков FTU-R могут не передавать сигналы или передавать сигналы нулевой амплитуды (что определено 0-элементом) в этот момент времени или в этой позиции символа. Нулевая амплитуда в группе абонентских линий с векторизацией может быть обнаружена на стороне приема без FEQ. Когда на стороне приема обнаруживают 0-элемент, на стороне приема могут синхронизироваться с временным периодом, например, когда 0-элемент маркирует начало или конец эталонной тестовой последовательности. На стороне приема известно содержимое эталонной тестовой последовательности, которое может быть заранее сохранено на стороне приема или которое может быть передано со стороны передачи на сторону приема во время более ранней фазы инициализации, такой как фаза установления связи. Соответственно, сторону приема можно синхронизировать со стороной передачи на основе 0-элемента.

Один или более 0-элементов можно добавить не только к началу (то есть в первый столбец) OPS, но также в любой другой подходящий столбец. На фиг. 4D показан другой пример описанной OPS 460, которая содержит 0-элемент в последнем столбце, что нужно для указания на конец OPS 460. Дополнительный 0-элемент может быть вставлен в любой OPS период (покрывающий длительности множество DMT символов). Следовательно, как показано на фиг. 4Е, OPS матрицу 440 или 460 можно наблюдать как повторение вправо с течением времени, в результате чего со временем формируется множество OPS матриц 480. Заметим, что за длительность N OPS периодов, результирующий эффект OPS 440 и OPS 460 может быть одинаковым, так как могут быть сформированы одинаковые OPS матрицы 480.

Вместо добавления 0-элемента к каждой OPS матрице W, в альтернативном варианте осуществления изобретения, показанном на фиг. 4F, 0-элемент может быть вставлен каждый N (любое целое число, большее единицы) период исходной W матрицы. Использование N>1 может уменьшить ненужные затраты на 0-элемент. Так как 0-элемент может быть использован для помощи инициализируемой линии в синхронизации ее устройства приема или устройства передачи с битовым индексом DS OPS или US OPS соответственно, иногда может быть необходимо передавать 0-элемент каждый OPS период.

При нормальном режиме работы, OPS может быть использован для динамической записи и обновления изменения FEXT каналов активных линий. Слишком частая передача 0-элемента (Z-состояния) может мешать активной линии из-за задержки обновления их FEXT каналов и, следовательно, обновления устройства предварительного кодирования и компенсации FEXT. Для минимизации этого потенциального недостатка и дополнительного уменьшения затрат, вызванных 0-элементом, в одном варианте осуществления изобретения 0-элемент может быть активирован (добавлен к OPS) движком (VCE) управления векторизацией при инициализации новой линии или присоединении новой линии к группе активных линий с векторизацией.

Хотя в большой части этого документа обсуждается DS направление, аналогичные принципы также могут быть применены для US направления. Так как входящее направление может использовать первую OPS, а исходящее направление может использовать вторую OPS, необходимо заметить, что первая OPS и вторая OPS могут совпадать и могут различаться. Далее, длины первой OPS и второй OPS могут совпадать и могут различаться. Тем не менее, синхронизацию можно упростить, есть одна будет целым множителем другой.

В одном варианте осуществления изобретения, когда период (или одинаковое количество битов в каждой строке) второй OPS совпадает с периодом первой OPS, их передача может быть синхронизирована. Более конкретно, первая OPS, и вторая OPS могут начинаться в одно и то же время или с одинаковым битовым индексом. Таким образом, знание времени начала первой OPS может приводить к знанию времени начала второй OPS. Таким образом, US OPS может быть синхронизована в группе абонентских линий с векторизацией.

Если Z-состояние (0-элемент) используют для каждого из N OPS периодов, значение N может быть одинаковым для DS и US направлений, и может быть разным для DS и US направлений. Например, Z-состояние можно вставлять каждые 10 OPS периодов в DS направлении и можно вставлять каждые 20 или любое другое число OPS периодов в US направлении.

Например, при использовании N OPS периодов для организации начала US OPS и DS OPS в один и тот же момент времени или с известным временем смещения, мы может предположить, что длина US OPS и DS OPS различна. В этом случае минимальным значением N является наименьшее общее кратное длины US OPS и длины DS OPS, разделенное на значение, являющееся наибольшим общим делителем длины US OPS и длины DS OPS.

С точки зрения реализации 0-элемент в OPS указывает, что точка созвездия (например, «1+i» или любое другое комплексное число, где i=sqrt(-1)) умножена на 0. В этом случае любой сигнал, сопоставленный с точкой созвездия, уничтожается или его амплитуда становится равной нулю. Когда 0-элемент передают с помощью символа синхронизации в группе абонентских линий с векторизацией, среди группы абонентских линий с векторизацией может не быть сигнала или FEXT. Соответственно, битовый индекс или временная позиция 0-элемента может быть обнаружена путем инициализации блока FTU-R до обучения FEQ. После определения 0-элемента, блок FTU-R может определить начало или конец OPS и синхронизироваться с битовым индексом OPS.

В DSL системе (например, системе 300) одна и та же OPS матрица может быть использована для множества гармоник, используемых в DSL системе, таким образом рассмотрение для одной из гармоник может быть также применено для других гармоник. Далее, одна и та же OPS матрица может быть совместно использована всеми устройствами приема. Таким образом, если устройство приема интересует только свой прямой канал, то устройству приема может понадобиться получить только соответствующую строку (тестовую последовательность) OPS матрицы. Эту строку можно назвать эталонной тестовой последовательностью или набором битов (элементов) тестовой последовательности. В устройстве приема, благодаря сопоставлению эталонной тестовой последовательности с принятыми символами по длине строки, остается прямой канал, а другие строки могут быть удалены при операции сопоставления, так как другие строки ортогональны и не коррелируют со строкой прямого канала. Следовательно, может быть убрано (или уничтожено) любое присутствующее FEXT. В качестве альтернативы, если в устройстве приема с индексом «i» интересуются FEXT из устройства передачи с индексом «j», в устройстве приема с индексом «i» может быть необходимо сопоставить свой принятый сигнал со строкой «j» OPS матрицы. В этом случае, прямой канал и FEXT из других каналов за исключением строки «j» могут быть уничтожены в процессе сопоставления и может остаться только FEXT от канала «j ». Тем не менее, в этом случае в устройстве приема «i» необходимо знать содержимое строки «j» OPS матрицы.

На фиг. 5А схематически показан шаблон 500 модуляции символов, используемый в G.993.5 для исходящей синхронизации OPS, а на фиг. 5В схематически показан вариант осуществления шаблона 540 модуляции символов. Фиг. 5А также приведена как фиг. 106 в стандарте G.993.5, раздел 10.3.3.5, таким образом, подробности реализации, касающиеся шаблона 500 модуляции символов, могут быть найдены в указанном разделе (для краткости здесь не повторены). Шаблон 500 с фиг. 5А содержит два состояния символа, обозначенные как 1 и 0. В соответствии с G.993.5, использование шаблона 500 может требовать заранее обучить FEQ и требовать его функционирование. Далее, синхронизацию может быть сравнительно сложно реализовать, и она может не быть устойчивой при сильном FEXT.

С другой стороны, шаблон 540 с фиг. 5В показывает 8-элементную тестовую последовательность «+1 -1 +1 +1 -1 -1 +1 -1» порта с добавленным в начале 0-элементом, таким образом шаблон 540 содержит три состояния символов, обозначенных как 0, +1 и -1. После сравнения шаблона 500 модуляции символов, используемого в G.993.5, с описанным здесь шаблоном 540 модуляции символов, специалисту в рассматриваемой области ясно, что шаблон 540 содержит дополнительное Z-состояние или 0-элемент, который не присутствует в шаблоне 500.

В стандарте G.fast одобрено, что «G.fast будет определять тестовые сигналы для оценки канала, которые помимо элементов тестовой последовательности со значениями 1 и -1, также содержат 0-элемент со значением 0, при этом 0-элемент обозначает отсутствие передачи мощности, например, маскированную тестовую гармонику (гармоники) или маскированный символ (символы)».

Надо понимать, что состояния 0, +1 и -1 в шаблоне 540 являются тремя отдельными элементами и могут требовать двух битов для представления каждого элемента, таким образом, они отличаются от обычных состояний +1 и -1, для представления которых нужен только один бит. Например, элементы тестовой последовательности могут быть представлены двумя битами следующим образом: 00 для 0-элемента, 01 для элемента +1 и 10 для элемента -1, при этом в обычном способе одного бита достаточно для представления двух отдельных элементов +1 и -1. На практике, когда OPS элемент умножают на DMT символ, если OPS элемент равен +1, то DMT символ остается неизменным; если OPS элемент равен -1, DMT символ инвертируют или поворачивают на 180 градусов по фазе (в качестве альтернативы DMT символ остается неизменным, если OPS элемент равен -1 и его инвертируют, если OPS элемент равен +1); иначе, если OPS элемент равен 0, DMT символ уничтожают (то есть ему придают нулевую амплитуду). Сигнал нулевой амплитуды (или полное отсутствие сигнала) приводит к нулевому FEXT в группе линий с векторизацией, что может быть определено на стороне приема без опоры на FEQ и с использованием устройства определения уровня мощности или с помощью других способов. В результате, по сравнению со способом синхронизации G.993.5 с исходящей OPS, для которого нужен FEQ, синхронизация с входящим OPS с использованием описанного способа, для которого не требуется FEQ, может быть сравнительно проще в реализации и может быть более устойчивой при сильном FEXT.

В соответствии с вариантом осуществления изобретения, на этапе обнаружения канала, обозначенном как этап CHANNEL DISCOVERY 1-1, в блоке FTU-O могут передавать символы синхронизации, модулированные OPS. OPS может начинаться с одного или нескольких 0-элементов или кончаться одним, или несколькими 0-элементами и для каждой линии она может быть определена стандартом G.994.1 на основе возможности, о которой сообщает блок FTU-R соединительной линии. OPS может совсем не содержать 0-элементов за исключением первого или последнего столбца OPS. Разные начальные состояния скремблирования на каждую линию могут быть использованы для символов данных, и они могут быть одинаковыми с состояниями, используемыми для символов синхронизации. Заметим, что эта OPS может отличаться от OPS, использованной в сигнале, на который ссылаются в G.fast и который называют как О-Р-VECTOR 1. Длительность этапа обнаружения канала может быть определена в блоке FTU-O в соответствии с G.944.1 на основе одного или нескольких запросов (например, запросов синхронизации) от блоков FTU-R соединительных линий.

Поддерживает ли блок FTU-R использование описанной здесь специальной тестовой последовательности может быть ясно из сообщения (CLR) с запросом списка возможностей, направленного из блока FTU-R в блок FTU-O на этапе установления связи G.994.1. В одном варианте осуществления изобретения сообщение CLR содержит поле информации стандарта, обозначенное как бит Npar(2), соответствующий биту SPar(1) стандарта G.fast, при этом бит Npar(2) может быть установлен равным нулю для указания того, что блок FTU-R не поддерживает использование специальной тестовой последовательности, которую нужно использовать на этапе обнаружения канала 1-1 и на этапе обнаружения канала 1. Иначе бит Npar(2) может быть установлен равным ЕДИНИЦЕ для указания того, что блок FTU-R поддерживает использование тестовой последовательности с одним или более 0-элементами, маркирующими начало тестовой последовательности.

Описанные варианты осуществления изобретения могут использовать 0-элемент в каждом OPS периоде или каждые N OPS периодов для указания начала OPS битового индекса. Следовательно, нет необходимости в заблаговременной передаче временного маркера DS OPS битового индекса из блока FTU-O в блок FTU-R. При синхронной дуплексной связи с временным разделением каналов (TDD), используемой в G.fast, US OPS и DS OPS могут начинаться в одно и то же время или с известным временным смещением. Следовательно, может не быть необходимости в дальнейшей передаче временного маркера US OPS из блока FTU-O в блок FTU-R. Так как активные и соединительные линии блока FTU-O могут передать 0-элемент, в линии может не присутствовать никакого сигнала (в том числе сигнала прямого канала или FEXT). Следовательно, обнаружение этого периода времени может быть легко достигнуто без необходимости в FEQ.

Для демонстрации улучшения эффективности описанных вариантов осуществления изобретения по сравнению с обычными способами был проведен ряд моделирований. На фиг. 6А-6D показаны виды, иллюстрирующие результаты моделирования, полученные при обучении FEQ с использованием алгоритма минимальной среднеквадратичной ошибки (LMS) при наличии FEXT, а на фиг. 7А-7D показаны виды, иллюстрирующие результаты моделирования, полученные при обучении FEQ с использованием описанного алгоритма типа CDMA, что возможно с использованием описанного варианта осуществления изобретения, при котором исключают FEXT при обучении FEQ. Другие настройки аналогичны и предполагается наличие в среде сравнительно сильного FEXT. На фиг. 6A-6D показано, что сильное FEXT уменьшает точность коэффициента FEQ с использованием обычного LMS алгоритма.

Заметное улучшение эффективности можно увидеть при сравнении фиг. 6A-6D соответственно с фиг. 7A-7D. Например, при увеличении частоты (заметим, что горизонтальная ось во всех результатах моделирования означает индекс гармоники для DMT) до примерно 4000, величина FEQ на фиг. 6А претерпевает внезапное повышение (признак нестабильности), а величина FEQ на фиг. 7А показывает гораздо более плавное повышение. Также, на фиг. 6С показано умножение функции прямого канала и FEQ (в идеале должна быть единица, так как FEQ представляет собой инвертирование прямого канала), которое отклоняется от единицы, а на фиг. 7С показано умножение, остающееся в области единицы независимо от увеличения частоты.

На фиг. 8 показана блок-схема варианта осуществления способа 800, который может быть реализован в DSL системе, например, DSL системе 300 или любой DSL системе, содержащей входящую секцию 100 и исходящую секцию 200. Способ 800 начинается этапом 810, на котором в одном или более устройствах передачи на передающем конце (например, DPU 302) могут передать OPS на множество устройств приема, которые соединены с передающим концом через группу абонентских линий с векторизацией. В альтернативных вариантах осуществления изобретения этап 810 может быть опущен, если OPS вручную сохраняют в устройствах приема.

OPS содержит столбец 0-элементов, которые указывают начало или конец OPS. В одном варианте осуществления изобретения столбец 0-элементов является первым столбцом или последним столбцом OPS (но не обоими столбцами), состоящими из 0-элементов, при этом первый столбец, содержащий только нулевые значения или 0-элементы, указывает начало OPS, а последний столбец, содержащий только 0-элементы, указывает конец OPS. Более того, OPS может содержать ненулевые значения в любом другом столбце за исключением первого или последнего столбцов. Например, OPS может содержать биты, равные плюс единице (+1), и биты, равные минус единице (-1), в другие столбцах за исключением столбца 0-элементов. В зависимости от реализации, в каждом устройстве приема могут принимать всю OPS или соответствующую строку OPS.

На этапе 820 на передающем конце могут модулировать множество синхронизированных сигналов с помощью OPS с целью генерирования множества модулированных синхронизированных сигналов. Модуляция может быть осуществлена любым подходящим образом. При модуляции каждый DMT символ может быть умножен на соответствующий DMT символу элемент, равный +1, или элемент, равный -1, или элемент, равный 0, при этом элемент, равный +1, оставляет DMT символ неизменным при модуляции, элемент, равный -1, изменяет фазу DMT символа на противоположную, а 0-элемент является причиной того, что DMT символ обладает нулевой амплитудой (в качестве альтернативы DMT символ может остаться неизменным, если OPS элемент равен -1, будет инвертирован по фазе, если OPS элемент равен +1).

На этапе 830 на передающем конце могут параллельно передавать множество модулированных синхронизированных сигналов в течение длительности некоторого количества DMT символов, при этом каждый из множества модулированных синхронизированных сигналов предназначен для одного из множества устройств приема. Из-за 0-элемента все множество модулированных синхронизированных сигналов могут обладать нулевой амплитудой во время первого или последнего DMT символа. Далее нулевая амплитуда множества синхронизируемых сигналов может привести к нулевому сигналу на дальнем конце и нулевому FEXT в группе абонентских линий с векторизацией в первом или последнем DMT символах.

В DS направлении каждое из множества устройств передачи может быть блоком FTU-O, расположенным в DPU, и каждое из множества устройств приема может быть расположено в СРЕ, которое выполнено для приема модулированного синхронизированного сигнала, определения нулевой амплитуды модулированного синхронизированного сигнала в течение DMT символа, маркировки DMT символа как начала эталонной тестовой последовательности, известной в СРЕ, и извлечения функции прямого канала из модулированного синхронизированного сигнала на основе эталонной тестовой последовательности.

Специалисту в рассматриваемой области ясно, что способ 800 содержит только часть необходимых этапов при связи между передающим концом и приемным концом, таким образом, дополнительные этапы могут быть встроены в любом подходящем месте или этапы могут быть модифицированы в зависимости от конкретного приложения. Например, в US направлении в способе 800 могут дополнительно принимать от приемного конца соединительной линии, запрос синхронизации до модулирования нескольких синхронизированных сигналов, при этом использование 0-элемента при модулировании нескольких синхронизированных сигналов с помощью OPS, основано на возможности, о которой сообщает приемный конец соединительной линии во время этапа установления связи между одним из устройств передачи и приемным концом соединительной линии.

В другом примере, в случае одного 0-элемента на N OPS периодов, OPS, используемая на этапе 820, может быть первой из множества OPS матриц, при этом остальные множества OPS матриц совпадают с первой OPS за исключением отсутствия 0-элементов в остальных OPS матрицах. Большее количество синхронизированных сигналов может быть модулировано с помощью оставшихся из множества OPS матриц с целью генерирования большего количества модулированных синхронизированных сигналов, которые далее могут быть параллельно переданы в течение длительности большего количества DMT символов во множество устройств приема. После входа в этап нормального функционирования дополнительные синхронизированные сигналы можно не модулировать 0-элементом с целью минимизации затрат.

Здесь описан, по крайней мере, один вариант осуществления изобретения и предложенные специалистом в рассматриваемой области изменения, объединения и/или модификации варианта (вариантов) осуществления изобретения находятся в пределах объема настоящего изобретения. Альтернативные варианты осуществления изобретения, которые могут появиться благодаря объединению, интеграции и/или исключению признаков варианта (вариантов) осуществления изобретения, также находятся в пределах объема настоящего изобретения. Когда числовые диапазоны или ограничения точно заявлены, то такие точные диапазоны или ограничения можно понимать, как содержащие итеративные диапазоны или ограничения аналогичной величины, попадающие в точно заявленные диапазоны или ограничения (например, примерно от 1 до примерно 10 содержит 2, 3, 4 и так далее; более 0,10 включает в себя 0,11, 0,12, 0, 13 и так далее). Например, когда рассматривают числовой диапазон с нижней границей Rl и верхней границей Ru, считаем, что рассматривают любое число, находящееся в этом диапазоне. В частности, рассматривают следующие числа, находящееся в диапазоне: R = Rl + k ⋅ (Ru - Rl), где k является переменной, находящейся в диапазоне от 1 процента до 100 процентов с шагом 1 процент, то есть k является 1 процентом, 2 процентами, 3 процентами, 4 процентами, 5 процентами, …, 50 процентами, 51 процентом, 52 процентами, …, 95 процентами, 96 процентами, 97 процентами, 98 процентами, 99 процентами или 100 процентами. Более того, любой числовой диапазон, определенный двумя действительными числами, как показано выше также считается рассматриваемым. Использование термина «примерно» означает +/-10% от соответствующего числа, если не оговорено обратное. Использование термина «при желании» для любого элемента формулы изобретения означает, что элемент требуется или, в качестве альтернативы, элемент не требуется, при этом обе альтернативы находятся в пределах объема формулы изобретения. Использования более широких терминов, таких как содержит, включает в себя и обладает можно понимать, как заключающее в себя более узкие термины, такие как состоит из, по существу состоит из и по существу выполнено из. Соответственно, приведенное выше описание не ограничивает объем изобретения, который определен приведенной ниже формулой изобретения, при этом объем изобретения включает в себя все эквиваленты объекта патентования из формулы изобретения. Каждый пункт формулы изобретения вставлен в описание как дополнительная информация, и пункты формулы изобретения являются вариантом (вариантами) осуществления настоящего изобретения. Рассмотрение ссылки в изобретении не является допущением, что она принадлежит уровню техники, особенно это касается любой ссылки, содержащей дату публикации после даты приоритета этой заявки. Описание всех патентов, заявок на патенты и публикаций, процитированных в описании, включено в настоящий документ посредством ссылки при условии, что они обеспечивают примеры, процедурные или другие подробности, добавляющие информации к описанию.

Хотя в настоящем описании приведено несколько вариантов осуществления изобретения, может быть ясно, что описанные системы и способы могут быть реализованы многими другими конкретными формами, не выходя за пределы идеи и объема настоящего изобретения. Настоящие примеры надо рассматривать как иллюстрацию, а не как ограничение, и приведенные здесь подробности не предусматривались для ограничения изобретения. Например, различные элементы и компоненты могут быть объединены или скомбинированы в другой системе или определенные признаки могут быть опущены или не реализованы.

Кроме того, технологии, системы, подсистемы и способы, которые описаны и проиллюстрированы в различных вариантах осуществления изобретения как дискретные или отдельные, могут быть объединены или скомбинированы с другими системами, модулями, технологиями или способами, не выходя при этом за пределы объема настоящего изобретения. Другие показанные или описанные элементы, которые соединены или непосредственно соединены, или связаны друг с другом, могут не напрямую соединяться или связываться с помощью некоторого интерфейса, устройства или промежуточного компонента, электрически, механически или другим образом. Другие примеры изменений, замен или модификаций очевидны специалисту в рассматриваемой области и могут быть выполнены без выхода за пределы описанных здесь идеи и объема изобретения.

Изобретение относится к технике связи и может использоваться в синхронизированных системах связи. Технический результат состоит в повышении надежности связи. Для этого способ включает в себя этапы, на которых: модулируют множество синхронизированных сигналов с помощью ортогональной тестовой последовательности (OPS) для генерирования множества модулированных синхронизированных сигналов, при этом OPS содержит нулевой элемент (0-элемент), указывающий начало или конец OPS, и параллельно передают, с использованием одного или более устройств передачи, множество модулированных синхронизированных сигналов в течение длительности некоторого количества дискретных многочастотных символов (DMT), при этом каждый из множества модулированных синхронизированных сигналов предназначен для одного из множества устройств приема, удаленно соединенных с одним или более устройствами передачи через группу абонентских линий с векторизацией, при этом столбец с 0-элементами вызывает то, что все множество модулированных синхронизированных сигналов обладают нулевой амплитудой во время первого или последнего DMT символа. 3 н. и 17 з.п. ф-лы, 16 ил.

1. Способ обеспечения самосинхронизирующейся тестовой последовательности, включающий в себя этапы, на которых:

модулируют множество синхронизированных сигналов с помощью ортогональной тестовой последовательности (OPS), для генерирования множества модулированных синхронизированных сигналов, при этом OPS содержит столбец с нулевыми элементами (0-элемент), указывающий начало или конец OPS; и

параллельно передают, с использованием одного или более устройств передачи, множество модулированных синхронизированных сигналов в течение длительности некоторого количества дискретных многочастотных символов (DMT), при этом каждый из множества модулированных синхронизированных сигналов предназначен для одного из множества устройств приема, удаленно соединенных с одним или более устройствами передачи через группу абонентских линий с векторизацией, причем столбец с 0-элементами вызывает то, что все множество модулированных синхронизированных сигналов обладают нулевой амплитудой во время первого или последнего DMT символа; при этом

столбец с 0-элементами является первым или последним столбцом OPS, при этом первый столбец, содержащий только 0-элементы, указывает начало OPS, а последний столбец, содержащий только 0-элементы, указывает конец OPS, причем OPS не содержит 0-элементов в любом другом столбце за исключением первого или последнего столбца.

2. Способ по п. 1, в котором нулевая амплитуда множества синхронизируемых сигналов приводит к нулевому сигналу дальнего конца и нулевому переходному затуханию (FEXT) на дальнем конце в группе абонентских линий с векторизацией в первом или последнем DMT символах.

3. Способ по п. 2, в котором столбец с 0-элементами содержит 0-элементы, при этом OPS дополнительно содержит элементы плюс единица (+1) и элементы минус единица (-1), расположенные в других столбцах, отличных от столбца с 0-элементами, при этом во время модуляции каждый DMT символ умножают или на элементы +1, или на элементы -1, или на 0-элементы, соответствующие DMT символу, при этом или элемент +1, или элемент -1 оставляет DMT символ неизменным, а другой инвертирует фазу DMT символа при модуляции, а 0-элемент вызывает то, что DMT символ обладает нулевой амплитудой.

4. Способ по п. 3, в котором элементы +1, элементы -1 и 0-элементы представляют двухбитовыми созвездиями, при этом элемент -1 сопоставляют с точкой 1+j созвездия, элемент +1 сопоставляют с точкой -1-i созвездия, а 0-элемент сопоставляют с точкой 0+0j созвездия.

5. Способ по п. 2, дополнительно включающий в себя этап, на котором: передают OPS на множество устройств приема до модуляции множества синхронизированных сигналов с помощью OPS.

6. Способ по п. 2, в котором одно или более устройств передачи расположены в блоке точки распределения (DPU), при этом множество модулированных синхронизированных сигналов передают в группу абонентских линий с векторизацией в направлении нисходящей передачи, а каждый из множества приемников, принадлежащих оконечным абонентским устройствам (СРЕ), выполненным с возможностью приема модулированного синхронизированного сигнала, выполнен с возможностью определения нулевой амплитуды модулированного синхронизированного сигнала в течение DMT символа, маркировки DMT символа, в качестве начала эталонной тестовой последовательности, известной в СРЕ, и извлечения функции прямого канала из модулированного синхронизированного сигнала на основе эталонной тестовой последовательности.

7. Способ по п. 2, в котором столбец с 0-элементами является первым столбцом OPS, при этом OPS является первой матрицей из множества OPS матриц, а оставшиеся из множества OPS матриц идентичны первой OPS матрице за исключением того, что ни одна из оставшихся OPS матриц не содержит столбца с 0-элементами, при этом большее количество синхронизированных символов модулированы с помощью оставшихся из множества OPS матриц для генерирования большего количества модулированных синхронизированных сигналов, передаваемых затем параллельно в течение длительности большего количества DMT символов на множество приемников.

8. Способ по п. 2, дополнительно включающий в себя этапы, на которых: принимают от приемного конца соединительной линии запрос синхронизации до модулирования множества синхронизированных сигналов, при этом модулирование множества синхронизированных сигналов с помощью OPS основано на возможности, о которой сообщает приемный конец соединительной линии во время этапа установки связи между одним из устройств передачи и приемным концом соединительной линии.

9. Устройство обеспечения самосинхронизирующейся тестовой последовательности, содержащее:

один или более процессоров для модулирования множества синхронизированных сигналов с использованием ортогональной тестовой последовательности (OPS), для генерирования множества модулированных синхронизированных сигналов, при этом каждый из множества модулированных синхронизированных сигналов содержит некоторое количество дискретных многочастотных символов (DMT); и

одно или более устройств передачи, соединенных с одним или более процессорами, для параллельной передачи множества модулированных синхронизированных сигналов в течение некоторого количества временных периодов, соответствующих DMT символам, при этом каждый из множества модулированных синхронизированных сигналов предназначен для одного из множества устройств приема, удаленно соединенных с одним или более устройствами передачи через группу абонентских линий с векторизацией, причем все множество модулированных синхронизированных сигналов обладает нулевой амплитудой в первом или последнем временном периоде, при этом

OPS представлена матрицей с множеством строк и множеством столбцов, при этом первый или последний столбец из множества столбцов является столбцом с нулевыми элементами (0-элемент), содержащим только нулевые значения, вызывающие возникновение нулевой амплитуды.

10. Устройство по п. 9, в котором одно или более устройств передачи дополнительно выполнены с возможностью передачи соответствующей строки OPS на соответствующее устройство приема до передачи одного из множества модулированных синхронизированных сигналов.

11. Устройство по п. 9, в котором нулевая амплитуда множества синхронизируемых сигналов приводит к нулевому сигналу дальнего конца и нулевому переходному затуханию (FEXT) на дальнем конце в группе абонентских линий с векторизацией в первом или последнем временном периоде, причем по меньшей мере множество синхронизируемых сигналов обладают ненулевой амплитудой в других временных периодах, отличных от первого или последнего временного периода.

12. Устройство по п. 11, в котором матрица, представляющая OPS, состоит из значений плюс единица (+1) и значений минус единица (-1) в столбцах, отличных от столбца с 0-элементами, при этом во время модуляции каждый DMT символ умножается или на значение +1, или на значение -1, или на нулевое значение, соответствующие DMT символу, при этом или значение +1, или значение -1 оставляет DMT символ неизменным, а другое значение инвертирует фазу DMT символа при модуляции, а нулевое значение вызывает то, что DMT символ обладает нулевой амплитудой.

13. Устройство по п. 11, характеризующееся тем, что выполнено с возможностью передачи множества модулированных синхронизированных сигналов в группу абонентских линий с векторизацией в направлении нисходящей передачи, причем каждое из одного или более устройств передачи является частью блока G.fast приемопередачи на стороне оператора (FTU-О), а каждое из множества устройств приема является частью блока приемопередачи на удаленном терминале G.fast (FTU-R).

14. Устройство по п. 11, в котором столбец с 0-элементами является первым столбцом матрицы, являющейся первой матрицей из множества OPS матриц, при этом оставшиеся из множества OPS матриц идентичны первой матрице за исключением того, что ни одна из оставшихся OPS матриц не содержит столбца с 0-элементами, при этом один или более процессоров дополнительно выполнены с возможностью модулирования дополнительных синхронизированных сигналов с помощью оставшихся множества OPS матриц для генерирования дополнительных модулированных синхронизированных сигналов, и при этом одно или более устройств передачи дополнительно выполнены с возможностью параллельной передачи дополнительных синхронизированных сигналов в течение длительности дополнительных DMT символов на множество устройств приема.

15. Устройство по п. 11, дополнительно содержащее: одно или более устройств приема, соединенных с одним или более процессорами и выполненных для приема от устройства передачи, расположенного на приемном конце соединительной линии, запроса синхронизации, при этом модулирование множества синхронизированных сигналов с помощью OPS основано на возможности, о которой сообщает приемный конец во время этапа установки связи между указанным устройством и приемным концом.

16. Устройство обеспечения самосинхронизирующейся тестовой последовательности, содержащее:

устройство приема для приема сигнала от устройства передачи в течение множества временных периодов, при этом каждый из множества временных периодов соответствует длительности дискретного многочастотного символа (DMT), а каждый DMT символ модулирован элементом тестовой последовательности, при этом тестовая последовательность ортогональна другим тестовым последовательностям других устройств передачи во множестве синхронизированных устройствах передачи; и

процессор, соединенный с устройством приема и выполненный с возможностью:

определения временного периода, когда принятый сигнал обладает нулевой амплитудой во всех каналах сигнала;

синхронизации нулевого элемента (0-элемента) с временным периодом, так что 0-элемент маркирует начало эталонной тестовой последовательности, известной процессору; и

извлечения прямого канала из принятого сигнала в течение некоторого количества временных периодов, следующих за 0-элементом, с использованием эталонной тестовой последовательности, при этом

тестовая последовательность представлена матрицей с множеством строк и множеством столбцов, при этом первый или последний столбец из множества столбцов является столбцом с нулевыми элементами (0-элемент), содержащим только нулевые значения, вызывающие возникновение нулевой амплитуды.

17. Устройство по п. 16, в котором устройство приема дополнительно выполнено с возможностью приема эталонной тестовой последовательности до приема сигнала, при этом эталонную тестовую последовательность используют при извлечении прямого канала из принятого сигнала, а указанное устройство дополнительно содержит память, соединенную с устройством приема и выполненную с возможностью хранения эталонной тестовой последовательности.

18. Устройство по п. 17, в котором эталонная тестовая последовательность состоит из значений плюс единица (+1) и значений минус единица (-1) за исключением 0-элемента, при этом устройство приема дополнительно выполнено с возможностью приема псевдослучайной двоичной последовательности (PRBS), соответствующей принятому сигналу, а извлечение прямого канала дополнительно основано на PRBS.

19. Устройство по п. 16, в котором принятый сигнал содержит компонент, соответствующий прямому каналу, и один или более компонентов, соответствующих одному или более каналам переходного затухания на дальнем конце (FEXT), а все каналы сигнала, содержащие прямой канал и каналы FEXT, обладают нулевой амплитудой в определенном временном периоде.

20. Устройство по п. 16, в котором устройство передачи, выполненное с возможностью передачи входящего сигнала, расположено в блоке G.fast приемопередачи на стороне оператора (FTU-О), при этом устройство приема и процессор являются частями блока G.fast приемопередачи на удаленном терминале (FTU-R), при этом блок FTU-R соединен с блоком FTU-О по абонентской линии.

| Колосоуборка | 1923 |

|

SU2009A1 |

| Способ измерения параметров турбулентности пламени и холодных газовых потоков | 1955 |

|

SU106010A1 |

| WO 00/13324 A1, 09.02.2000 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

Авторы

Даты

2017-04-25—Публикация

2014-04-24—Подача