Предлагаемое изобретение относится к радиолокации, в частности к устройству цифровой активной фазированной антенной решетки (ЦАФАР), работающей в составе импульсно-доплеровской бортовой радиолокационной станции (БРЛС). Изобретение может быть использовано в ЦАФАР для снижения объема и скорости передачи цифровых данных в центральный процессор.

В настоящее время в БРЛС в качестве антенны все чаще используют ЦАФАР, где осуществляется распределенное генерирование, распределенный прием и обработка принятых сигналов. Использование ЦАФАР повышает возможности БРЛС по получению информации о нескольких разнесенных по углу целях, по подавлению активных помех, позволяет решать многофункциональные задачи на базе одной БРЛС. Одним из требований к современным антеннам является возможность формирования множества различных приемных диаграмм, что определяет ее структуру с использованием цифровой пространственной обработки принятого сигнала.

При переходе от АФАР к ЦАФАР возникают новые технические проблемы. Во-первых, это необходимость реализации многоканального приемника, что приводит к росту габаритов, массы и стоимости аппаратуры. Во-вторых, это огромный объем цифровых данных, которые необходимо передать в центральный процессор и обработать. Это требует реализации высокоскоростных каналов передачи цифровых данных. Центральный процессор должен обеспечить прием и обработку этих данных в реальном времени. Для сокращения нагрузки на центральный процессор и для разгрузки каналов передачи данных необходимо выполнить часть обработки цифровых сигналов в приемо-передающих модулях (ППМ).

В [3] описан метод обработки сигнала в ЦАФАР для формирования квадратурного сигнала цифровым способом с переносом на нулевую частоту, который после обработки сигнала в цифровом ФНЧ и децимации отсчетов позволяет снизить объем цифровых данных примерно в 2 раза. Для получения квадратурного сигнала в качестве одного из вариантов предлагается использовать специализированный сигнальный процессор DDC (Digital Down Converter). Однако автор не рассматривает вопросы буферизации цифровых данных для снижения пиковой скорости передачи данных.

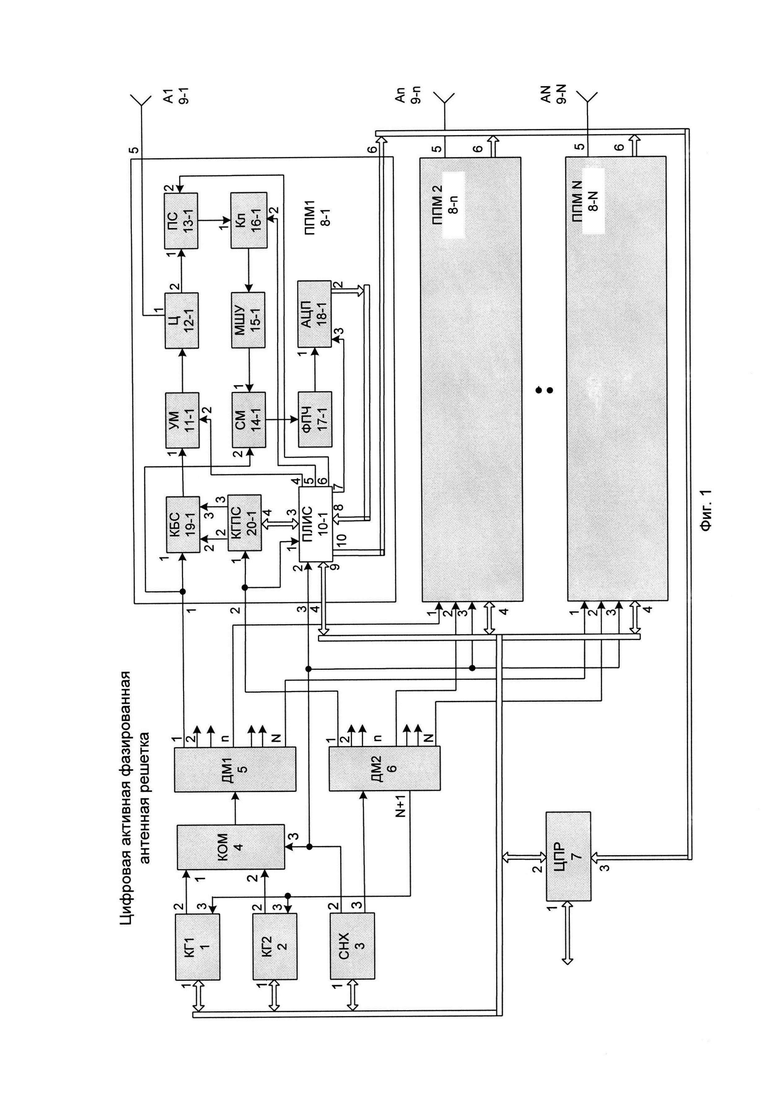

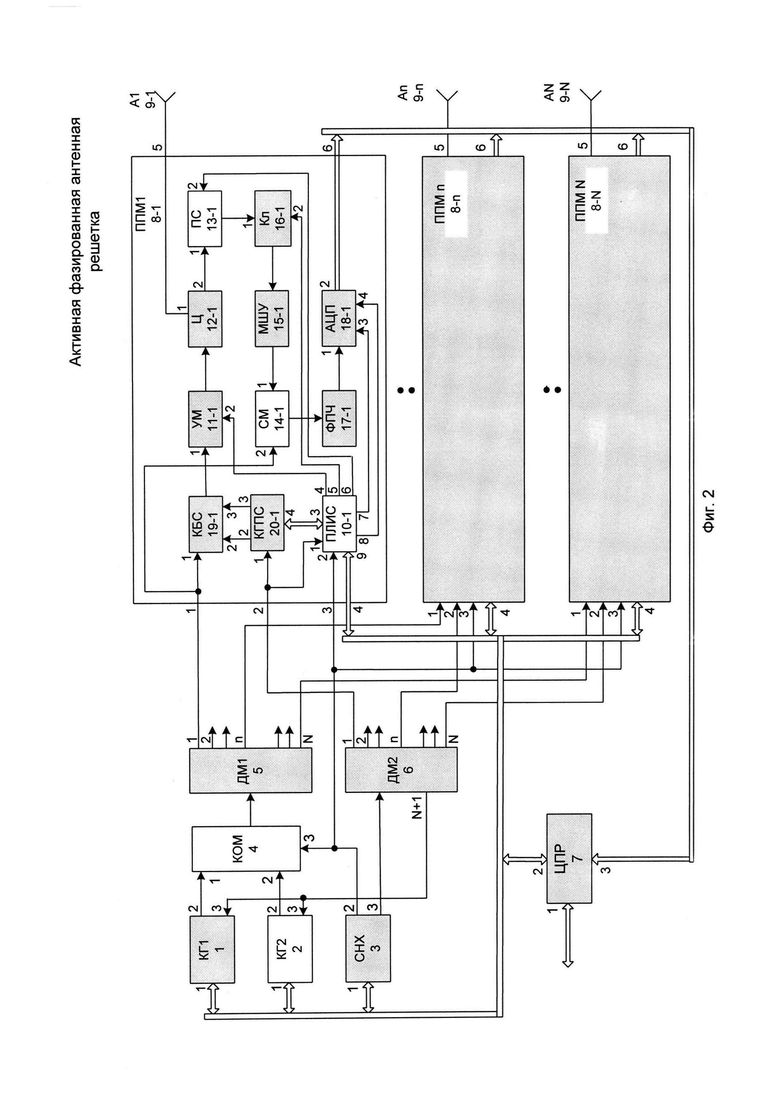

Известна цифровая активная фазированная антенная решетка [1], блок-схема которой показана на Фиг. 2, используемая в качестве прототипа. Ее работа выполняется следующим образом.

Перед началом работы центральный процессор 7 через второй вход-выход по шине управления задает значения параметров выбранного режима работы ЦАФАР. При этом устанавливается частота колебаний первого когерентного гетеродина 1 (гетеродин передатчика) и второго когерентного гетеродина 2 (гетеродин приемника). В синхронизатор 3 передаются значения длительности зондирующих импульсов и периода их повторения. В программируемую логическую интегральную схему (ПЛИС) 10-n каждого ППМ 8-n передаются значения амплитуды и начальной фазы сигнала, необходимые для формирования передающей ДН антенны, а также частота сигнала КГПС 20-n и параметры внутриимпульсной модуляции зондирующего импульса. Эти параметры через третий вход-выход ПЛИС 10-n передаются в КГПС 20-n. В ПЛИС 10-n передаются параметры настройки преселекторов, в соответствии с которыми ПЛИС вырабатывает сигналы управления и с шестого выхода передает их на второй вход преселектора 13-n. В ПЛИС 10-n передаются также параметры приемного строба и частоты дискретизации, которые используются для управления работой АЦП 18-n.

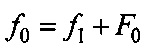

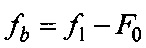

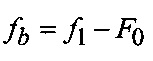

При этом первый когерентный гетеродин 1 формирует сигнал гетеродина передатчика с частотой  , а второй когерентный гетеродин 2 формирует сигнал гетеродина приемника с частотой

, а второй когерентный гетеродин 2 формирует сигнал гетеродина приемника с частотой  , которые поступают на входы коммутатора 4. Синхронизатор 3 формирует на третьем выходе последовательность тактовых импульсов. Через делитель мощности 6 эта последовательность импульсов поступает на первые входы КГПС 20-n и ПЛИС 10-n. Она же поступает на третьи входы когерентных гетеродинов 1 и 2. При этом все сигналы и гетеродин формируются от одной последовательности импульсов, стабилизированной кварцевым резонатором, что обеспечивает пространственную и временную когерентность ЦАФАР. В ПЛИС 10-n последовательность импульсов, поступающая на вход 1, используется для формирования всех сигналов синхронизации работы ППМ. Делением ее частоты получается последовательность импульсов дискретизации, которая через седьмой выход подается на третий вход АЦП 18-n. Это обеспечивает синхронную временную дискретизацию всех принятых сигналов, что сохраняет их пространственную когерентность.

, которые поступают на входы коммутатора 4. Синхронизатор 3 формирует на третьем выходе последовательность тактовых импульсов. Через делитель мощности 6 эта последовательность импульсов поступает на первые входы КГПС 20-n и ПЛИС 10-n. Она же поступает на третьи входы когерентных гетеродинов 1 и 2. При этом все сигналы и гетеродин формируются от одной последовательности импульсов, стабилизированной кварцевым резонатором, что обеспечивает пространственную и временную когерентность ЦАФАР. В ПЛИС 10-n последовательность импульсов, поступающая на вход 1, используется для формирования всех сигналов синхронизации работы ППМ. Делением ее частоты получается последовательность импульсов дискретизации, которая через седьмой выход подается на третий вход АЦП 18-n. Это обеспечивает синхронную временную дискретизацию всех принятых сигналов, что сохраняет их пространственную когерентность.

После установки всех параметров из процессора 7 в синхронизатор 3 выдается команда начала работы. На каждом периоде повторения синхронизатор формирует на втором выходе видеоимпульс запуска передатчика, определяющий временное положение и длительность зондирующего импульса. На время действия импульса коммутатор 4 подключает второй выход первого когерентного гетеродина 1 к входу делителя мощности 5, поэтому на первые входы квадратурных балансных смесителей 19-n поступает гетеродин передатчика. Видеоимпульс подается также на второй вход ПЛИС 10-n и используется для синхронизации работы всех ППМ. ПЛИС передает этот импульс через четвертый выход на второй вход усилителей мощности 11-n для формирования огибающей зондирующего импульса. С пятого выхода ПЛИС на второй вход ключа 16-n подается импульс бланкирования приемника. По фронту импульса через третий вход-выход в КГПС 20-n подается команда начала работы. Это приводит к одновременному запуску формирования закона модуляции зондирующего импульса всех ППМ, что обеспечивает пространственную когерентность сигналов.

При этом на выходах всех КГПС 20-n формируются квадратурные сигналы с частотой F0 и одинаковым законом угловой модуляции ϕ(f). Амплитуда и начальная фаза сигналов Un, ϕn заданы индивидуально для каждого ППМ и определяют форму и направление ДН передающей антенны. На выходе квадратурных балансных смесителей 19-n формируется сигнал с частотой  . Кроме того, на выход смесителя проходит неподавленный остаток гетеродина передатчика с частотой

. Кроме того, на выход смесителя проходит неподавленный остаток гетеродина передатчика с частотой  , а также остаток второй боковой составляющей модуляции с частотой

, а также остаток второй боковой составляющей модуляции с частотой  .

.

Сформированный сигнал с выхода смесителя 19-n подается на первый вход усилителя мощности 11-n, который обеспечивает формирование огибающей зондирующего импульса и его усиление до требуемой мощности. Затем зондирующий импульс через циркулятор 12-n передается на элемент антенной решетки 9-n и излучается. В это время на первый вход смесителя 14-n поступает неподавленный ключом 16-n остаток излучаемого сигнала, а на второй его вход поступает гетеродин передатчика с частотой  . При этом сигналы на выходе смесителя имеют частоту F0, которая много меньше промежуточной, что защищает тракт ПЧ от перегрузки.

. При этом сигналы на выходе смесителя имеют частоту F0, которая много меньше промежуточной, что защищает тракт ПЧ от перегрузки.

По окончании импульса запуска передатчика излучение зондирующего сигнала прекращается и все ППМ переводятся в режим приема. При этом коммутатор 4 подключает второй выход второго когерентного гетеродина 2 к входу делителя мощности 5. Гетеродин приемника с частотой  через коммутатор 4, делитель мощности 5 и входы 1-n всех ППМ поступает на вторые входы смесителей 14-n. Принятый элементами антенны 9-n сигнал через циркулятор 12-n, преселектор 13-n, открытый ключ 16-n, малошумящий усилитель 15-n поступает на смеситель 14-n, а с его выхода - на вход фильтра промежуточной частоты 17-n. При этом преселектор обеспечивает подавление помех на частоте зеркального канала приема, а также широкополосных помех.

через коммутатор 4, делитель мощности 5 и входы 1-n всех ППМ поступает на вторые входы смесителей 14-n. Принятый элементами антенны 9-n сигнал через циркулятор 12-n, преселектор 13-n, открытый ключ 16-n, малошумящий усилитель 15-n поступает на смеситель 14-n, а с его выхода - на вход фильтра промежуточной частоты 17-n. При этом преселектор обеспечивает подавление помех на частоте зеркального канала приема, а также широкополосных помех.

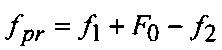

Промежуточная частота сигнала на выходе смесителя  . Сигнал, излученный на частоте

. Сигнал, излученный на частоте  после отражения от цели, приема и преобразования частоты в смесителе, имеет частоту

после отражения от цели, приема и преобразования частоты в смесителе, имеет частоту  . Она отличается от промежуточной на 2F0, что превышает ширину полосы пропускания фильтра промежуточной частоты 17-n. Это обеспечивает эффективное подавление мешающего сигнала.

. Она отличается от промежуточной на 2F0, что превышает ширину полосы пропускания фильтра промежуточной частоты 17-n. Это обеспечивает эффективное подавление мешающего сигнала.

При работе ППМ в режиме приема устойчивость работы его СВЧ-части обеспечивается несколькими способами. Развязка приемника и передатчика обеспечивается применением раздельных смесителей и циркулятора. Кроме того, по окончании импульса запуска передатчика запирается усилитель мощности 11-n, а КГПС 20-n прекращает формирование сигнала, что приводит к запиранию квадратурного балансного смесителя 19-n. Перечисленные меры обеспечивают не только устойчивость схемы, но и глубокое подавление шумов передатчика на входе приемника.

Выделенный фильтром 17-n сигнал от цели поступает на первый вход АЦП 18-n. На его третий вход поступает последовательность импульсов дискретизации с седьмого выхода ПЛИС 10-n. В соответствии с заданными параметрами ПЛИС 10-n формирует на восьмом выходе видеоимпульс, определяющий временное положение и длительность приемного строба. Для обеспечения пространственной когерентности сигналов приемный строб всех ППМ жестко привязан к фронту импульса запуска передатчика. Он подается на четвертый вход АЦП 18-n и определяет множество временных отсчетов сигнала, которые со второго входа-выхода АЦП 18-n через шестой выход ППМ 8-n передаются на третий вход центрального процессора 7.

Частота дискретизации  должна как минимум в 2 раза превышать ширину спектра принятого сигнала. Для минимизации числа отсчетов промежуточная частота

должна как минимум в 2 раза превышать ширину спектра принятого сигнала. Для минимизации числа отсчетов промежуточная частота  должна быть кратной частоте дискретизации. Тогда АЦП обеспечивает цифровое преобразование частоты сигнала на нулевую промежуточную частоту. Оцифрованный сигнал со второго выхода АЦП 18-n по сигнальной шине передачи цифровых данных передается на третий вход центрального процессора 7. Все остальные операции, связанные с пространственной и временной обработкой сигнала, выполняются в цифровой форме в центральном процессоре.

должна быть кратной частоте дискретизации. Тогда АЦП обеспечивает цифровое преобразование частоты сигнала на нулевую промежуточную частоту. Оцифрованный сигнал со второго выхода АЦП 18-n по сигнальной шине передачи цифровых данных передается на третий вход центрального процессора 7. Все остальные операции, связанные с пространственной и временной обработкой сигнала, выполняются в цифровой форме в центральном процессоре.

Недостатком данной ЦАФАР является большой объем цифровых данных, передаваемых в центральный процессор, а также высокая пиковая скорость передачи цифровых данных. Они формируются только во время приемного строба, который имеет скважность не ниже 3. АЦП передает их в реальном времени в центральный процессор без буферизации. При этом цифровой канал данных реально использует в лучшем случае треть времени, а пиковая скорость передачи данных как минимум в 3 раза превышает среднюю. Кроме того, передаваемый цифровой сигнал имеет достаточно высокую частоту дискретизации, обеспечивающую цифровое формирование квадратурного сигнала в центральном процессоре с подавлением посторонних участков спектра, что увеличивает общее число временных отсчетов. Все это затрудняет реализацию цифровых каналов передачи данных и повышает их стоимость.

Целью предлагаемого изобретения является снижение объема формируемых в каждом ППМ цифровых данных и пиковой скорости их передачи в центральный процессор.

Реализация поставленной цели в предлагаемой ЦАФАР обеспечивается передачей формируемых в АЦП цифровых данных в ПЛИС, формированием временных отсчетов квадратурного сигнала и переносом его спектра на нулевую частоту, обработкой квадратурного сигнала в цифровом ФНЧ для обужения спектра, децимацией временных отсчетов для снижения их количества, буферизацией данных для снижения пиковой скорости их передачи. Обработанные таким образом цифровые данные собираются в пакеты (кадры) и передаются из ПЛИС в центральный процессор. При этом общий объем данных снижается примерно в 2 раза, а пиковая скорость передачи данных - в 6 раз.

Для достижения поставленной цели в ЦАФАР [1], содержащей первый и второй когерентные СВЧ гетеродины, выходы которых через первый и второй входы коммутатора соединены с входом первого делителя мощности, выходы которого соединены с первыми входами N приемо-передающих модулей (ППМ), синхронизатор, второй выход которого соединен с третьим входом коммутатора и с третьими входами всех ППМ, третий выход синхронизатора через второй делитель мощности соединен со вторыми входами всех ППМ, N+1-й выход второго делителя мощности соединен с третьими входами первого и второго когерентных гетеродинов, первый вход каждого ППМ через последовательно соединенные квадратурный балансный смеситель, усилитель мощности, циркулятор и пятый вход-выход ППМ соединен с элементом антенной решетки (АР), номер которого соответствует номеру ППМ, второй выход циркулятора каждого ППМ через последовательно соединенные преселектор, ключ защиты, малошумящий усилитель, смеситель, фильтр промежуточной частоты соединен с первым входом АЦП, второй вход смесителя соединен с первым входом ППМ, второй вход каждого ППМ соединен с первым входом программируемой логической интегральной схемы (ПЛИС) и с первым входом квадратурного генератора прямого цифрового синтеза (КГПС), второй и третий выходы которого соединены со вторым и третьим входами квадратурного балансного смесителя, третий вход каждого ППМ соединен со вторым входом ПЛИС, третий вход-выход которой соединен с четвертым входом-выходом КГПС, четвертый выход ПЛИС соединен со вторым входом усилителя мощности, пятый выход ПЛИС соединен со вторым входом ключа защиты, шестой выход ПЛИС соединен со вторым входом преселектора, седьмой выход ПЛИС соединен с третьим входом АЦП, девятый вход-выход ПЛИС через четвертый вход-выход каждого ППМ и сигнальную шину соединен со вторым входом-выходом центрального процессора, который по этой же шине соединен с первыми входами-выходами синхронизатора, первого и второго когерентных гетеродинов, первый вход-выход центрального процессора обеспечивает связь ЦАФАР с потребителем, введена обработка формируемых в АЦП цифровых данных в ПЛИС каждого ППМ, для чего второй выход АЦП каждого ППМ через шину данных соединен с восьмым входом ПЛИС, десятый выход ПЛИС через шестой выход каждого ППМ и шину данных соединен с третьим входом центрального процессора, при этом центральный процессор для заданного потребителем режима работы ЦАФАР выдает команды установки частоты в первый и второй когерентные СВЧ гетеродины, команды установки периода повторения и длительности зондирующих импульсов в синхронизатор, команды установки начальной фазы и амплитуды сигнала индивидуально для каждого ППМ, общих параметров модуляции сигнала и приемного строба в ПЛИС каждого ППМ; центральный процессор по известным алгоритмам выполняет цифровую обработку принятого сигнала; ПЛИС в каждом ППМ обеспечивает настройку полосы пропускания преселектора, установку параметров сигнала в КГПС, на время формирования зондирующего импульса открывает усилитель мощности и запирает ключ защиты приемника, формирует последовательность импульсов дискретизации для управления работой АЦП, принимает от АЦП непрерывную последовательность временных отсчетов принятого сигнала, выполняет их стробирование в соответствии с заданными параметрами приемного строба, по известным алгоритмам формирует из них временные отсчеты квадратурного сигнала, смещает его спектр на нулевую частоту, обрабатывает в цифровом фильтре нижних частот, выполняет децимацию временных отсчетов, затем выполняет их буферизацию, формирует пакеты данных и передает их для обработки в центральный процессор.

Сущность изобретения поясняется дальнейшим описанием и чертежами предлагаемой ЦАФАР.

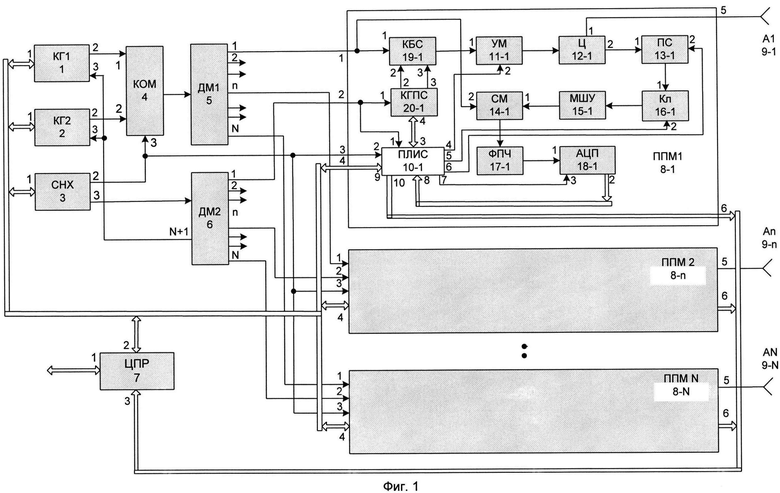

Фиг. 1 - структурная схема ЦАФАР.

На фиг. 1 приняты следующие обозначения:

1 - Первый когерентный СВЧ гетеродин (КГ1),

2 - Второй когерентный СВЧ гетеродин (КГ2),

3 - Синхронизатор (СНХ);

4 - Коммутатор (КОМ),

5 - Первый делитель мощности (ДМ1),

6 - Второй делитель мощности (ДМ2),

7 - Центральный процессор (ЦПР),

8-n - Приемо-передающий модуль с номером n (ППМn),

9-n - Элемент антенной решетки с номером n (An),

10-n - Программируемая логическая интегральная схема (ПЛИС),

11-n - Усилитель мощности (УМ),

12-n - Циркулятор (Ц),

13-n - Преселектор (ПС),

14-n - Смеситель (СМ),

15-n - Малошумящий усилитель (МШУ),

16-n - Ключ защиты приемника (Кл),

17-n - Фильтр ПЧ (ФПЧ),

18-n - Аналого-цифровой преобразователь (АЦП),

19-n - Квадратурный балансный смеситель (КБС),

20-n - Квадратурный генератор прямого цифрового синтеза (КГПС).

В ЦАФАР, изображенной на фиг. 1, второй выход первого когерентного СВЧ гетеродина 1 соединяется с первым входом коммутатора 4, второй выход второго когерентного СВЧ гетеродина 2 соединяется со вторым входом коммутатора 4, выход которого соединен с входом первого делителя мощности 5, к выходам которого подключены первые входы всех ППМ 8-n. Второй выход синхронизатора 3 соединен с третьим входом коммутатора 4 и через третьи входы каждого ППМ 8-n соединен со вторым входом ПЛИС 10-n. Третий выход синхронизатора 3 соединен с входом второго делителя мощности 6, к выходам которого подключены вторые входы всех ППМ 8-n. (N+1)-й выход второго делителя мощности 6 соединен с третьим входом первого и второго когерентных гетеродинов 1 и 2.

Первый вход каждого ППМ 8-n через последовательно соединенные квадратурный балансный смеситель 19-n, усилитель мощности 11-n, циркулятор 12-n, преселектор 13-n, ключ защиты 16-n, малошумящий усилитель 15-n, смеситель 14-n, фильтр ПЧ 17-n соединен с первым входом АЦП 18-n. Первый вход-выход циркулятора 12-n через пятый вход-выход ППМ 8-n соединен с элементом АР 9-n, номер которого соответствует номеру ППМ. Первый вход каждого ППМ 8-n соединен со вторым входом смесителя 14-n. Второй вход каждого ППМ 8-n соединен с первым входом КГПС 20-n и с первым входом ПЛИС 10-n. Второй и третий выходы КГПС 20-n соединены со вторым и третьим входами квадратурного балансного смесителя 19-n. Четвертый вход-выход КГПС 20-n подключен к третьему входу-выходу ПЛИС 10-n. Четвертый, пятый и шестой выходы ПЛИС 10-n соединены со вторыми входами усилителя мощности 11-n, ключа защиты 16-n и преселектора 13-n соответственно. Седьмой выход ПЛИС 10-n соединен с третьим входом АЦП 18-n, второй выход которого через шину данных соединен с восьмым входом ПЛИС 10-n. Десятый выход ПЛИС 10-n через шестой выход каждого ППМ 8-n и шину данных соединен с третьим входом центрального процессора 7. Второй вход-выход центрального процессора 7 через шину управления соединен с первыми входами-выходами первого и второго когерентных гетеродинов 1 и 2, синхронизатора 3, а через четвертые входы-выходы всех ППМ 8-n соединен с девятым входом-выходом ПЛИС 10-n. Первый вход-выход центрального процессора 7 обеспечивает связь ЦАФАР с потребителем.

В качестве синхронизатора 3 может быть использована микросхема EP3C55F484I7N семейства Cyclone III фирмы Altera.

В качестве КГПС сигналов 20-n может быть использована микросхема AD9959 фирмы Analog Device.

В качестве квадратурных балансных смесителей 19-n может быть использована микросхема НМС709 фирмы Hittite Microwave Corp.

В качестве малошумящих усилителей 15-n может быть использована микросхема НМС564 фирмы Hittite Microwave Corp.

В качестве ключей защиты ППМ 16-n может быть использована микросхема НМС347 фирмы Hittite Microwave Corp.

В качестве преселектора 13-n может быть использован микрополосковый полосовой фильтр. Для обеспечения работы в нескольких поддиапазонах можно использовать несколько коммутируемых фильтров.

В качестве центрального процессора 7 может быть использована вычислительная машина НКШР.466535.133 производства НКБВС, г. Таганрог.

Когерентные гетеродины 1 и 2 с режимом формирования ЛЧМ-колебаний могут быть реализованы на микросхеме AD9959 фирмы Analog Device, включенной в кольцо цифровой ФАПЧ [2].

Коммутатор 4 может быть реализован на микросхеме HMC547LP3 фирмы Hittite Microwave Corp.

Аналого-цифровые преобразователи 18-n могут быть выполнены на микросхеме AD9228 фирмы Analog Device.

В качестве ПЛИС 10-n можно использовать микросхему EP3C25F256I7N семейства Cyclone III фирмы Altera.

Остальные элементы ЦАФАР широко используются в радиолокации и не требуют пояснений по реализации.

С учетом структуры и технических возможностей перечисленных микросхем возможно конструктивное объединение четырех ППМ в один модуль, что позволяет сократить число используемых дорогостоящих микросхем. Для каждого модуля потребуется одна ПЛИС EP3C25F256I7N, одна микросхема АЦП AD9228 и две микросхемы КГПС AD9959. Кроме того, это позволяет использовать для четырех ППМ общие кабели и шины передачи цифровых данных. Все это позволяет снизить стоимость, габариты и массу ЦАФАР.

Работа предлагаемой ЦАФАР производится следующим образом.

Перед началом работы центральный процессор 7 через второй вход-выход по шине управления задает значения параметров выбранного режима работы ЦАФАР. При этом устанавливается частота колебаний первого когерентного гетеродина 1 (гетеродин передатчика) и второго когерентного гетеродина 2 (гетеродин приемника). В синхронизатор 3 передаются значения длительности зондирующего импульса, периода повторения импульсов и параметров его вобуляции. В ПЛИС 10-n каждого ППМ передаются индивидуальные значения амплитуды и начальной фазы сигнала для формирования передающей ДН антенны, а также одинаковые значения частоты сигнала КГПС и параметров внутриимпульсной модуляции зондирующего сигнала. Эти параметры через третий вход-выход ПЛИС 10-n передаются в КГПС 20-n. В ПЛИС 10-n передаются параметры настройки преселекторов, в соответствии с которыми ПЛИС вырабатывает сигналы управления и передает их на вход 2 преселектора 13-n. В ПЛИС 10-n передаются также параметры приемного строба и частоты дискретизации, которые используются для формирования временных отсчетов принятого сигнала.

При этом первый когерентный гетеродин 1 формирует сигнал гетеродина передатчика с частотой  , а второй когерентный гетеродин 2 формирует сигнал гетеродина приемника с частотой

, а второй когерентный гетеродин 2 формирует сигнал гетеродина приемника с частотой  , которые поступают на входы коммутатора 4. Синхронизатор 3 формирует на третьем выходе последовательность тактовых импульсов. Через делитель мощности 6 эта последовательность импульсов поступает на первые входы КГПС 20-n в качестве тактовых импульсов. Она же поступает на третьи входы когерентных гетеродинов 1 и 2 и на второй вход ПЛИС 10-n. При этом все сигналы и гетеродины формируются от одной последовательности тактовых импульсов, стабилизированной кварцевым резонатором, что обеспечивает их пространственную и временную когерентность. В ПЛИС 10-n последовательность импульсов, поступающая на первый вход, используется для формирования всех сигналов синхронизации работы ППМ 8-n. Делением ее частоты получается последовательность импульсов дискретизации, которая через седьмой выход подается на третий вход АЦП 18-n. Это обеспечивает синхронную временную дискретизацию всех принятых сигналов, что сохраняет их пространственную когерентность.

, которые поступают на входы коммутатора 4. Синхронизатор 3 формирует на третьем выходе последовательность тактовых импульсов. Через делитель мощности 6 эта последовательность импульсов поступает на первые входы КГПС 20-n в качестве тактовых импульсов. Она же поступает на третьи входы когерентных гетеродинов 1 и 2 и на второй вход ПЛИС 10-n. При этом все сигналы и гетеродины формируются от одной последовательности тактовых импульсов, стабилизированной кварцевым резонатором, что обеспечивает их пространственную и временную когерентность. В ПЛИС 10-n последовательность импульсов, поступающая на первый вход, используется для формирования всех сигналов синхронизации работы ППМ 8-n. Делением ее частоты получается последовательность импульсов дискретизации, которая через седьмой выход подается на третий вход АЦП 18-n. Это обеспечивает синхронную временную дискретизацию всех принятых сигналов, что сохраняет их пространственную когерентность.

После установки всех параметров из процессора 7 в синхронизатор 3 выдается команда начала работы. На каждом периоде повторения синхронизатор формирует на втором выходе видеоимпульс запуска передатчика, определяющий временное положение и длительность зондирующего импульса. На время действия импульса коммутатор 4 подключает второй выход первого когерентного гетеродина 1 к входу делителя мощности 5, поэтому на первые входы квадратурных балансных смесителей 19-n поступает гетеродин передатчика. Видеоимпульс подается также на второй вход ПЛИС 10-n всех ППМ и используется для синхронизации их работы. ПЛИС передает этот импульс через четвертый выход на второй вход усилителей мощности 11-n для формирования огибающей зондирующего импульса. С пятого выхода ПЛИС на второй вход ключа 16-n подается импульс бланкирования приемника. По фронту импульса через третий вход-выход в КГПС 20-n подается команда начала работы. Это приводит к одновременному запуску формирования закона модуляции зондирующего импульса всех ППМ, что обеспечивает пространственную когерентность сигналов.

При этом на выходах всех КГПС 20-n формируются квадратурные сигналы с частотой F0 и одинаковым законом угловой модуляции ϕ(t). Амплитуда и начальная фаза сигналов Un, ϕn заданы индивидуально для каждого ППМ и определяют форму и направление ДН передающей антенны. На выходе квадратурных балансных смесителей 19-n формируется сигнал с частотой  . Кроме того, на выход смесителя проходит неподавленный остаток гетеродина передатчика с частотой

. Кроме того, на выход смесителя проходит неподавленный остаток гетеродина передатчика с частотой  , а также остаток второй боковой составляющей модуляции с частотой

, а также остаток второй боковой составляющей модуляции с частотой  .

.

Сформированный сигнал с выхода смесителя 19-n подается на вход усилителя мощности 11-n, который обеспечивает формирование огибающей зондирующего импульса и его усиление до требуемой мощности. Затем зондирующий импульс через циркулятор 12-n передается на элемент антенной решетки 9-n и излучается. В это время на первый вход смесителя 14-n поступает неподавленный циркулятором 12-n и ключом 16-n остаток зондирующего сигнала, а на второй его вход поступает гетеродин передатчика с частотой  . При этом сигналы на выходе смесителя имеют частоту F0, которая меньше промежуточной, что защищает тракт ПЧ от перегрузки.

. При этом сигналы на выходе смесителя имеют частоту F0, которая меньше промежуточной, что защищает тракт ПЧ от перегрузки.

По окончании импульса запуска передатчика излучение зондирующего сигнала прекращается и ППМ переводится в режим приема. При этом коммутатор 4 подключает второй выход второго когерентного гетеродина 2 к входу первого делителя мощности 5. Гетеродин приемника с частотой  через коммутатор 4, делитель мощности 5 и входы 1-n всех ППМ поступает на вторые входы смесителей 14-n. Принятый элементами антенны 9-n сигнал через циркулятор 12-n, преселектор 13-n, открытый ключ 16-n, малошумящий усилитель 15-n поступает на смеситель 14-n, а с его выхода - на вход фильтра ПЧ 17-n. При этом преселектор обеспечивает подавление помех на частоте зеркального канала приема, а также широкополосных помех.

через коммутатор 4, делитель мощности 5 и входы 1-n всех ППМ поступает на вторые входы смесителей 14-n. Принятый элементами антенны 9-n сигнал через циркулятор 12-n, преселектор 13-n, открытый ключ 16-n, малошумящий усилитель 15-n поступает на смеситель 14-n, а с его выхода - на вход фильтра ПЧ 17-n. При этом преселектор обеспечивает подавление помех на частоте зеркального канала приема, а также широкополосных помех.

При работе ППМ в режиме приема устойчивость работы его СВЧ-части обеспечивается несколькими способами. Развязка приемника и передатчика обеспечивается применением раздельных смесителей и циркулятора. Кроме того, по окончании импульса запуска передатчика запирается усилитель мощности 11-n, а КГПС 20-n прекращает формирование сигнала, что приводит к запиранию квадратурного балансного смесителя 19-n. Перечисленные меры обеспечивают не только устойчивость схемы, но и подавление шумов передатчика на входе приемника.

Выделенный фильтром ПЧ 17-n сигнал поступает на первый вход АЦП 18-n. На его третий вход поступает последовательность импульсов дискретизации с седьмого выхода ПЛИС 10-n. При этом АЦП формирует непрерывную последовательность временных отсчетов сигнала, которые со второго выхода АЦП 18-n по информационной шине передаются на восьмой вход ПЛИС 10-n.

ПЛИС выполняет селекцию временных отсчетов в соответствии с заданными параметрами приемного строба. Затем известными методами [3, разделы 3.5-3.7] выполняет цифровое преобразование на нулевую частоту с одновременным формированием квадратурного сигнала и выделение спектра сигнала цифровым ФНЧ для защиты от наложения спектров цифрового сигнала. Аналогичную обработку выполняет специализированная микросхема AD 6620, но это может быть реализовано и на ПЛИС, которая уже имеется в составе ППМ. После этого ПЛИС выполняет децимацию временных отсчетов и их буферизацию, формирует пакеты данных и через десятый выход по информационной шине передает их для обработки в центральный процессор 7.

Затем процессор по известным алгоритмам выполняет пространственную, временную и вторичную обработку полученных цифровых данных.

Описанное выше формирование квадратурного сигнала вместо ПЛИС может быть выполнено в центральном процессоре, однако это приведет к сильному росту объема и скорости передачи цифровых данных. Частоту дискретизации АЦП приходится увеличить примерно в 2 раза для упрощения реализации цифрового ФНЧ, выполняющего защиту от наложения спектров цифрового сигнала [3]. Поэтому после обработки сигнала цифровым ФНЧ и децимации объем передаваемых из каждого ППМ в центральный процессор цифровых данных сокращается в 2 раза. Буферизация временных отсчетов в ПЛИС обеспечивает равномерную во времени загрузку цифровых каналов передачи данных. При скважности приемного строба, равной 3, достигается трехкратное снижение пиковой скорости передачи данных. С учетом двукратного снижения объема данных общее снижение пиковой скорости передачи составляет 6 раз.

Согласно сведениям, представленным в материалах заявки, ЦАФАР может быть изготовлена по существующей известной в радиопромышленности технологии на базе известных комплектующих изделий и использована в БРЛС летательных аппаратов.

ЛИТЕРАТУРА

1 Патент РФ МПК H01Q 3/00, H01Q 3/26 №2451373 от 20.05.12 г. Активная фазированная антенная решетка.

2 Манасевич В. Синтезаторы частоты, теория и проектирование. Пер. с англ. - М.: Связь, 1979. - 384 с.

3 Григорьев Л.Н. Цифровое формирование диаграммы направленности в фазированных антенных решетках. - М.: Радиотехника, 2010. - 144 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2015 |

|

RU2608637C1 |

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2010 |

|

RU2451373C1 |

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2012 |

|

RU2531562C2 |

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2018 |

|

RU2710105C1 |

| СПОСОБ ПОВЫШЕНИЯ ШИРОКОПОЛОСНОСТИ ПРИЕМОПЕРЕДАЮЩЕГО МОДУЛЯ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ, ИСПОЛЬЗУЮЩЕГО ГЕНЕРАЦИЮ СИГНАЛОВ МЕТОДОМ ПРЯМОГО ЦИФРОВОГО СИНТЕЗА, И ВАРИАНТЫ ЕГО РЕАЛИЗАЦИИ | 2008 |

|

RU2392704C1 |

| МОНОИМПУЛЬСНАЯ РЛС МИЛЛИМЕТРОВОГО ДИАПАЗОНА | 2015 |

|

RU2600109C1 |

| ИМПУЛЬСНО-ДОПЛЕРОВСКАЯ МОНОИМПУЛЬСНАЯ РЛС | 2011 |

|

RU2497146C2 |

| МНОГОФУНКЦИОНАЛЬНАЯ МНОГОДИАПАЗОННАЯ МАСШТАБИРУЕМАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ДЛЯ ЛЕТАТЕЛЬНЫХ АППАРАТОВ | 2011 |

|

RU2496120C2 |

| Многофункциональная малогабаритная радиолокационная система для летательных аппаратов | 2016 |

|

RU2630278C1 |

| СПОСОБ ВСТРОЕННОГО КОНТРОЛЯ ХАРАКТЕРИСТИК ЦИФРОВОЙ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2020 |

|

RU2752553C1 |

Изобретение относится к радиолокации. Особенностью заявленной цифровой активной фазированной антенной решетки (ЦАФАР) является то, что второй выход аналого-цифрового преобразователя (АЦП) каждого приемо-передающего модуля (ППМ) через шину данных соединен с восьмым входом программируемой логической интегральной схемы (ПЛИС), десятый выход ПЛИС через шестой выход каждого ППМ и шину данных соединен с третьим входом центрального процессора, при этом центральный процессор для заданного потребителем режима работы ЦАФАР выдает команды установки частоты в первый и второй когерентные СВЧ гетеродины, команды установки периода повторения и длительности зондирующих импульсов в синхронизатор, команды установки начальной фазы и амплитуды сигнала индивидуально для каждого ППМ, общих параметров модуляции сигнала и приемного строба в ПЛИС каждого ППМ. Техническим результатом является снижение объема формируемых в каждом ППМ цифровых данных и пиковой скорости их передачи в центральный процессор. 2 ил.

Цифровая активная фазированная антенная решетка (ЦАФАР), содержащая первый и второй когерентные СВЧ гетеродины, выходы которых через первый и второй входы коммутатора соединены с входом первого делителя мощности, выходы которого соединены с первыми входами N приемо-передающих модулей (ППМ), синхронизатор, второй выход которого соединен с третьим входом коммутатора и с третьими входами всех ППМ, третий выход синхронизатора через второй делитель мощности соединен со вторыми входами всех ППМ, N+1-й выход второго делителя мощности соединен с третьими входами первого и второго когерентных гетеродинов, первый вход каждого ППМ через последовательно соединенные квадратурный балансный смеситель, усилитель мощности, циркулятор и пятый вход-выход ППМ соединен с элементом антенной решетки (АР), номер которого соответствует номеру ППМ, второй выход циркулятора каждого ППМ через последовательно соединенные преселектор, ключ защиты, малошумящий усилитель, смеситель и фильтр промежуточной частоты соединен с первым входом АЦП, второй вход смесителя соединен с первым входом ППМ, второй вход каждого ППМ соединен с первым входом программируемой логической интегральной схемы (ПЛИС) и с первым входом квадратурного генератора прямого цифрового синтеза (КГПС), второй и третий выходы которого соединены со вторым и третьим входами квадратурного балансного смесителя, третий вход каждого ППМ соединен со вторым входом ПЛИС, третий вход-выход которой соединен с четвертым входом-выходом КГПС, четвертый выход ПЛИС соединен со вторым входом усилителя мощности, пятый выход ПЛИС соединен со вторым входом ключа защиты, шестой выход ПЛИС соединен со вторым входом преселектора, седьмой выход ПЛИС соединен с третьим входом АЦП, девятый вход-выход ПЛИС через четвертый вход-выход каждого ППМ и сигнальную шину соединен со вторым входом-выходом центрального процессора, который по этой же шине соединен с первыми входами-выходами синхронизатора, первого и второго когерентных гетеродинов, первый вход-выход центрального процессора обеспечивает связь ЦАФАР с потребителем, отличающаяся тем, что второй выход АЦП каждого ППМ через шину данных соединен с восьмым входом ПЛИС, десятый выход ПЛИС через шестой выход каждого ППМ и шину данных соединен с третьим входом центрального процессора, при этом центральный процессор для заданного потребителем режима работы ЦАФАР выдает команды установки частоты в первый и второй когерентные СВЧ гетеродины, команды установки периода повторения и длительности зондирующих импульсов в синхронизатор, команды установки начальной фазы и амплитуды сигнала индивидуально для каждого ППМ, общих параметров модуляции сигнала и приемного строба в ПЛИС каждого ППМ; центральный процессор по известным алгоритмам выполняет цифровую обработку принятого сигнала; ПЛИС в каждом ППМ обеспечивает настройку полосы пропускания преселектора, установку параметров сигнала в КГПС, на время формирования зондирующего импульса открывает усилитель мощности и запирает ключ защиты приемника, формирует последовательность импульсов дискретизации для управления работой АЦП, принимает от АЦП непрерывную последовательность временных отсчетов принятого сигнала, выполняет их стробирование в соответствии с заданными параметрами приемного строба, по известным алгоритмам формирует из них временные отсчеты квадратурного сигнала, смещает его спектр на нулевую частоту, обрабатывает в цифровом фильтре нижних частот, выполняет децимацию временных отсчетов, затем выполняет их буферизацию, формирует пакеты данных и передает их для обработки в центральный процессор.

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2010 |

|

RU2451373C1 |

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2007 |

|

RU2338307C1 |

| WO 9703367 A1, 30.01.1997 | |||

| Прибор для измерения атмосферного давления | 1959 |

|

SU125397A1 |

| US 5943010 A, 24.08.1999. | |||

Авторы

Даты

2017-04-25—Публикация

2015-10-26—Подача