Область техники, к которой относится изобретение

Настоящее изобретение в целом относится к области электроники. Если более точно, некоторые варианты осуществления изобретения в целом относится к гибридным запоминающим устройствам.

Уровень техники

Постоянные достижения в системной архитектуре, например в многоядерной обработке, а также достижения в ее использовании требуют соответствующих достижений в запоминающих системах. Высокая емкость запоминающего устройства приобретает увеличивающуюся важность вместе с увеличением количества ядер в системе процессора с большим количеством приложений, например, базы данных "в памяти" и виртуализированных серверах, которые требуют значительно более высокой емкости запоминающего устройства. Способность масштабировать существующие запоминающие системы (например, модули памяти с двухсторонним расположением микросхем с удвоенной скоростью обмена (DDR DIMMs) ограничивается вследствие нескольких факторов, включающих в себя стоимость, потребление энергии, плотность и производительность. Типичная платформа запоминающего устройства большой емкости может быть составлена из количества модулей памяти с двухсторонним расположением микросхем (DIMM), достигающего 16 или более. Это создает вызовы в процессе расположения компонентов, охлаждения, а также в маршрутизации сигналов, причем все эти факторы увеличивают стоимость этих систем.

В добавление к емкости энергостойкая память приобретает увеличивающееся значение в определенных приложениях. Типичным примером является база данных "в памяти", в которой время для построения отображения в памяти может иметь существенно большую величину, поскольку размер базы данных увеличивается. Способность поддерживать содержимое памяти на протяжении энергетических циклов может уменьшать время запуска и удалять необходимое условие для чрезмерно активных или находящихся в дежурном режиме серверов.

Соответственно, гибридные запоминающие устройства могут найти применение.

Краткое описание чертежей

Подробное описание обеспечивается ссылками на сопроводительные чертежи. На этих фигурах самые левые цифры номера ссылки идентифицируют фигуру, в которой этот номер ссылки впервые появляется. Использование одинаковых номеров ссылки на различных фигурах обозначает подобные или идентичные элементы.

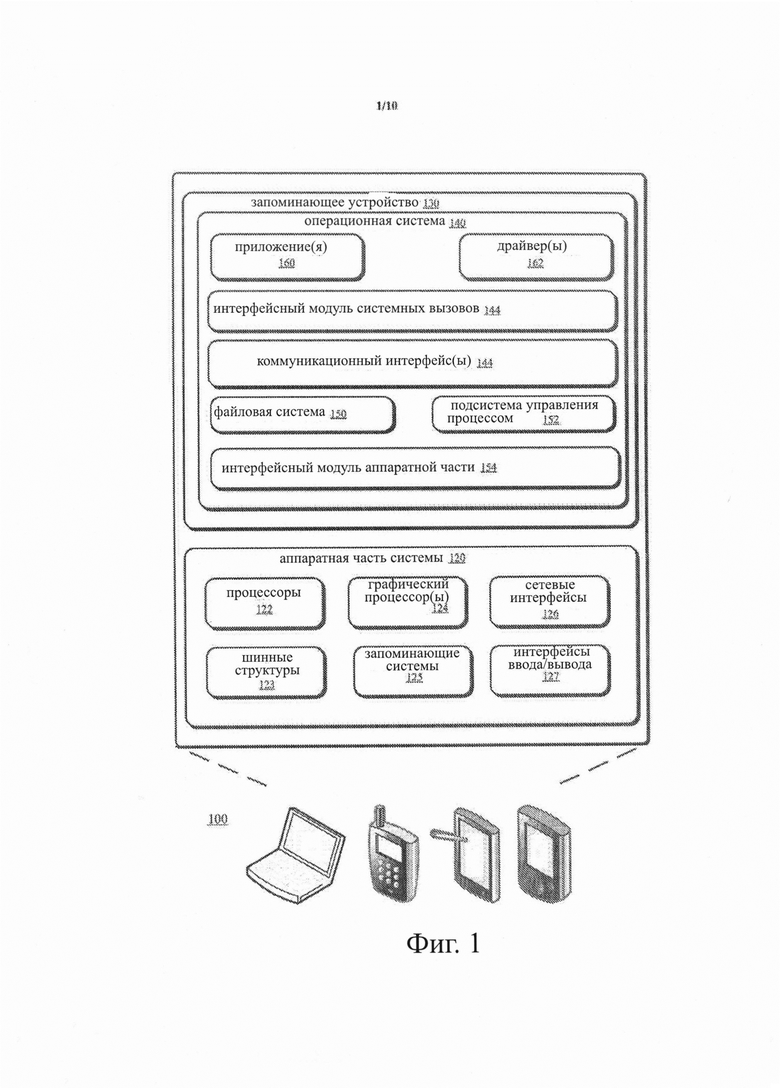

Фиг. 1 является схематической блок-схемой, иллюстрирующей компоненты устройства для применения гибридного запоминающего устройства, в соответствии с различными обсуждаемыми здесь вариантами осуществления изобретения.

Фиг. 2А является схематической блок-схемой иллюстративной архитектуры, в которой может применяться гибридное запоминающее устройство, в соответствии с различными обсуждаемыми здесь вариантами осуществления изобретения.

Фиг. 2В является схематической иллюстрацией энергозависимой памяти, в соответствии с различными обсуждаемыми здесь вариантами осуществления изобретения.

Фиг. 3 является схематической иллюстрацией распределения памяти, в соответствии с различными обсуждаемыми здесь вариантами осуществления изобретения.

Фиг. 4-5 являются картами последовательности процессов, иллюстрирующих операции в способе применения гибридного запоминающего устройства, в соответствии с различными обсуждаемыми здесь вариантами осуществления изобретения.

Фиг. 6-10 являются схематическими блок-схемами, иллюстрирующими электронные устройства, которые могут быть адаптированы для применения гибридного запоминающего устройства, в соответствии с различными обсуждаемыми здесь вариантами осуществления изобретения.

Подробное описание

Некоторые запоминающие системы могут применяться с использованием локального запоминающего устройства с быстрой выборкой, которое часто осуществляется как энергозависимая память и которое может функционировать как сверхоперативная память и одно или более дистанционных запоминающих устройств, которые могут содержать энергонезависимую память, например, магнитное или оптическое запоминающее устройство. Например, дистанционные запоминающие устройства могут содержать один или более модулей памяти с двухрядным расположением выводов (DIMMs), каждый из которых может содержать один или более рангов памяти, которые в свою очередь, могут содержать одну или более микросхем динамического запоминающего устройства с произвольной выборкой (DRAM, динамическое ЗУПВ) или могут включать в себя энергонезависимую память, например, трехмерную перекрестную память, флеш-память, сегнетоэлектрическое запоминающее устройство, запоминающее устройство со структурой кремний-оксид-нитрид-оксид кремний (SONOS), запоминающее устройство на полимере, запоминающее устройство, нанопровод, ферроэлектрическое транзисторное оперативное запоминающее устройство (FeTRAM или FeRAM), нанопроводное или электрически стираемое программируемое постоянное запоминающее устройство (EEPROM). Некоторые электронные устройства (например, смартфоны, планшетные компьютеры, и подобные устройства) могут содержать более простые дистанционные запоминающие системы, состоящие из одного или более динамических запоминающих устройств с произвольной выборкой (DRAMs).

Описываемые здесь устройства являются гибридными запоминающими устройствами, которые содержат энергозависимую память (например, DRAM) и энергонезависимую память. Устройства дополнительно содержат контроллер, содержащий буфер памяти и логику для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения. Электронное устройство, включающее в себя запоминающее устройство, может содержать процессор для работы операционной системы и одно или более приложений, а также драйвер устройства операционной системы для управления операций доступа к памяти между по меньшей мере одним приложением и запоминающим устройством.

Обсуждаемые здесь технологии могут обеспечиваться в различных вычислительных системах (например, включающих в себя серверы, настольные компьютеры, блокнотные компьютеры, смартфоны, планшеты, портативные игровые приставки, и т.д.), которые могут включать в себя запоминающую систему, содержащую множество микросхем динамического запоминающего устройства с произвольной выборкой (DRAM, динамическое ЗУПВ), в большинстве случаев собранных в модуль памяти с двухрядным расположением выводов (DIMM) и энергонезависимую память. В таких вариантах осуществления изобретения один или более DIMMs могут содержать отдельную управляющую логику.

В последующем описании формулируются многочисленные специфические подробности, чтобы обеспечивать исчерпывающее понимание различных вариантов осуществления изобретения. Однако различные варианты осуществления изобретения могут применяться на практике и без специфических подробностей. В других примерах хорошо известные способы, процедуры, компоненты и схемы не будут описываться подробно, для того чтобы не осложнять понимание отдельных вариантов осуществления изобретения. Кроме того, различные аспекты вариантов осуществления изобретения могут выполняться с использованием различных средств, таких как интегрированные полупроводниковые цепи (аппаратная часть), считываемые компьютером инструкции, систематизированные в одну или более программ (программное обеспечение), или некоторая комбинация аппаратной части и программного обеспечения. С целью раскрытия этого изобретения ссылка на «логику» будет означать или аппаратную часть, или программное обеспечение, или некоторую их комбинацию.

Фиг. 1 является схематической иллюстрацией показательного электронного устройства 100, которое может быть адаптировано для включения в свой состав гибридного запоминающего устройства, как здесь описывается, в соответствии с некоторыми вариантами осуществления изобретения. В различных вариантах осуществления изобретения электронное устройство 100 может быть реализовано как персональный компьютер, портативный компьютер, персональный электронный секретарь, мобильный телефон, устройство для развлечения, планшетный компьютер, электронное устройство для чтения, или другое вычислительное устройство.

Электронное устройство 100 включает в себя системную аппаратную часть 120 и запоминающее устройство 130, которые могут применяться как оперативное запоминающее устройство и/или постоянное запоминающее устройство. Источник энергии, такой как батарея 180, может присоединяться к электронному устройству 100.

Системная аппаратная часть 120 может включать в себя один или более процессоров 122, шинные структуры 123, один или более графических процессоров 124, запоминающие системы 125, сетевые интерфейсы 126, и интерфейсы 127 ввода/вывода. В одном варианте осуществления изобретения процессор 122 может быть реализован как процессор Intel® Core2 Duo®, доступный от корпорации Intel Corporation, Санта Клара, Калифорния, США. В данном контексте термин «процессор» означает любой тип вычислительного элемента, например такого, но не ограничиваясь этим, как микропроцессор, микроконтроллер, микропроцессор со сложным набором команд типа CISC (Complex Instruction Set Computer), микропроцессор с сокращенным набором команд типа RISC (reduced instruction set computer), микропроцессор командными словами сверхбольшой длины типа VLIW (Very Long Instruction Word), или любой другой тип процессора или обрабатывающей схемы.

Шинные структуры 123 соединяют различные компоненты системной аппаратной части 120. В одном варианте осуществления изобретения шинные структуры 128 могут быть одной или более шинной структуры (структур) нескольких типов, включающих в себя шину запоминающего устройства, периферийную шину или внешнюю шину, и/или локальную шину, использующую любое многообразие доступных шинных архитектур, включая в себя, но не ограничиваясь этим, 11-битную шину, архитектуру шины промышленного стандарта (ISA, Industry Standard Architecture), микроканальную архитектуру шины (MSA, Micro-Channel Architecture), расширенную архитектуру шины промышленного стандарта (EISA, Extended Industry Standard Architecture), интеллектуальную дисковую электронику (IDE, Intelligent Drive Electronics), локальную шину VESA (VLB), межсоединение периферийных компонентов (PCI, Peripheral Component Interconnect), универсальную последовательную шину (USB, Universal Serial Bus), расширенный графический порт (AGP, Advanced Graphics Port), шину Международной ассоциации производителей карт памяти для персональных компьютеров (PCMCIA, Personal Computer Memory Card International Association), и интерфейс малых компьютерных систем (SCSI, small computer system interface).

Графический процессор(ы) 124 может функционировать как вспомогательный процессор, который управляет графическими и/или видео операциями. Графический процессор(ы) 124 может быть интегрирован на материнской плате электронного устройства 100 или может быть присоединен через гнездо для платы расширения к материнской плате.

Запоминающие системы 125 могут содержать локальную память, например, сверхбыстродействующую энергозависимую оперативную память, одну или более форм энергозависимой памяти и энергонезависимой памяти, как описывалось выше.

В одном варианте осуществления изобретения сетевой интерфейс(ы) 126 может быть проводным интерфейсом, таким как интерфейс Ethernet (см. например, Институт инженеров по электротехнике и радиоэлектронике/ИИЭР, Institute of Electrical and Electronics Engineers/IEEE 802.3-2002) или беспроводным интерфейсом, таким как IEEE 802.11а, b, g - совместимый интерфейс (см. например, Стандарт IEEE для IT-телекоммуникаций и обмен информацией между системами локальная сеть/ региональная вычислительная сеть (LAN/MAN) - Часть II: управление доступом к среде передачи данных (MAC) беспроводной локальной сети и протокол физического уровня (PHY, Physical layer protocol) исправление 4 описаний: дальнейшее расширение более высокой скорости передачи данных в полосе частот 2.4 ГГц, 802.11G-2003). В качестве другого примера беспроводного интерфейса можно привести интерфейс пакетной радиосвязи общего назначения (протокол GPRS) (см. например, Директивы по GPRS, требования для мобильных телефонов, Глобальная система для мобильных коммуникаций/ассоциация GSM, Global System for Mobile Communications, Версия 3.0.1, декабрь 2002).

Интерфейсы 127 ввода/вывода могут применяться на одном или более устройств ввода/вывода, например таких как дисплей, сенсорный экран, один или более громкоговорителей, клавиатура, манипулятор для управления курсором (мышь), сенсорная панель или подобные устройства.

Запоминающее устройство 130 может сохранять в памяти операционную систему 140 для управления операциями электронного устройства 100. В одном варианте осуществления изобретения операционная система 140 включает в себя интерфейсный модуль 154 аппаратной части, например, одной или более операционных системных драйверов устройства, которые обеспечивают интерфейс для системной аппаратной части 120. Кроме того, операционная система 140 может включать в себя файловую систему 150, которая управляет файлами, используемыми при работе электронного устройства 100 и подсистему 152 управления процессом, которая управляет процессами, выполняемыми на электронном устройстве 100.

Операционная система 140 может включать в себя (или управлять) одним или более коммуникационными интерфейсами, которые могут работать во взаимосвязи с системной аппаратной частью 120, чтобы принимать и передавать пакеты данных и/или потоки данных из удаленного источника. Операционная система 140 может дополнительно включать в себя модуль 142 интерфейса системных вызовов, который обеспечивает интерфейс между операционной системой 140 и одним или более резидентных модулей приложения в запоминающем устройстве 130. Операционная система 140 может быть реализована как операционная система Unix или любая из ее производных (например, Linux, Solaris, и т.д.) или как операционная система товарного знака Windows®, или другие операционные системы.

В некоторых вариантах осуществления изобретения запоминающее устройство 130 может сохранять в памяти одно или более приложений 160, которые могут выполняться на одном или более процессорах 122 под контролем операционной системы 140 и одном или более драйверах 162 запоминающего устройства. Приложения 160 и драйвер 162 могут быть реализованы как логические инструкции, сохраняемые в материальном считываемом компьютером энергонезависимом носителе (т.е. программное обеспечение или программно-аппаратные средства), которые могут быть выполнены на одном или более процессорах 122. Альтернативно, эти приложения могут быть реализованы как логические на программируемом устройстве, таком как матрица логических элементов с эксплуатационным программированием (FPGA, Field Programmable Gate Array), или подобное устройство. Альтернативно, эти приложения могут быть уменьшены до логики, которая может быть жестко закодированной в интегральной микросхеме.

Фиг. 2А является схематической блок-схемой иллюстративной архитектуры, в которой может применяться гибридное запоминающее устройство, в соответствии с различными обсуждаемыми здесь вариантами осуществления изобретения. Как показано на фиг. 2А, в некоторых вариантах осуществления изобретения блок 200 центрального процессора (ЦП, CPU), который может содержать один или более центральных процессоров 210, присоединяется к управляющему концентратору 220 и локальному запоминающему устройству 230. Управляющий концентратор 220 содержит контроллер 222 памяти и интерфейс 224 памяти.

Интерфейс 224 памяти присоединяется к одному или более дистанционных запоминающих устройств 240 через коммуникационную шину 235. В одном примере коммуникационная шина 235 может быть шиной памяти с удвоенной скоростью передачи данных.

Запоминающее устройство 240 может содержать контроллер 242 и энергонезависимую память 250, энергозависимую память 260 и источник 280 энергии*. Контроллер 242 содержит один или более управляющих регистров 244 и буферы 246 памяти, а также интерфейс ввода/вывода, такой как мультиплексор 248.

В различных вариантах осуществления изобретения энергонезависимая память 250 может применяться с использованием, например, памяти на фазовых переходах, памяти NAND-типа (флеш), ферроэлектрического транзисторного оперативного запоминающего устройства (FeTRAM), энергонезависимой памяти на основе нанопровода, памяти, которая включает в себя технологию мемристора, статического запоминающего устройства с произвольной выборкой (СЗУПВ, SRAM), трехмерной (3D) перекрестной памяти*, такой как память на фазовых переходах (РСМ), память на основе переноса спинового момента (STT-RAM) или память NAND.

В различных вариантах осуществления изобретения энергозависимая память 260 может применяться с использованием одного или более модулей динамического запоминающего устройства с произвольной выборкой (динамическое ЗУПВ, DRAM). Например, как показано на фиг. 2В, в некоторых вариантах осуществления изобретения энергозависимая память 260 может содержать один или более модулей 270 памяти с двухсторонним расположением микросхем (DIMMs), присоединенных к каналу 272 с памятью, который обеспечивает линию связи с контроллером 122 памяти. В варианте осуществления изобретения, изображенном на фиг. 2В, каждый из модулей 270 DIMM содержит первый ранг 274 и второй ранг 276, каждый из которых включает в себя множество модулей 278 динамического запоминающего устройства с произвольной выборкой (DRAM). Специалист в данной области техники будет отдавать себе отчет, что энергозависимая память 260 может содержать большее или меньшее количество DIMMs 270, и большее или меньшее количество рангов на один DIMM. Кроме того, некоторые электронные устройства (например, смартфоны, планшетные компьютеры, и подобные устройства) могут содержать более простые запоминающие системы, состоящие из одного или более динамических запоминающих устройств с произвольной выборкой (DRAMs).

Как показано на фиг. 3, в некоторых вариантах осуществления изобретения энергонезависимая память 250 больше, чем энергозависимая память 260. Это вводит поправку на адресующую схему, в которой системная физическое запоминающее устройство, открытое для операционной системы 140, ограничивается размером энергозависимой памяти 260. Энергонезависимая память 250 включает в себя область для архивирования, которая обеспечивает резервное энергонезависимое запоминающее устройство для энергозависимой памяти 260. Остальная часть адресного пространства энергонезависимой памяти доступно в качестве пространства для страничных файлов*, управляемых драйвером 162 запоминающего устройства. Таким образом, общее виртуальное адресное пространство, доступное для приложения (приложений) 160, может быть общим адресным пространством физического энергонезависимого запоминающего устройства.

Как правило, операционная система ограничивает разбиение памяти на страницы из энергонезависимого запоминающего устройства, например, накопителя на жестких дисках или полупроводникового накопителя, до виртуальной памяти за счет гарантирования того, что распределяемая виртуальная память имеет достаточную систему резервирования физического запоминающего устройства. Разбиение памяти на страницы обычно ограничивается до возобновления процесса после периода неактивности. В запоминающем устройстве 240 копирование из энергонезависимой памяти 250 в энергозависимую память имеет место на том же самом запоминающем устройстве, например DIMM, и может производиться очень быстро. Кроме того, приложению 160 может быть позволен доступ к данным, в то время как происходит копирование из энергонезависимой памяти в энергозависимую память. Это позволяет приложению 160 и драйверу 162 обрабатывать ошибки страницы памяти синхронным способом.

Кроме того, поскольку все перемещения данных между энергонезависимой памятью 250 и энергозависимой памятью 260 сохраняются на запоминающем устройстве 240, коммуникационный канал 235 используется только для действительного доступа процессора к данным. Этот ограниченный профиль перемещения данных может значительно уменьшить расход энергии, требуемой для осуществления разбиения виртуальной памяти на страницы.

Эти факторы учитывают более динамичное разбиения памяти на страницы между энергонезависимой памятью 250 в энергозависимой памятью 260, таким образом обеспечивая намного большее виртуальное адресное пространство для использования приложения 160. Доступы к памяти приложений направлены на энергозависимую память и следовательно, получают высокую производительность работы памяти.

Как описывалось выше, в некоторых вариантах осуществления изобретения контроллер 242 в запоминающем устройстве (устройствах) 240 взаимодействует с драйвером 162 в электронном устройстве 100, чтобы производить операции управления памятью в запоминающем устройстве 240. Операции, применяемые контроллером 242 и/или драйвером 162 будут описываться со ссылками на фиг. 4-5. Фиг. 4 иллюстрирует операции, применяемые для управления копированием одной или более страниц из энергонезависимой памяти 250 в энергозависимую память 260 (т.е. операции подкачки страниц в оперативную память), в то время как фиг. 5 иллюстрирует операции, применяемые для управления копированием одной или более страниц из энергозависимой памяти в энергонезависимую память 260 (т.е. операции откачки страниц из оперативной памяти).

Обратимся сначала к фиг. 4, во время операции 410 приложение 160 считывает страницу, которая вызывает страничную ошибку, это приводит к тому, что страничная ошибка высылается в операционную систему 140. Во время операции 415 операционная система 140 принимает запрос на страничную ошибку от приложения 160 и в ответ на запрос на страничную ошибку, запрашивает (операция 420) драйвер 162 на передачу страницы данных, запрашиваемую приложением 160, из энергонезависимой памяти 250 в энергозависимую память 260 (т.е. запрос на операцию подкачки страниц в оперативную память). Во время операции 425 драйвер принимает запрос на операцию перемещения страницы, а во время операции 430 драйвер 162 программирует контроллер 242 на перемещение страницы из энергонезависимой памяти 250 в буфер 246 памяти. Запрос на данные пересылается к контроллеру 242 в запоминающее устройство(а) 240 через шину 235. Во время операции 435 драйвер 162 аннулирует строки данных сверхоперативной памяти для страницы в центральных процессорах 210.

Во время операции 440 контроллер 242 принимает запрос на операцию подкачки страниц в оперативную память, а во время операции 445 контроллер 242 копирует запрашиваемую страницу данных из энергонезависимой памяти 250 в буферы 246 памяти в контроллере 242. Во время операции 450 контроллер 242 устанавливает сигнал статуса выполнения, который возвращается к драйверу 162. Во время операции 455 драйвер 162 считывает сигнал статуса, который проходит к операционной системе 140.

Во время операции 460 операционная система 140 принимает сигнал о выполнении от драйвера 162, а во время операции 465 операционная система 140 перемещает страницу к приложению 160d. Во время операции 470 приложение ожидает, когда операционная система 140 будет обрабатывать страничную ошибку. Когда страница перемещается к приложению, управление передается к операции 470 и приложение 160 считывает страницу данных из буферов 240 памяти (операция 475). Во время операции 480 контроллер 242 принимает запрос на считывание, и в ответ на запрос на считывание во время операции 485 контроллер 242 поставляет страницу из буферов 246 в энергозависимую память 260 и освобождает буфер. Когда приложение считывает данные, контроллер 242 записывает (операция 455) данные страницы в энергозависимую память 260 и аннулирует буфер на основе строка данных за строкой данных сверхоперативной памяти. Таким образом, операция подкачки страниц в оперативную память гарантирует, что не будет никакого адресного конфликта для энергонезависимой памяти 260. В последующих операциях страничной ошибки, если драйвер 162 не находит свободной памяти в буфере 246, то драйвер 162 может сбрасывать буферы в энергозависимую память 260, например за счет выполнения фиктивных записей через шину 260 в единственную линию памяти*. Это гарантирует, что не будет никакого конфликта в доступе к энергонезависимой памяти между ЦП 210 и передачей содержимого буфера. Во время операции 490 приложение 160 использует новые данные.

Как показано на фиг. 5, во время операции откачки страниц из оперативной памяти приложение или операционная система 140 нуждается (операция 510) в том, чтобы освободить страницу из энергозависимой памяти 150 для использования приложением 160. Во время операции 515 операционная система 140 запрашивает драйвер 162 для перемещения страницы данных из энергозависимой памяти 260 к энергонезависимой памяти 250. Во время операции 520 драйвер 162 принимает запрос и выполняет проверку (операция 525), чтобы гарантировать, что буфер 246 памяти доступен для операции считывания. Во время операции 530 драйвер 162 программирует контроллер 242 для копирования страницы из энергозависимой памяти 260 к энергонезависимой памяти 250 через буферы 246 памяти.

Во время операции 535 драйвер 162 выполняет последовательности считывающих операций в фиктивное ("dummy") местоположение в буфер 246 памяти контроллера 242. Например, драйвер может выполнять 64 операции считывания строки данных сверхоперативной памяти для 4KB страницы. Фиктивные считывающие операции сохраняют ЦП 210 занятым считыванием фиктивных ("dummy") местоположений, в то время как контроллер копирует страницу из энергозависимой памяти 260 в энергонезависимую память 250. Это позволяет избежать потенциального конфликта между считыванием страницы из энергозависимой памяти 260 в буфер 246 памяти и ЦП 210, который пытается считывать энергозависимую память 260 для другого приложения.

Во время операции 540 контроллер 242 принимает запрос на операцию откачки страницы из оперативной памяти. Во время операции 545 контроллер 242 обеспечивает фиктивные данные для драйвера 162, а во время операции 550 контроллер 242 копирует данные страницы из энергозависимой памяти 260 в буфер 246 как операцию в фоновом режиме. Операция фиктивного считывания сохраняет буферы 246 занятыми до тех пор пока страница не скопируется. В некоторых вариантах осуществления изобретения контроллер 242 применяет считывающую операцию из энергозависимой памяти 260 для каждой операции фиктивного считывания, выполненной во время операции 530, которая позволяет избежать конфликтов при доступе к энергозависимой памяти 260.

Во время операции 555 драйвер 162 аннулирует страницу из сверхоперативной памяти в центральном процессоре (процессорах) 210, а во время операции 560 драйвер 162 передает страницу из энергозависимой памяти 260 в операционную систему. Во время операции 565 операционная система 140 принимает сигнал из драйвера 162 о том, что страница данных освобождается из энергозависимой памяти.

Как описывалось выше, в некоторых вариантах осуществления изобретения электронное устройство может быть реализовано как компьютерная система. Фиг. 6 иллюстрирует блок-схему компьютерной системы 600, в соответствии с вариантом осуществления изобретения. Компьютерная система 600 может включать в себя один или более центральных процессоров (ЦП) 602 или процессоров, которые соединяются между собой через сеть межкомпонентного соединения (или шину) 604. Процессоры 602 могут включать в себя процессор общего назначения, сетевой процессор (который обрабатывает данные, передаваемые через компьютерную сеть 603), или другие типы процессоров (включая в себя процессор с сокращенным набором команд (RISC processor) или процессор со сложным набором команд (CISC)). Кроме того, процессоры 602 могут иметь конструкцию с одноядерной или многоядерной архитектурой. Процессоры 602 с многоядерной архитектурой могут объединять различные типы ядер процессора на том же самом кристалле интегральной схемы (IC, ИС). Кроме того, процессоры 602 с многоядерной архитектурой могут использоваться как симметричные или асимметричные многопроцессорные системы. В варианте осуществления изобретения один или более процессоров 602 могут быть одинаковыми или подобными процессорам 102, показанным на фиг. 1. Например, один или более процессоров 602 могут включать в себя управляющий блок 120, обсуждавшийся ранее со ссылками на фиг. 1-3. Кроме того, операции, обсуждавшиеся ранее со ссылками на фиг. 3-5, могут выполняться с помощью одного или более компонентов системы 600.

Микропроцессорный набор 606 также может иметь связь с сетью 604 межкомпонентного соединения. Микропроцессорный набор 606 может включать в себя контроллер-концентратор памяти (МСН) 608. МСН 608 может включать в себя контроллер 610 памяти, который осуществляет связь с запоминающим устройством 612 (которое может быть таким же или аналогичным запоминающему устройству 130 на фиг. 1). Запоминающее устройство 412 может сохранять данные, включающие в себя последовательности инструкций, которые могут выполняться центральным процессором (ЦП) 602, или любым другим устройством, включенным в состав вычислительной системы 600. В одном варианте осуществления изобретения запоминающее устройство 612 может включать в себя одно или более энергозависимых запоминающих устройств (или памяти), таких как запоминающее устройство с произвольной выборкой (RAM, ЗУПВ), динамическое запоминающее устройство с произвольной выборкой (DRAM, динамическое ЗУПВ), синхронное динамическое ЗУПВ (SDRAM), статическое запоминающее устройство с произвольной выборкой (СЗУПВ, SRAM), или другие типы запоминающих устройств. Энергонезависимая память также может использоваться, например такая как жесткий диск. Дополнительные устройства могут связываться через сеть 604 межкомпонентного соединения, например такие устройства как множество ЦП и/или множество системных запоминающих устройств.

Контроллер-концентратор памяти (МСН) 608 также может включать в себя графический интерфейс 614, который осуществляет связь с устройством 616 отображения. В одном варианте осуществления изобретения графический интерфейс 614 может осуществлять связь с устройством 616 отображения через ускоренный графический порт (AGP). В варианте осуществления изобретения устройство 616 отображения (например такое как плоская индикаторная панель) может осуществлять связь с графическим интерфейсом 614 через, например, преобразователь сигнала, который преобразовывает цифровое представление изображения, сохраняемое в запоминающем устройстве, таком как видеопамять или системная память, в сигналы отображения, которые интерпретируются и отображаются дисплеем 616. Сигналы отображения, производимые устройством отображения, могут проходить через различные управляющие устройства, перед тем как они интерпретируются и впоследствии отображаются на дисплее 616.

Интерфейс 618 концентратора может позволить контроллеру-концентратору 608 памяти (МСН) и контроллеру-концентратору 620 ввода-вывода (ICH) осуществлять связь. Контроллер-концентратор 620 ввода-вывода может обеспечивать интерфейс для устройства (устройств) ввода-вывода, которые осуществляют связь с вычислительной системой 600. ICH 620 может осуществлять связь с шиной 622 через периферийный мост (или контроллер) 624, такой как мост межсоединения периферийных компонентов (PCI), контроллер универсальной последовательной шины (USB), или другие типы периферийных мостов или контроллеров. Мост 624 может обеспечивать тракт данных между центральным процессором (ЦП) 602 и периферийными устройствами. Могут быть использованы и другие типы топологий. Кроме того, множество шин могут связываться с ICH 620, например, через множество мостов или контроллеров. Кроме того, другие периферийные компоненты, находящиеся в соединении с ICH 620, могут включать в себя в различных вариантах осуществления изобретения накопитель (накопители) на жестких дисках со встроенным интерфейсом накопителей (IDE) или интерфейсом малых компьютерных систем (SCSI), порт(ы) универсальной последовательной шины (USB), клавиатуру, манипулятор мышь, параллельный порт(ы), последовательный порт(ы), накопитель (накопители) на гибких дисках, поддержку цифрового вывода (например, цифровой видеоинтерфейс (DVI)), или другие устройства.

Шина 622 может осуществлять связь со звуковым устройством 626, одним или более дисковым накопителем(ями) 628 и устройством 630 сетевого интерфейса (которое имеет связь с компьютерной сетью 603). Другие устройства могут осуществлять связь через шину 622. Кроме того, различные компоненты (такие как устройство 630 сетевого интерфейса) могут осуществлять связь с контроллером-концентратором 608 памяти (МСН) в некоторых вариантах осуществления изобретения. Кроме того, процессор 602 и один или более других обсуждаемых здесь компонентов, могут комбинироваться, чтобы формировать единую микросхему (например, чтобы обеспечивать систему на кристалле (SOC, system-on-a-chip)). Кроме того, графический ускоритель 616 может быть включен в состав контроллера-концентратора 608 памяти (МСН) в других вариантах осуществления изобретения.

Кроме того, вычислительная система 600 может включать в себя энергозависимую и/или энергонезависимую память (или запоминающее устройство). Например, энергонезависимая память может включать в себя одно или более из следующих устройств: постоянное запоминающее устройство (ROM, ПЗУ), программируемое постоянное запоминающее устройство (PROM, ППЗУ), стираемое программируемое постоянное запоминающее устройство (EPROM, СППЗУ), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM, ЭСППЗУ),дисковый накопитель (например, 628), гибкий диск, компакт-диск, предназначенный только для чтения (CD-ROM), цифровой видеодиск (DVD), флеш-память, магнитно-оптический диск, или другие типы энергонезависимой считываемой машиной среды, которая способна сохранять электронные данные (например, включающие в себя инструкции).

Фиг. 7 иллюстрирует блок-схему вычислительной системы 700, в соответствии с вариантом осуществления изобретения. Система 700 может включать в себя один или более процессоров от 702-l до 702-N (в целом определяемые здесь как «процессоры 702» или «процессор 702»). Процессоры 702 могут осуществлять связь через сеть с внутрисхемной коммутацией или через шину 704. Каждый процессор может включать в себя различные компоненты, некоторые из которых обсуждаются только со ссылкой на процессор 702-1 для ясности. Соответственно, каждый из остающихся процессоров от 702-2 до 702-N, может включать в себя те же самые или аналогичные компоненты, которые обсуждаются со ссылкой на процессор 702-1.

В варианте осуществления изобретения процессор 702-1 может включать в себя одно или более ядер от 706-1 до 706-М процессора (определяемых здесь как «ядра 706» или в более общем варианте «ядро 706»), совместно используемую сверхоперативную память 708, маршрутизатор 710, и/или управляющую логику процессора или модуль 720. Ядра 706 процессора могут быть использованы на единственном кристалле интегральной схемы (IC, ИС). Кроме того, интегральная схема может включать в себя одну или более совместно используемых и/или собственных блоков сверхоперативной памяти (таких как сверхоперативная память 708), шины или межкомпонентные соединения (такие как шина или сеть 712 с внутрисхемной коммутацией), контроллеры памяти, или другие компоненты.

В одном варианте осуществления изобретения маршрутизатор 710 может использоваться для связи между различными компонентами процессора 702-1 и/или системы 700. Кроме того, процессор 702-1 может включать в себя более чем один маршрутизатор 710. Кроме того, множество маршрутизаторов 710 могут иметь связь между собой, чтобы позволить маршрутизацию данных между различными компонентами внутри или снаружи процессора 702-1.

Совместно используемая сверхоперативная память 708 может сохранять данные (например, включающие в себя инструкции), которые используются одним или более компонентами процессора 702-1, такими как ядра 706. Например, совместно используемая сверхоперативная память 708 может локально помещать в сверхоперативную память данные, сохраняемые в запоминающем устройстве 714 для более быстрого доступа компонентами процессора 702. В варианте осуществления изобретения сверхоперативная память 708 может включать в себя сверхоперативную память регионального уровня (например такого как уровень 2 (L2), уровень 3 (L3), уровень 4 (L4), или другие уровни сверхоперативной памяти), сверхоперативная память последнего уровня (LLC), и/или их комбинации. Кроме того, различные компоненты процессора 702-1 могут иметь связь с совместно используемой сверхоперативной памятью 708 напрямую через шину (например, шину 712), и/или контроллер памяти или концентратор. Как показано на фиг. 7, в некоторых вариантах осуществления изобретения одно или более ядер 706 могут включать в себя уровень 1 (L1) сверхоперативной памяти 716-1 (в целом определяемого здесь как «L1 сверхоперативная память 716»). В одном варианте осуществления изобретения управляющий модуль 720 может включать в себя логику, чтобы применять ее в операциях, описываемых выше со ссылками на контроллер 122 памяти на фиг. 2.

Фиг. 8 иллюстрирует блок-схему частей ядра 706 процессора и других компонентов вычислительной системы, в соответствии с вариантом осуществления изобретения. В одном варианте осуществления изобретения стрелки, показанные на фиг. 8, иллюстрируют направление потока инструкций через ядро 706. Одно или более ядер процессора (таких как ядро 706 процессора) могут применяться на единственном кристалле интегральной схемы (или кристалле "die" микросхемы), например таком, который обсуждался со ссылками на фиг. 7. Кроме того, микросхема может включать в себя одну или более совместно используемых и/или собственных блоков сверхоперативной памяти (например, сверхоперативная память 708 на фиг. 7), межкомпонентные соединения 704 и/или 112 на фиг. 7), блоки управления, контроллеры памяти, или другие компоненты.

Как иллюстрируется на фиг. 8, ядро 706 процессора может включать в себя модуль 802 для выборки, чтобы выбирать инструкции (включая в себя инструкции с условными переходами) для выполнения их с помощью ядра 706. Инструкции могут быть выбираться из любых запоминающих устройств, таких как запоминающее устройство 714. Ядро 706 процессора также может включать в себя модуль 804 для декодирования, чтобы декодировать выбранные инструкции. Например, модуль 804 для декодирования может декодировать выбранные инструкции во множество микрокоманд (микроопераций).

Кроме того, ядро 706 процессора может включать в себя модуль 806 планирования. Этот модуль 806 планирования может выполнять различные операции, связанные с хранящимися декодированными инструкциями (например, принятых от модуля 804 для декодирования), до тех пор, пока инструкции не будут готовы для отправки, например до тех пор, пока все значения источника декодированной инструкции не станут доступными. В одном варианте осуществления изобретения модуль 806 планирования может планировать и/или выпускать (или отправлять) декодированные инструкции к исполнительному модулю 808 для выполнения. Исполнительный модуль 808 может выполнять отправленные инструкции после того, как они декодируются (например, модулем 804 для декодирования) и высылаются (например, модулем 806 для планирования). В варианте осуществления изобретения исполнительный модуль 808 может включать в себя более чем один исполнительный модуль. Исполнительный модуль 808 может также выполнять различные арифметические операции, такие как сложение, вычитание, умножение, и/или деление, и может включать в себя один или более арифметических логических модулей (ALU, АЛУ). В варианте осуществления изобретения сопроцессор (не показан) может выполнять различные арифметические операции во взаимодействии с исполнительным модулем 808.

Кроме того, исполнительный модуль 808 может выполнять инструкции с изменением их очередности. Следовательно, ядро 706 процессора может быть в одном варианте осуществления изобретения ядром процессора с измененным порядком очередности. Ядро 706 процессора также может включать в себя модуль 810 изъятия. Модуль 810 изъятия может изымать выполненные инструкции после их передачи. В варианте осуществления изобретения изъятие выполненных инструкций может вызывать состояние процессора, в которое он помещается после выполнения инструкций, физические регистры, используемые инструкциями, перестают быть локализованными и т.д.

Ядро 706 процессора также может включать в себя модуль 714 шины, чтобы позволять компонентам ядра 706 процессора и другим компонентам (например таким компонентам, которые обсуждались со ссылками на фиг. 8) связываться между собой через одну или более шин (например, шины 804 и/или 812). Ядро 706 процессора также может включать в себя один или более регистров 816 для сохранения данных, доступных различным компонентам ядра 706 процессора (например таких как значения, относящиеся к установкам состояния потребления энергии).

Кроме того, даже несмотря на то, что фиг. 7 иллюстрирует управляющий блок 720 присоединенным к ядру 706 процессора через межкомпонентное соединение 812, в различных вариантах осуществления изобретения управляющий блок 720 может располагаться где-то в другом месте, например внутри ядра 706 процессора и присоединяться к ядру через шину 704, и т.д.

В некоторых вариантах осуществления изобретения один или более компонентов, обсуждаемых здесь, может быть реализован как устройство с однокристальной системой (SOC). Фиг. 9 иллюстрирует блок-схему пакета SOC, в соответствии с вариантом осуществления изобретения. Как иллюстрируется на фиг. 9, SOC 902 включает в себя одно или более ядер 920 центрального процессора (ЦП, CPU), одно или более ядер 930 графического процессора, интерфейс 940 ввода-вывода (I/O), и контроллер 942 памяти. Различные компоненты пакета 902 SOC могут присоединяться к межкомпонентному соединению или шине таким образом, как здесь обсуждалось со ссылками на другие фигуры. Кроме того, пакет 902 SOC может включать в себя большее или меньшее количество компонентов, как здесь обсуждалось со ссылками на другие фигуры. Кроме того, каждый компонент пакета 902 SOC может включать в себя один или более других компонентов, например, как здесь обсуждалось со ссылками на другие фигуры. В одном варианте осуществления изобретения пакет 902 SOC (и его компоненты) обеспечиваются на одном или более кристаллов интегральной схемы (IC, ИС), например, эти компоненты упаковываются в единое полупроводниковое устройство.

Как иллюстрируется на фиг. 9, пакет 902 SOC присоединяется к запоминающему устройству 960 (которое может быть аналогичным или таким же, как запоминающее устройство, обсуждавшееся здесь со ссылкой на другие фигуры) через контроллер 942 памяти. В варианте осуществления изобретения запоминающее устройство 960 (или его часть) может быть интегрировано в пакет 902 SOC.

Интерфейс 940 ввода-вывода (I/O) может быть присоединен к одному или более устройств 970 ввода-вывода, например, через межкомпонентное соединение и/или шину, например такую, которая обсуждалась здесь со ссылкой на другие фигуры. Устройство(а) 970 ввода-вывода может включать в себя одно или более устройств: клавиатура, манипулятор для управления курсором (мышь), сенсорная панель, дисплей, устройство для записи изображения/видео (такое как камера или записывающая видеокамера/видеомагнитофон), сенсорный экран, громкоговоритель, или подобные устройства.

Фиг. 10 иллюстрирует вычислительную систему 1000, которая располагается в конфигурации с двухточечным соединением (point-to-point, PtP), в соответствии с вариантом осуществления изобретения. В частности, фиг. 10 показывает систему, в которой процессоры, запоминающее устройство, и устройства ввода-вывода являются взаимосвязанными определенным количеством интерфейсов с коммуникацией между двумя узлами.

Как иллюстрируется на фиг. 10, система 1000 может включать в себя несколько процессоров, из которых на фиг. для ясности показаны только два процессора 1002 и 1004. Каждый из процессоров 1002 и 1004 может включать в себя локальный контроллер-концентратор памяти (МСН) 1006 и 1008, чтобы позволить осуществлять связь с запоминающими устройствами 1010 и 1012. МСН 1006 и 1008 могут включать в себя контроллер 120 памяти и/или логический узел 125, показанный на фиг. 1, в некоторых вариантах осуществления изобретения.

В варианте осуществления изобретения процессоры 1002 и 1004 могут быть одним из процессоров 702, которые обсуждались со ссылкой на фиг. 7. Процессоры 1002 и 1004 могут обмениваться данными через интерфейс 1014 с коммуникацией между двумя узлами (PtP), используя, соответственно, цепи 1016 и 1018 интерфейса PtP. Кроме того, каждый из процессоров 1002 и 1004 может обмениваться данными с микропроцессорным набором 1020 через отдельные интерфейсы PtP 1022 и 1024 с использованием цепей 1026, 1028, 1030 и 1032 интерфейса с коммуникацией между двумя узлами (PtP). Микропроцессорный набор 1020 может дополнительно обмениваться данными с цепью 1034 графики с высоким разрешением через интерфейс 1036 графики с высоким разрешением, например, с использованием цепи 1037 интерфейса PtP.

Как показано на фиг. 10, одно или более ядер 106 и/или сверхоперативная память 108, показанные на фиг. 1, могут располагаться внутри процессоров 1004. Однако другие варианты осуществления изобретения могут существовать в других цепях, логических узлах, или устройств внутри системы 1000, показанной на фиг. 10. Кроме того, другие варианты осуществления изобретения могут распределяться через несколько цепей, логических узлов или устройств, проиллюстрированных на фиг. 10.

Микропроцессорный набор 1020 может устанавливать связь с шиной 1040, используя цепь 1041 интерфейса PtP. Шина 1040 может иметь одно или более устройств, которые устанавливать связь с ним, например такие как мост 1042 шины и устройства 1043 ввода/вывода. Через шину 1044 мост 1043 шины может устанавливать связь с другими устройствами, такими как клавиатура/манипулятор курсора типа мышь 1045, коммуникационные устройства 1046 (такие как модемы, устройства сетевого интерфейса или другие коммуникационные устройства, которые могут устанавливать связь с компьютерной сетью 1003), звуковые устройства ввода/вывода, и/или устройства 1048 для хранения данных. Устройство 1048 для хранения данных (которое может быть накопителем на жестком диске или NAND флеш-памятью, основанной на полупроводниковом накопителе) может сохранять код 1049, который может выполняться процессорами 1004.

Последующие примеры имеют отношение к дополнительным вариантам осуществления изобретения.

Пример 1 является запоминающим устройством, содержащим энергозависимую память, энергонезависимую память и контроллер, содержащий буфер памяти, а также логический блок для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения.

В примере 2 энергозависимая память, показанная в примере 1, может дополнительно включать в себя динамическое запоминающее устройство с произвольной выборкой (динамическое ЗУПВ, DRAM), а энергонезависимая память содержит трехмерную перекрестную память.

В примере 3 предмет обсуждения любого из примеров 1-2 может дополнительно включать в себя энергонезависимую память, которая обеспечивает резервную копию для энергозависимой памяти.

В примере 4 предмет обсуждения любого из примеров 1-3 может дополнительно включать в себя логический блок для приема запроса на подкачку страниц в оперативную память и в ответ на запрос на подкачку страниц в оперативную память перемещать страницу данных из энергонезависимой памяти в буфер памяти, обеспечивать сигнал для приложения, о том что страница данных является доступной, и в ответ на операцию считывания из приложения, записывать страницу данных из буфера памяти в энергозависимую память.

В примере 5 предмет обсуждения любого из примеров 1-4 может дополнительно включать в себя буфер памяти, который содержит множество строк данных сверхоперативной памяти, а контроллер дополнительно содержит логический блок, чтобы аннулировать строку данных сверхоперативной памяти в буфере памяти, когда строка данных сверхоперативной памяти записывается в энергозависимую память.

В примере 6 предмет обсуждения любого из примеров 1-5 может дополнительно включать в себя логический блок для приема запроса на операцию откачки страниц из оперативной памяти, и в ответ на запрос на операцию откачки страниц из оперативной памяти принимать операцию считывания по заданному адресу, в ответ на операцию считывания, производить считывание страницы данных из энергонезависимой памяти в буфер памяти и записывать страницу данных в энергонезависимую память.

В примере 7 предмет обсуждения любого из примеров 1-6 может дополнительно включать в себя источник энергии*.

Пример 8 является электронным устройством, содержащим процессор для осуществления работы операционной системы и по меньшей мере одно приложение и запоминающее устройство, содержащее энергозависимую память и энергонезависимую память, а также контроллер, содержащий буфер памяти и логический блок для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения, и драйвер для управления операциями доступа к памяти между по меньшей мере одним приложением и запоминающим устройством.

В примере 9 энергозависимая память примера 8 может дополнительно включать в себя энергозависимую память, которая содержит динамическое запоминающее устройство с произвольной выборкой (динамическое ЗУПВ, DRAM); а энергонезависимая память содержит трехмерную перекрестную память.

В примере 10 предмет обсуждения любого из примеров 8-9 может дополнительно включать в себя энергонезависимую память, которая обеспечивает резервную копию для энергозависимой памяти.

В примере 11 предмет обсуждения любого из примеров 8-10 может дополнительно включать в себя логический блок, чтобы генерировать запрос на подкачку страниц в оперативную память для перемещения страницы данных из энергонезависимой памяти в энергозависимую память, и аннулировать одну или более строк данных сверхоперативной памяти в процессоре для страницы.

В примере 12 предмет обсуждения любого из примеров 8-11 может дополнительно включать в себя логический блок, чтобы принимать запрос на подкачку страниц в оперативную память, и в ответ на запрос на подкачку страниц в оперативную память перемещать страницу данных из энергонезависимой памяти в буфер памяти, обеспечивать сигнал к приложению о том, что страница данных является доступной, и в ответ на операцию считывания из приложения, записывать страницу данных из буфера памяти в энергозависимую память.

В примере 13 предмет обсуждения любого из примеров 8-12 может дополнительно включать в себя буфер памяти, который содержит множество строк данных сверхоперативной памяти, и логический блок, чтобы аннулировать строки данных сверхоперативной памяти в буфере памяти, когда строка данных сверхоперативной памяти записывается в энергозависимую память.

В примере 14 предмет обсуждения любого из примеров 8-13 может дополнительно включать в себя логический блок, чтобы генерировать запрос на операцию откачки страниц из оперативной памяти для перемещения страницы данных из энергонезависимой памяти в энергозависимую память.

В примере 15 предмет обсуждения любого из примеров 8-14 может дополнительно включать в себя логический блок для приема запроса на операцию откачки страниц из оперативной памяти, и в ответ на запрос на операцию откачки страниц из оперативной памяти принимать считывающую операцию по заданному адресу, в ответ на считывающую операцию считывать страницу данных из энергонезависимой памяти в буфер памяти и записывать страницу данных в энергонезависимую память.

В примере 16 предмет обсуждения любого из примеров 8-15 может дополнительно включать в себя источник энергии.

Пример 17 является контроллером для запоминающего устройства, содержащего энергозависимую память и энергонезависимую память, при этом контроллер содержит буфер памяти и логический блок для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, причем данные в буфере памяти являются доступными для приложения.

В примере 18 энергозависимая память, показанная в примере 17, может дополнительно включать в себя энергозависимую память, которая содержит динамическое запоминающее устройство с произвольной выборкой (динамическое ЗУПВ, DRAM), а энергонезависимая память содержит трехмерную перекрестную память.

В примере 19 предмет обсуждения любого из примеров 17-18 может дополнительно включать в себя энергонезависимую память, которая обеспечивает резервную копию для энергозависимой памяти.

В примере 20 предмет обсуждения любого из примеров 17-19 может дополнительно включать в себя логический блок для приема запроса на подкачку страниц в оперативную память и в ответ на запрос на подкачку страниц в оперативную память перемещать страницу данных из энергонезависимой памяти в буфер памяти, обеспечивать сигнал к приложению о том, что страница данных является доступной, и в ответ на операцию считывания из приложения, записывать страницу данных из буфера памяти в энергозависимую память.

В примере 21 предмет обсуждения любого из примеров 17-20 может дополнительно включать в себя буфер памяти, который содержит множество строк данных сверхоперативной памяти, и логический блок, чтобы аннулировать строки данных сверхоперативной памяти в буфере памяти, когда строка данных сверхоперативной памяти записывается в энергозависимую память.

В примере 22 предмет обсуждения любого из примеров 17-21 может дополнительно включать в себя логический блок для приема запроса на операцию откачки страниц из оперативной памяти, и в ответ на запрос на операцию откачки страниц из оперативной памяти принимать считывающую операцию по заданному адресу, в ответ на считывающую операцию считывать страницы данных из энергонезависимой памяти в буфер памяти и записывать страницу данных в энергонезависимую память.

Пример 23 является компьютерным программным продуктом, содержащим логические инструкции, сохраняемые в энергонезависимой считываемой компьютером среде, которые при их выполнении контроллером для запоминающего устройства, содержащего энергозависимую память и энергонезависимую память, конфигурируют контроллер для логической схемы, передающей данные между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения.

В примере 24 предмет обсуждения примера 23 может дополнительно включать в себя логические инструкции, сохраняемые в энергонезависимой считываемой компьютером среде, которые при их выполнении контроллером для запоминающего устройства, содержащего энергозависимую память и энергонезависимую память, конфигурируют контроллер для приема запроса на подкачку страниц в оперативную память, и в ответ на запрос на подкачку страниц в оперативную память перемещают страницу данных из энергонезависимой памяти в буфер памяти, обеспечивать сигнал к приложению о том, что страница данных является доступной, и в ответ на операцию считывания из приложения, записывать страницу данных из буфера памяти в энергозависимую память.

В примере 25 предмет обсуждения любого из примеров 23-24 может дополнительно включать в себя буфер памяти, который содержит множество строк данных сверхоперативной памяти, и логические инструкции, сохраняемые в энергонезависимой считываемой компьютером среде, которые при их выполнении контроллером для запоминающего устройства, содержащего энергозависимую память и энергонезависимую память, конфигурируют контроллер таким образом, чтобы аннулировать строки данных сверхоперативной памяти в буфере памяти, когда строка данных сверхоперативной памяти записывается в энергозависимую память.

В примере 26 предмет обсуждения любого из примеров 23-25 может дополнительно включать в себя логические инструкции, сохраняемые в энергонезависимой считываемой компьютером среде, которые при их выполнении контроллером для запоминающего устройства, содержащего энергозависимую память и энергонезависимую память, конфигурируют контроллер для приема запроса на операцию откачки страниц из оперативной памяти, и в ответ на запрос на операцию откачки страниц из оперативной памяти принимают считывающую операцию по заданному адресу, в ответ на считывающую операцию считывают страницы данных из энергонезависимой памяти в буфер памяти и записывают страницу данных в энергонезависимую память.

В различных вариантах осуществления изобретения обсуждаемые здесь операции могут быть применены как аппаратная часть (например, электрические схемы), программное обеспечение, программно-аппаратные средства, микрокод, или их комбинации, которые могут быть обеспечены как компьютерный программный продукт, например включающий в себя вещественную (например, энергонезависимую) считываемую машиной или считываемую компьютером среду, имеющую сохраняемые в ней инструкции (или процедуры программного обеспечения), используемые для программирования компьютера, чтобы выполнять обсуждаемый здесь процесс. Кроме того, термин "logic" (логический) может включать в себя, например, программное обеспечение, аппаратную часть, или их комбинацию. Считываемая машиной среда может включать в себя запоминающее устройство, такое как обсуждаемые здесь устройства.

Ссылка в описании на «один вариант осуществления изобретения» или «вариант осуществления изобретения» ("embodiment") означает, что отдельный признак, структура, или характеристика, описываемые во взаимосвязи с вариантом осуществления изобретения, могут быть включены в состав по меньшей мере одного варианта исполнения. Появления фразы «в одном варианте осуществления изобретения» в различных местах описания могут все ссылаться на тот же самый вариант осуществления изобретения, но могут и не ссылаться.

Кроме того, в описании и формуле изобретения термины "coupled" и "connected" (присоединенный) могут использоваться наряду с их производными. В некоторых вариантах осуществления изобретения термин "connected" (присоединенный) может использоваться для обозначения того, что два или более элементов находятся в непосредственном физическом или электрическом контакте друг с другом. Термин "coupled" может означать, что два или более элементов находятся в непосредственном физическом или электрическом контакте. Однако "coupled" также может означать, что два или более элементов могут не находиться в непосредственном контакте друг с другом, но могут тем не менее взаимодействовать или влиять друг на друга.

Таким образом, хотя варианты осуществления изобретения были описаны на языке, являющимся специфическим для структурных признаков и/или методологических действий, следует принимать во внимание, что заявленный объект изобретения может не ограничиваться специфическими признаками или описанными действиями. В большей степени специфические признаки и действия раскрываются как образцовые формы применения заявленного объекта изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАТИВНОЕ РЕГУЛИРОВАНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ТВЕРДОТЕЛЬНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2014 |

|

RU2624563C2 |

| СПОСОБ И СИСТЕМА ДЛЯ ВИРТУАЛИЗАЦИИ ГОСТЕВОГО ФИЗИЧЕСКОГО АДРЕСА В СРЕДЕ ВИРТУАЛЬНОЙ МАШИНЫ | 2006 |

|

RU2393534C2 |

| УСТРОЙСТВО, СПОСОБ И СИСТЕМА УПРАВЛЕНИЯ МАТРИЦАМИ | 2010 |

|

RU2491616C2 |

| ЗАПОМИНАЮЩИЕ СИСТЕМЫ И ПАМЯТЬ С ПРИВЯЗКАМИ | 2014 |

|

RU2669008C2 |

| ЭНТРОПИЙНЫЙ КОДЕР ДЛЯ СЖАТИЯ ИЗОБРАЖЕНИЯ | 2011 |

|

RU2575679C2 |

| ШИНА РАЗБИЕНИЙ | 2005 |

|

RU2390827C2 |

| ОДНОПРОЦЕССОРНАЯ ЭЛЕКТРОННАЯ СИСТЕМА БОРТОВОЙ ДОКУМЕНТАЦИИ 3-ГО КЛАССА | 2011 |

|

RU2568779C2 |

| УПРАВЛЕНИЕ ВРЕМЕНЕМ ОБРАЩЕНИЯ К ПАМЯТИ | 2014 |

|

RU2618938C2 |

| ОТЛОЖЕННАЯ ОЧИСТКА БУФЕРОВ БЫСТРОГО ПРЕОБРАЗОВАНИЯ АДРЕСОВ | 2004 |

|

RU2361267C2 |

| СХЕМА СЖАТИЯ DRAM ДЛЯ СНИЖЕНИЯ ПОТРЕБЛЕНИЯ ЭНЕРГИИ ПРИ КОМПЕНСАЦИИ ДВИЖЕНИЯ И ОБНОВЛЕНИЯ ОТОБРАЖЕНИЯ | 2011 |

|

RU2599959C2 |

Изобретение относится к гибридным запоминающим устройствам. Технический результат заключается в повышении быстродействия памяти при том же размере и емкости памяти. Описываются запоминающие устройства, контроллеры и электронные устройства, содержащие запоминающие устройства. В одном варианте осуществления изобретения запоминающее устройство содержит энергозависимую память, энергонезависимую память и контроллер, содержащий буфер памяти и логический блок для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения. Также раскрываются и заявляются другие варианты осуществления изобретения. 3 н. и 14 з.п. ф-лы, 11 ил.

1. Запоминающее устройство, содержащее:

- энергозависимую память,

- энергонезависимую память, и

- контроллер, содержащий:

- буфер памяти; и

- логический блок для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения;

- логический блок для приема запроса на подкачку страниц в оперативную память, и в ответ на запрос на подкачку страниц в оперативную память:

перемещает страницу данных из энергонезависимой памяти в буфер памяти,

обеспечивает сигнал для приложения о том, что страница данных является доступной, и

в ответ на операцию считывания из приложения записывает страницу данных из буфера памяти в энергозависимую память.

2. Запоминающее устройство по п. 1, в котором энергозависимая память содержит динамическое запоминающее устройство с произвольной выборкой (DRAM, динамическое ЗУПВ); а энергонезависимая память содержит трехмерную перекрестную память.

3. Запоминающее устройство по п. 1, в котором энергонезависимая память обеспечивает резервную копию для энергозависимой памяти.

4. Запоминающее устройство по п. 1, в котором:

- буфер памяти содержит множество строк данных сверхоперативной памяти, и

- контроллер дополнительно содержит логический блок, чтобы аннулировать строку данных сверхоперативной памяти в буфере памяти, когда строка данных сверхоперативной памяти записывается в энергозависимую память.

5. Запоминающее устройство по п. 1, в котором контроллер содержит логический блок для приема запроса на операцию откачки страниц из оперативной памяти и в ответ на запрос на операцию откачки страниц из оперативной памяти:

- принимает операцию считывания по заданному адресу,

- в ответ на операцию считывания производит считывание страницы данных из энергонезависимой памяти в буфер памяти и

- записывает страницу данных в энергонезависимую память.

6. Устройство управления операциями доступа к памяти, содержащее:

- процессор для осуществления работы операционной системы и по меньшей мере одно приложение,

- запоминающее устройство, содержащее:

- энергозависимую память;

- энергонезависимую память, и

- контроллер, содержащий буфер памяти и логический блок для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения; и

- драйвер для управления операциями доступа к памяти между по меньшей мере одним приложением и запоминающим устройством, в котором драйвер содержит логический блок, чтобы:

- генерировать запрос на подкачку страниц в оперативную память для перемещения страницы данных из энергонезависимой памяти в энергозависимую память, и

- аннулировать одну или более строк данных сверхоперативной памяти в процессоре для страницы.

7. Устройство по п. 6, в котором энергозависимая память содержит динамическое запоминающее устройство с произвольной выборкой (динамическое ЗУПВ, DRAM), а энергонезависимая память содержит трехмерную перекрестную память.

8. Устройство по п. 6, в котором энергонезависимая память обеспечивает резервную копию для энергозависимой памяти.

9. Устройство по п. 6, в котором контроллер содержит логический блок, чтобы принимать запрос на подкачку страниц в оперативную память, и в ответ на запрос на подкачку страниц в оперативную память:

- перемещать страницу данных из энергонезависимой памяти в буфер памяти,

- обеспечивать сигнал к приложению о том, что страница данных является доступной, и

- в ответ на операцию считывания из приложения записывать страницу данных из буфера памяти в энергозависимую память.

10. Устройство по п. 9, в котором:

- буфер памяти содержит множество строк данных сверхоперативной памяти, и

- контроллер содержит логический блок, чтобы аннулировать строки данных сверхоперативной памяти в буфере памяти, когда строка данных сверхоперативной памяти записывается в энергозависимую память.

11. Устройство по п. 6, в котором драйвер содержит логический блок, чтобы генерировать запрос на операцию откачки страниц из оперативной памяти для перемещения страницы данных из энергонезависимой памяти в энергозависимую память.

12. Устройство по п. 6, в котором контроллер содержит логический блок для приема запроса на операцию откачки страниц из оперативной памяти, и в ответ на запрос на операцию откачки страниц из оперативной памяти:

- принимает считывающую операцию по заданному адресу,

- в ответ на считывающую операцию считывает страницу данных из энергонезависимой памяти в буфер памяти, и

- записывает страницу данных в энергонезависимую память.

13. Контроллер для запоминающего устройства, содержащий энергозависимую память и энергонезависимую память, при этом контроллер содержит:

- буфер памяти, и

- логический блок для передачи данных между энергонезависимой памятью и энергозависимой памятью через буфер памяти в ответ на запросы от приложения, при этом данные в буфере памяти являются доступными для приложения;

- логический блок для приема запроса на подкачку страниц в оперативную память, и в ответ на запрос на подкачку страниц в оперативную память:

- перемещает страницу данных из энергонезависимой памяти в буфер памяти,

- обеспечивает сигнал к приложению о том, что страница данных является доступной, и

- в ответ на операцию считывания из приложения записывает страницу данных из буфера памяти в энергозависимую память.

14. Контроллер по п. 13, в котором энергозависимая память содержит динамическое запоминающее устройство с произвольной выборкой (динамическое ЗУПВ, DRAM); а энергонезависимая память содержит трехмерную перекрестную память.

15. Контроллер по п. 13, в котором энергонезависимая память обеспечивает резервную копию для энергозависимой памяти.

16. Контроллер по п. 13, в котором:

- буфер памяти содержит множество строк данных сверхоперативной памяти, и

- контроллер дополнительно содержит логический блок, чтобы аннулировать строки данных сверхоперативной памяти в буфере памяти, когда строка данных сверхоперативной памяти записывается в энергозависимую память.

17. Контроллер по п. 13, дополнительно содержащий логический блок для приема запроса на операцию откачки страниц из оперативной памяти, и в ответ на запрос на операцию откачки страниц из оперативной памяти:

- принимает считывающую операцию по заданному адресу,

- в ответ на считывающую операцию считывает страницы данных из энергонезависимой памяти в буфер памяти, и

- записывает страницу данных в энергонезависимую память.

| RU 22442211 C2, 10.02.2012 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

Авторы

Даты

2017-08-03—Публикация

2014-06-23—Подача