Родственная заявка

Данная заявка относится и устанавливает приоритет предварительной заявки на патент США №61/829983 под названием "Оперативное регулирование производительности твердотельных запоминающих устройств" от 31.05.2013 и заявки на патент США №13/929708 под названием "Оперативное регулирование производительности твердотельных запоминающих устройств" от 27.06.2013.

Область техники

Настоящая заявка в целом относится к области электроники. Более конкретно, некоторые варианты осуществления изобретения в целом относятся к технологиям оперативного регулирования для твердотельных запоминающих устройств.

Уровень техники

В общем, память, используемая для хранения данных в вычислительной системе, может быть энергозависимой (чтобы хранить меняющуюся информацию) или энергонезависимой (для хранения постоянной информации). Изменяемые структуры данных, хранимые в энергонезависимой памяти, используют для временной или промежуточной информации, которая необходима для поддержки функциональности программы во время исполнения программы. С другой стороны, постоянные структуры данных, хранимые в энергонезависимой памяти, доступны после исполнения программы, и их можно использовать повторно. Более того, новые данные обычно вырабатывают сначала в виде непостоянных данных, до того как программа или пользователь решит сделать данные постоянными. Например, программисты или пользователи могут вызвать преобразование (т.е. создание экземпляра) изменяемых структур в энергозависимой памяти, которая непосредственно доступна процессору. Постоянные структуры данных, с другой стороны, создают в энергонезависимых запоминающих устройствах, таких как вращающиеся диски, подключенные к шинам ввода-вывода (I/O или IO), или энергонезависимых запоминающих устройствах, такие как флеш-память.

Для увеличения производительности в некоторых системах может использоваться твердотельный накопитель (SSD), который включает в себя энергонезависимую память, такую как флеш-память, для энергонезависимого хранения данных. Такие SSD, в общем, занимают меньше места, имеют меньший вес и являются более быстрыми, чем более традиционные накопители на жестких дисках (HDD). Более того, накопители на жестких дисках обеспечивают сравнительно более дешевое решение для хранения данных, и их используют во многих вычислительных устройствах в качестве энергонезависимого запоминающего устройства. Накопители на жестких дисках, тем не менее, могут использовать больше энергии по сравнению с твердотельными накопителями, так как в накопителях на жестких дисках необходимо вращать диски со сравнительно высокой скоростью и перемещать головки относительно вращающихся дисков для записи/чтения данных. Все эти физические перемещения приводят в выработке теплоты и повышают энергопотребление.

Для этого некоторые мобильные устройства переходят к применению твердотельных накопителей. Также некоторые стационарные вычислительные системы (такие как настольные компьютеры, рабочие станции, серверы и т.д.) могут использовать такие твердотельные накопители для повышения производительности. Тем не менее, применение той же модели использования для твердотельных накопителей в других типах вычислительных устройств может не всегда приводить к оптимальному балансу между производительностью и надежностью.

Краткое описание чертежей

Подробное описание приведено со ссылкой на прилагаемые чертежи. На фигурах самая левая цифра(ы) ссылочной позиции обозначает фигуру, на которой впервые встречается эта ссылочная позиция. Использование одинаковых ссылочных позиций на различных фигурах обозначает аналогичные или идентичные элементы.

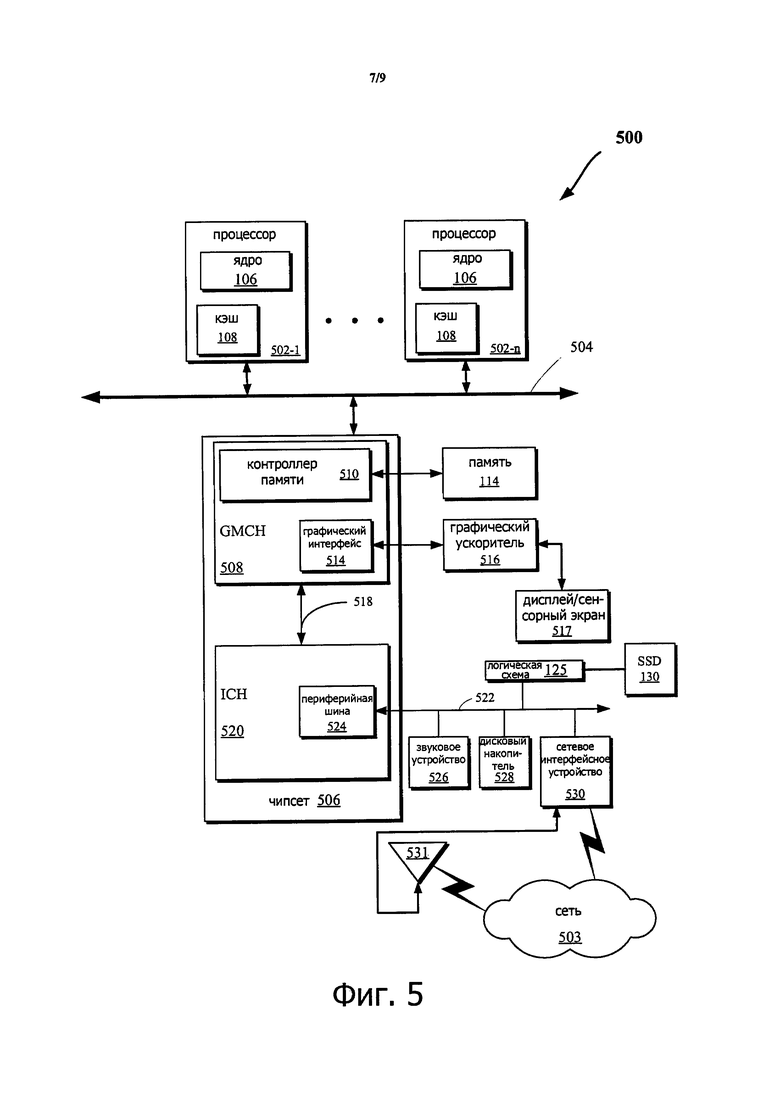

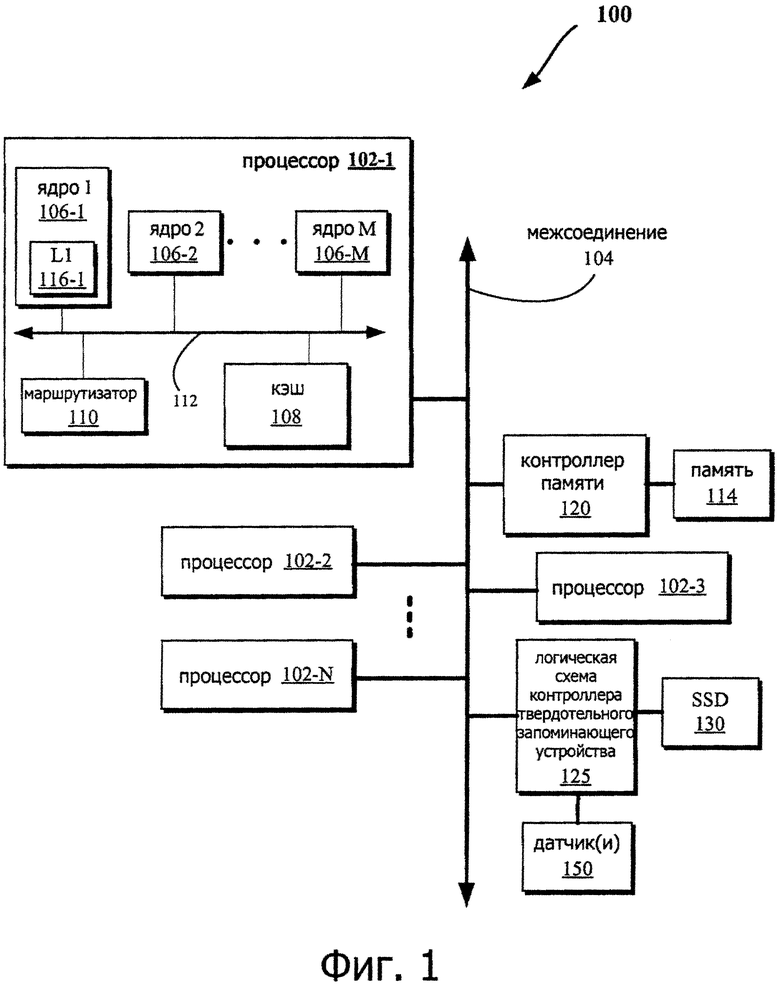

На фиг. 1, 5 и 6-7 показаны блок-схемы вариантов осуществления вычислительных систем, которые могут использоваться для реализации различных вариантов осуществления, обсуждаемых в этом документе.

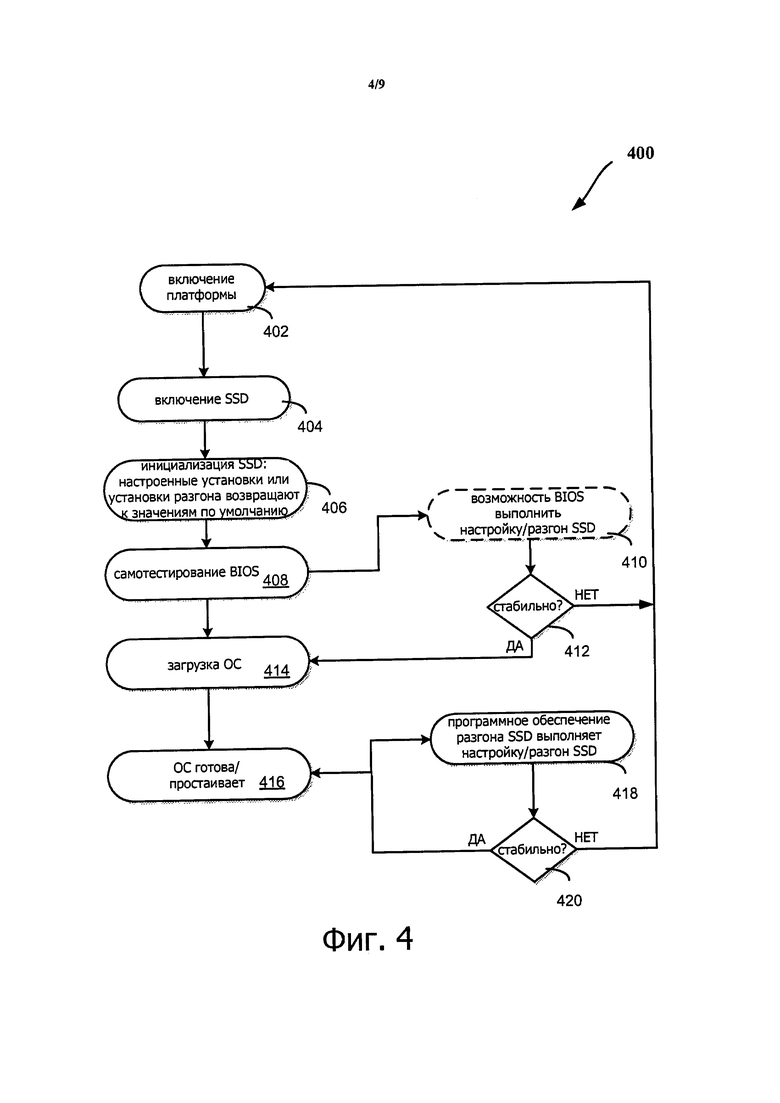

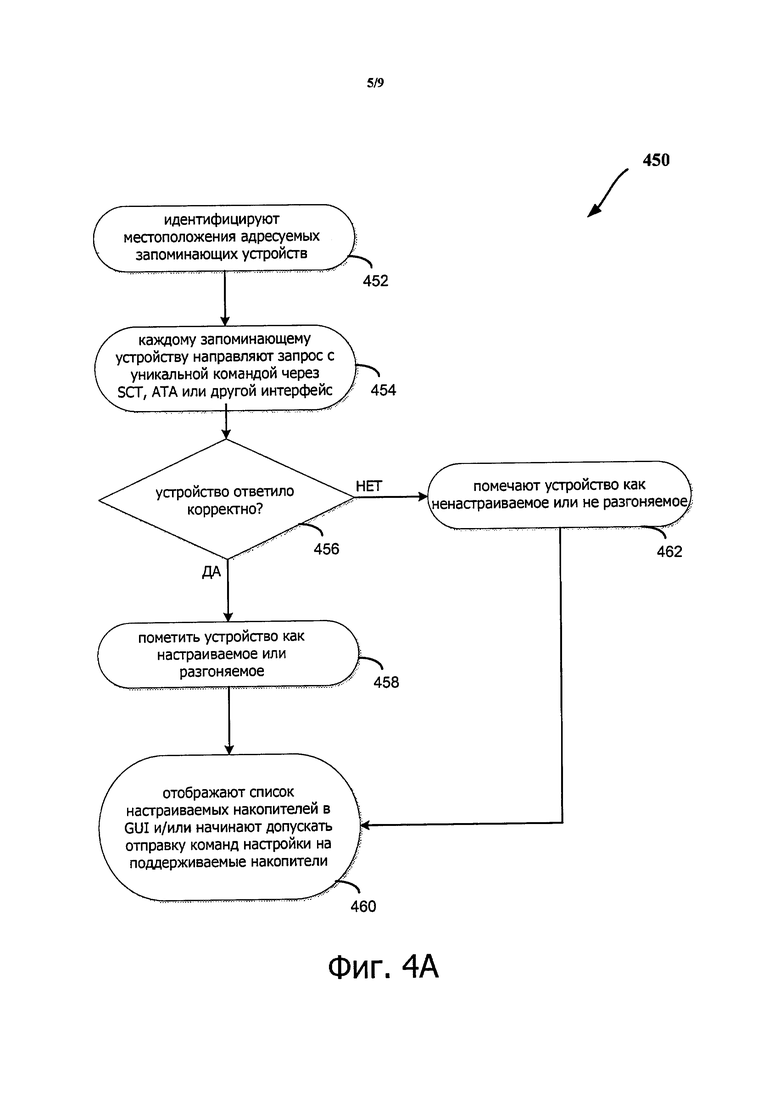

На фиг. 2, 4 и 4А показаны блок-схемы последовательности действий в соответствии с некоторыми вариантами осуществления.

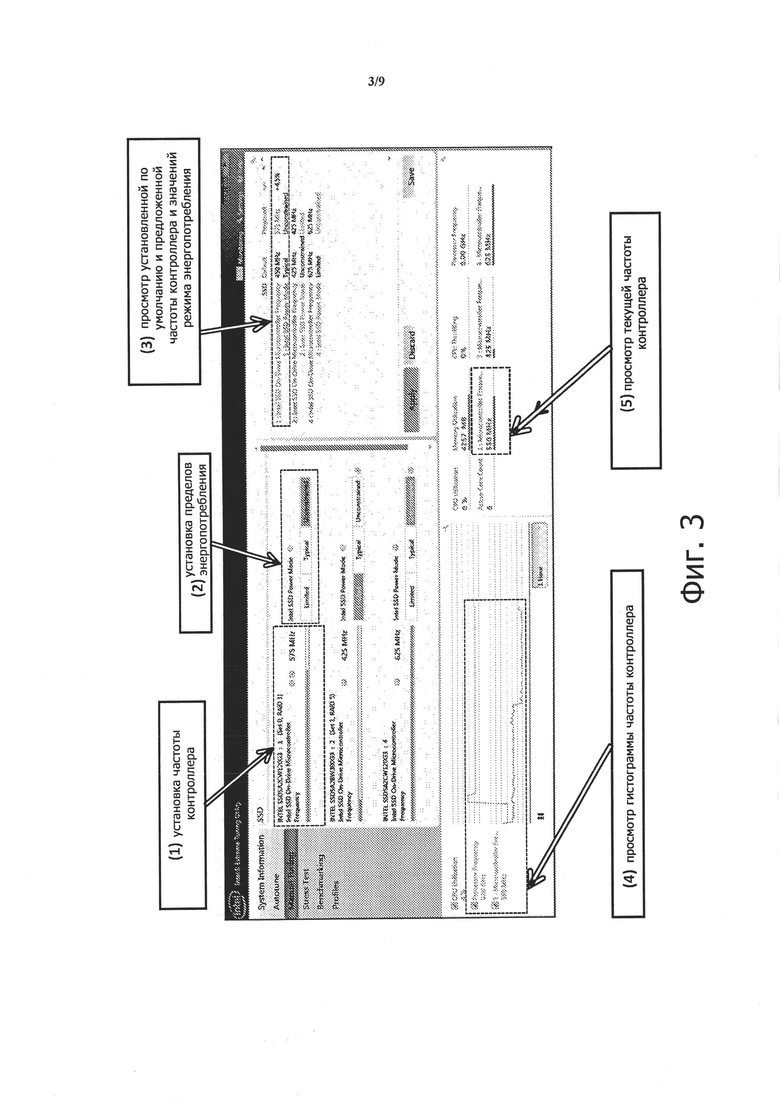

На фиг. 3 показан пример пользовательского интерфейса для обеспечения управления настройкой твердотельного запоминающего устройства в соответствии с вариантом осуществления.

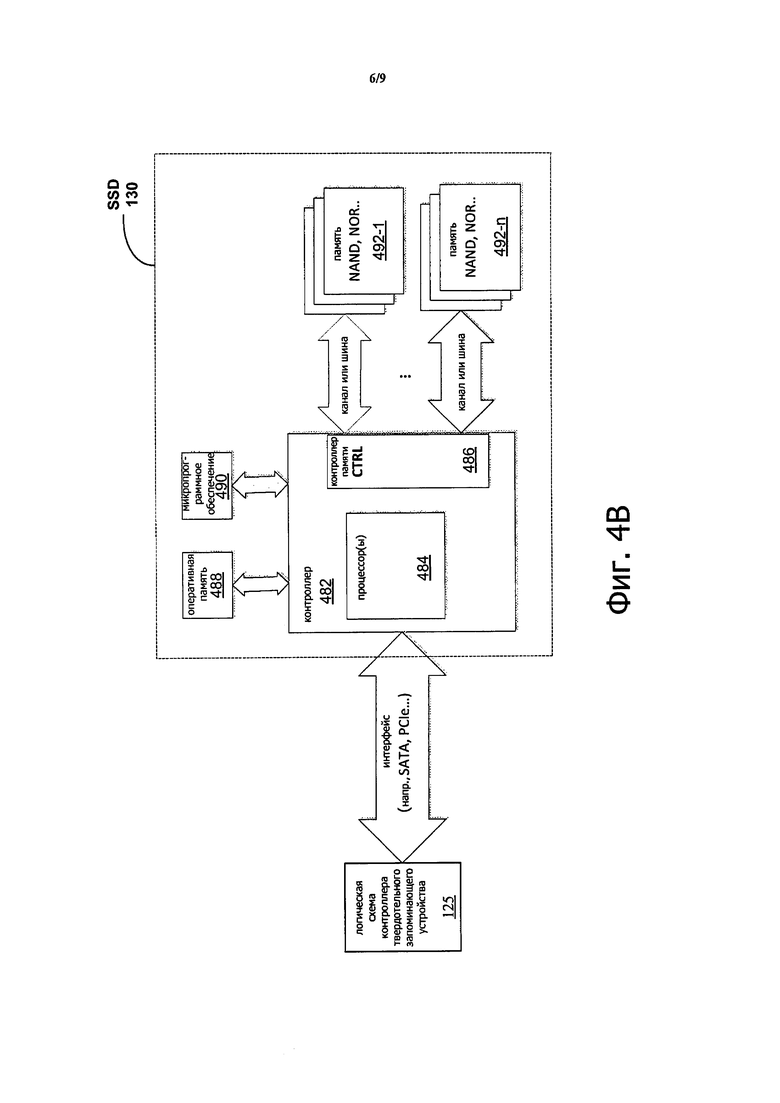

На фиг. 4В показана блок-схема различных компонентов SSD соответствии с вариантом осуществления.

Подробное описание изобретения

В нижеследующем описании для полного понимания различных вариантов осуществления изложено множество специфических деталей. Тем не менее, различные варианты осуществления изобретения могут быть реализованы без специфических подробностей. В остальных случаях, чтобы не затруднять понимание определенных вариантов осуществления изобретения, не приводятся описания широко известных способов, процедур, компонентов и схем. Кроме того, различные аспекты вариантов осуществления изобретения могут быть выполнены с использованием различных средств, таких как интегральные полупроводниковые схемы ("аппаратное обеспечение"), машинные инструкции, организованные в виде одной или нескольких программ ("программное обеспечение") или некоторое сочетание аппаратного и программного обеспечения. Для целей этого описания термин "логика" означает либо аппаратное, либо программное, либо микропрограммное обеспечение или некоторое их сочетание.

Некоторые варианты осуществления обеспечивают технологии оперативного регулирования производительности твердотельных накопителей. Как обсуждалось в этом документе, "оперативное" или "динамическое" регулирование производительности относится к регулированию производительности, не требующему перезагрузки вычислительной системы или операционной системы (ОС). Также такие твердотельные накопители могут включать в себя флеш-память (также называемую в этом документе твердотельным запоминающим устройством), память на фазовых переходах (РСМ), оперативная память произвольного доступа на основе переноса спинового момента (STTRAM), резистивную память произвольного доступа, 3D (3-мерную) координатную память, и т.д. Следовательно, в некоторых вариантах осуществления предложены способы и/или устройство для динамического управления производительностью SSD. Вариант осуществления позволяет конечным пользователям динамически управлять производительностью SSD, находя компромисс между производительностью, надежностью, тепловыми ограничениями и/или сроком службы устройства. В одном варианте осуществления командный интерфейс (например, посредством программного обеспечения) допускает такое согласование производительности на лету, например, из ОС.

В варианте осуществления конечный пользователь может применять технологии/признаки, обсуждаемые в этом документе, чтобы регулировать/настраивать производительность SSD, например, допуская разгон SSD. Под разгоном, в общем, понимается повышение рабочей частоты компонента (такого как SSD) сверх нормальной/заданной по умолчанию рабочей частоты, например, для увеличения производительности. Например, регулировка может быть основана на толерантности OEM (производителя оригинального оборудования) и/или конечного пользователя к изменениям тепловых условий, условий энергопотребления и/или надежности. Такие подходы допускают использование различных характеристик или модели использования для SSD в различных типах вычислительных устройств для того, чтобы обеспечить более оптимальный баланс между производительностью, надежностью, энергопотреблением, тепловыми условиями и т.д.

Более того, без некоторых вариантов осуществления может быть необходимо, чтобы SSD, используемые в более крупных настольных системах с дополнительным питанием и возможностями охлаждения, работали при тех же ограничениях, что и для SSD, применяемых в ультратонких ноутбуках при их меньших возможностях охлаждения и питания. Также, от файлового сервера может ожидаться большая надежность, чем от игровой системы. Для этого, некоторые варианты осуществления допускают для разработчика системы (или сообразительного пользователя) ввод этих оптимальных соотношений для платформы. Более того, некоторые варианты осуществления предусматривают зависящую от платформы возможность типа "Турбо" для SSD, где производительность SSD можно регулировать (также в этом документе используют термин "настраивать") в режиме реального времени или во время работы для одного или нескольких (последовательных или непоследовательных) периодов времени и/или на основе различных критериев, таких как: требования к рабочей загрузке программного обеспечения, данных от датчиков и/или окружающих условий. Кроме того, утилита экстремальной настройки от корпорации Intel® (XTU) позволяет конечным пользователям разгонять центральный процессор (CPU), графический процессор (GPU) и/или системную память для достижения более высокой производительности системы. В варианте осуществления эта утилита может быть расширена, чтобы позволить конечным пользователям разгонять их SSD, например, приводя к повышенной производительности для предельных нагрузок I/O (ввода/вывода) накопителя. Кроме того, допуская возможность разгонять SSD, некоторые варианты осуществления предотвращают потенциальную избыточную потерю данных (например, когда контроллер твердотельного накопителя прекращает работу). Более того, хотя в некоторых вариантах осуществления в этом документе обсуждаются технологии, применяемые к SSD, предполагается, что такие же или аналогичные технологии также могут быть применены к другим типам энергонезависимых запоминающих устройств.

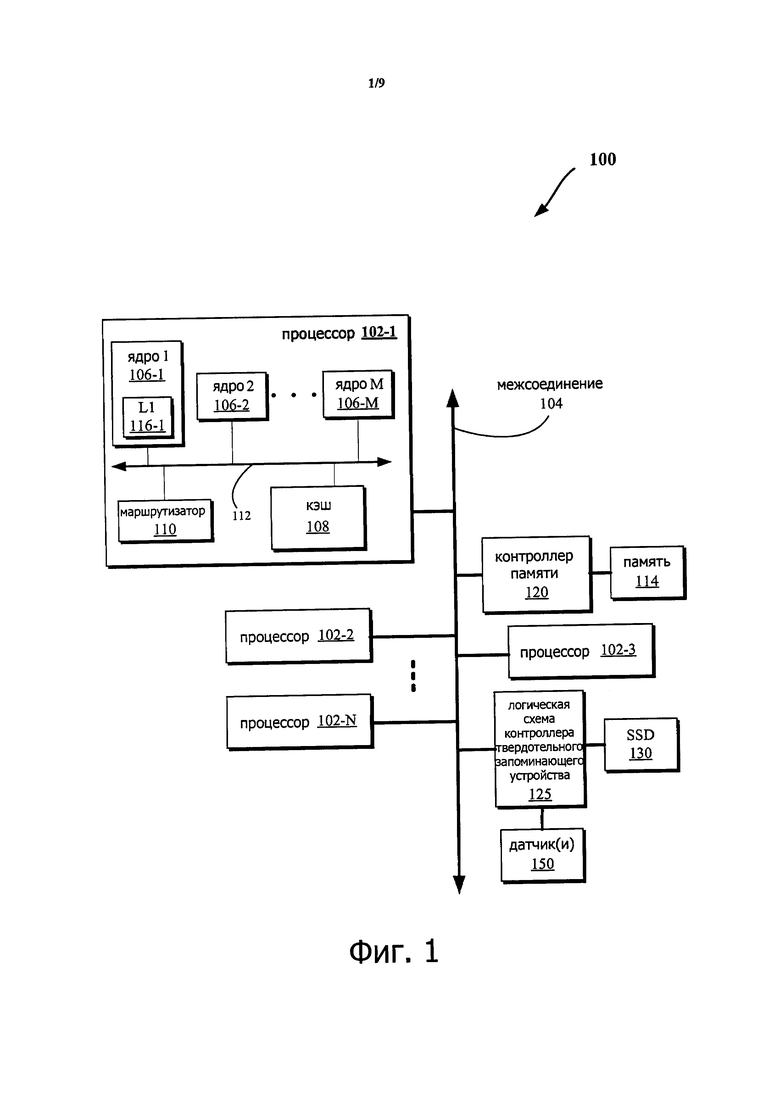

Технологии, обсуждаемые в этом документе, могут быть выполнены в различных вычислительных системах (включая, например, смартфоны, планшеты, портативные игровые консоли, ультрамобильные персональные компьютеры (UMPCs) и т.д.), таких, как обсуждаемые со ссылкой на фиг. 1-7. Более конкретно, на фиг. 1 показана блок-схема вычислительной системы 100 в соответствии с вариантом осуществления изобретения. Система 100 может включать в себя один или несколько процессоров 102-1, …, 102-N (в целом называемые здесь "процессорами 102" или "процессором 102"). Процессоры 102 могут осуществлять связь через межсоединение или шину 104. Каждый процессор может включать в себя различные компоненты, некоторые из которых для ясности обсуждаются только со ссылкой на процессор 102-1. Соответственно, каждый из оставшихся процессоров 102-2, …, 102-N может включать в себя такие же или аналогичные компоненты, обсуждаемые со ссылкой на процессор 102-1.

В варианте осуществления процессор 102-1 может включать в себя одно или несколько процессорных ядер 106-1, …, 106-М (называемые в этом документе "ядрами 106" или, в более общем случае, "ядром 106"), кэш 108 (который может быть общим кэшем или индивидуальным кэшем в различных вариантах осуществления) и/или маршрутизатор 110. Процессорные ядра 106 могут быть реализованы на одной интегральной микросхеме (IC). Более того, микросхема может включать в себя один или несколько общих и/или индивидуальных кэшей (таких как кэш 108), шины или межсоединения (такие как шина или межсоединение 112), логическую схему 120, контроллеры памяти (такие как обсуждаются со ссылкой на фиг. 5-7), или другие компоненты.

В одном варианте осуществления маршрутизатор 110 может использоваться для осуществления связи между различными компонентами процессора 102-1 и/или системы 100. Более того, процессор 102-1 может включать в себя более одного маршрутизатора 110. Более того, множество маршрутизаторов 110 могут сообщаться, чтобы сделать возможным маршрутизацию данных между различными компонентами внутри или за пределами процессора 102-1.

Кэш 108 может хранить данные (например, включающие в себя инструкции), которые используются одним или несколькими компонентами процессора 102-1, такими как ядра 106. Например, кэш 108 может локально кэшировать данные, хранящиеся в памяти 114, чтобы компоненты процессора 102 могли быстрее получать к ним доступ. Как показано на фиг. 1, память 114 может сообщаться с процессорами 102 через межсоединение 104. В варианте осуществления кэш 108 (который может быть общим) может иметь различные уровни, например, кэш 108 может являться кэшем среднего уровня и/или кэшем последнего уровня (LLC). Также, каждое из ядер 106 может включать в себя кэш (116-1) первого уровня (L1) (в целом, называемый в этом документе "L1-кэшем 116"). Различные компоненты процессора 102-1 могут непосредственно сообщаться с кэшем 108 через шину (например, шину 112) и/или контроллер памяти или концентратор.

Как показано на фиг. 1, память 114 может быть соединена с другими компонентами системы 100 через контроллер 120 памяти. Память 114 в некоторых вариантах осуществления может включать в себя энергонезависимую память, такую как флеш-память (или твердотельное запоминающее устройство, включая SSD), PCM, SSTTRAM, резистивная память произвольного доступа, 3D (3-мерная) координатная память и т.д. Хотя контроллер памяти 120 показан соединенным между межсоединением 104 и памятью 114, контроллер памяти 120 может быть расположен где-то в другом месте системы 100. Например, в некоторых вариантах осуществления контроллер 120 памяти или его части могут быть выполнены в одном из процессоров 102. Также, в некоторых вариантах осуществления система 100 может включать в себя логическую схему (например, логическую схему 125 контроллера твердотельного запоминающего устройства) для управления доступом к одному или нескольким NVM-устройствам или энергонезависимым запоминающим устройствам (включая одно или несколько твердотельных запоминающих устройств) (таким как один или несколько SSD 130, дополнительно обсуждаемым со ссылкой на фиг. 2), где в некоторых вариантах осуществления одно или несколько NVM-устройств могут быть выполнены на одной и той же интегральной схеме). Более того, хотя логическая схема 125 показана на фиг. 1 непосредственно соединенной с межсоединением 104, логическая схема 125 может, как вариант, сообщаться через шину запоминающих устройств/межсоединение (такую как шина SATA (последовательный интерфейс обмена данными с накопителями информации), обсуждаемая со ссылкой на фиг. 2) с одним или несколькими другими компонентами системы 100 (например, когда шина запоминающих устройств соединена с межсоединением 104 через некоторую другую логическую схему, такую как межшинный мост, чипсет (как обсуждаемый со ссылкой на фиг. 5-6) и т.д.). Кроме того, логическая схема 125 в различных вариантах осуществления может быть встроена в контроллер памяти (такой как обсуждаемые со ссылкой на фиг. 1 и 5-6) или по меньшей мере выполнена на той же интегральной схеме.

Более того, логическая схема 125 может быть соединена с одним или несколькими датчиками 150, чтобы принимать информацию (например, в виде одного или нескольких битов или сигналов), чтобы показывать состояние или значения, определенные одним или несколькими датчиками 150. Датчик(и) 150 может быть выполнен вблизи от компонентов системы 100 (или других вычислительных систем, обсуждаемых в этом документе, таких как обсуждаемые со ссылкой на другие фигуры, включая, например, 5-7), таких как ядра 106, межсоединения 104 или 112, компонентов, расположенных за пределами процессора 102, SSD, шины SSD, шины SATA, логической схемы 125 и т.д., чтобы воспринимать изменения различных факторов, влияющих на энергетическое/тепловое поведение системы/платформы, например, температуру, рабочую частоту, рабочее напряжение, энергопотребление и/или межъядерную передачу информации и т.д.

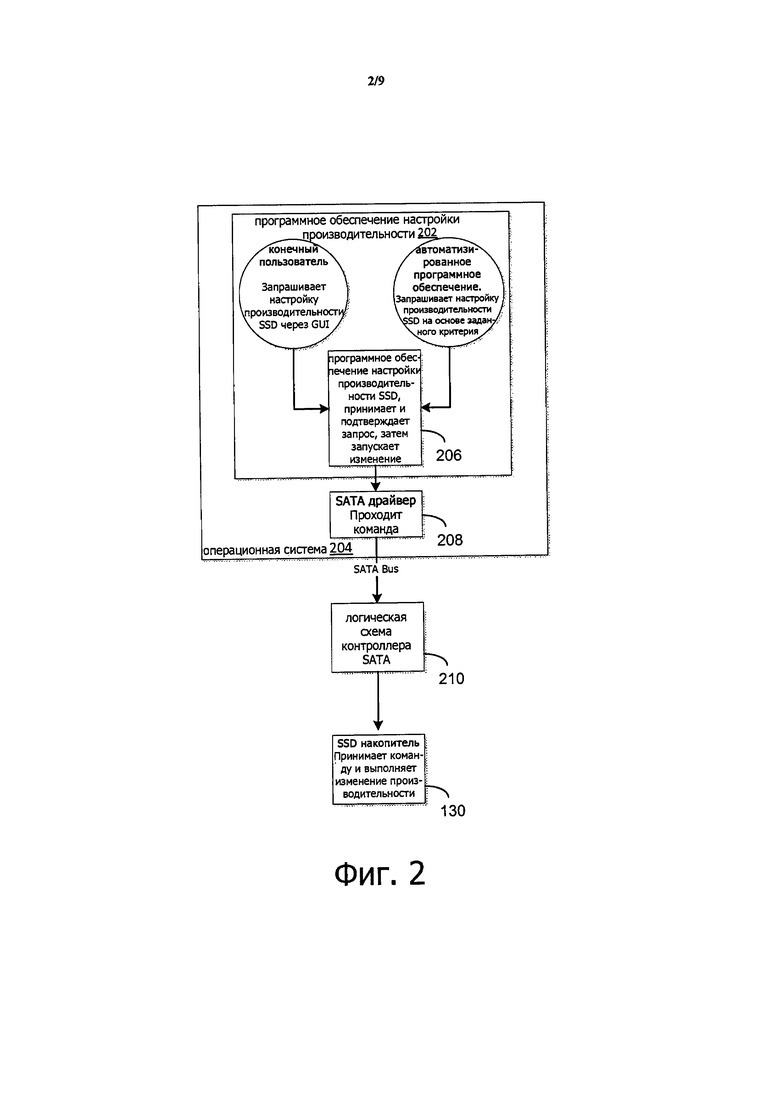

На фиг. 2 показана высокоуровневая блок-схема последовательности действий настройки SSD в соответствии с вариантом осуществления. Хотя касательно фиг. 2 обсуждается настройка SSD, такие же или аналогичные технологии также можно применить к любому типу твердотельного NVM запоминающего устройства. Как показано, программа 202 настройки производительности (которая может представлять собой приложение, выполняемое в ОС 204) включает в себя программное приложение 206 настройки производительности SSD, которое принимает и подтверждает запрос(ы) на настройку производительности SSD от конечного пользователя (например, через графический пользовательский интерфейс (GUI)) и/или от автоматизированного программного приложения (например, на основе одного или нескольких заданных критериев).

На этапе 208 передают команду драйвера, чтобы запустить настройку/изменение производительности SSD (например, через драйвер запоминающего устройства, такого как SATA-драйвер). Команду драйвера передают на логическую схему 210 SATA контроллера (например, входящую в периферийный контроллер-концентратор (РСН) или другое оборудование) через SATA-шину. В варианте осуществления SATA контроллер 210 совпадает с логической схемой 125 на фиг. 1 или аналогичен ей. В свою очередь, SSD 130 принимает команду и выполняет изменение производительности, применимое к SSD (например, изменение рабочей частоты шины, которая соединяет внутренний SSD контроллер с энергонезависимыми ячейками памяти в SSD, энергонезависимыми ячейками памяти и/или другими компонентами SSD).

На фиг. 3 показан пример GUI, предназначенного для обеспечения программных элементов управления для настройки SSD в соответствии с вариантом осуществления. Как обсуждается в этом документе, настройка SSD относится к регулированию производительности SSD, например, позволяя разгонять SSD. Также, под разгоном, в общем, понимается повышение рабочей частоты компонента (такого как SSD, его интерфейс/шина или логическая схема 125 контроллера SSD и т.д.) сверх нормальной/заданной по умолчанию рабочей частоты, например, для увеличения производительности. Например, регулировка может быть основана на толерантности OEM и/или конечного пользователя к изменениям тепловых условий, условий энергопотребления и/или надежности. Хотя касательно фиг. 3 обсуждаются технологии настройки SSD, такие же или аналогичные технологии также можно применить к другим типам твердотельных запоминающих устройств. На фиг. 3 в одном варианте осуществления показан пример реализации с использованием утилиты экстремальной настройки от корпорации Intel® (XTU). Как показано, GUI допускает установку частоты (1) контроллера SSD, такой как рабочая частота логической схемы 125 на фиг. 1, установку пределов (2) энергопотребления SSD, просмотр установленной по умолчанию и предлагаемой частоты контроллера SSD и значений (3) режима энергопотребления, просмотр гистограммы частоты контроллера SSD в течение заданного периода (4) времени и/или просмотр текущей рабочей частоты (5) контроллера SSD.

Более того, в некоторых вариантах осуществления обеспечивается оперативная регулировка параметров производительности для твердотельных запоминающих устройств (включая SSD) путем предоставления возможности вносить изменения без перезагрузки системы или ОС. Допускается несколько опций настройки в реальном времени посредством механизмов связи и управления программного и/или аппаратного обеспечения, чтобы управлять динамической настройкой, как, например, обсуждается со ссылкой на фиг. 2-3. В варианте осуществления выполнен командный интерфейс для обнаружения конфигурируемых опций и передачи изменений на твердотельное запоминающее устройство.

Например, на фиг. 3 показано, как можно использовать программное приложение для регулировки параметров производительности SSD. Хотя со ссылкой на фиг. 2-3 обсуждается пример реализации, варианты осуществления изобретения могут быть выполнены через различные сочетания служб, приложений и фоновых служб.

Соответственно, в некоторых вариантах осуществления возможен разгон твердотельного запоминающего устройства путем настройки частоты контроллера устройства (например, логической схемы 125 на фиг. 1), динамического масштабирования частоты логической схемы контроллера свыше стандартного уровня с использованием SCT (Smart Command Transport) команды (которая может быть передана через SATA шину или другой интерфейс, включая, например, межсоединение 104 на фиг. 1), допуская быстрый бросок энергопотребления до безопасного предела энергопотребления запоминающего устройства (например, где "бросок" означает пиковый период энергопотребления во время пика передачи данных), допуская (например, для SoC (однокристальной системы)) превышение заданного OEM порогового энергопотребления с помощью API (прикладного программного интерфейса), допуская (например, для NAND и/или NOR или других типов NVM) разгон флеш-памяти путем динамического масштабирования частоты флеш-памяти сверх стандартного уровня посредством SCT команды и/или отбор контроллеров твердотельных запоминающих устройств для совокупностей с наибольшей производительностью путем использования внутренних регистров (например, посредством сегментации или "классификации" контроллеров твердотельных запоминающих устройств с помощью их определенного/назначенного верхнего/максимального предела рабочей частоты). "Совокупность", в общем, относится к совокупности электронных компонентов, которые являются SKU (единицей учета) на основе классификации их определенной/назначенной рабочей частоты.

Более того, такие технологии можно использовать для того, чтобы задействовать признак "SSD Turbo", где логика платформы (например, программное и/или микропрограммное обеспечение) может динамически модифицировать производительность SSD, чтобы сбалансировать/изменить производительность относительно времени работы от батареи в определенных форм-факторах и рабочих условиях. Также, некоторые варианты осуществления предотвращают катастрофические неисправности (например, вызванные атаками злоумышленника), обеспечивая способы восстановления (такие как обсуждаемые со ссылкой на фиг. 4) и фиксированные границы на входные диапазоны для настройки параметров производительности SSD (такие как пороговые значения частоты для устройства флеш-памяти и/или логической схемы 125 контроллера), чтобы обеспечить дополнительную защиту, как будет дополнительно обсуждаться ниже. Также, может быть выполнена утилита для реинициализации привода после неисправности, например, путем стирания привода, делая его опять пригодным к использованию.

На фиг. 4 показана блок-схема последовательности операций способа 400 для восстановления после неисправности в соответствии с вариантом осуществления. Способ 400 можно использовать для восстановления стабильности после неисправности, например, из-за выбора чрезмерно агрессивных параметров настройки при настройке производительности SSD. Хотя касательно фиг. 4 обсуждаются технологии настройки SSD, такие же или аналогичные технологии также можно применить к другим типам NVM устройств. В различных вариантах осуществления одно или несколько действий способа 400 могут быть выполнены одним или несколькими компонентами, обсуждаемыми со ссылкой на другие фигуры (например, логической схемой 125).

Со ссылкой на фиг. 4, после включения платформы на этапе 402 включается SSD на этапе 404. На этапе 406 выполняют инициализацию SSD (например, возвращая установки настройки или разгона к значениям по умолчанию). На этапе 408 выполняют самотестирование при включении питания BIOS (базовой системы ввода-вывода). На этапе 410 BIOS имеет возможность выполнять тестирование SSD и/или разгон. На этапе 412 определяют, является ли стабильной работа SSD, и если нет, то происходит сброс системы путем возврата к этапу 402. В противном случае выполнение способа 400 продолжается загрузкой ОС на этапе 414 (например, с SSD или другого NVM устройства). Как вариант, за этапом 408 может непосредственно следовать 414. На этапе 416 ОС готова и работает (например, простаивает). В варианте осуществления выполняют этапы 418 и/или 420 (как только ОС будет в рабочем состоянии на этапе 416), чтобы отрегулировать разгон/настройку SSD и определить стабильность работы SSD при текущих настройках. Если работа SSD становится нестабильной на этапе 420, то происходит сброс системы путем возврата к этапу 402.

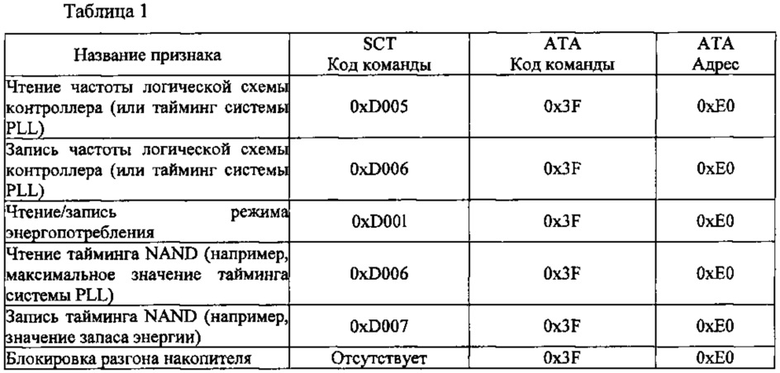

В различных вариантах осуществления используют команды SCT/ATA (интерфейс обмена данными с накопителями информации) для связи с SSD, чтобы выполнить настройку или разгон. Команда SCT может быть передана посредством команды SATA, отправленной на SSD. Ниже в таблице 1 перечислены SCT команды, которые могут быть использованы в некоторых вариантах осуществления (которые в некоторых вариантах осуществления могут зависеть от производителя). В одном варианте осуществления используются SCT команды для значения тайминга NAND, максимального значения частоты контроллера и значения запаса энергии. В варианте осуществления команду блокировки разгона SSD используют, чтобы программно предотвращать разгон накопителя пользователями, пока эта возможность не будет специально разблокирована (например, способствуя предотвращению ущерба от вредоносного кода или некоторых пользователей). Следовательно, блокировка предотвращает настройку или разгон, а разблокировка допускает изменения. Команда блокировки может вызвать установку (или сброс в зависимости от реализации) бита статуса блокировки в некотором запоминающем устройстве (таком как память (включая запоминающие устройства, обсуждаемые со ссылкой на фиг. 1 или 5-7), регистр, память в логической схеме 125 контроллера, в микропрограммном обеспечении, в SSD, и т.д.). Для дополнительной защиты некоторые варианты осуществления ограничивают/лимитируют диапазон принятых значений для элементов, приведенных ниже.

Более того, команды АТА могут использоваться для чтения модели/серийного номера SSD и другой идентификационной информации (например, по АТА адресам в запоминающем устройстве, микропрограммном обеспечении и т.д.). Температура SSD также может отслеживаться посредством АТА команды (например, с помощью одного или нескольких датчиков 150 на фиг. 1, которые могут быть физически расположены возле SSD, внутри SSD или иным образом термически связаны с SSD).

Некоторые варианты осуществления используют существующие протоколы управления SCT и АТА; тем не менее, для уникальных признаков настройки, обсуждаемых в этом документе (например, таких, как приведенные в таблице 1), добавляют новые команды. Большинство используемых команд являются основанными на SCT командами. Например, касательно последней строки таблицы 1, команда блокировки разгона накопителя создана (и полдюжины других, показанных в таблице 1) для управления возможностью настройки производительности SSD на лету и в реальном времени (в отличие от использования жестко запрограммированного микрокода, который производители SSD могли бы использовать, например, для развития/тестирования своих решений).

Более того, в некоторых вариантах осуществления применяют АТА команды, например, для телеметрии входов контуров обратной связи, если интеллектуальное программное обеспечение динамически изменяет параметры настройки. Например, при установке пределов производительности запоминающее устройство может нагреться, и могут использоваться АТА команды для получения данных о температуре, чтобы обнаружить эту ситуацию и сократить один или несколько параметров настройки, чтобы сохранить привод в нормальных условиях работы.

На фиг. 4А показана блок-схема последовательности операций способа 450 для определения того, какой из приводов или запоминающих устройств (например, SSD) в системе можно настраивать, в соответствии с вариантом осуществления. В варианте осуществления способ 450 выполняют до того, как пользователю с помощью программного обеспечения или утилит будет предоставлена опция настройки производительности. В различных вариантах осуществления одно или несколько действий способа 400 могут быть выполнены одним или несколькими компонентами, обсуждаемыми со ссылкой на другие фигуры (например, логической схемой 125).

Со ссылкой на фиг. 4А на этапе 452 определяют места для адресуемых запоминающих устройств. На этапе 454 на каждое запоминающее устройство (идентифицированное на этапе 452) подается запрос с уникальной командой (например, посредством SCT/ATA команд или другого интерфейса). На этапе 456, если устройство корректно отвечает на запрос, выполненный на этапе 454, то на этапе 458 это устройство помечается как настраиваемое. На этапе 460 отображают список настраиваемых накопителей (например, с помощью графического пользовательского интерфейса (GUI)) и/или разрешают отправлять команды настройки на поддерживаемые накопители. Как показано на фиг. 4А, если на этапе 456 устройство не может ответить, то на этапе 462 устройство помечают как ненастраиваемое, и способ 450 возвращается к этапу 460.

На фиг. 4В показана блок-схема различных компонентов SSD в соответствии с вариантом осуществления. Как показано на фиг. 4В, SSD 130 включает в себя логическую схему 482 контроллера (которая, в свою очередь, включает в себя одно или несколько процессорных ядер или процессоров 484 и логическую схему 486 контроллера памяти), оперативную память произвольного доступа (RAM) 488, устройство 490 для хранения микропрограммного обеспечения и один или несколько модулей 492-1, …, 492-n памяти (которые могут включать в себя NAND, NOR или другие типы энергонезависимой памяти). Модули 492-1, …, 492-n памяти соединены с логической схемой 486 контроллера памяти через один или несколько каналов памяти или шины. Также, SSD 130 сообщается с логической схемой 125 через интерфейс (такой как SATA, интерфейс PCIe (разъем взаимодействия периферийных компонент типа экспресс) и т.д.).

Более того, настройка может быть инициирована системным программным обеспечением (например, приложением, утилитой и т.д.) или системным BIOS. Также, настройка может быть инициирована вручную (например, через пользовательский GUI) или автоматически (например, интеллектуальной логической схемой, включающей в себя программное и/или микропрограммное обеспечение). Команды для инициации этой настройки могут использовать SCT или АТА протоколы, такие как обсуждавшиеся со ссылкой на таблицу 1 выше. Например, если запуск был выполнен из ОС, то команды проходят через драйвер запоминающего устройства (который, например, может храниться в памяти 114 на фиг. 1), системный интерфейс, шину SATA или запоминающее устройство PCIe (например, SSD 130). Затем, логическая схема 482 контроллера на запоминающем устройстве исполняет микропрограммный код, чтобы разобрать и выполнить команды.

В варианте осуществления логическая схема 482 контроллера может менять собственную тактовую/рабочую частоту, меняя соотношение (так называемый множитель) на свою собственную тактовую частоту. Например, если номинальная частота контроллера составляет 33,3 МГц, а обычный фиксированный множитель равен 3 для эффективной частоты 100 МГц, то изменение соотношения на 4 даст более высокую (например, 133 МГц) тактовую частоту, что может увеличить производительность. Аналогично, в различных вариантах осуществления можно изменить тактовую/рабочую частоту одной или нескольких шин или каналов, соединенных между модулями 492-1, …, 492-n памяти и логической схемой 786 контроллера, а также рабочие/тактовые частоты одного или нескольких модулей 492-1, …, 492-n памяти. Более того, хотя приведен пример изменения соотношений, вместо этого (или в дополнение к этому) также можно непосредственно изменить номинальную тактовую частоту. В таких случаях, последовательность действий будет аналогичной, и, как вариант, она может включать в себя связь/управление внешним источником тактовой частоты.

В соответствии с некоторыми вариантами осуществления, используемые элементы управления могут включать в себя одно или несколько из следующего: (а) частота логической схемы 125 контроллера, например, полученная из тайминга системы PLL (фазовой автоподстройки частоты)) (например, примерно от 400 МГц до 600 МГц); (b) частота шины SSD, которая может включать в себя шину SATA, соединенную с SSD, внутреннюю шину в SSD, которая соединена с энергонезависимыми ячейками памяти SSD и т.д. (например, переключающаяся от 83 МГц до 100 МГц); и/или (с) режим энергопотребления (как, например, низкое, обычное, неограниченное и т.д.).

Кроме того, в соответствии с некоторыми вариантами осуществления, отслеживаемые величины могут включать в себя одно или несколько из следующего: температуру, частоту логической схемы 125 контроллера, частоту шины флеш-памяти (которая, например, может быт такой же, что и частота логической схемы 125 контроллера), рабочую частоту твердотельного запоминающего устройства и/или запас энергии.

Более того, некоторые варианты осуществления предусматривают зависящую от платформы возможность типа "Турбо" для твердотельного запоминающего устройства, где, например, можно увеличить производительность твердотельных запоминающих устройств, например, в режиме реального времени для одного или нескольких (последовательных или непоследовательных) периодов времени и/или на основе различных критериев, таких как: требования к рабочей загрузке программного обеспечения, данных от датчиков и/или окружающих условий. Признак Турбо SSD может быть выстроен с помощью стандартных блоков настройки и разгона SSD, обсуждаемых вместе в этом документе. Следовательно, некоторые варианты осуществления впервые обеспечивают инфраструктуру, которая допускает динамическое изменение производительности SSD, включая мониторинг частот(ы), энергопотребления и параметров обратной связи. Таким образом, общий принцип Турбо можно применить к SSD, например, ускоряя SSD, чтобы удовлетворить пиковые запросы, и замедляя SSD (используя более низкие уровни энергопотребления), когда требования снижаются.

На фиг. 5 показана блок-схема вычислительной системы 500 в соответствии с вариантом осуществления системы. Вычислительная система 500 может включать в себя один или несколько центральных процессоров (CPU) 502 или процессоров, которые сообщаются через сеть межсоединения 504 (или шину). Процессоры 502 могут включать в себя процессор общего назначения, сетевой процессор (который обрабатывает данные, передаваемые по компьютерной сети 503), прикладной процессор (такой, как процессоры, используемые в сотовых телефонах, смартфонах и т.д.) или другие типы процессоров (включая процессор с архитектурой сокращенного набора команд (RISC) или с архитектурой полного набора команд (CISC)). Могут использоваться различные типы компьютерных сетей 503, включая проводные (например, Ethernet, Gigabit, Fiber и т.д.) или беспроводные сети (такие как сотовые, 3G (технология сотовой связи третьего поколения или беспроводной формат 3-го поколения (UWCC)), 5G, маломощные встроенные (LPE) и т.д.). Более того, процессоры 502 могут иметь одноядерную или многоядерную архитектуру. Процессоры 502 с многоядерной архитектурой могут объединять ядра разных типов на одном кристалле интегральной схемы (IC). Процессоры 502 с многоядерной архитектурой также могут быть выполнены в виде симметричных или асимметричных мультипроцессоров.

В варианте осуществления один или несколько процессоров 502 могут быть такими же или аналогичными процессорам 102 на фиг. 1. Например, один или несколько процессоров 502 может включать в себя одно или несколько ядер 106 и/или кэш 108. Также, действия, обсуждавшиеся со ссылкой на фиг. 1-4, могут быть выполнены одним или несколькими компонентами системы 500.

Чипсет 506 также может сообщаться с сетью 504 межсоединений. Чипсет 506 может включать в себя контроллер-концентратор 508 графической и оперативной памяти (GMCH). GMCH 508 может включать в себя контроллер 510 памяти (который в варианте осуществления может быть таким же или аналогичным контроллеру 120 памяти на фиг. 1), который сообщается с памятью 114. Память 114 может хранить данные, включая последовательности инструкций, исполняемых CPU 502 или любым другим устройством, входящим в вычислительную систему 500. Также, система 500 включает в себя логическую схему 125 и SSD 130 (которые в различных вариантах осуществления могут быть соединены с системой 500 через шину 522, как показано, через другие межсоединения, как, например, 504, где логическая схема 125 входит в чипсет 506 и т.д.). В одном варианте осуществления изобретения память 114 может включать в себя одно или несколько энергозависимых запоминающих устройств (или память), таких как оперативная память (RAM), динамическая память (DRAM), синхронная динамическая память (SDRAM), статическая оперативная память (SRAM) или другие типы запоминающих устройств. Также может использоваться энергонезависимая память, такая как жесткий диск, флеш, РСМ, 3D координатная память, резистивная память произвольного доступа и STTRAM. С сетью 504 межсоединений могут сообщаться дополнительные устройства, такие как несколько CPU и/или несколько системных памятей.

GMCH 508 также может включать в себя графический интерфейс 514, который сообщается с графическим ускорителем 516. В одном варианте осуществления изобретения графический интерфейс 514 может сообщаться с графическим ускорителем 516 через ускоренный графический порт (AGP). В варианте осуществления изобретения дисплей 517 (например, дисплей с плоским экраном, сенсорный экран и т.д.) может сообщаться с графическим интерфейсом 514 через, например, конвертер сигнала, который транслирует цифровое представление изображения, хранящегося на запоминающем устройстве, таком как видеопамять или системная память, в сигналы, которые интерпретируются и отображаются дисплеем. Сигналы отображения, производимые устройством отображения, могут проходить через различные управляющие устройства перед тем, как будут интерпретированы и затем отображены на дисплее 517.

Интерфейс 518 шины может позволить сообщаться GMCH 508 с узлом 520 управления вводом/выводом (ICH). ICH 520 может обеспечивать интерфейс для устройств ввода/вывода, которые сообщаются с вычислительной системой 500. ICH 520 может сообщаться с шиной 522 через периферийный мост (или контроллер) 524, такой как мост межсоединения периферийных компонентов (PCI), контроллер универсальной последовательной шины (USB) или другие типы периферийных мостов или контроллеров. Мост 524 может обеспечивать канал передачи данных между CPU 502 и периферийными устройствами. Могут использоваться другие типы топологий. Также с ICH 520 может сообщаться несколько шин, например через несколько мостов или контроллеров. Более того, периферийные устройства, подсоединенные к ICH 520, могут включать в себя в различных вариантах осуществления изобретения жесткие диски на интерфейсной шине накопителей (IDE) или жесткие диски со скази-интерфейсом (SCSI), USB порт(ы), клавиатуру, мышь, параллельный(ые) порт(ы), последовательный(ые) порт(ы), дисковод(ы) для гибких дисков, поддержку цифрового вывода (например, интерфейс цифрового видео (DVI)) или другие устройства.

Шина 522 может сообщаться со звуковым устройством 526, одним или несколькими дисковыми накопителями 528 и сетевым интерфейсным устройством 530 (которое соединено с компьютерной сетью 503, например, через проводной или беспроводной интерфейс). Как показано, сетевое интерфейсное устройство 530 может быть соединено с антенной 531, чтобы осуществлять беспроводную связь с сетью 503 (например, через интерфейс 802.11 Института инженеров по электротехнике и радиоэлектронике (IEEE) (включая IEEE 802.11la/b/g/n, и т.д.), интерфейс сотовой связи, 3G, 5G, LTE и т.д.). К шине 522 могут присоединяться другие устройства. Также, в некоторых вариантах осуществления изобретения с GMCH 508 могут сообщаться различные компоненты (такие как сетевое интерфейсное устройство 530). В дополнение, процессор 502 и МСН 508 могут быть скомбинированы в единой микросхеме. Более того, в других вариантах осуществления изобретения графический ускоритель 516 может входить в состав GMCH 508.

Более того, вычислительная система 500 может включать в себя энергозависимую и/или энергонезависимую память (или запоминающее устройство). Например, энергонезависимая память может включать один или более из следующих элементов: постоянное запоминающее устройство (ROM), программируемое постоянное запоминающее устройство (PROM), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), дисковый накопитель (например, 528), гибкий диск, компакт-диск (CD-ROM), компакт-диск формата DVD, флеш-память, магнитооптический диск или другие типы энергонезависимых машинных носителей, способных хранить электронные данные (например, включая инструкции).

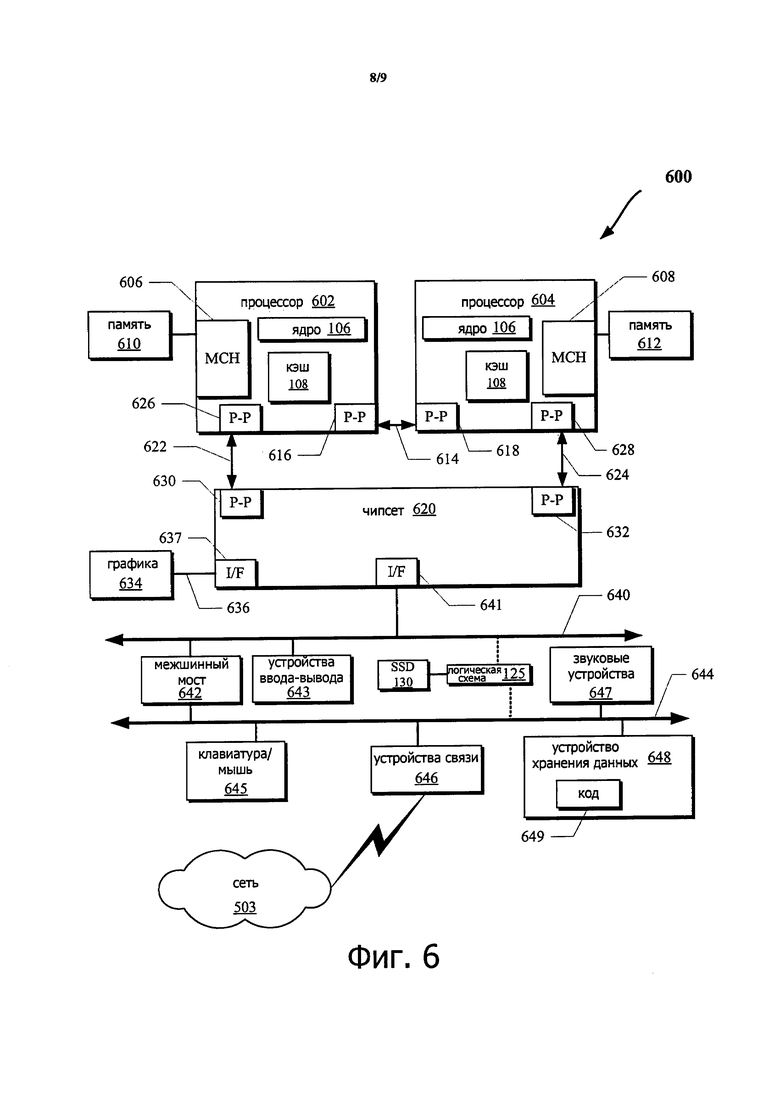

На фиг. 6 показана вычислительная система 600, выполненная в конфигурации "точка-точка" в соответствии с вариантом осуществления изобретения. В частности, на фиг. 6 показана система, в которой процессоры, память и устройства ввода/вывода соединены между собой посредством нескольких интерфейсов "точка-точка". Действия, обсуждавшиеся со ссылкой на фиг. 1-5, могут быть выполнены одним или несколькими компонентами системы 600.

Как показано на фиг. 6, система 600 может включать в себя несколько процессоров, из которых для ясности показано только два, а именно, процессоры 602 и 604. Каждый процессор 602 и 604 может включать в себя локальный контроллер-концентратор 606 и 608 памяти (МСН), чтобы можно было осуществлять связь с памятью 610 и 612. Память 610 и/или 612 может хранить различные данные, такие как обсуждались со ссылкой на память 114 на фиг. 1 и/или 5. Также, в некоторых вариантах осуществления МСН 606 и 608 может включать в себя контроллер 120 памяти. Более того, система 600 включает в себя логическую схему 125 и SSD 130 (которые в различных вариантах осуществления могут быть соединены с системой 600 через шину 640/644, как показано, через другие соединения "точка-точка" с процессором 602/604 или чипсетом 620, где логическая схема 125 входит в чипсет 620 и т.д.).

В варианте осуществления процессоры 602 и 604 могут представлять собой один из процессоров 502, обсуждавшихся со ссылкой на фиг. 5. Процессоры 602 и 604 могут обмениваться данными через интерфейс 614 "точка-точка" (PtP), используя схемы 616 и 618 PtP интерфейса соответственно. Также, каждый процессор 602 и 604 может обмениваться данными с чипсетом 620 через отдельные PtP интерфейсы 622 и 624, используя схемы 626, 628, 630 и 632 интерфейса "точка-точка". Чипсет 620 также может обмениваться данными с высокопроизводительной графической схемой 634 через интерфейс 636 высокопроизводительной графики, например, используя схему 637 PtP интерфейса. Как обсуждалось со ссылкой на фиг. 5, в некоторых вариантах осуществления графический интерфейс 636 может быть соединен с устройством отображения (например, с дисплеем 517).

Как показано на фиг. 6, одно или несколько ядер 106 и/или кэш 108 на фиг. 1 могут быть расположены в процессорах 602 и 604. Тем не менее, другие варианты осуществления могут иметься в других схемах, логических блоках или устройствах в системе 600 на фиг. 6. Более того, другие варианты осуществления могут быть распределены по нескольким схемам, логическим блокам или устройствам, показанным на фиг. 6.

Чипсет 620 может сообщаться с шиной 640, используя схему 641 PtP интерфейса. Шина 640 может иметь одно или несколько устройств, которые сообщаются с ней, таких как межшинный мост 642 и устройства 643 ввода/вывода. Через шину 644 межшинный мост 642 может сообщаться с другими устройствами, таким как клавиатура/мышь 645, устройства 646 связи (такие как модемы, сетевые интерфейсные устройства или другие устройства связи, которые могут осуществлять связь с компьютерной сетью 503, как обсуждалось со ссылкой на сетевое интерфейсное устройство 530, например, включающее в себя антенны 531), устройство ввода/вывода звука и/или устройство 648 хранения данных. Устройство 648 хранения данных может хранить код 649, который может выполняться процессорами 602 и/или 604.

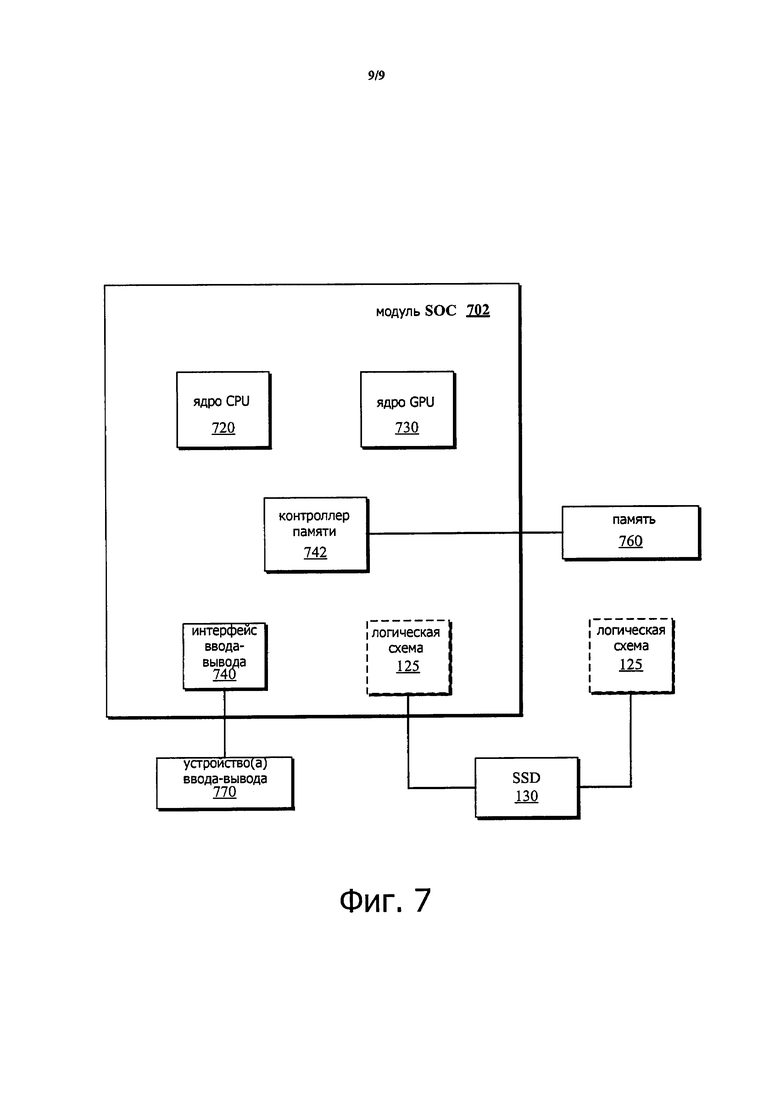

В некоторых вариантах осуществления один или несколько компонентов, обсуждавшихся в этом документе, могут быть выполнены в виде однокристальной системы (SoC). На фиг. 7 показана блок-схема модуля SoC в соответствии с вариантом осуществления. Как показано на фиг. 7, SoC 702 включает в себя одно или несколько ядер 720 центральных процессоров (CPU), одно или несколько ядер 730 графического процессора (GPU), интерфейс 740 ввода/вывода (I/O) и контроллер 742 памяти. Различные компоненты модуля SoC 702 могут быть соединены с межсоединением или шиной, как обсуждалось в этом документе со ссылкой на другие фигуры. Также, модуль SoC 702 может включать в себя больше или меньше компонентов, таких как обсуждавшиеся в этом документе со ссылкой на другие фигуры. Кроме того, каждый компонент модуля SoC 720 может включать в себя один или несколько других компонентов, например, таких как обсуждавшиеся в этом документе со ссылкой на другие фигуры. В одном варианте осуществления модуль SoC 702 (и ее компоненты) выполнен на одной или нескольких интегральных схемах, например, размещенных на одном полупроводниковом устройстве.

Как показано на фиг. 7, модуль SoC 702 соединен с памятью 760 (которая может быть аналогична или такой же, как память, обсуждавшаяся в этом документе со ссылкой на другие фигуры) через контроллер 742 памяти. В варианте осуществления память 760 (или ее часть) может быть интегрирована на модуле SoC 702.

Интерфейс 740 ввода-вывода может быть связан с одним или несколькими устройствами 770 ввода-вывода, например, посредством межсоединения и/или шины, такой как обсуждавшаяся в этом документе со ссылкой на другие фигуры. Устройство(а) 770 ввода-вывода может включать в себя одно или несколько из следующего: клавиатуру, мышь, сенсорную панель, дисплей, устройство захвата видео/изображения (такое как камера или камкордер/устройство видеозаписи), сенсорный экран, громкоговоритель и т.п. Более того, в варианте осуществления модуль SoC 702 может включать в себя/интегрировать логическую схему 125. Как вариант, логическая схема 125 может быть выполнена за пределами модуля SoC 702 (т.е. в виде отдельной логической схемы).

Следующие примеры относятся к дополнительным вариантам осуществления. Пример 1 включает в себя устройство, содержащее: логическую схему контроллера, предназначенную для управления доступом к одному или нескольким энергонезависимым устройствам; причем логическая схема контроллера предназначена для изменения рабочей частоты одного или нескольких из следующих элементов: логическая схема контроллера, шина, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, и одно или несколько энергонезависимых запоминающих устройств, причем логическая схема контроллера предназначена для изменения рабочей частоты в ответ на команду. Пример 2 включает в себя устройство примера 1, в котором одно или несколько энергонезависимых запоминающих устройств могут представлять собой одно или несколько из следующего: твердотельное запоминающее устройство, память на фазовых переходах, 3D (3-мерная) координатная память, резистивная память произвольного доступа и оперативная память произвольного доступа на основе переноса спинового момента. Пример 3 включает в себя устройство примера 1, в котором команда представляет собой команду Smart Command Transport. Пример 4 включает в себя устройство примера 1, в котором команду выдают во время работы, чтобы вызвать изменение без перезагрузки системы или операционной системы. Пример 5 включает в себя устройство примера 1, в котором логическая схема контроллера не должна вызывать изменение в ответ на команду блокировки. Пример 6 включает в себя устройство примера 1, в котором логическая схема контроллера не должна вызывать изменение в ответ на значение бита статуса блокировки. Пример 7 включает в себя устройство примера 1, в котором логическая схема контроллера должна вызывать сброс системы в ответ на определение нестабильных рабочих условий, связанных с одним или несколькими энергонезависимыми запоминающими устройствами. Пример 8 включает в себя устройство примера 1, в котором команду выдают посредством пользовательского интерфейса или автоматизированного программного приложения. Пример 9 включает в себя устройство примера 1, в котором одно или несколько энергонезависимых запоминающих устройств выполнены на одной и той же интегральной схеме. Пример 10 включает в себя устройство примера 1, в котором одна или несколько логических схем контроллера, одно или несколько энергонезависимых запоминающих устройств и ядро процессора выполнены на одной и той же интегральной схеме. Пример 11 включает в себя устройство примера 1, в котором контроллер памяти содержит логическую схему контроллера.

Пример 12 включает в себя способ, содержащий следующее: управляют доступом к одному или нескольким энергонезависимым запоминающим устройствам посредством логической схемы контроллера; и изменяют рабочую частоту одного или нескольких изследующих элементов: логической схемы контроллера, шины, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, и одного или нескольких энергонезависимых запоминающих устройств на логической схеме контроллера, причем логическая схема контроллера вызывает изменение рабочей частоты в ответ на команду. Пример 13 включает в себя способ примера 12, в котором одно или несколько энергонезависимых запоминающих устройств представляют собой одно или несколько из следующего: твердотельное запоминающее устройство, память на фазовых переходах, 3D (3-мерная) координатная память, резистивная память произвольного доступа и оперативная память произвольного доступа на основе переноса спинового момента. Пример 14 включает в себя способ примера 12, в котором команда представляет собой команду Smart Command Transport. Пример 15 включает в себя способ примера 12, дополнительно содержащий следующее: выдают команду во время работы, чтобы вызвать изменение без перезагрузки системы или операционной системы. Пример 16 включает в себя способ примера 12, дополнительно содержащий следующее: логическая схема контроллера не вызывает изменение в ответ на команду блокировки. Пример 17 включает в себя способ примера 12, дополнительно содержащий следующее: логическая схема контроллера не вызывает изменение в ответ на значение бита статуса блокировки. Пример 18 включает в себя способ примера 12, дополнительно содержащий следующее: логическая схема контроллера вызывает сброс системы в ответ на определение нестабильных рабочих условий, связанных с одним или несколькими энергонезависимыми запоминающими устройствами. Пример 19 включает в себя способ примера 12, дополнительно содержащий следующее: выдают команду посредством пользовательского интерфейса или автоматизированного программного приложения.

Пример 20 включает в себя систему, содержащую следующее: одно или несколько энергонезависимых запоминающих устройств; и по меньшей мере одно процессорное ядро для доступа к одному или нескольким энергонезависимым запоминающим устройствам посредством логической схемы контроллера, причем логическая схема контроллера предназначена для изменения рабочей частоты одного или нескольких из следующих элементов: логическая схема контроллера, шина, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, и одно или несколько энергонезависимых запоминающих устройств, причем логическая схема контроллера предназначена для изменения рабочей частоты в ответ на команду. Пример 21 включает в себя систему примера 20, в которой одно или несколько энергонезависимых запоминающих устройств могут представлять собой одно или несколько из следующего: твердотельное запоминающее устройство, память на фазовых переходах, 3D (3-мерная) координатная память, резистивная память произвольного доступа и оперативная память произвольного доступа на основе переноса спинового момента. Пример 22 включает в себя систему примера 20, в которой команда представляет собой команду Smart Command Transport. Пример 23 включает в себя систему примера 20, в которой команду выдают во время работы, чтобы вызвать изменение без перезагрузки системы или операционной системы. Пример 24 включает в себя систему примера 20, в которой одна или несколько логических схем контроллера, одно или несколько энергонезависимых запоминающих устройств и по меньшей мере одно ядро процессора выполнены на одной и той же интегральной схеме. Пример 25 включает в себя систему примера 20, дополнительно содержащую сенсорный экран, предназначенный для отображения данных, хранящихся в одном или нескольких энергонезависимых запоминающих устройствах.

Пример 26 включает в себя устройство для оперативного регулирования производительности твердотельных запоминающих устройств, причем устройство содержит: средство для управления доступом к одному или нескольким энергонезависимым запоминающим устройствам, соединенным с логической схемой контроллера; и средство для изменения рабочей частоты одного или нескольких из следующих элементов: логической схемы контроллера, шины, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, и одного или нескольких энергонезависимых запоминающих устройств на логической схеме контроллера, причем логическая схема контроллера вызывает изменение рабочей частоты в ответ на команду. Пример 27 включает в себя устройство примера 26, содержащее средство для выдачи команды во время работы, чтобы вызвать изменение без перезагрузки системы или операционной системы. Пример 28 включает в себя устройство примера 26, содержащее средство, предназначенное для того, чтобы логическая схема контроллера не вызывала изменения в ответ на команду блокировки. Пример 29 включает в себя устройство примера 26, содержащее средство, предназначенное для того, чтобы логическая схема контроллера не вызывала изменения в ответ на значения бита статуса блокировки.

Пример 30 включает в себя машинный носитель, содержащий одну или несколько инструкций, при выполнении которых процессором выполняется конфигурация процессора так, чтобы он выполнял одно или несколько действий любого из примеров 12-19.

В различных вариантах осуществления изобретения, обсуждаемые в этом документе действия, например, со ссылкой на фиг. 1-7, могут быть реализованы в виде аппаратного обеспечения (например, схемы), программного обеспечения, микропрограммного обеспечения, микрокода или их сочетания, которое может быть выполнено в виде компьютерного программного продукта, например, включающего в себя материальный (например, энергонезависимый) машинный или компьютерный носитель, на котором хранятся инструкции (или программные процедуры), применяемые для программирования компьютера так, чтобы он выполнял обсуждаемый в этом документе процесс. Также, термин "логика" может включать в себя, в качестве примера, программное обеспечение, аппаратное обеспечение или сочетания программного и аппаратного обеспечения. Машинный носитель может включать в себя запоминающее устройство, такое как обсуждавшиеся касательно фиг. 1-7.

Кроме того, такой материальный носитель может быть загружен в виде программного продукта, причем программа может передаваться от удаленного компьютера (например, сервера) на запрашивающий компьютер (например, клиент) при помощи сигналов передачи данных (например, на несущей волне или в другой среде распространения) через линию связи (например, шину, модем или сетевое соединение).

В спецификации ссылка на "один вариант осуществления" или "вариант осуществления" означает, что конкретный признак, структура или характеристика, описанная в связи с вариантом осуществления, может содержаться, по меньшей мере, в реализации. При появлении фразы "в одном варианте осуществления" в различных местах этой спецификации не обязательно ссылаются на один и тот же вариант осуществления.

Также в описании и формуле изобретения могут использоваться термины "связанный" и "соединенный", а также производные от них. В некоторых вариантах осуществления изобретения термин "соединенный" может использоваться для того, чтобы показать, что два или несколько элементов находятся в непосредственном физическом или электрическом контакте друг с другом. Термин "связанный" может означать, что два или более элементов находятся в непосредственном физическом или электрическом контакте. Тем не менее, термин "связанный" также может означать, что два или более элементов могут не быть в непосредственном контакте друг с другом, но все еще могут взаимодействовать или влиять друг на друга.

Таким образом, хотя варианты осуществления изобретения были описаны на языке, специфичном для структурных признаков и/или методологических действий, понятно, что сформулированная сущность может не быть ограниченной описанными специфическими признаками или действиями. Наоборот, специфические признаки и действия приведены в качестве примеров реализации сформулированной сущности.

Изобретение относится к области запоминающих устройств. Техническим результатом является изменение рабочей частоты шины, которая соединяет одно или несколько энергонезависимых запоминающих устройств. Устройство для изменения рабочей частоты элементов содержит: логическую схему контроллера, по меньшей мере частично воплощенную в аппаратном обеспечении и предназначенную для управления доступом к одному или нескольким энергонезависимым устройствам по меньшей мере частично на основании ответа от каждого из одного или нескольких энергонезависимых устройств; причем логическая схема контроллера предназначена для изменения рабочей частоты шины, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, в ответ на определение, что ответ обозначает, что каждое из одного или нескольких энергонезависимых устройств является настраиваемым, причем логическая схема контроллера предназначена для изменения рабочей частоты в ответ на команду, в которой по меньшей мере частично в ответ на команду блокировки или значение бита статуса блокировки логическая схема контроллера не должна вызывать изменение в ответ на запрос, инициированный программным обеспечением. 3 н. и 30 з.п. ф-лы, 9 ил., 1 табл.

1. Устройство для изменения рабочей частоты элементов, содержащее следующее:

логическую схему контроллера, по меньшей мере частично воплощенную в аппаратном обеспечении и предназначенную для управления доступом к одному или нескольким энергонезависимым устройствам по меньшей мере частично на основании ответа от каждого из одного или нескольких энергонезависимых устройств;

причем логическая схема контроллера предназначена для изменения рабочей частоты шины, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, в ответ на определение, что ответ обозначает, что каждое из одного или нескольких энергонезависимых устройств является настраиваемым, причем логическая схема контроллера предназначена для изменения рабочей частоты в ответ на команду,

в котором по меньшей мере частично в ответ на команду блокировки или значение бита статуса блокировки логическая схема контроллера не должна вызывать изменение в ответ на запрос, инициированный программным обеспечением.

2. Устройство по п. 1, в котором одно или несколько энергонезависимых запоминающих устройств могут представлять собой одно или несколько из следующего: твердотельное запоминающее устройство, память на фазовых переходах, 3D (3-мерная) координатная память, резистивная память произвольного доступа и оперативная память произвольного доступа на основе переноса спинового момента.

3. Устройство по п. 1, в котором команда представляет собой команду Smart Command Transport.

4. Устройство по п. 1, в котором команду выдают во время работы, чтобы вызвать изменение без перезагрузки системы или операционной системы.

5. Устройство по п. 1, в котором логическая схема контроллера должна вызывать сброс системы в ответ на определение нестабильных рабочих условий, связанных с одним или несколькими энергонезависимыми запоминающими устройствами.

6. Устройство по п. 1, в котором команду выдают посредством пользовательского интерфейса или автоматизированного программного приложения.

7. Устройство по п. 1, в котором одно или несколько энергонезависимых запоминающих устройств выполнены на одной и той же интегральной схеме.

8. Устройство по п. 1, в котором одна или несколько логических схем контроллера, одно или несколько энергонезависимых запоминающих устройств и ядро процессора выполнены на одной и той же интегральной схеме.

9. Устройство по п. 1, в котором контроллер памяти содержит логическую схему контроллера.

10. Устройство по п. 1, в котором логическая схема контроллера побуждает по меньшей мере одно из одного или нескольких энергонезависимых запоминающих устройств работать на разогнанной частоте, причем разогнанная частота представляет собой более высокую частоту, чем нормальная рабочая частота.

11. Устройство по п. 1, в котором логическая схема контроллера дополнительно изменяет рабочую частоту логической схемы контроллера или одного или нескольких из одного или нескольких энергонезависимых запоминающих устройств.

12. Устройство по п. 1, в котором логическая схема контроллера помечает как настраиваемое одно или несколько энергонезависимых запоминающих устройств на основании ответа.

13. Устройство по п. 1, дополнительно содержащее графический пользовательский интерфейс, предназначенный для отображения списка настраиваемых устройств, помеченных логической схемой контроллера на основании ответа.

14. Устройство по п. 1, дополнительно содержащее графический пользовательский интерфейс, предназначенный для дополнительного предоставления набора частот для логической схемы контроллера и текущего значения частоты логической схемы контроллера.

15. Устройство по п. 1, дополнительно содержащее графический пользовательский интерфейс, предназначенный для дополнительного предоставления набора пределов энергопотребления для логической схемы контроллера.

16. Устройство по п. 1, дополнительно содержащее графический пользовательский интерфейс, предназначенный для дополнительного предоставления гистограммы частоты контроллера для логической схемы контроллера.

17. Устройство по п. 1, в котором команду принимают от графического пользовательского интерфейса, при этом графический пользовательский интерфейс предназначен для предоставления установленной по умолчанию и предлагаемой частоты контроллера и значений режима энергопотребления для логической схемы контроллера.

18. Способ изменения рабочей частоты элементов, содержащий следующее:

управляют доступом к одному или нескольким энергонезависимым запоминающим устройствам посредством логической схемы контроллера по меньшей мере частично на основании ответа от каждого из одного или нескольких энергонезависимых устройств; и

изменяют рабочую частоту шины, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, в ответ на определение, что ответ обозначает, что каждое из одного или нескольких энергонезависимых устройств является настраиваемым,

причем логическая схема контроллера вызывает изменение рабочей частоты в ответ на команду,

в котором по меньшей мере частично в ответ на команду блокировки или значение бита статуса блокировки логическая схема контроллера не должна вызывать изменение в ответ на запрос, инициированный программным обеспечением.

19. Способ по п. 18, в котором одно или несколько энергонезависимых запоминающих устройств представляют собой одно или несколько из следующего: твердотельное запоминающее устройство, память на фазовых переходах, 3D (3-мерная) координатная память, резистивная память произвольного доступа и оперативная память произвольного доступа на основе переноса спинового момента.

20. Способ по п. 18, в котором команда представляет собой команду Smart Command Transport.

21. Способ по п. 18, дополнительно содержащий следующее: выдают команду во время работы, чтобы вызвать изменение без перезагрузки системы или операционной системы.

22. Способ по п. 18, дополнительно содержащий следующее: логическая схема контроллера не вызывает изменение в ответ на команду блокировки.

23. Способ по п. 18, дополнительно содержащий следующее: логическая схема контроллера не вызывает изменение в ответ на значение бита статуса блокировки.

24. Способ по п. 18, дополнительно содержащий следующее: логическая схема контроллера вызывает сброс системы в ответ на определение нестабильных рабочих условий, связанных с одним или несколькими энергонезависимыми запоминающими устройствами.

25. Способ по п. 18, дополнительно содержащий следующее: выдают команду посредством пользовательского интерфейса или автоматизированного программного приложения.

26. Способ по п. 18, в котором команду принимают от графического пользовательского интерфейса, при этом графический пользовательский интерфейс предназначен для предоставления установленной по умолчанию и предлагаемой частоты контроллера и значений режима энергопотребления для логической схемы контроллера.

27. Система для изменения рабочей частоты элементов, содержащая:

одно или несколько энергонезависимых запоминающий устройств; и

по меньшей мере одно процессорное ядро для доступа к одному или нескольким энергонезависимым запоминающим устройствам посредством логической схемы контроллера по меньшей мере частично на основании ответа от каждого из одного или нескольких энергонезависимых устройств;

причем логическая схема контроллера предназначена для изменения рабочей частоты шины, которая соединяет одно или несколько энергонезависимых запоминающих устройств с логической схемой контроллера, в ответ на определение, что ответ обозначает, что каждое из одного или нескольких энергонезависимых устройств является настраиваемым, причем логическая схема контроллера предназначена для изменения рабочей частоты в ответ на команду,

в которой по меньшей мере частично в ответ на команду блокировки или значение бита статуса блокировки логическая схема контроллера не должна вызывать изменение в ответ на запрос, инициированный программным обеспечением.

28. Система по п. 27, в которой одно или несколько энергонезависимых запоминающих устройств могут представлять собой одно или несколько из следующего: твердотельное запоминающее устройство, память на фазовых переходах, 3D (3-мерная) координатная память, резистивная память произвольного доступа и оперативная память произвольного доступа на основе переноса спинового момента.

29. Система по п. 27, в которой команда представляет собой команду Smart Command Transport.

30. Система по п. 27, в которой команду выдают во время работы, чтобы вызвать изменение без перезагрузки системы или операционной системы.

31. Система по п. 27, в которой одна или несколько логических схем контроллера, одно или несколько энергонезависимых запоминающих устройств и по меньшей мере одно ядро процессора выполнены на одной и той же интегральной схеме.

32. Система по п. 27, дополнительно содержащая сенсорный экран, предназначенный для отображения данных, хранящихся в одном или нескольких энергонезависимых запоминающих устройствах.

33. Система по п. 27, в которой команду принимают от графического пользовательского интерфейса, при этом графический пользовательский интерфейс предназначен для предоставления установленной по умолчанию и предлагаемой частоты контроллера и значений режима энергопотребления для логической схемы контроллера.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| US 7382366 B1, 03.06.2008 | |||

| СПОСОБ ОПТИМИЗАЦИИ ТВЕРДОТЕЛЬНОГО НАКОПИТЕЛЯ И ОПТИМИЗАТОР | 2008 |

|

RU2479013C2 |

Авторы

Даты

2017-07-04—Публикация

2014-05-27—Подача