ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Изобретение относится к устройству для передачи широковещательных сигналов, устройству для приема широковещательных сигналов и способам передачи и приема широковещательных сигналов.

УРОВЕНЬ ТЕХНИКИ

Поскольку эпоха передачи аналогового широковещательного сигнала подходит к концу, разрабатываются различные технологии передачи/приема цифровых широковещательных сигналов. Цифровой широковещательный сигнал может включать в себя больший объем видео/аудиоданных, чем аналоговый широковещательный сигнал, и дополнительно включают в себя различные типы дополнительных данных помимо видео/аудиоданных.

Таким образом, цифровая широковещательная система может обеспечивать изображения HD (высокой четкости), многоканальный аудиосигнал и различные дополнительные услуги. Однако эффективность передачи данных для передачи больших объемов данных, надежность сетей передачи/приема и гибкость сети с учетом того, что мобильное приемное оборудование нуждается в усовершенствовании для цифрового широковещания.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Техническая задача

Соответственно, настоящее изобретение относится к устройству для передачи широковещательных сигналов и к устройству для приема широковещательных сигналов для перспективных широковещательных услуг и к способам передачи и приема широковещательных сигналов для перспективных широковещательных услуг.

Задачей настоящего изобретения является обеспечение устройства и способа передачи широковещательных сигналов для мультиплексирования данных системы широковещательной передачи/приема, обеспечивающей две или более разных широковещательных услуг во временной области и передачи мультиплексированных данных в одной и той же полосе RF сигнала и устройства и способа приема соответствующих широковещательных сигналов.

Другой задачей настоящего изобретения является обеспечение устройства для передачи широковещательных сигналов, устройства для приема широковещательных сигналов и способов передачи и приема широковещательных сигналов для классификации данных, соответствующих услугам, по компонентам, передачи данных, соответствующих каждому компоненту, в качестве конвейера данных, приема и обработки данных.

Еще одной задачей настоящего изобретения является обеспечение устройства для передачи широковещательных сигналов, устройства для приема широковещательных сигналов и способов передачи и приема широковещательных сигналов для сигнализации информации сигнализации, необходимой для обеспечения широковещательных сигналов.

РЕШЕНИЕ ЗАДАЧИ

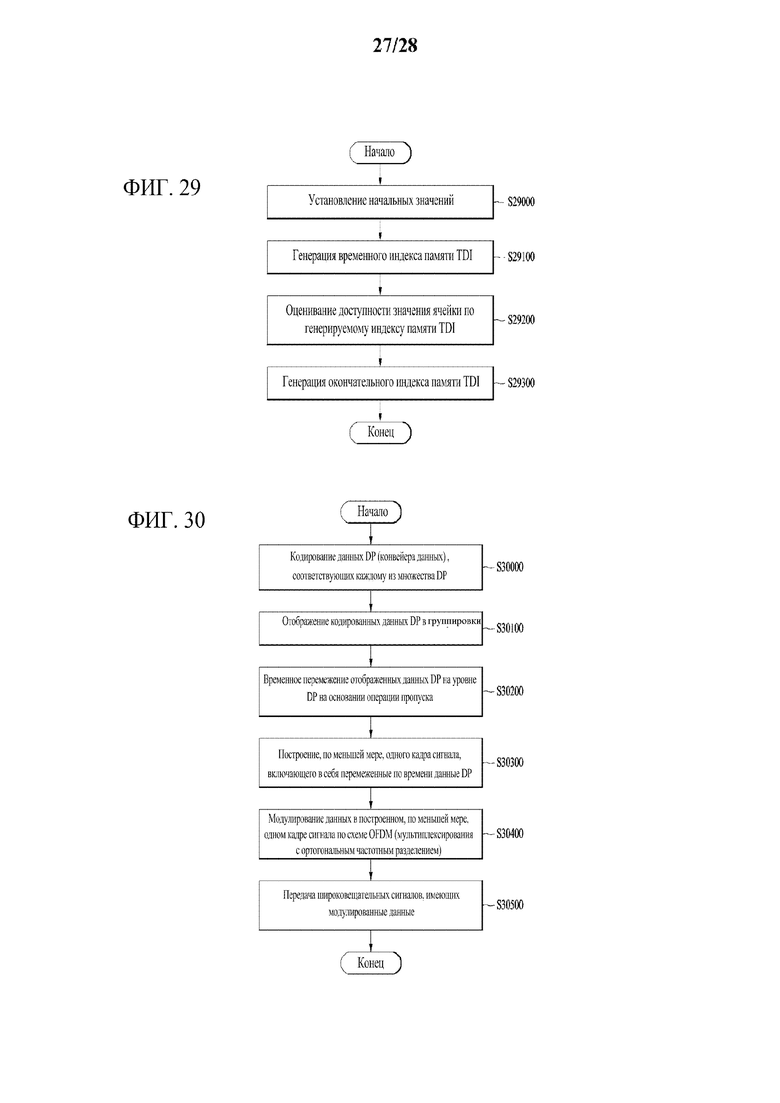

Для достижения поставленной цели и других преимуществ и в соответствии с целью изобретения реализованный и описанный здесь в общих чертах способ передачи широковещательных сигналов содержит кодирование данных DP (конвейера данных), соответствующих каждому из множества DP, причем каждый из множества DP несет, по меньшей мере, один компонент услуги, отображение кодированных данных DP в группировки (группы), временное перемежение отображенных данных DP на уровне DP путем пропуска ячеек, имеющих нулевые значения данных DP, построение, по меньшей мере, одного кадра сигнала, включающего в себя перемеженные по времени данные DP, модулирование данных в построенном, по меньшей мере, одном кадре сигнала по схеме OFDM (мультиплексирования с ортогональным частотным разделением) и передачу широковещательных сигналов, имеющих модулированные данные.

ПОЛЕЗНЫЕ ЭФФЕКТЫ ИЗОБРЕТЕНИЯ

Настоящее изобретение позволяет обрабатывать данные согласно характеристикам услуги для управления QoS для каждой услуги или компонента услуги, таким образом, обеспечивая различные широковещательные услуги.

Настоящее изобретение позволяет достичь гибкости передачи за счет передачи различных широковещательных услуг в одной и той же полосе RF сигнала.

Настоящее изобретение позволяет повысить эффективность передачи данных и повысить надежность передачи/приема широковещательных сигналов с использованием системы MIMO.

Согласно настоящему изобретению можно обеспечить способы передачи и приема широковещательного сигнала и устройство, способное принимать цифровые широковещательные сигналы без ошибок даже с мобильным приемным оборудованием или в окружении в помещении.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

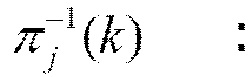

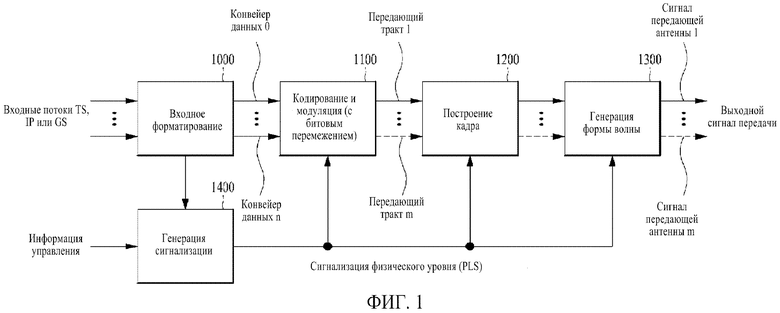

Фиг. 1 демонстрирует структуру устройства для передачи широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения.

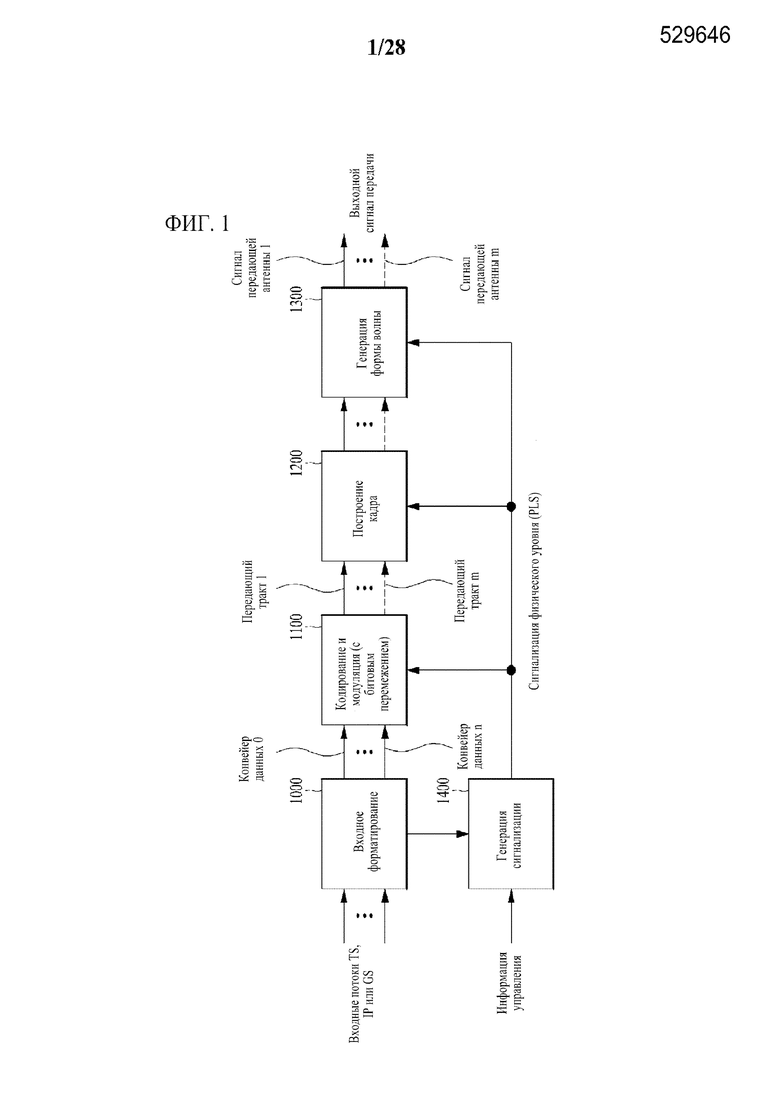

Фиг. 2 демонстрирует модуль входного форматирования согласно варианту осуществления настоящего изобретения.

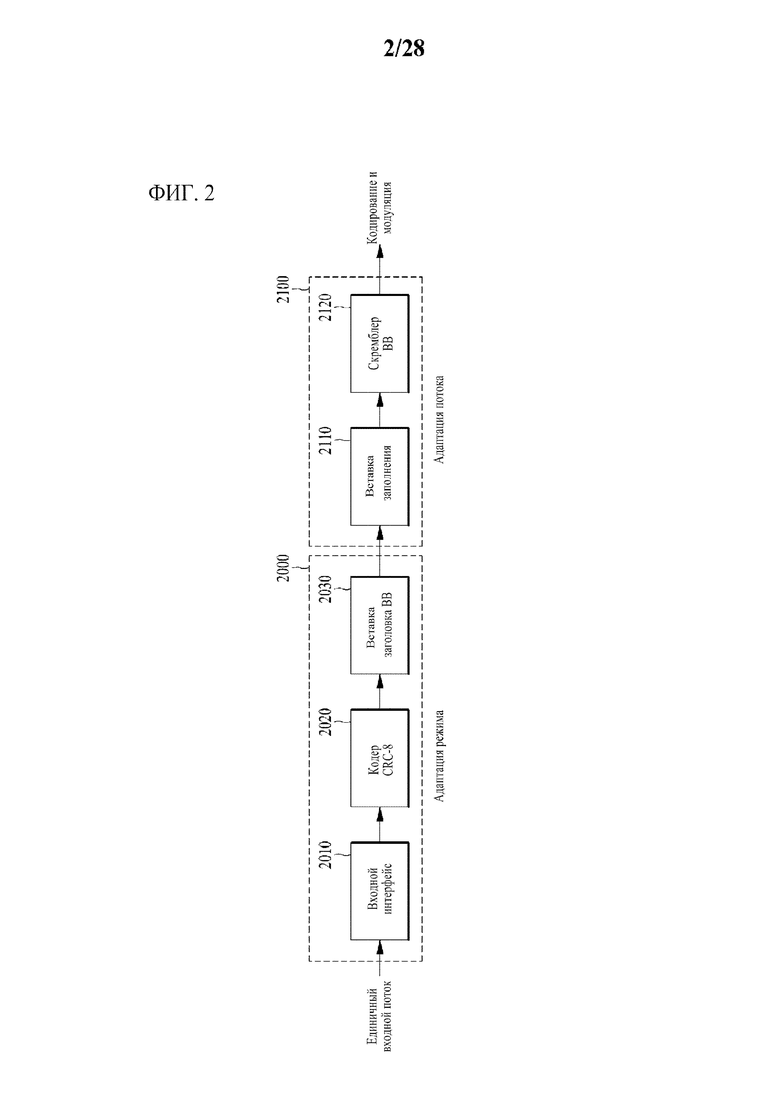

Фиг. 3 демонстрирует модуль входного форматирования согласно другому варианту осуществления настоящего изобретения.

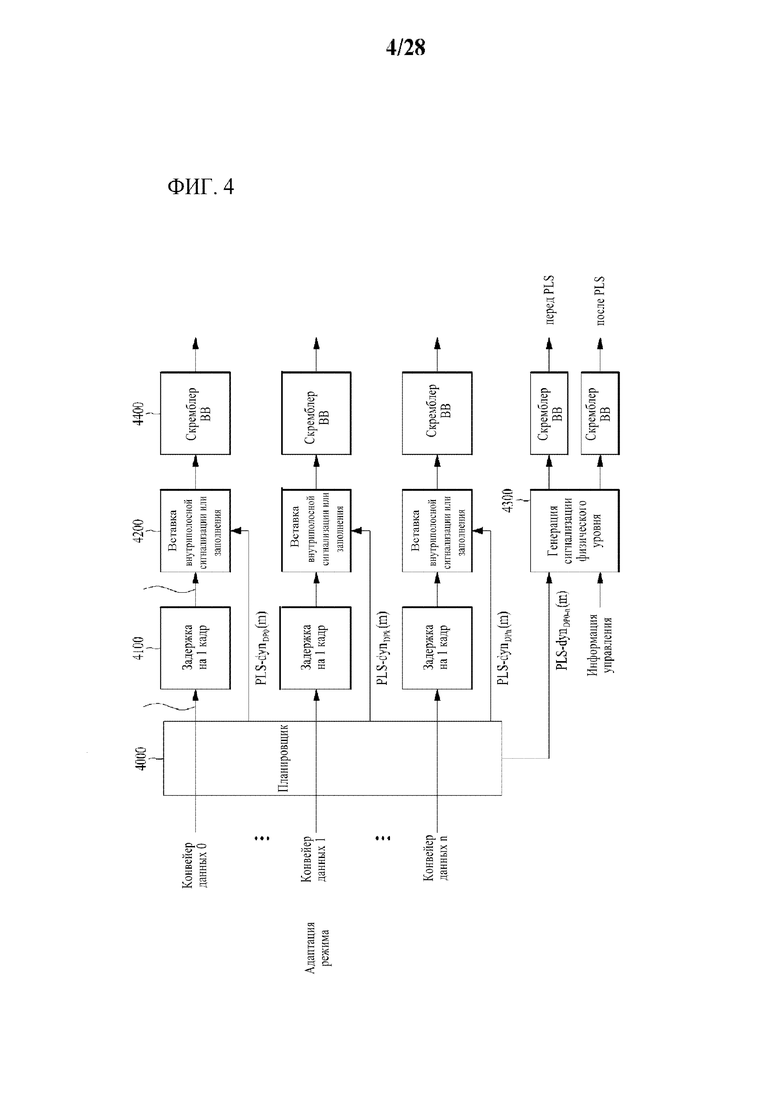

Фиг. 4 демонстрирует модуль входного форматирования согласно другому варианту осуществления настоящего изобретения.

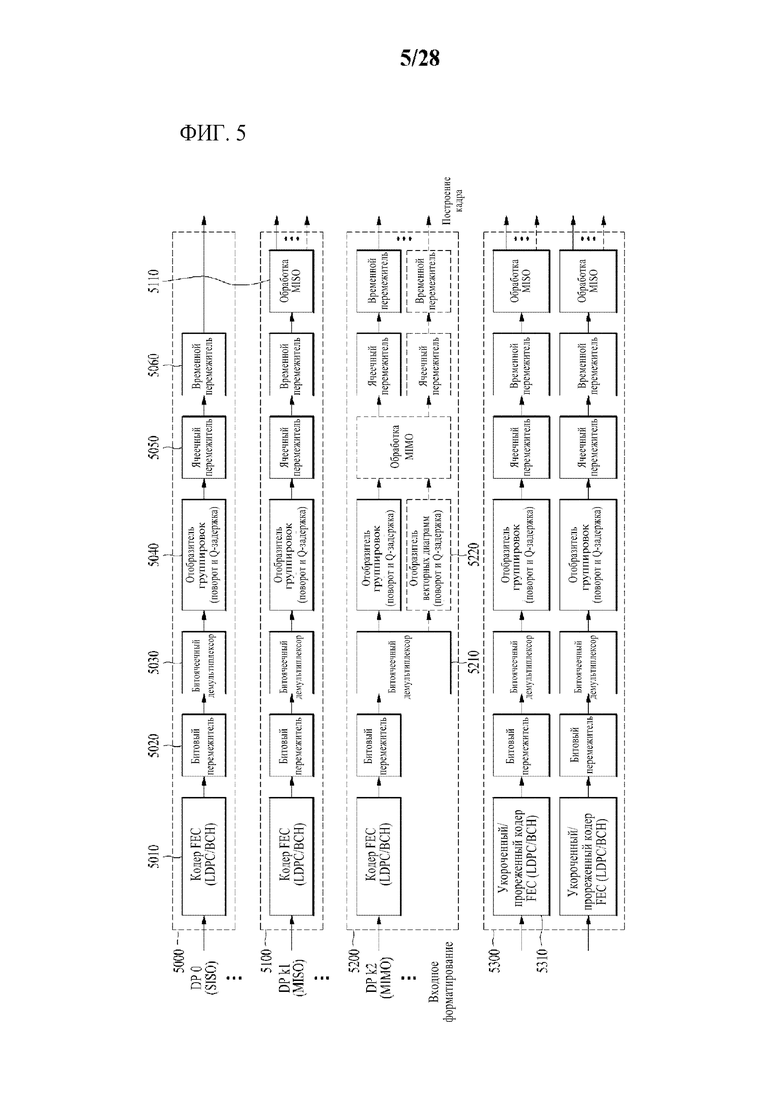

Фиг. 5 демонстрирует модуль кодирования и модуляции согласно варианту осуществления настоящего изобретения.

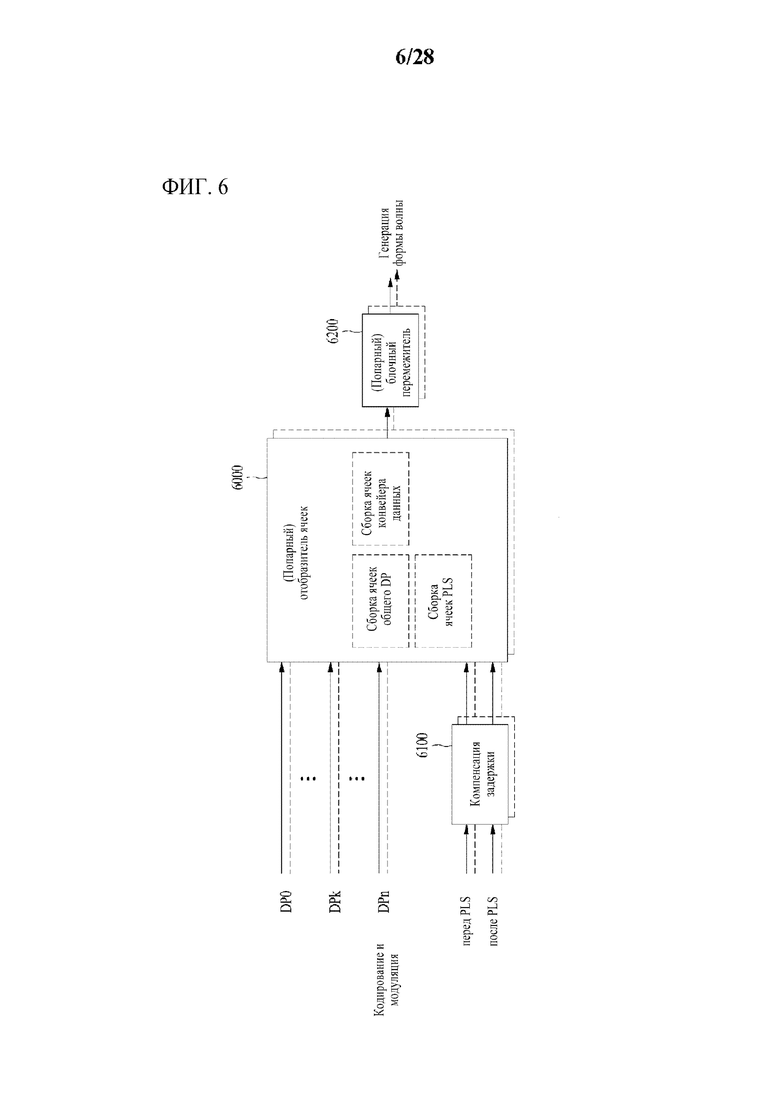

Фиг. 6 демонстрирует модуль построения кадра согласно варианту осуществления настоящего изобретения.

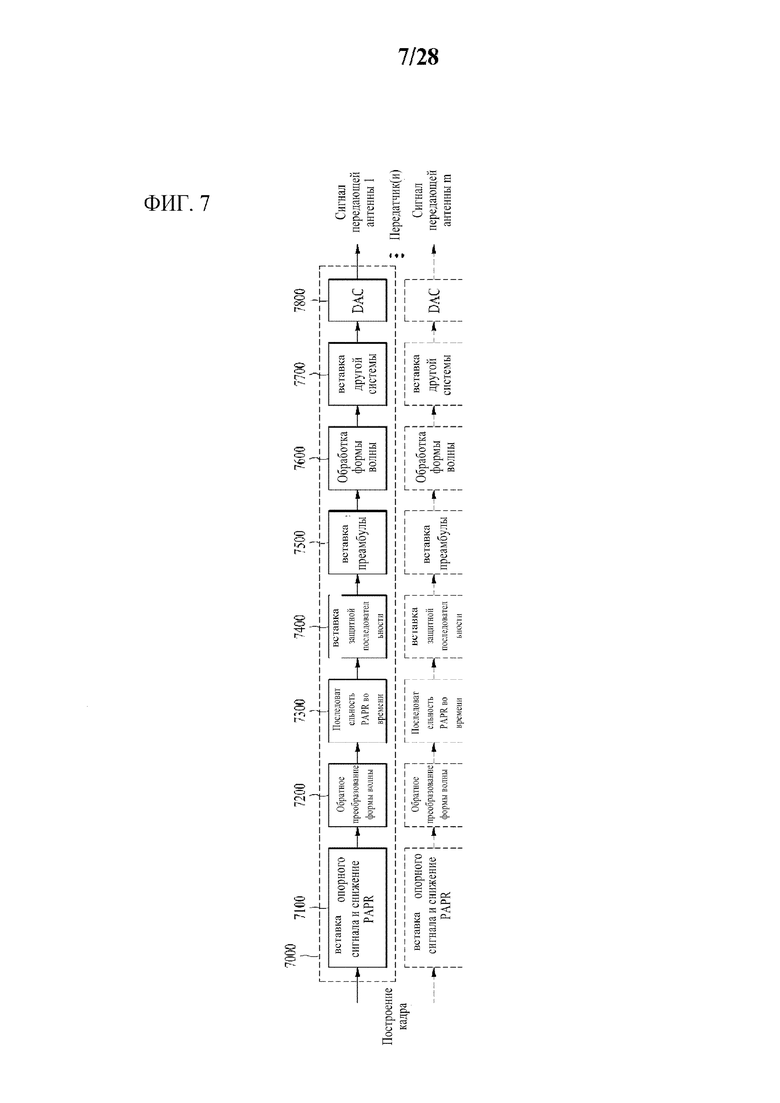

Фиг. 7 демонстрирует модуль генерации формы волны согласно варианту осуществления настоящего изобретения.

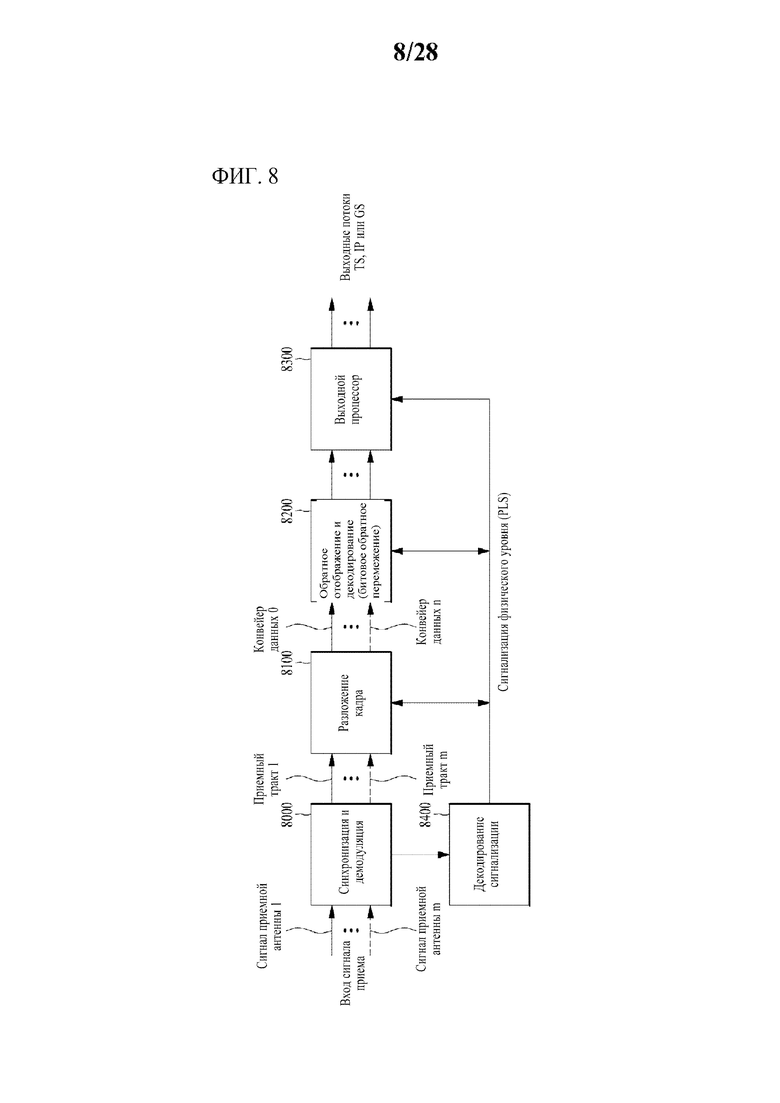

Фиг. 8 демонстрирует структуру устройства для приема широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения.

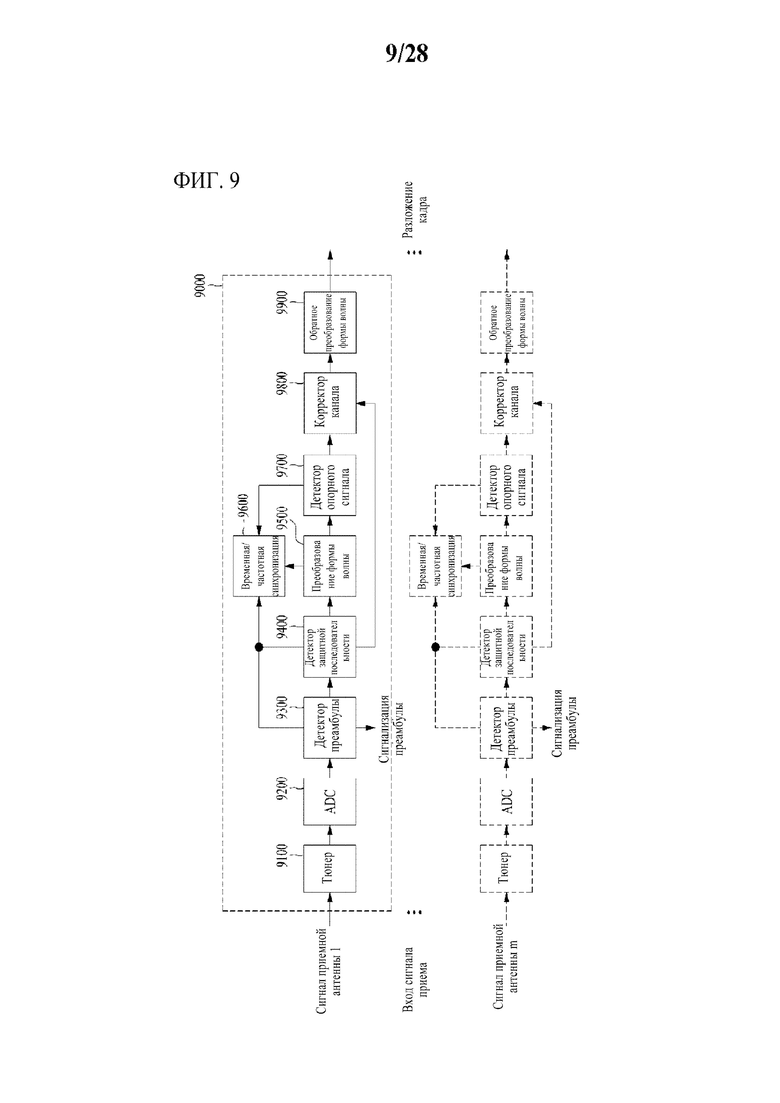

Фиг. 9 демонстрирует модуль синхронизации и демодуляции согласно варианту осуществления настоящего изобретения.

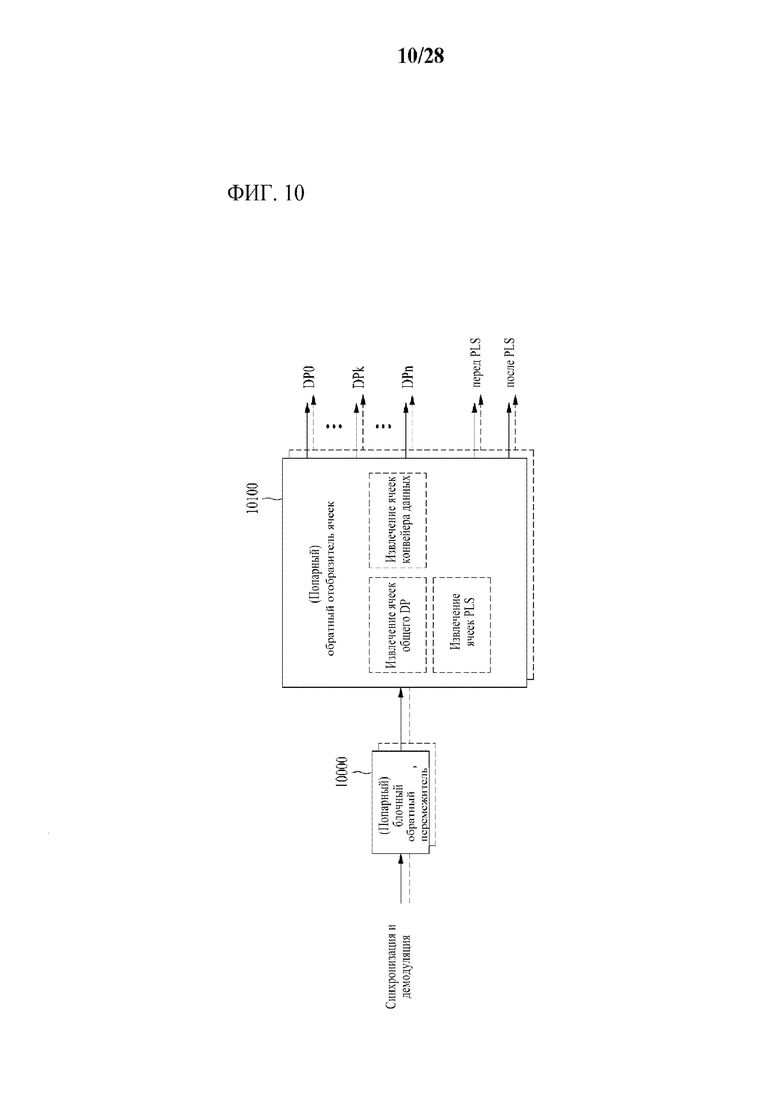

Фиг. 10 демонстрирует модуль синтаксического анализа кадра согласно варианту осуществления настоящего изобретения.

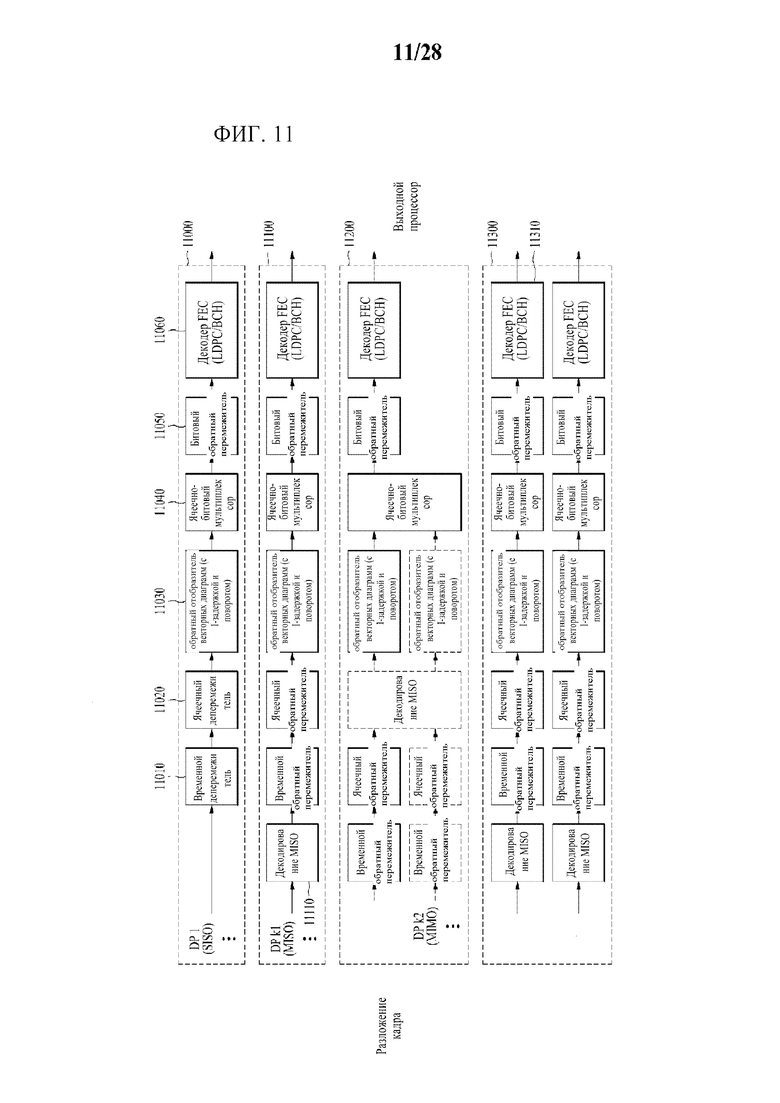

Фиг. 11 демонстрирует модуль обратного отображения и декодирования согласно варианту осуществления настоящего изобретения.

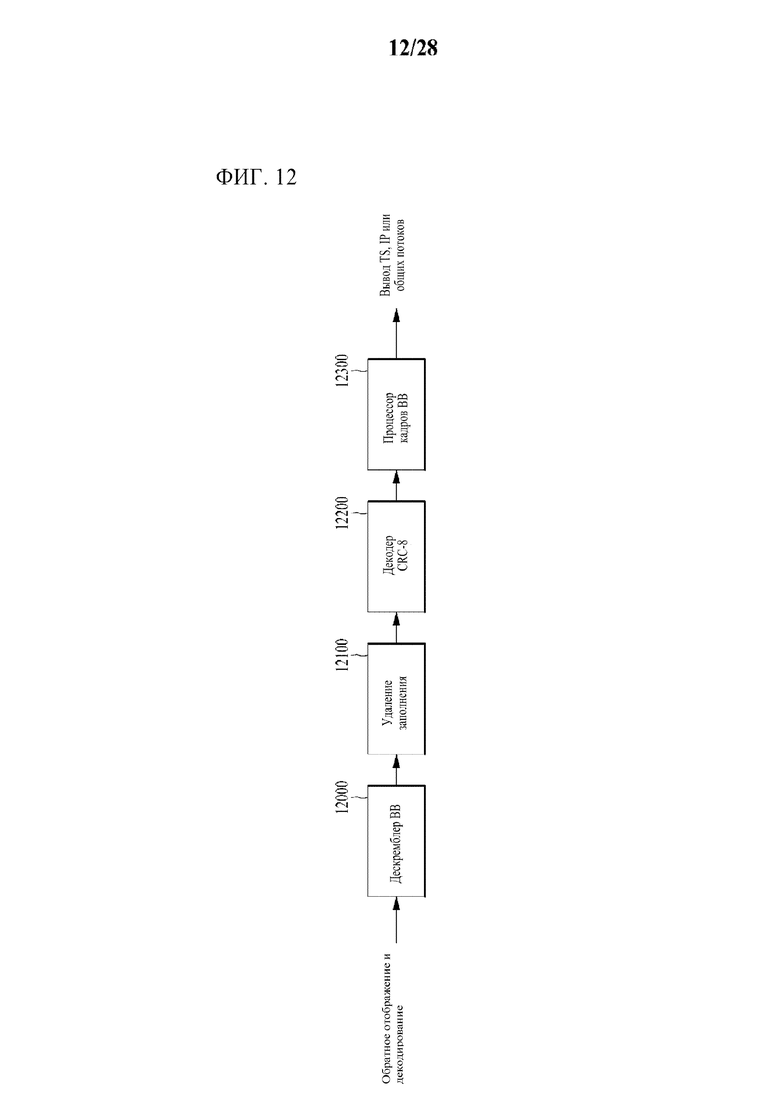

Фиг. 12 демонстрирует выходной процессор согласно варианту осуществления настоящего изобретения.

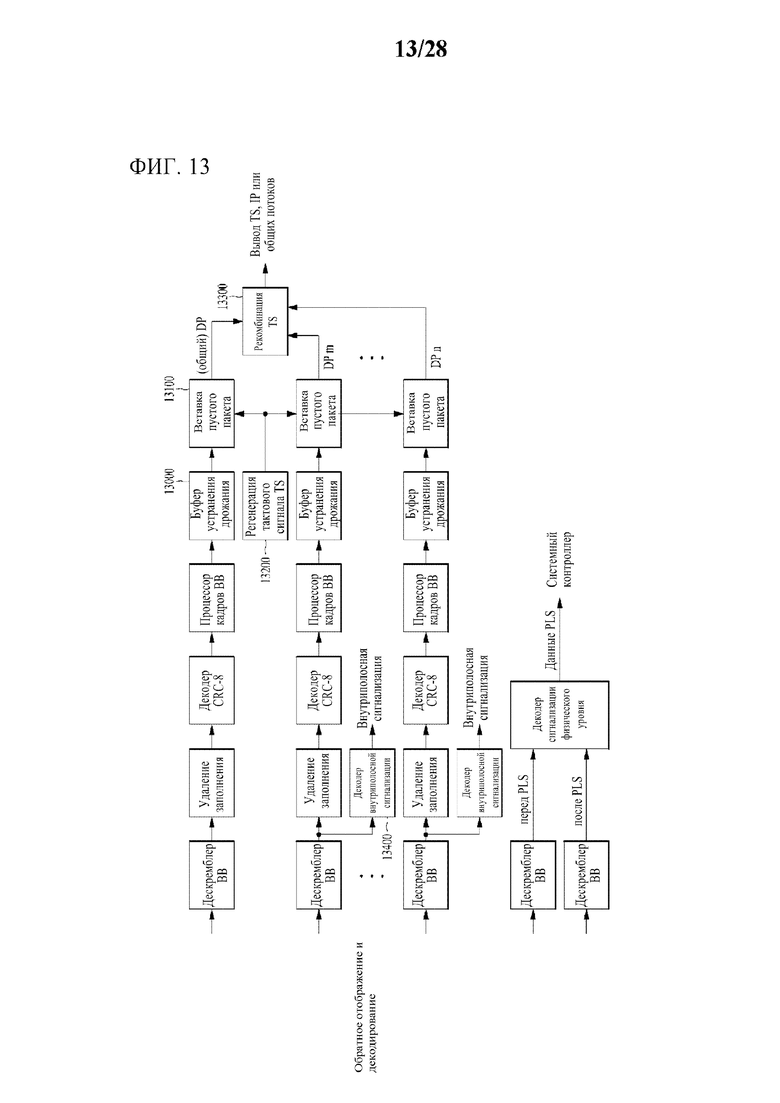

Фиг. 13 демонстрирует выходной процессор согласно другому варианту осуществления настоящего изобретения.

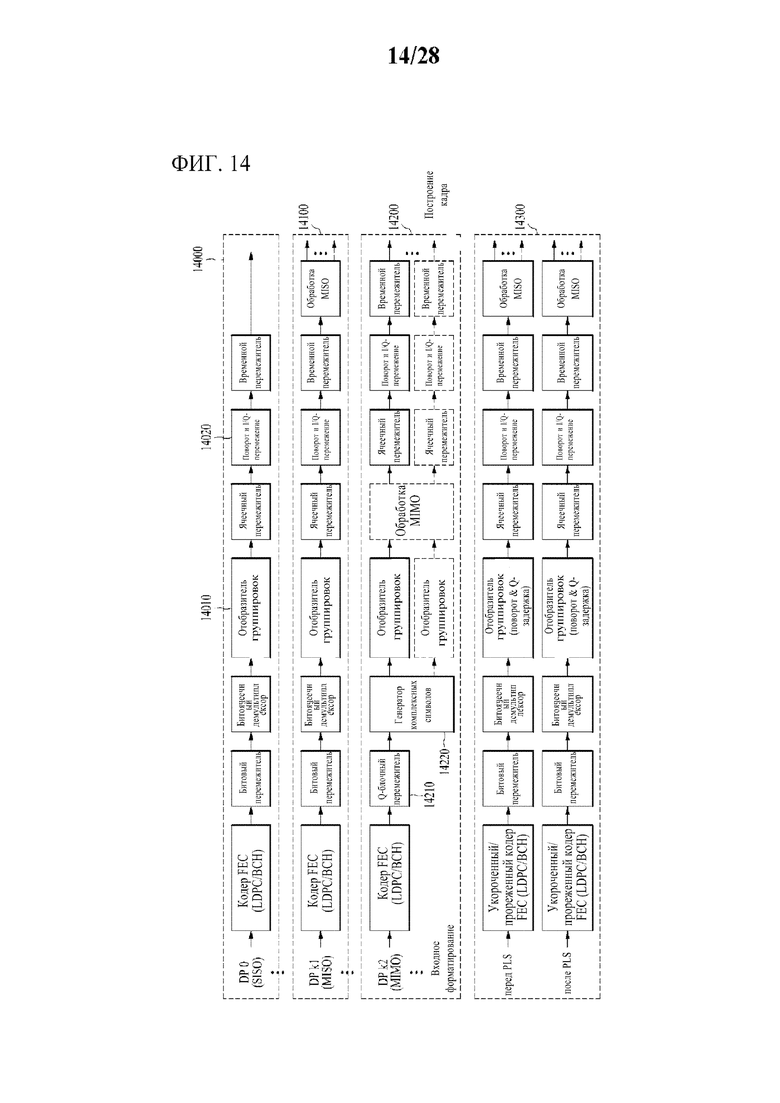

Фиг. 14 демонстрирует модуль кодирования и модуляции согласно другому варианту осуществления настоящего изобретения.

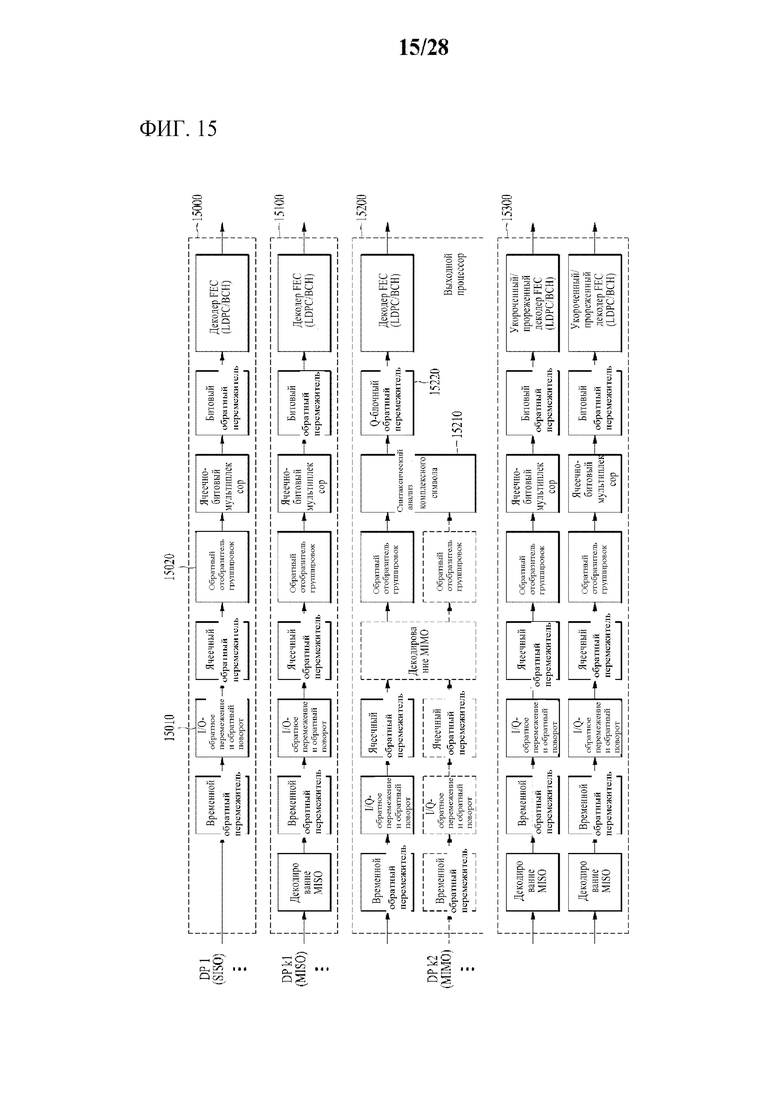

Фиг. 15 демонстрирует модуль обратного отображения и декодирования согласно другому варианту осуществления настоящего изобретения.

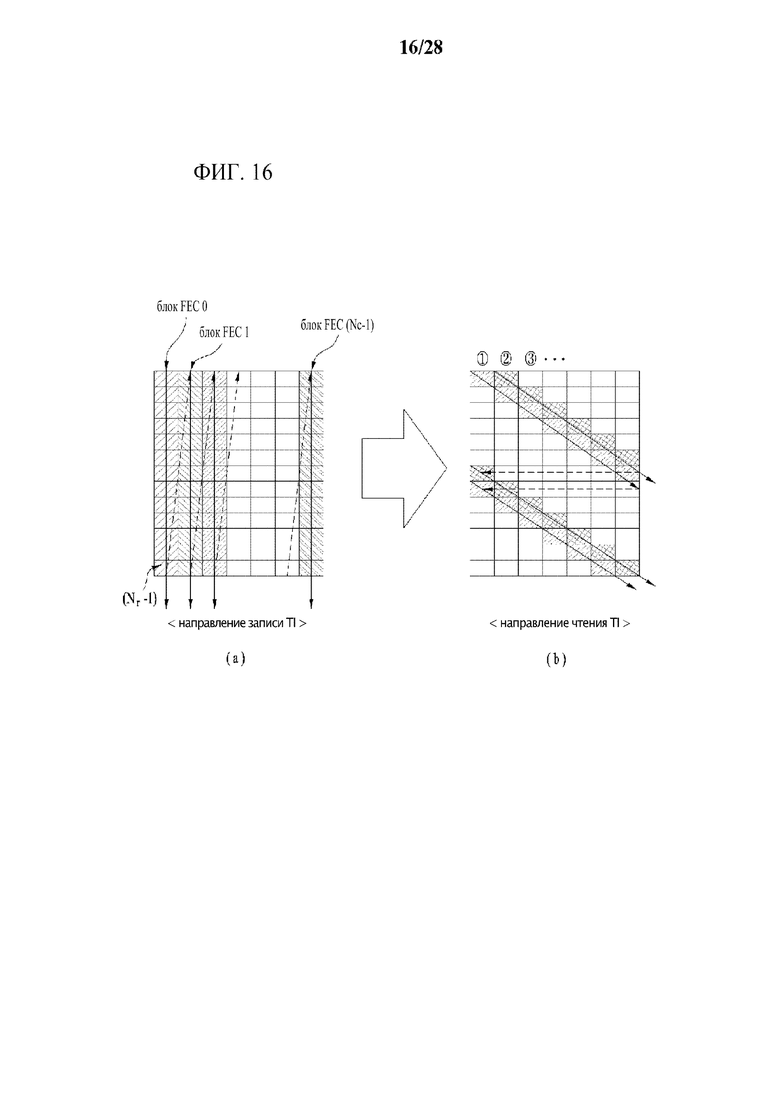

Фиг. 16 демонстрирует процесс временного перемежения согласно варианту осуществления настоящего изобретения.

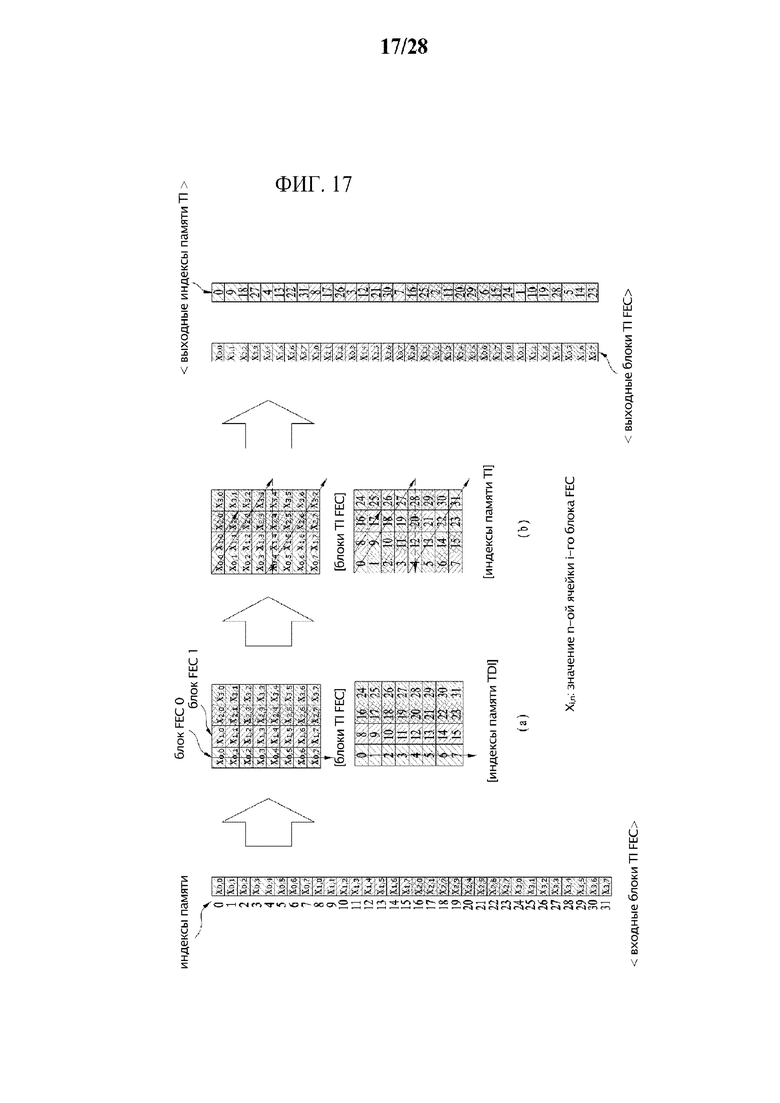

Фиг. 17 демонстрирует процесс временного перемежения согласно другому варианту осуществления настоящего изобретения.

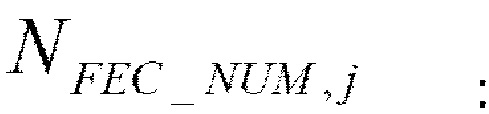

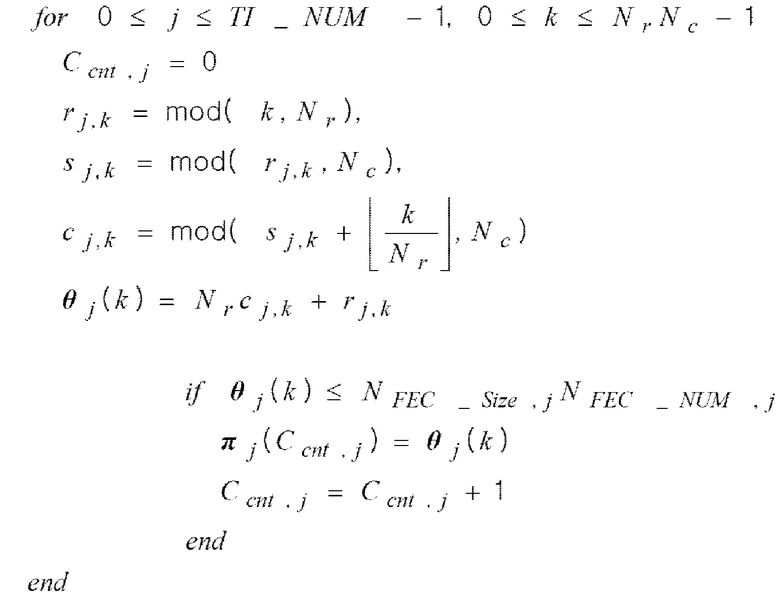

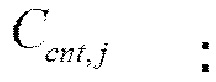

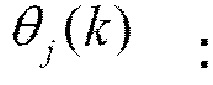

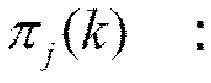

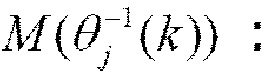

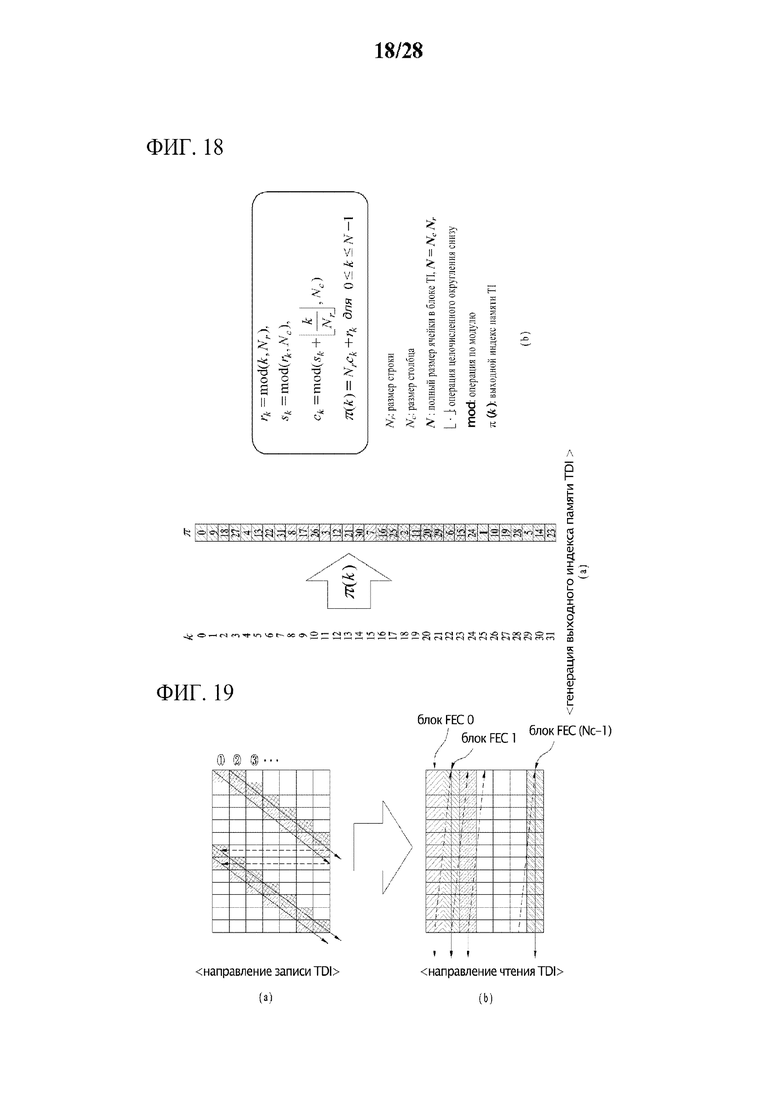

Фиг. 18 демонстрирует процесс генерации выходных индексов памяти TI согласно варианту осуществления настоящего изобретения.

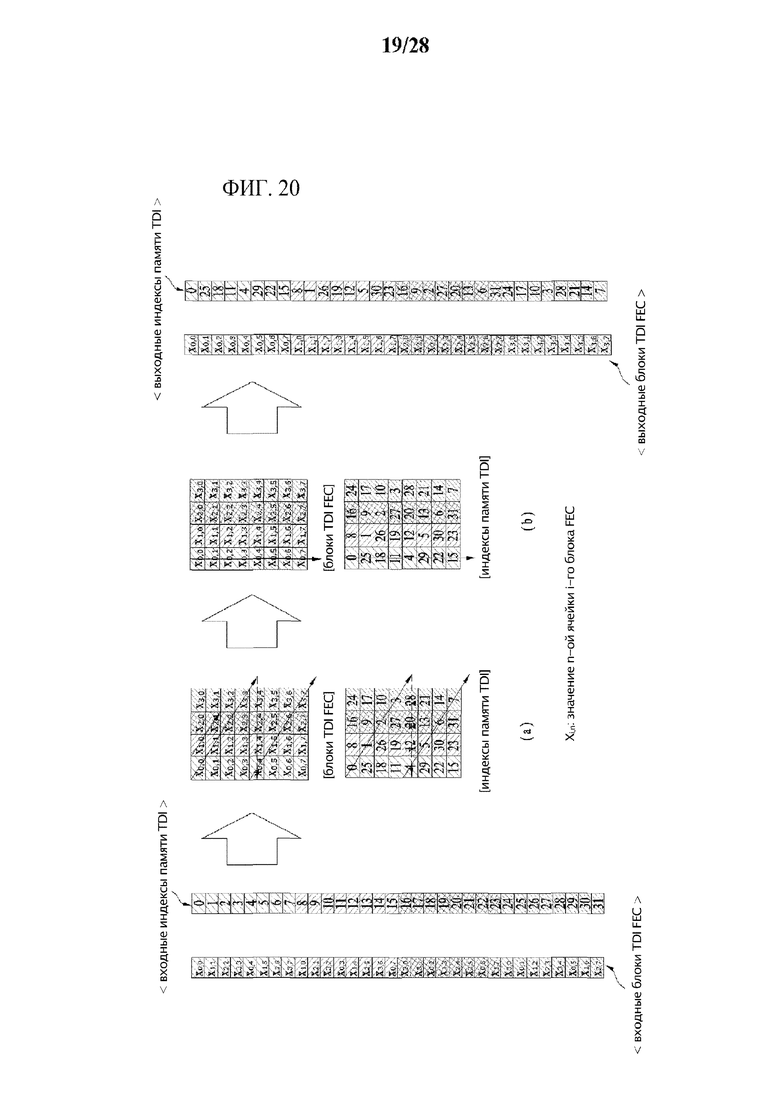

Фиг. 19 демонстрирует процесс временного обратного перемежения согласно варианту осуществления настоящего изобретения.

Фиг. 20 демонстрирует процесс временного обратного перемежения согласно другому варианту осуществления настоящего изобретения.

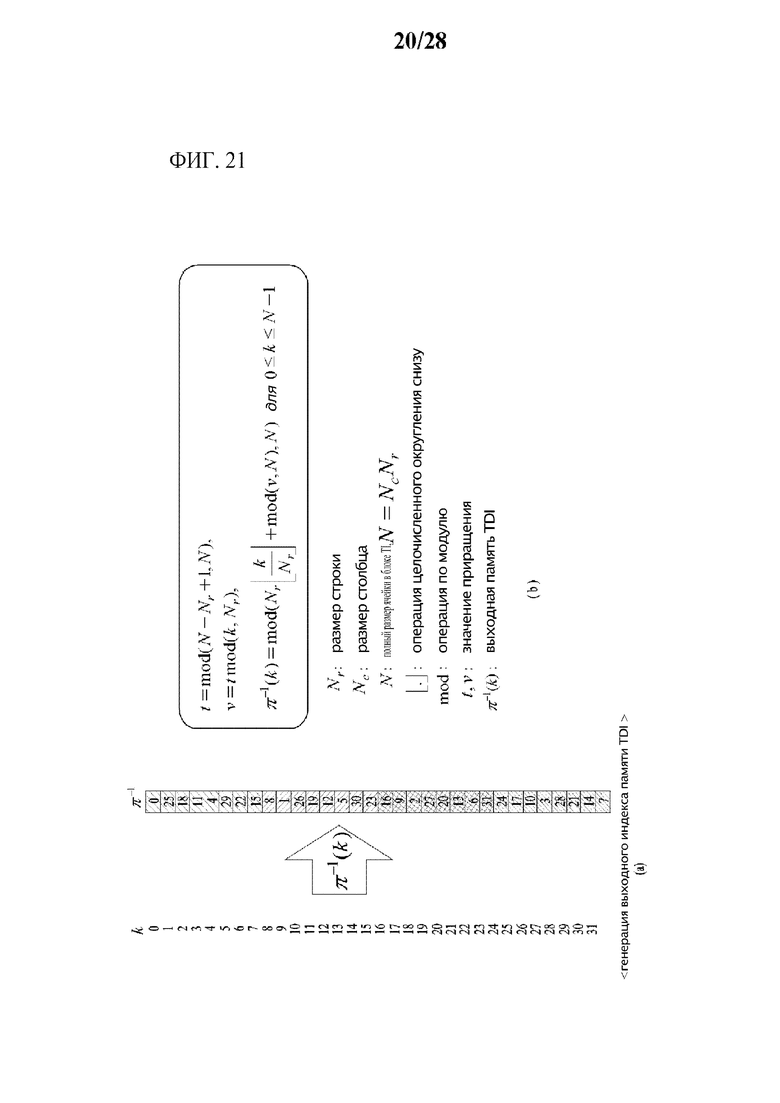

Фиг. 21 демонстрирует процесс генерации выходных индексов памяти TDI согласно варианту осуществления настоящего изобретения.

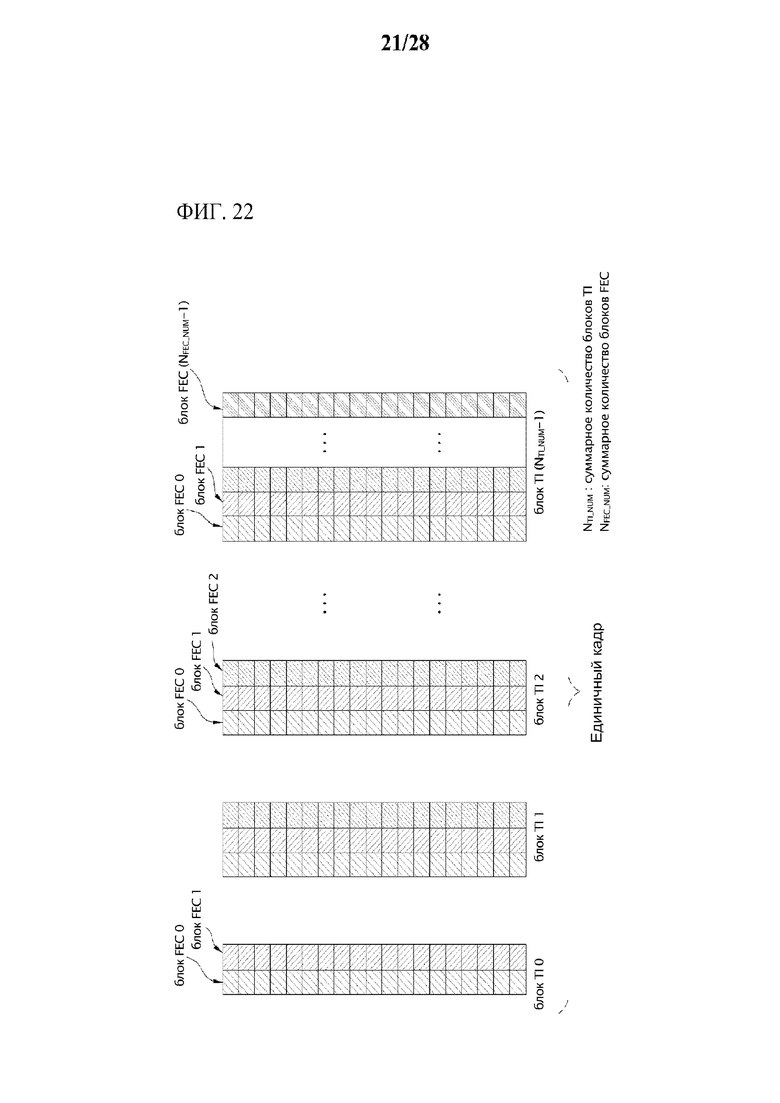

Фиг. 22 – принципиальная схема, демонстрирующая систему переменной скорости передачи данных согласно варианту осуществления настоящего изобретения.

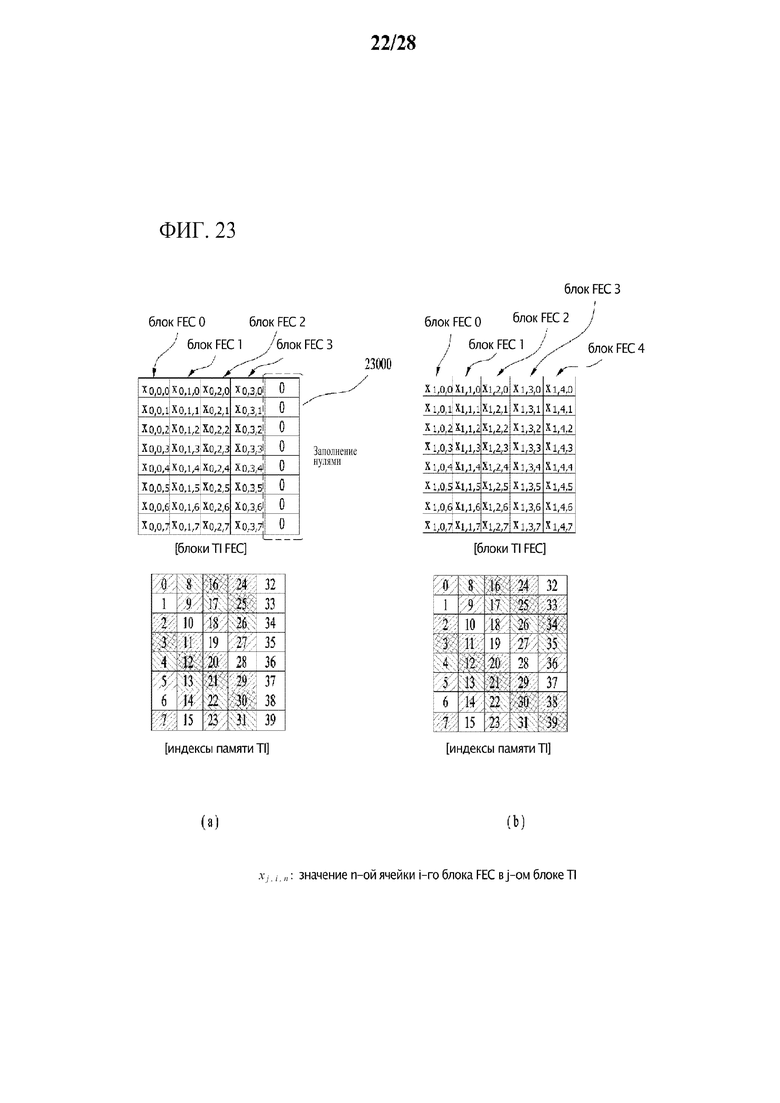

Фиг. 23 демонстрирует процесс временного перемежения согласно другому варианту осуществления настоящего изобретения.

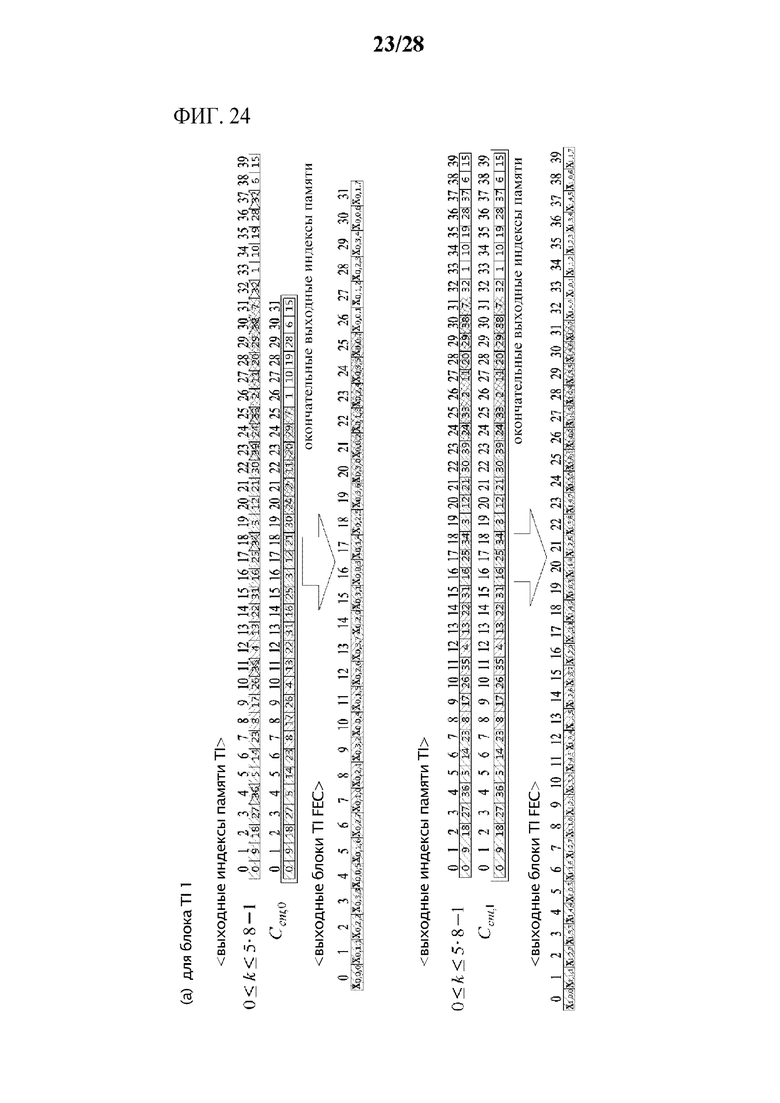

Фиг. 24 демонстрирует процесс генерации выходных индексов памяти TI согласно другому варианту осуществления настоящего изобретения.

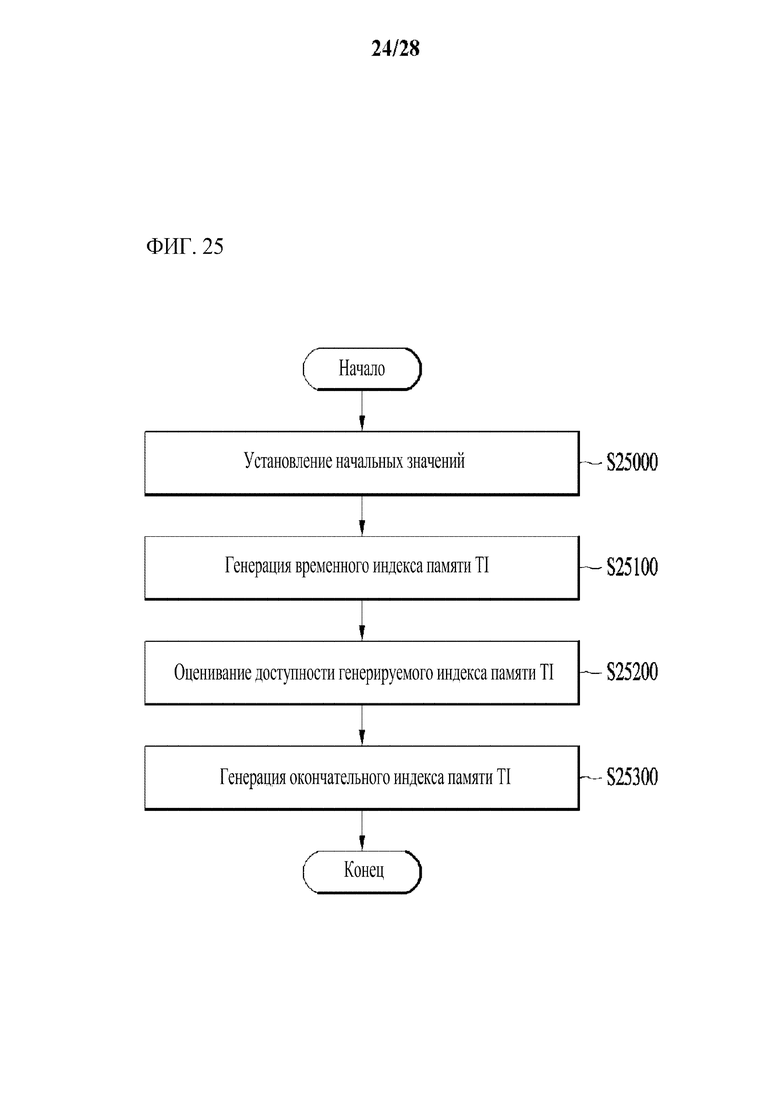

Фиг. 25 – блок-схема операций, демонстрирующая процесс генерации индексов памяти TI согласно варианту осуществления настоящего изобретения.

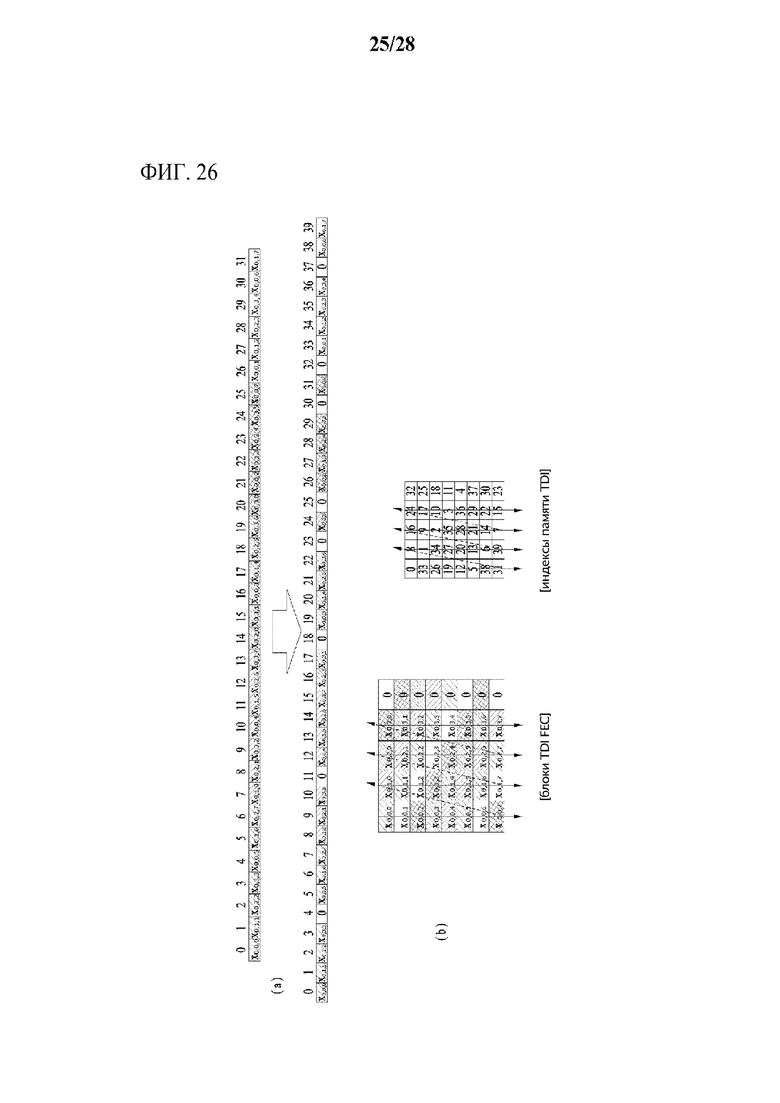

Фиг. 26 демонстрирует процесс временного обратного перемежения согласно другому варианту осуществления настоящего изобретения.

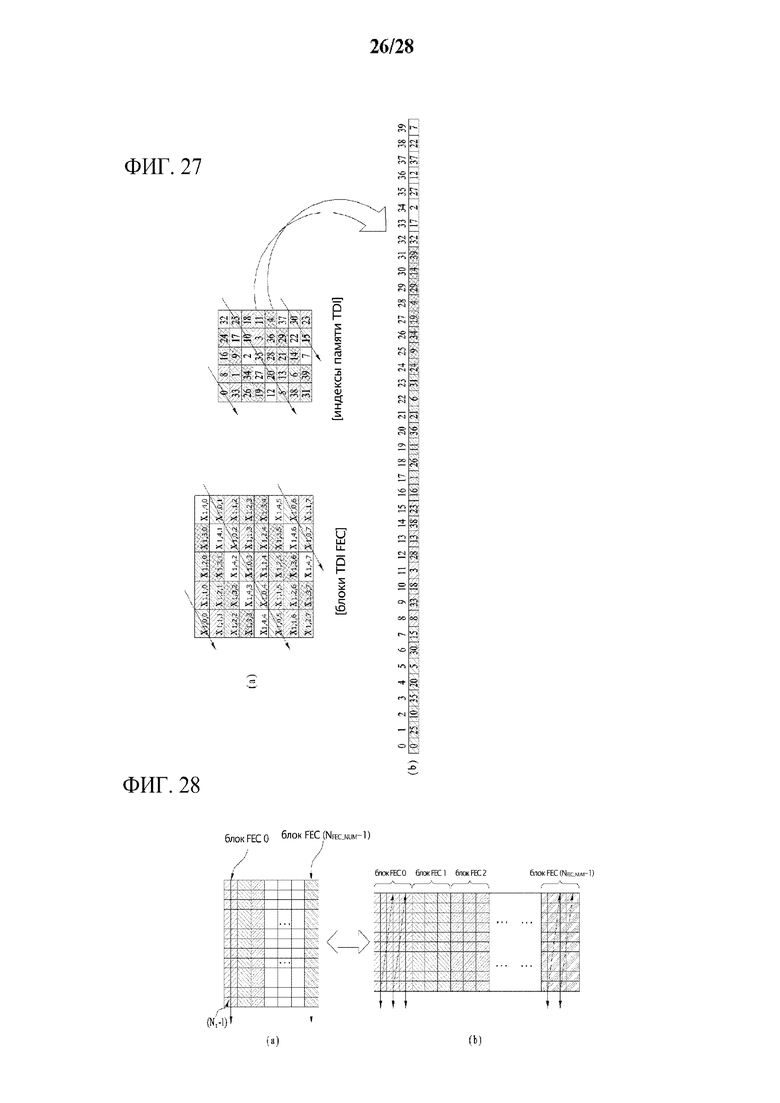

Фиг. 27 демонстрирует процесс временного обратного перемежения согласно другому варианту осуществления настоящего изобретения.

Фиг. 28 демонстрирует способ записи согласно варианту осуществления настоящего изобретения.

Фиг. 29 – блок-схема операций, демонстрирующая процесс генерации индексов памяти TDI согласно варианту осуществления настоящего изобретения.

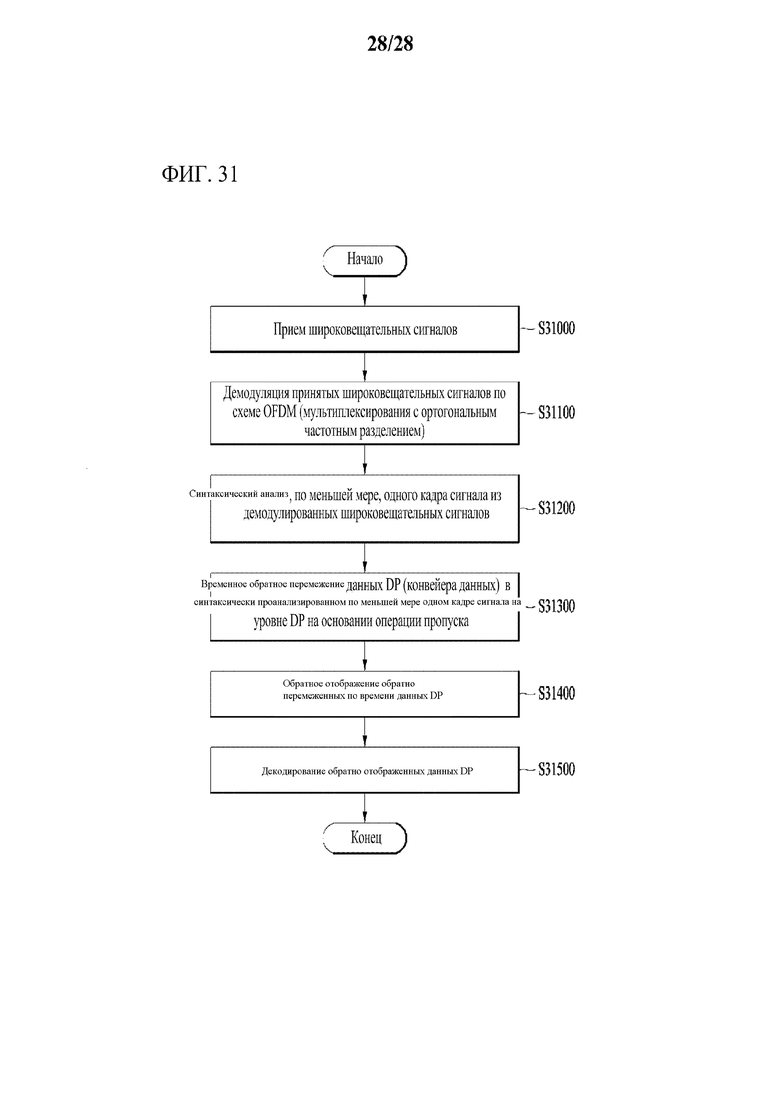

Фиг. 30 – блок-схема операций, демонстрирующая способ передачи широковещательных сигналов согласно варианту осуществления настоящего изобретения.

Фиг. 31 – блок-схема операций, демонстрирующая способ приема широковещательных сигналов согласно варианту осуществления настоящего изобретения.

ПРЕДПОЧТИТЕЛЬНЫЕ ВАРИАНТЫ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Обратимся к подробному описанию предпочтительных вариантов осуществления настоящего изобретения, примеры которых проиллюстрированы в прилагаемых чертежах. Подробное описание, которое будет приведено ниже со ссылкой на прилагаемые чертежи, призвано пояснять иллюстративные варианты осуществления настоящего изобретения, а не показать только варианты осуществления, которые можно реализовать согласно настоящему изобретению. Нижеследующее подробное описание включает в себя конкретные детали для обеспечения полного понимания настоящего изобретения. Однако специалистам в данной области очевидно, что настоящее изобретение можно осуществлять на практике без таких конкретных деталей.

Хотя большинство терминов, используемых в настоящем изобретении, выбрано среди общих терминов, широко используемых в уровне техники, некоторые термины выбраны заявителем произвольно, и их смысловые значения, при необходимости, подробно объяснены в нижеследующем описании. Таким образом, настоящее изобретение следует понимать на основании назначенных смысловых значений терминов, а не просто их названий или смысловых значений.

Настоящее изобретение предусматривает устройства и способы передачи и приема широковещательных сигналов для перспективных широковещательных услуг. Перспективные широковещательные услуги согласно варианту осуществления настоящего изобретения включают в себя наземную широковещательную услугу, мобильную широковещательную услугу, услугу UHDTV и т.д. Настоящее изобретение могут обрабатывать широковещательные сигналы для перспективных широковещательных услуг посредством не-MIMO (множественных входов и множественных выходов) или MIMO согласно одному варианту осуществления. Схема не-MIMO согласно варианту осуществления настоящего изобретения может включать в себя схему MISO (множественных входов и одного выхода), схему SISO (одного входа и одного выхода), и т.д.

Хотя в дальнейшем для удобства описания предполагается, что MISO или MIMO использует две антенны, настоящее изобретение применимо к системам, использующим две или более антенн.

Фиг. 1 демонстрирует структуру устройства для передачи широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения.

Устройство для передачи широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения может включать в себя модуль 1000 входного форматирования, модуль 1100 кодирования и модуляции, модуль 1200 построения кадра, модуль 1300 генерации формы волны и модуль 1400 генерации сигнализации. Ниже приведено описание работы каждого модуля устройства для передачи широковещательных сигналов.

Согласно фиг. 1 устройство для передачи широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения может принимать MPEG-TS, потоки IP (v4/v6) и общие потоки (GS) в качестве входного сигнала. Кроме того, устройство для передачи широковещательных сигналов может принимать информацию управления, касающуюся конфигурации каждого потока, образующего входной сигнал, и генерировать окончательный сигнал физического уровня согласно принятой информации управления.

Модуль 1000 входного форматирования согласно варианту осуществления настоящего изобретения может классифицировать входные потоки на основании стандарта для кодирования и модуляции или услуг или компонентов услуги и выводить входные потоки как множество логических конвейеров данных (или конвейеров данных или данных DP). Конвейер данных является логическим каналом на физическом уровне, который несет данные услуги или соответствующие метаданные, которые могут нести одну или несколько услуг или компонентов услуги. Кроме того, данные, передаваемые через каждый конвейер данных, могут именоваться данными DP.

Кроме того, модуль 1000 входного форматирования согласно варианту осуществления настоящего изобретения может делить каждый конвейер данных на блоки, необходимые для осуществления кодирования и модуляции, и осуществлять процессы, необходимые для повышения эффективности передачи или для осуществления планирования. Ниже будет подробно описана работа модуля 1000 входного форматирования.

Модуль 1100 кодирования и модуляции согласно варианту осуществления настоящего изобретения может осуществлять кодирование с прямым исправлением ошибок (FEC) на каждом конвейере данных, принятым от модуля 1000 входного форматирования, таким образом, что устройство для приема широковещательных сигналов может корректировать ошибку, которая может генерироваться на канале передачи. Кроме того, модуль 1100 кодирования и модуляции согласно варианту осуществления настоящего изобретения может преобразовывать выходные битовые данные FEC в символьные данные и перемежать символьные данные для коррекции пакетной ошибки, вызванной каналов. Как показано на фиг. 1, модуль 1100 кодирования и модуляции согласно варианту осуществления настоящего изобретения может делить обработанные данные таким образом, что разделенные данные могут выводиться через тракты данных для соответствующих антенных выходов для передачи данных через две или более передающие антенны.

Модуль 1200 построения кадра согласно варианту осуществления настоящего изобретения может отображать данные, выводимые из модуля 1100 кодирования и модуляции в кадры сигнала. Модуль 1200 построения кадра согласно варианту осуществления настоящего изобретения может осуществлять отображение с использованием информации планирования, выводимой из модуля 1000 входного форматирования, и перемежать данные в кадрах сигнала для получения дополнительного коэффициента усиления, обусловленного разнесением.

Модуль 1300 генерации формы волны согласно варианту осуществления настоящего изобретения может преобразовывать кадры сигнала, выводимые из модуля 1200 построения кадра, в сигнал для передачи. В этом случае модуль 1300 генерации формы волны согласно варианту осуществления настоящего изобретения может вставлять сигнал преамбулы (или преамбулу) в сигнал для обнаружения устройства передачи и вставлять опорный сигнал для оценивания канала передачи для компенсации искажения в сигнал. Кроме того, модуль 1300 генерации формы волны согласно варианту осуществления настоящего изобретения может обеспечивать защитный интервал и вставлять конкретную последовательность в него для смещения влияния разброса задержки канала вследствие многолучевого приема. Дополнительно, модуль 1300 генерации формы волны согласно варианту осуществления настоящего изобретения может осуществлять процедуру, необходимую для эффективной передачи с учетом характеристик сигнала, например отношения пиковой мощности к средней выходного сигнала.

Модуль 1400 генерации сигнализации согласно варианту осуществления настоящего изобретения генерирует окончательную информацию сигнализации физического уровня с использованием входной информации управления и информации, генерируемой модулем 1000 входного форматирования, модулем 1100 кодирования и модуляции и модулем 1200 построения кадра. Соответственно, устройство приема согласно варианту осуществления настоящего изобретения может декодировать принятый сигнал путем декодирования информации сигнализации.

Как описано выше, устройство для передачи широковещательных сигналов для перспективных широковещательных услуг согласно одному варианту осуществления настоящего изобретения может обеспечивать наземную широковещательную услугу, мобильную широковещательную услугу, услугу UHDTV и т.д. Соответственно, устройство для передачи широковещательных сигналов для перспективных широковещательных услуг согласно одному варианту осуществления настоящего изобретения может мультиплексировать сигналы для разных услуг во временной области и передавать их.

Фиг. 2, 3 и 4 демонстрируют модуль 1000 входного форматирования согласно вариантам осуществления настоящего изобретения. Ниже приведено описание каждой фигуры.

Фиг. 2 демонстрирует модуль входного форматирования согласно одному варианту осуществления настоящего изобретения. На Фиг. 2 показан модуль входного форматирования, когда входной сигнал является единичным входным потоком.

Согласно фиг. 2 модуль входного форматирования согласно одному варианту осуществления настоящего изобретения может включать в себя модуль 2000 адаптации режима и модуль 2100 адаптации потока.

Как показано на фиг. 2, модуль 2000 адаптации режима может включать в себя блок 2010 входного интерфейса, блок 2020 кодера CRC-8 и блок 2030 вставки заголовка BB. Ниже приведено описание каждого блока модуля 2000 адаптации режима.

Блок 2010 входного интерфейса может делить поступающий на него единичный входной поток на фрагменты данных, каждый из которых имеет длину кадра основной полосы (BB), используемую для FEC (BCH/LDPC), которая будет осуществляться позже, и выводить фрагменты данных.

Блок 2020 кодера CRC-8 может осуществлять кодирование CRC на данных кадра BB для добавления к нему данных избыточности.

Блок 2030 вставки заголовка BB может вставлять в данные кадра BB заголовок, включающий в себя информацию, например тип адаптации режима (TS/GS/IP), длину пользовательского пакета, длину поля данных, байт синхронизации пользовательского пакета, начальный адрес байта синхронизации пользовательского пакета в поле данных, индикатор режима высокой эффективности, поле синхронизации входного потока и т.д.

Как показано на фиг. 2, модуль 2100 адаптации потока может включать в себя блок 2110 вставки заполнения и блок 2120 скремблера BB. Ниже приведено описание каждого блока модуля 2100 адаптации потока.

Если длина данных, принятых от модуля 2000 адаптации режима, меньше длины входных данных, необходимой для кодирования FEC, блок 2110 вставки заполнения может вставлять бит заполнения в данные таким образом, чтобы данные имели длину входных данных, и выводить данные, включающие в себя бит заполнения.

Блок 2120 скремблера BB может рандомизировать входной битовый поток, осуществляя операцию XOR над входным битовым потоком и псевдослучайной двоичной последовательностью (PRBS).

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции.

Как показано на фиг. 2, модуль входного форматирования может, наконец, выводить конвейеры данных на модуль кодирования и модуляции.

Фиг. 3 демонстрирует модуль входного форматирования согласно другому варианту осуществления настоящего изобретения. На Фиг. 3 показан модуль 3000 адаптации режима модуля входного форматирования, когда входной сигнал соответствует множественным входным потокам.

Модуль 3000 адаптации режима модуля входного форматирования для обработки множественных входных потоков может независимо обрабатывать множественные входные потоки.

Согласно фиг. 3 модуль 3000 адаптации режима для соответственно обработки множественных входных потоков может включать в себя блоки входного интерфейса, блоки 3100 синхронизатор входных потоков, блоки 3200 компенсации задержки, блоки 3300 удаления пустых пакетов, блоки кодера CRC-8 и блоки вставки заголовка BB. Ниже приведено описание каждого блока модуля 3000 адаптации режима.

Операции блока входного интерфейса, блока кодера CRC-8 и блока вставки заголовка BB соответствуют операциям блока входного интерфейса, блока кодера CRC-8 и блока вставки заголовка BB, описанных со ссылкой на фиг. 2, и, таким образом, их описание опущено.

Блок 3100 синхронизатор входных потоков может передавать информацию тактовой частоты входного потока (ISCR) для генерации информации хронирования, необходимой устройству для приема широковещательных сигналов для восстановления TS или GS.

Блок 3200 компенсация задержки может задерживать входные данные и выводить задержанные входные данные таким образом, что устройство для приема широковещательных сигналов может синхронизировать входные данные в случае возникновения задержки между конвейерами данных согласно обработке данных, включающих в себя информацию хронирования, устройством передачи.

Блок 3300 удаления пустых пакетов может удалять передаваемые без необходимости входные пустые пакеты из входных данных, вставлять количество удаленных пустых пакетов во входные данные на основании позиций, в которых пустые пакеты удалены, и передавать входные данные.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции.

Фиг. 4 демонстрирует модуль входного форматирования согласно другому варианту осуществления настоящего изобретения.

В частности, фиг. 4 демонстрирует модуль адаптации потока модуля входного форматирования, когда входной сигнал соответствует множественным входным потокам.

Модуль адаптации потока модуля входного форматирования, когда входной сигнал соответствует множественным входным потокам, может включать в себя планировщик 4000, блок 4100 задержки на 1 кадр, блок 4200 вставки внутриполосной сигнализации или заполнения, блок 4300 генерации сигнализации физического уровня и блок 4400 скремблера BB. Ниже приведено описание каждого блока модуля адаптации потока.

Планировщик 4000 может осуществлять планирование для системы MIMO, использующей множественные антенны, имеющие двойную полярность. Кроме того, планировщик 4000 может генерировать параметры для использования в блоках обработки сигнала для антенных трактов, например, в блоке битоячеечного демультиплексора, блоке ячеечного перемежителя, блоке временного перемежителя и т.д., включенных в модуль кодирования и модуляции, представленный на фиг. 1.

Блок 4100 задержки на 1 кадр может задерживать входные данные на один кадр передачи, что позволяет передавать информацию планирования для следующего кадра в текущем кадре, чтобы информацию внутриполосной сигнализации можно было вставлять в конвейеры данных.

Блок 4200 вставки внутриполосной сигнализации или заполнения может вставлять информацию сигнализации, динамически зависящую от сигнализации физического уровня (PLS), без задержки в данные, задержанные на один кадр передачи. В этом случае блок 4200 вставки внутриполосной сигнализации или заполнения может вставлять бит заполнения, когда присутствует пространство для заполнения, или вставлять информацию внутриполосной сигнализации в пространство заполнения. Кроме того, планировщик 4000 может выводить информацию сигнализации, динамически зависящую от сигнализации физического уровня, для текущего кадра отдельно от информации внутриполосной сигнализации. Соответственно, отобразитель ячеек, который будет описан ниже, может отображать входные ячейки согласно информации планирования, выводимой из планировщика 4000.

Блок 4300 генерации сигнализации физического уровня может генерировать данные сигнализации физического уровня, которые будут передаваться в символе преамбулы кадра передачи или распределяться и передаваться в символе данных, отличном от информации внутриполосной сигнализации. В этом случае данные сигнализации физического уровня согласно варианту осуществления настоящего изобретения можно именовать информацией сигнализации. Кроме того, данные сигнализации физического уровня согласно варианту осуществления настоящего изобретения могут делиться на информацию перед PLS и информацию после PLS. Информация перед PLS может включать в себя параметры, необходимые для кодирования информации после PLS и статические данные сигнализации PLS, и информация после PLS может включать в себя параметры, необходимые для кодирования конвейеров данных. Параметры, необходимые для кодирования конвейеров данных, можно классифицировать на статические данные сигнализации PLS и динамические данные сигнализации PLS. Статические данные сигнализации PLS представляют собой параметр, одинаково применимый ко всем кадрам, включенным в суперкадр, который может изменяться от суперкадра к суперкадру. Динамические данные сигнализации PLS представляют собой параметр, по-разному применимый к соответствующим кадрам, включенным в суперкадр, который может изменяться от кадра к кадру. Соответственно, устройство приема может получать информацию после PLS путем декодирования информации перед PLS и декодировать нужные конвейеры данных путем декодирования информации после PLS.

Блок 4400 скремблера BB может генерировать псевдослучайную двоичную последовательность (PRBS) и осуществлять операцию XOR над PRBS и входными битовыми потоками для уменьшения отношения пиковой мощности к средней (PAPR) выходного сигнала блока генерации формы волны. Как показано на фиг. 4, скремблирование блока 4400 скремблера BB применимо и к конвейерам данных, и к информации сигнализации физического уровня.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции по желанию разработчика.

Как показано на фиг. 4, модуль адаптации потока может, наконец, выводить конвейеры данных на модуль кодирования и модуляции.

Фиг. 5 демонстрирует модуль кодирования и модуляции согласно варианту осуществления настоящего изобретения.

Модуль кодирования и модуляции, показанный на фиг. 5, соответствует варианту осуществления модуля кодирования и модуляции, представленному на фиг. 1.

Как описано выше, устройство для передачи широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения может обеспечивать наземную широковещательную услугу, мобильную широковещательную услугу, услугу UHDTV и т.д.

Поскольку QoS (качество обслуживания) зависит от характеристик услуги, предоставляемой устройством для передачи широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения, данные, соответствующие соответствующим услугам, необходимо обрабатывать согласно разным схемам. Соответственно, модуль кодирования и модуляции согласно варианту осуществления настоящего изобретения может независимо обрабатывать конвейеры данных, поступающие на него, независимо применяя схемы SISO, MISO и MIMO к конвейерам данных, соответственно, соответствующим трактам данных. В результате устройство для передачи широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения может управлять QoS для каждой услуги или компонента услуги, передаваемого через каждый конвейер данных.

Соответственно, модуль кодирования и модуляции согласно варианту осуществления настоящего изобретения может включать в себя первый блок 5000 для SISO, второй блок 5100 для MISO, третий блок 5200 для MIMO и четвертый блок 5300 для обработки информации перед PLS/после PLS. Модуль кодирования и модуляции, представленный на фиг. 5, является иллюстративным и может включать в себя только первый блок 5000 и четвертый блок 5300, второй блок 5100 и четвертый блок 5300 или третий блок 5200 и четвертый блок 5300 согласно конструкции. Таким образом, модуль кодирования и модуляции может включать в себя блоки для обработки конвейеров данных одинаково или по-разному согласно конструкции.

Ниже приведено описание каждого блока модуля кодирования и модуляции.

Первый блок 5000 обрабатывает входной конвейер данных согласно SISO и может включать в себя блок 5010 кодера FEC, блок 5020 битового перемежителя, блок 5030 битоячеечного демультиплексора, блок 5040 отобразителя группировок, блок 5050 ячеечного перемежителя и блок 5060 временного перемежителя.

Блок 5010 кодера FEC может осуществлять кодирование BCH и кодирование LDPC на входном конвейере данных для добавления к нему избыточности таким образом, что устройство приема может корректировать ошибку, генерируемую на канале передачи.

Блок 5020 битового перемежителя может перемежать битовые потоки кодированного с FEC конвейера данных согласно правилу перемежения таким образом, что битовые потоки обладают устойчивость к пакетной ошибке, которая может генерироваться на канале передачи. Соответственно, когда к символам QAM применяется глубокое замирание или стирание, можно предотвращать возникновение ошибок в последовательных битах из всех битов кодового слова, поскольку перемеженные биты отображаются в символы QAM.

Блок 5030 битоячеечного демультиплексора может определять порядок входных битовых потоков таким образом, что каждый бит в блоке FEC можно передавать с надлежащей надежностью с учетом как порядка входных битовых потоков, так и правила отображения группировки.

Кроме того, блок 5020 битового перемежителя располагается между блоком 5010 кодера FEC и блоком 5040 отобразителя группировок и может соединять выходные биты кодирования LDPC, осуществляемого блоком 5010 кодера FEC с позициями битов, имеющих разные значения надежности и оптимальные значения отобразителя группировок с учетом декодирования LDPC устройства для приема широковещательных сигналов. Соответственно, блок 5030 битоячеечного демультиплексора можно заменить блоком, имеющим аналогичную или равную функцию.

Блок 5040 отобразителя группировок может отображать битовое слово, поступающее на него, в одну группировку. В этом случае блок 5040 отобразителя группировок может дополнительно осуществлять поворот и Q-задержку. Таким образом, блок 5040 отобразителя группировок может поворачивать входные группировки согласно углу поворота, делить группировки на синфазную составляющую и квадратурнофазную составляющую и задерживать только квадратурнофазную составляющую на произвольное значение. Затем блок 5040 отобразителя группировок может повторно отображать группировки в новые группировки с использованием спаренных синфазной составляющей и квадратурнофазной составляющей.

Кроме того, блок 5040 отобразителя группировок может перемещать точки группировки на двухмерной плоскости для нахождения оптимальных точек группировки. Этот процесс позволяет оптимизировать емкость модуля 1100 кодирования и модуляции. Кроме того, блок 5040 отобразителя группировок может осуществлять вышеописанную операцию с использованием IQ-сбалансированных точек группировки и поворота. Блок 5040 отобразителя группировок можно заменить блоком, имеющим аналогичную или равную функцию.

Блок 5050 ячеечного перемежителя может случайно перемежать ячейки, соответствующие одному блоку FEC и выводить перемеженные ячейки таким образом, что ячейки, соответствующие соответствующим блокам FEC, можно выводить в том или ином порядке.

Блок 5060 временного перемежителя может перемежать ячейки, принадлежащие множеству блоков FEC, и выводить перемеженные ячейки. Соответственно, ячейки, соответствующие блокам FEC, рассеиваются и передаются в период, соответствующий глубине временного перемежения и, таким образом, можно получить коэффициент усиления, обусловленный разнесением.

Второй блок 5100 обрабатывает входной конвейер данных согласно MISO и может включать в себя блок кодера FEC, блок битового перемежителя, блок битоячеечного демультиплексора, блок отобразителя группировок, блок ячеечного перемежителя и блок временного перемежителя таким же образом, как первый блок 5000. Однако второй блок 5100 отличающийся от первого блока 5000 тем, то второй блок 5100 дополнительно включает в себя блок 5110 обработки MISO. Второй блок 5100 осуществляет такую же процедуру, включающую в себя операцию ввода в операцию временного перемежителя, как для первого блока 5000 и, таким образом, описание соответствующих блоков опущено.

Блок 5110 обработки MISO может кодировать входные ячейки согласно матрице кодирования MISO, обеспечивая разнесение передачи и выводить MISO-обработанные данные через два тракта. Обработка MISO согласно одному варианту осуществления настоящего изобретения может включать в себя OSTBC (ортогональное пространственно-временное блочное кодирование)/OSFBC (ортогональное пространственно-частотное блочное кодирование, кодирование по Аламоути).

Третий блок 5200 обрабатывает входной конвейер данных согласно MIMO и может включать в себя блок кодера FEC, блок битового перемежителя, блок битоячеечного демультиплексора, блок отобразителя группировок, блок ячеечного перемежителя и блок временного перемежителя таким же образом, как второй блок 5100, как показано на фиг. 5. Однако процедура обработки данных третьего блока 5200 отличается от процедуры второго блока 5100 поскольку третий блок 5200 включает в себя блок 5220 обработки MIMO.

Таким образом, в третьем блоке 5200, основные роли блока кодера FEC и блока битового перемежителя такие же, как у первого и второго блоков 5000 и 5100, хотя их функции могут отличаться от функций первого и второго блоков 5000 и 5100.

Блок 5210 битоячеечного демультиплексора может генерировать столько же выходных битовых потоков, сколько и входных битовых потоков обработки MIMO и выводить выходные битовые потоки через тракты MIMO для обработки MIMO. В этом случае блок 5210 битоячеечного демультиплексора может быть сконструирован для оптимизации производительности декодирования устройства приема с учетом характеристика LDPC и обработка MIMO.

Основные роли блока отобразителя группировок, блока ячеечного перемежителя и блока временного перемежителя такие же, как у первого и второго блоков 5000 и 5100, хотя их функции могут отличаться от функций первого и второго блоков 5000 и 5100. Как показано на фиг. 5, может присутствовать столько же блоков отобразителя группировок, блоков ячеечного перемежителя и блоков временного перемежителя, сколько существует трактов MIMO для обработки MIMO. В этом случае блоки отобразителя группировок, блоки ячеечного перемежителя и блоки временного перемежителя может действовать одинаково или независимо для данных, поступающих через соответствующие тракты.

Блок 5220 обработки MIMO может осуществлять обработку MIMO на двух входных ячейках с использованием матрицы кодирования MIMO и выводить MIMO-обработанные данные через два тракта. Матрица кодирования MIMO согласно варианту осуществления настоящего изобретения может включать в себя пространственное мультиплексирование, код Голдена, полноскоростной код полного разнесения, код линейной дисперсии и т.д.

Четвертый блок 5300 обрабатывает информацию перед PLS/после PLS и может осуществлять обработку SISO или MISO.

Основные роли блока битового перемежителя, блока битоячеечного демультиплексора, блока отобразителя группировок, блока ячеечного перемежителя, блока временного перемежителя и блока обработки MISO, включенных в четвертый блок 5300, соответствуют соответствующим блокам второго блока 5100, хотя их функции могут отличаться от функций второго блока 5100.

Блок 5310 укороченного/прореженного кодера FEC, включенный в четвертый блок 5300, может обрабатывать данные PLS с использованием схемы кодирования FEC для тракта PLS, обеспеченного для случая, когда длина входных данных меньше длины, необходимой для осуществления кодирование FEC. В частности, блок 5310 укороченного/прореженного кодера FEC может осуществлять кодирование BCH на входных битовых потоков, заполнение нулями соответствующее нужной длине входного битового потока, необходимо для нормального кодирования LDPC, осуществлять кодирование LDPC и затем удалять нули заполнения для прореживания битов четности таким образом, что эффективная скорость кодирования оказывается меньше или равна скорости конвейера данных.

Блоки, включенные в блоки с первого 5000 по четвертый 5300 можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Как показано на фиг. 5, модуль кодирования и модуляции может выводить конвейеры данных (или данные DP), информацию перед PLS и информацию после PLS, обработанные для соответствующих трактов, на модуль построения кадра.

Фиг. 6 демонстрирует модуль построения кадра согласно одному варианту осуществления настоящего изобретения.

Модуль построения кадра, показанный на фиг. 6, соответствует варианту осуществления модуля 1200 построения кадра, представленного на фиг. 1.

Модуль построения кадра согласно одному варианту осуществления настоящего изобретения может включать в себя, по меньшей мере, один отобразитель 6000 ячеек, по меньшей мере, один модуль 6100 компенсации задержки и, по меньшей мере, один блочный перемежитель 6200. Количество отобразителей 6000 ячеек, модулей 6100 компенсации задержки и блочных перемежителей 6200 может изменяться. Ниже приведено описание каждого модуля блока построения кадра.

Отобразитель 6000 ячеек может выделять ячейки, соответствующие SISO-, MISO- или MIMO-обработанным конвейерам данных, выводимым из модуля кодирования и модуляции, ячейки, соответствующие общим данным, одинаково применимым к конвейерам данных, и ячейки, соответствующие информации перед PLS/после PLS, кадрам сигнала согласно информации планирования. Общие данные относятся к информации сигнализации, совместно применяемой ко всем или некоторым конвейерам данных, и их можно передавать через конкретный конвейер данных. Конвейер данных, через который передаются общие данные, можно именовать общим конвейером данных, и он может изменяться согласно конструкции.

Когда устройство для передачи широковещательных сигналов согласно варианту осуществления настоящего изобретения использует две выходные антенны, и для обработки MISO используется кодирование по Аламоути, отобразитель 6000 ячеек может осуществлять попарное отображение ячеек для поддержания ортогональности согласно кодированию по Аламоути. Таким образом, отобразитель 6000 ячеек может обрабатывать две последовательные ячейки из входных ячеек в качестве одной единицы и отображать единицу в кадр. Соответственно, спаренные ячейки на входном тракте, соответствующем выходному тракту каждой антенны, можно выделять соседним позициям в кадре передачи.

Блок 6100 компенсации задержки может получать данные PLS, соответствующие текущему кадру передачи, задерживая входные ячейки данных PLS для следующего кадра передачи на один кадр. В этом случае данные PLS, соответствующие текущему кадру, можно передавать через преамбульную часть в текущем кадре сигнала, и данные PLS, соответствующие следующему кадру сигнала, можно передавать через преамбульную часть в текущем кадре сигнала или внутриполосную сигнализацию в каждом конвейере данных текущего кадра сигнала. Это может изменяться разработчиком.

Блочный перемежитель 6200 может получать дополнительный коэффициент усиления, обусловленный разнесением, за счет перемежения ячеек в транспортном блоке, соответствующем единице кадра сигнала. Кроме того, блочный перемежитель 6200 может осуществлять перемежение, обрабатывая две последовательные ячейки из входных ячеек в качестве одной единицы, когда осуществляется вышеописанное попарное отображение ячеек. Соответственно, ячейки, выводимые из блочного перемежителя 6200, могут быть двумя последовательными идентичными ячейками.

Когда осуществляются попарное отображение и попарное перемежение, по меньшей мере, один отобразитель ячеек и, по меньшей мере, один блочный перемежитель могут действовать одинаково или независимо для данных, поступающих через тракты.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Как показано на фиг. 6, модуль построения кадра может выводить, по меньшей мере, один кадр сигнала на модуль генерации формы волны.

Фиг. 7 демонстрирует модуль генерации формы волны согласно варианту осуществления настоящего изобретения.

Модуль генерации формы волны, представленный на фиг. 7, соответствует варианту осуществления модуля 1300 генерации формы волны, описанного со ссылкой на фиг. 1.

Модуль генерации формы волны согласно варианту осуществления настоящего изобретения может модулировать и передавать столько же кадров сигнала, сколько имеется антенн для приема и вывода кадров сигнала, выводимых из модуля построения кадра, представленного на фиг. 6.

В частности, модуль генерации формы волны, представленный на фиг. 7, является вариантом осуществления модуля генерации формы волны устройства для передачи широковещательных сигналов с использованием m передающих антенн и может включать в себя m блоков обработки для модуляции и вывода кадров, соответствующих m трактам. m блоков обработки могут осуществлять одну и ту же процедуру обработки. Ниже приведено описание работы первого блока 7000 обработки из m блоков обработки.

Первый блок 7000 обработки может включать в себя блок 7100 вставки опорного сигнала и снижения PAPR, блок 7200 обратного преобразования формы волны, блок 7300 снижения PAPR во временной области, блок 7400 вставки защитной последовательности, блок 7500 вставки преамбулы, блок 7600 обработки формы волны, блок 7700 вставки другой системы и блок 7800 DAC (цифро-аналогового преобразователя).

Блок 7100 вставки опорного сигнала и снижения PAPR может вставлять опорный сигнал в заранее определенную позицию каждого блока сигнала и применять схему снижения PAPR для снижения PAPR во временной области. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения соответствует системе OFDM, блок 7100 вставки опорного сигнала и снижения PAPR может использовать способ резервирования некоторых активных поднесущих вместо их использования. Кроме того, блок 7100 вставки опорного сигнала и снижения PAPR может не использовать схему снижения PAPR в качестве необязательного признака согласно системе широковещательной передачи/приема.

Блок 7200 обратного преобразования формы волны может преобразовывать входной сигнал таким образом, чтобы повышать эффективность передачи и гибкость с учетом характеристик канала передачи и архитектура системы. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения соответствует системе OFDM, блок 7200 обратного преобразования формы волны может применять способ преобразования сигнала частотной области в сигнал временной области посредством обратной операции FFT. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения соответствует системе одной несущей, блок 7200 обратного преобразования формы волны может не использоваться в модуле генерации формы волны.

Блок 7300 снижения PAPR во временной области может использовать способ снижения PAPR входного сигнала во временной области. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения соответствует системе OFDM, блок 7300 снижения PAPR во временной области может использовать способ простого ограничения пиковой амплитуды. Кроме того, блок 7300 снижения PAPR во временной области может не использоваться в системе широковещательной передачи/приема согласно варианту осуществления настоящего изобретения, поскольку он является необязательным признаком.

Блок 7400 вставки защитной последовательности может обеспечивать защитный интервал между соседними блоками сигнала и, при необходимости, вставлять конкретную последовательность в защитный интервал для минимизации влияние разброса задержки канала передачи. Соответственно, устройство приема может легко осуществлять синхронизацию или оценку канала. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения соответствует системе OFDM, блок 7400 вставки защитной последовательности может вставлять циклический префикс в защитный интервал символа OFDM.

Блок 7500 вставки преамбулы может вставлять сигнал известного типа (например, преамбулу или символ преамбулы) согласованный между устройством передачи и устройством приема, в сигнал передачи таким образом, что устройство приема может быстро и эффективно обнаруживать целевой сигнал системы. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения соответствует системе OFDM, блок 7500 вставки преамбулы может задавать кадр сигнала, состоящий из множества символов OFDM, и вставлять символ преамбулы в начало каждого кадра сигнала. Таким образом, преамбула несет основные данные PLS и располагается в начале кадра сигнала.

Блок 7600 обработки формы волны может осуществлять обработку формы волны на входном сигнале основной полосы таким образом, чтобы входной сигнал основной полосы согласовывался с характеристиками передачи канала. Блок 7600 обработки формы волны может использовать способ осуществления фильтрации типа "корень из приподнятого косинуса"(SRRC) для получения стандарта для внеполосного излучения сигнала передачи. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения соответствует системе множественных несущих, блок 7600 обработки формы волны может не использоваться.

Блок 7700 вставки другой системы может мультиплексировать сигналы множества систем широковещательной передачи/приема во временной области таким образом, что данные двух или более разных систем широковещательной передачи/приема обеспечение широковещательные услуги могут одновременно передаваться в одной и той же полосе RF сигнала. В этом случае две или более разных систем широковещательной передачи/приема относятся к системам, обеспечивающим разные широковещательные услуги. Разные широковещательные услуги могут относиться к наземной широковещательной услуге, мобильной широковещательной услуге и т.д. Данные, связанные с соответствующими широковещательными услугами, можно передавать в разных кадрах.

Блок 7800 DAC может преобразовывать входной цифровой сигнал в аналоговый сигнал и выводить аналоговый сигнал. Сигнал, выводимый из блока 7800 DAC, может передаваться через m выходных антенн. Передающая антенна согласно варианту осуществления настоящего изобретения может иметь вертикальную или горизонтальную полярность.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Фиг. 8 демонстрирует структуру устройства для приема широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения.

Устройство для приема широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения может соответствовать устройству для передачи широковещательных сигналов для перспективных широковещательных услуг, описанному со ссылкой на фиг. 1. Устройство для приема широковещательных сигналов для перспективных широковещательных услуг согласно варианту осуществления настоящего изобретения может включать в себя модуль 8000 синхронизации и демодуляции, модуль 8100 синтаксического анализа кадра, модуль 8200 обратного отображения и декодирования, выходной процессор 8300 и модуль 8400 декодирования сигнализации. Ниже приведено описание работы каждого модуля устройства для приема широковещательных сигналов.

Модуль 8000 синхронизации и демодуляции может принимать входные сигналы через m приемных антенн, осуществлять обнаружение сигнала и синхронизацию по отношению к системе, соответствующей устройству для приема широковещательных сигналов и осуществлять демодуляцию, соответствующую процедуре, обратной процедуре, осуществляемой устройством для передачи широковещательных сигналов.

Модуль 8100 синтаксического анализа кадра может синтаксически анализировать кадры входного сигнала и извлекать данные, через которые передается услуга, выбранная пользователем. Если устройство для передачи широковещательных сигналов осуществляет перемежение, модуль 8100 синтаксического анализа кадра может осуществлять обратное перемежение, соответствующее процедуре, обратной перемежению. В этом случае позиции сигнала и данные, которые необходимо извлечь, можно получать путем декодирования данных, выводимых из модуля 8400 декодирования сигнализации, для восстановления информации планирования, генерируемой устройством для передачи широковещательных сигналов.

Модуль 8200 обратного отображения и декодирования может преобразовывать входные сигналы в данные битовой области и затем, при необходимости, обратно перемежать их. Модуль 8200 обратного отображения и декодирования может осуществлять обратное отображение для применяемого отображения для эффективности передачи и корректировать ошибку, генерируемую на канале передачи при декодировании. В этом случае модуль 8200 обратного отображения и декодирования может получать параметры передачи, необходимые для обратного отображения и декодирования, путем декодирования данных, выводимых из модуля 8400 декодирования сигнализации.

Выходной процессор 8300 может осуществлять процедуры, обратные различным процедурам сжатия/обработки сигнала, которые применяются устройством для передачи широковещательных сигналов для повышения эффективности передачи. В этом случае выходной процессор 8300 может получать необходимую информацию управления из данных, выводимых из модуля 8400 декодирования сигнализации. Выходной сигнал выходного процессора 8300 соответствует сигналу, поступающему на устройство для передачи широковещательных сигналов, и может представлять собой MPEG-TS, потоки IP (v4 или v6) и общие потоки.

Модуль 8400 декодирования сигнализации может получать информацию PLS из сигнала, демодулированного модулем 8000 синхронизации и демодуляции. Как описано выше, модуль 8100 синтаксического анализа кадра, модуль 8200 обратного отображения и декодирования и выходной процессор 8300 может выполнять их функции с использованием данных, выводимых из модуля 8400 декодирования сигнализации.

Фиг. 9 демонстрирует модуль синхронизации и демодуляции согласно варианту осуществления настоящего изобретения.

Модуль синхронизации и демодуляции, показанный на фиг. 9, соответствует варианту осуществления модуля синхронизации и демодуляции, описанному со ссылкой на фиг. 8. Модуль синхронизации и демодуляции, показанный на фиг. 9, может осуществлять операцию, обратную операции модуля генерации формы волны, представленного на фиг. 7.

Как показано на фиг. 9, модуль синхронизации и демодуляции согласно варианту осуществления настоящего изобретения соответствует модулю синхронизации и демодуляции устройства для приема широковещательных сигналов, использующему m приемных антенн, и может включать в себя m блоков обработки для демодуляции сигналов, соответственно, поступающих через m трактов. m блоков обработки могут осуществлять одну и ту же процедуру обработки. Ниже приведено описание работы первого блока 9000 обработки из m блоков обработки.

Первый блок 9000 обработки может включать в себя тюнер 9100, блок 9200 ADC, детектор 9300 преамбулы, детектор 9400 защитной последовательности, блок 9500 преобразования формы волны, блок 9600 временной/частотной синхронизации, детектор 9700 опорного сигнала, корректор 9800 канала и блок 9900 обратного преобразования формы волны.

Тюнер 9100 может выбирать нужную полосу частот, компенсировать величину принятого сигнала и выводить скомпенсированный сигнал на блок 9200 ADC.

Блок 9200 ADC может преобразовывать сигнал, выводимый из тюнера 9100, в цифровой сигнал.

Детектор 9300 преамбулы может обнаруживать преамбулу (или сигнал преамбулы или символ преамбулы) для проверки, является ли цифровой сигнал сигналом системы, соответствующей устройству для приема широковещательных сигналов. В этом случае детектор 9300 преамбулы может декодировать основные параметры передачи, принятые в преамбуле.

Детектор 9400 защитной последовательности может обнаруживать защитную последовательность в цифровом сигнале. Блок 9600 временной/частотной синхронизации может осуществлять временную/частотную синхронизацию с использованием обнаруженной защитной последовательности, и корректор 9800 канала может оценивать канал посредством принятой/восстановленной последовательности с использованием обнаруженной защитной последовательности.

Блок 9500 преобразования формы волны может осуществлять операцию, обратную обратному преобразованию формы волны, когда устройство для передачи широковещательных сигналов осуществляет обратное преобразование формы волны. Когда система широковещательной передачи/приема согласно одному варианту осуществления настоящего изобретения является системой множественных несущих, блок 9500 преобразования формы волны может осуществлять FFT. Кроме того, когда система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения является системой одной несущей, блок 9500 преобразования формы волны может не использоваться, если принятый сигнал временной области обрабатывается в частотной области или обрабатывается во временной области.

Блок 9600 временной/частотной синхронизации может принимать выходные данные детектора 9300 преамбулы, детектора 9400 защитной последовательности и детектора 9700 опорного сигнала и осуществлять синхронизацию по времени и синхронизацию по несущей частоте, включающую в себя обнаружение защитной последовательности и размещение окна блока на обнаруженном сигнале. При этом блок 9600 временной/частотной синхронизации может возвращать выходной сигнал блока 9500 преобразования формы волны для синхронизации по частоте.

Детектор 9700 опорного сигнала может обнаруживать принятый опорный сигнал. Соответственно, устройство для приема широковещательных сигналов согласно варианту осуществления настоящего изобретения может осуществлять синхронизацию или оценку канала.

Корректор 9800 канала может оценивать канал передачи от каждой передающей антенны к каждой приемной антенне из защитной последовательности или опорного сигнала и осуществлять коррекцию канала для принятых данных с использованием оцененного канала.

Блок 9900 обратного преобразования формы волны может восстанавливать исходную область принятых данных, когда блок 9500 преобразования формы волны осуществляет преобразование формы волны для эффективной синхронизации и оценки/коррекции канала. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения является системой одной несущей, блок 9500 преобразования формы волны может осуществлять FFT для осуществления синхронизации/оценки/коррекции канала в частотной области, и блок 9900 обратного преобразования формы волны может осуществлять IFFT на сигнале, полученном коррекцией канала, для восстановления переданных символов данных. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения является системой множественных несущих, блок 9900 обратного преобразования формы волны может не использоваться.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Фиг. 10 демонстрирует модуль синтаксического анализа кадра согласно варианту осуществления настоящего изобретения.

Модуль синтаксического анализа кадра, представленный на фиг. 10, соответствует варианту осуществления модуля синтаксического анализа кадра, описанному со ссылкой на фиг. 8. Модуль синтаксического анализа кадра, показанный на фиг. 10, может осуществлять операцию, обратную операции модуля построения кадра, представленного на фиг. 6.

Как показано на фиг. 10, модуль синтаксического анализа кадра согласно варианту осуществления настоящего изобретения может включать в себя, по меньшей мере, один блочный перемежитель 10000 и, по меньшей мере, один обратный отобразитель 10100 ячеек.

Блочный перемежитель 10000 может обратно перемежать данные, поступающие через тракты данных m приемных антенн и обработанные модулем синхронизации и демодуляции для каждого блока сигнала. В этом случае если, устройство для передачи широковещательных сигналов осуществляет попарное перемежение, как показано на фиг. 8, блочный перемежитель 10000 может обрабатывать два последовательных фрагмента данных как пару для каждого входного тракта. Соответственно, блочный перемежитель 10000 может выводить два последовательных фрагмента данных даже когда осуществлялось обратное перемежение. Кроме того, блочный перемежитель 10000 может осуществлять операцию, обратную операции перемежения, осуществляемой устройством для передачи широковещательных сигналов, для вывода данных в исходном порядке.

Обратный отобразитель 10100 ячеек может извлекать ячейки, соответствующие общим данным, ячейки, соответствующие конвейерам данных, и ячейки, соответствующие данным PLS, из кадров принятого сигнала. Обратный отобразитель 10100 ячеек может объединять распределенные и переданные данные и, при необходимости, выводить их в виде потока. Когда два последовательных фрагмента входных данных ячейки обрабатываются как пара и отображаются в устройстве для передачи широковещательных сигналов, как показано на фиг. 6, обратный отобразитель 10100 ячеек может осуществлять попарное обратное отображение ячеек для обработки двух последовательных входных ячеек в качестве одной единицы в порядке процедуры, обратной операции отображения устройства для передачи широковещательных сигналов.

Кроме того, обратный отобразитель 10100 ячеек может извлекать данные сигнализации PLS, принятые в текущем кадре, как данные перед PLS и после PLS и выводить данные перед PLS и после PLS.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Фиг. 11 демонстрирует модуль обратного отображения и декодирования согласно варианту осуществления настоящего изобретения.

Модуль обратного отображения и декодирования, показанный на фиг. 11, соответствует варианту осуществления модуля обратного отображения и декодирования, представленному на фиг. 8. Модуль обратного отображения и декодирования, показанный на фиг. 11, может осуществлять операцию, обратную операции модуля кодирования и модуляции, представленного на фиг. 5.

Модуль кодирования и модуляции устройства для передачи широковещательных сигналов согласно варианту осуществления настоящего изобретения может обрабатывать входные конвейеры данных, независимо применяя к ним SISO, MISO и MIMO для соответствующих трактов, как описано выше. Соответственно, модуль обратного отображения и декодирования, представленный на фиг. 11, может включать в себя блоки для обработки данных, выводимых из модуля синтаксического анализа кадра согласно SISO, MISO и MIMO в ответ на устройство для передачи широковещательных сигналов.

Как показано на фиг. 11, модуль обратного отображения и декодирования согласно варианту осуществления настоящего изобретения может включать в себя первый блок 11000 для SISO, второй блок 11100 для MISO, третий блок 11200 для MIMO и четвертый блок 11300 для обработки информации перед PLS/после PLS. Модуль обратного отображения и декодирования, показанный на фиг. 11 является иллюстративным и может включать в себя только первый блок 11000 и четвертый блок 11300, только второй блок 11100 и четвертый блок 11300 или только третий блок 11200 и четвертый блок 11300 согласно конструкции. Таким образом, модуль обратного отображения и декодирования может включать в себя блоки для обработки конвейеров данных одинаково или по-разному согласно конструкции.

Ниже приведено описание каждого блока модуля обратного отображения и декодирования.

Первый блок 11000 обрабатывает входной конвейер данных согласно SISO и может включать в себя блок 11010 временного обратного перемежителя, блок 11020 ячеечного обратного перемежителя, блок 11030 обратного отобразителя группировок, блок 11040 ячеечно-битового мультиплексора, блок 11050 битового обратного перемежителя и блок 11060 декодера FEC.

Блок 11010 временного обратного перемежителя может осуществлять процесс, обратный процессу, осуществляемому блоком 5060 временного перемежителя, представленным на фиг. 5. Таким образом, блок 11010 временного обратного перемежителя может обратно перемежать входные символы, перемеженные во временной области, в их исходные позиции.

Блок 11020 ячеечного обратного перемежителя может осуществлять процесс, обратный процессу, осуществляемому блоком 5050 ячеечного перемежителя, представленным на фиг. 5. Таким образом, блок 11020 ячеечного обратного перемежителя может обратно перемежать позиции ячеек, распределенных в одном блоке FEC, в их исходные позиции.

Блок 11030 обратного отобразителя группировок может осуществлять процесс, обратный процессу, осуществляемому блоком 5040 отобразителя группировок, представленным на фиг. 5. Таким образом, блок 11030 обратного отобразителя группировок может обратно отображать входной сигнал символьной области в данные битовой области. Кроме того, блок 11030 обратного отобразителя группировок может осуществлять жесткое принятие решения и выводить битовые данные, в отношении которых принято решение. Кроме того, блок 11030 обратного отобразителя группировок может выводить логарифмическое отношение правдоподобия (LLR) каждого бита, которое соответствует значению мягкого принятия решения или значению вероятности. Если устройство для передачи широковещательных сигналов применяет повернутую группировку для получения дополнительного коэффициента усиления, обусловленного разнесением, блок 11030 обратного отобразителя группировок может осуществлять двухмерное обратное отображение LLR, соответствующее повернутой группировке. При этом блок 11030 обратного отобразителя группировок может вычислять LLR таким образом, что можно скомпенсировать задержку, применяемую устройством для передачи широковещательных сигналов к составляющей I или Q.

Блок 11040 ячеечно-битового мультиплексора может осуществлять процесс, обратный процессу, осуществляемому блоком 5030 битоячеечного демультиплексора, представленным на фиг. 5. Таким образом, блок 11040 ячеечно-битового мультиплексора может восстанавливать битовые данные, отображенные блоком 5030 битоячеечного демультиплексора, в исходные битовые потоки.

Блок 11050 битового обратного перемежителя может осуществлять процесс, обратный процессу, осуществляемому битовым перемежителем 5020, представленным на фиг. 5. Таким образом, блок 11050 битового обратного перемежителя может обратно перемежать битовые потоки, выводимые из блока 11040 ячеечно-битового мультиплексора, в исходном порядке.

Блок 11060 декодера FEC может осуществлять процесс, обратный процессу, осуществляемому блоком 5010 кодера FEC, представленным на фиг. 5. Таким образом, блок 11060 декодера FEC может корректировать ошибку, генерируемую на канале передачи путем осуществления декодирование декодирования LDPC и BCH.

Второй блок 11100 обрабатывает входной конвейер данных согласно MISO и может включать в себя блок временного обратного перемежителя, блок ячеечного обратного перемежителя, блок обратного отобразителя группировок, блок ячеечно-битового мультиплексора, блок битового обратного перемежителя и блок декодера FEC таким же образом, как первый блок 11000, как показано на фиг. 11. Однако второй блок 11100 отличающийся от первого блока 11000 тем, то второй блок 11100 дополнительно включает в себя блок 11110 декодирования MISO. Второй блок 11100 осуществляет такую же процедуру, включающую в себя операцию временного обратного перемежения по отношению к операции вывода, что и первый блок 11000 и, таким образом, описание соответствующих блоков опущено.

Блок 11110 декодирования MISO может осуществлять операцию, обратную операции блока 5110 обработки MISO, представленного на фиг. 5. Если система широковещательной передачи/приема согласно варианту осуществления настоящего изобретения использует STBC, блок 11110 декодирования MISO может осуществлять декодирование по Аламоути.

Третий блок 11200 обрабатывает входной конвейер данных согласно MIMO и может включать в себя блок временного обратного перемежителя, блок ячеечного обратного перемежителя, блок обратного отобразителя группировок, блок ячеечно-битового мультиплексора, блок битового перемежителя и блок декодера FEC таким же образом, как второй блок 11100, как показано на фиг. 11. Однако третий блок 11200 отличается от второго блока 11100 тем, что третий блок 11200 дополнительно включает в себя блок 11210 декодирования MIMO. Основные роли блока временного обратного перемежителя, блока ячеечного обратного перемежителя, блока обратного отобразителя группировок, блока ячеечно-битового мультиплексора и блока битового обратного перемежителя, включенных в третий блок 11200, такие же, как у соответствующих блоков, включенных в первый и второй блоки 11000 и 11100, хотя их функции могут отличаться от первого и второго блоков 11000 и 11100.

Блок 11210 декодирования MIMO может принимать выходные данные ячеечного обратного перемежителя для входных сигналов m приемных антенн и осуществлять декодирование MIMO в качестве операции, обратной операции блока 5220 обработки MIMO, представленного на фиг. 5. Блок 11210 декодирования MIMO может осуществлять декодирование методом максимального правдоподобия для получения оптимальной производительности декодирования или осуществлять сферическое декодирование с пониженной сложностью. В противном случае блок 11210 декодирования MIMO может достичь повышенной производительности декодирования путем осуществления обнаружения MMSE или осуществления итерационного декодирования с обнаружением MMSE.

Четвертый блок 11300 обрабатывает информацию перед PLS/после PLS и может осуществлять декодирование SISO или MISO. Четвертый блок 11300 может осуществлять процесс, обратный процессу, осуществляемому четвертым блоком 5300, описанным со ссылкой на фиг. 5.

Основные роли блока временного обратного перемежителя, блока ячеечного обратного перемежителя, блока обратного отобразителя группировок, блока ячеечно-битового мультиплексора и блока битового обратного перемежителя, включенных в четвертый блок 11300, такие же, как у соответствующих блоков первого, второго и третьего блоков 11000, 11100 и 11200, хотя их функции могут отличаться от первого, второго и третьего блоков 11000, 11100 и 11200.

Укороченный/прореженный декодер FEC 11310, включенный в четвертый блок 11300, может осуществлять процесс, обратный процессу, осуществляемому блоком 5310 укороченного/прореженного кодера FEC, описанным со ссылкой на фиг. 5. Таким образом, укороченный/прореженный декодер FEC 11310 может осуществлять деукорочение и депрореживание на данных, укороченных/прореженных согласно длине данных PLS, и затем осуществлять на них декодирование FEC. В этом случае декодер FEC, используемый для конвейеров данных, также можно использовать для PLS. Соответственно, дополнительное оборудование декодера FEC только для PLS не требуется, что позволяет упростить конструкцию системы и достичь эффективного кодирования.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Модуль обратного отображения и декодирования согласно варианту осуществления настоящего изобретения может выводить конвейеры данных и информацию PLS, обработанную для соответствующих трактов, на выходной процессор, как показано на фиг. 11.

Фиг. 12 и 13 демонстрируют выходные процессоры согласно вариантам осуществления настоящего изобретения.

Фиг. 12 демонстрирует выходной процессор согласно варианту осуществления настоящего изобретения. Выходной процессор, представленный на фиг. 12, соответствует варианту осуществления выходного процессора, представленному на фиг. 8. Выходной процессор, представленный на фиг. 12, принимает единичный конвейер данных, выводимый из модуля обратного отображения и декодирования, и выводит единичный выходной поток. Выходной процессор может осуществлять операцию, обратную операции модуля входного форматирования, представленного на фиг. 2.

Выходной процессор, показанный на фиг. 12, может включать в себя блок 12000 скремблера BB, блок 12100 удаления заполнения, блок 12200 декодера CRC-8 и блок 12300 процессора кадров BB.

Блок 12000 скремблера BB может дескремблировать входной битовый поток путем генерации той же PRBS, которая используется в устройстве для передачи широковещательных сигналов для входного битового потока, и осуществлять операцию XOR на PRBS и битовом потоке.

Блок 12100 удаления заполнения, при необходимости, может удалять биты заполнения, вставленные устройством для передачи широковещательных сигналов.

Блок 12200 декодера CRC-8 может проверять блочную ошибку путем осуществления декодирования CRC на битовом потоке, принятом от блока 12100 удаления заполнения.

Блок 12300 процессора кадров BB может декодировать информацию, передаваемую в заголовке кадра BB, и восстанавливать MPEG-TS, потоки IP (v4 или v6) или общие потоки с использованием декодированной информации.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Фиг. 13 демонстрирует выходной процессор согласно другому варианту осуществления настоящего изобретения. Выходной процессор, показанный на фиг. 13, соответствует варианту осуществления выходного процессора, представленному на фиг. 8. Выходной процессор, показанный на фиг. 13, принимает множественные конвейеры данных, выводимые из модуля обратного отображения и декодирования. Декодирование множественных конвейеров данных может включать в себя процесс объединения общих данных, одинаково применимых к множеству конвейеров данных, и связанных с ними конвейеров данных и их декодирование или процесс одновременного декодирования множества услуг или компонентов услуги (включающего в себя масштабируемую видеоуслугу) устройством для приема широковещательных сигналов.

Выходной процессор, показанный на фиг. 13, может включать в себя блок дескремблера BB, блок удаления заполнения, блок декодера CRC-8 и блок процессора кадров BB, как и выходной процессор, представленный на фиг. 12. Основные роли этих блоков соответствуют ролям блоков, описанных со ссылкой на фиг. 12, хотя их операции могут отличаться от операций блоков, представленных на фиг. 12.

Блок 13000 буфер устранения дрожания, включенный в выходной процессор, показанный на фиг. 13, может компенсировать задержку, вводимую устройством для передачи широковещательных сигналов для синхронизации множественных конвейеров данных, согласно восстановленному параметру TTO (время для вывода).

Блок 13100 вставки пустого пакета может восстанавливать пустой пакет, удаленный из потока, со ссылкой на восстановленный DNP (удаленный пустой пакет) и выводить общие данные.

Блок 13200 регенерации тактового сигнала TS может восстанавливать синхронизацию по времени выходных пакетов на основании информации ISCR (тактовой частоты входного потока).

Блок 13300 рекомбинации TS может рекомбинировать общие данные и связанные с ними конвейеры данных, выводимые из блока 13100 вставки пустого пакета, для восстановления исходных MPEG-TS, потоков IP (v4 или v6) или общих потоков. Информацию TTO, DNT и ISCR можно получать из заголовка кадра BB.

Блок 13400 декодирования внутриполосной сигнализации может декодировать и выводить информацию внутриполосной сигнализации физического уровня, передаваемую через поле битов заполнения в каждом кадре FEC конвейера данных.

Выходной процессор, показанный на фиг. 13, может дескремблировать в BB информацию перед PLS и информацию после PLS, соответственно введенную через тракт перед PLS и тракт после PLS, и декодировать дескремблированные данные для восстановления исходных данных PLS. Восстановленные данные PLS доставляются на системный контроллер, включенный в устройство для приема широковещательных сигналов. Системный контроллер может обеспечивать параметры, необходимые для модуля синхронизации и демодуляции, модуля синтаксического анализа кадра, модуля обратного отображения и декодирования и модуля выходного процессора устройства для приема широковещательных сигналов.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Фиг. 14 демонстрирует модуль кодирования и модуляции согласно другому варианту осуществления настоящего изобретения.

Модуль кодирования и модуляции, показанный на фиг. 14, соответствует другому варианту осуществления модуля кодирования и модуляции, представленного на фиг. 1-5.

Для управления QoS для каждой услуги или компонента услуги, передаваемого через каждый конвейер данных, как описано выше со ссылкой на фиг. 5, модуль кодирования и модуляции, показанный на фиг. 14 может включать в себя первый блок 14000 для SISO, второй блок 14100 для MISO, третий блок 14200 для MIMO и четвертый блок 14300 для обработки информации перед PLS/после PLS. Кроме того, модуль кодирования и модуляции может включать в себя блоки для обработки конвейеров данных одинаково или по-разному согласно конструкции. Блоки с первого по четвертый 14000-14300, показанные на фиг. 14 аналогичны блокам с первого по четвертый 5000-5300, представленным на фиг. 5.

Однако блоки с первого по четвертый 14000-14300, показанные на фиг. 14, отличаются от блоков с первого по четвертый 5000-5300, представленных на фиг. 5, тем, что отобразитель 14010 группировок, включенный в блоки с первого по четвертый 14000-14300, имеет функцию, отличную от блоков с первого по четвертый 5000-5300, представленных на фиг. 5, блок 14020 поворота и I/Q-перемежения присутствует между ячеечным перемежителем и временным перемежителем блоков с первого по четвертый 14000-14300, представленных на фиг. 14, и третий блок 14200 для MIMO имеет конфигурацию, отличную от третьего блока 5200 для MIMO, представленного на фиг. 5. Нижеследующее описание посвящено этим различиям между блоками с первого по четвертый 14000-14300, показанными на фиг. 14, и блоками с первого по четвертый 5000-5300, представленными на фиг. 5.

Блок 14010 отобразителя группировок, показанный на фиг. 14, может отображать входное битовое слово в комплексный символ. Однако блок 14010 отобразителя группировок может не осуществлять поворот группировки, в отличие от блока отобразителя группировок, показанного на фиг. 5. Блок 14010 отобразителя группировок, показанный на фиг. 14, одинаково применим к первому, второму и третьему блокам 14000, 14100 и 14200, как описано выше.

Блок 14020 поворота и I/Q-перемежения может независимо перемежать синфазные и квадратурнофазные составляющие каждого комплексного символа ячеечно перемеженных данных, выводимых из ячеечного перемежителя, и выводить синфазные и квадратурнофазные составляющие символ за символом. Количество входных фрагментов данных и выходных фрагментов данных блока 14020 поворота и I/Q-перемежения составляет два или более, что может изменяться разработчиком. Кроме того, блок 14020 поворота и I/Q-перемежения может не перемежать синфазную составляющую.

Блок 14020 поворота и I/Q-перемежения одинаково применим к блокам с первого по четвертый 14000-14300, как описано выше. В этом случае, применяется ли блок 14020 поворота и I/Q-перемежения к четвертому блоку 14300 для обработки информации перед/после PLS, может сигнализироваться посредством вышеописанной преамбулы.

Третий блок 14200 для MIMO может включать в себя блок 14210 Q-блочного перемежителя и блок 14220 генератора комплексных символов, как показано на фиг. 14.

Блок 14210 Q-блочного перемежителя может переставлять четностную часть блока FEC, кодированного с FEC, принятого от кодера FEC. Соответственно, четностную часть матрицы LDPC H можно заменить циклической структурой наподобие информационной части. Блок 14210 Q-блочного перемежителя может переставлять выходных битовых блоков, имеющих размер Q, матрицы LDPC H, и затем осуществлять строково-столбцовое блочное перемежение для генерации окончательных битовых потоков.

Блок 14220 генератора комплексных символов принимает битовые потоки, выводимые из блока 14210 Q-блочного перемежителя, отображает битовые потоки в комплексные символы и выводит комплексные символы. В этом случае блок 14220 генератора комплексных символов может выводить комплексные символы через, по меньшей мере, два тракта. Это может изменяться разработчиком.

Вышеописанные блоки можно исключить или заменить блоками, имеющими аналогичные или идентичные функции согласно конструкции.

Модуль кодирования и модуляции согласно другому варианту осуществления настоящего изобретения, представленный на фиг. 14, может выводить конвейеры данных, информацию перед PLS и информацию после PLS, обработанную для соответствующих трактов, на модуль построения кадра.

Фиг. 15 демонстрирует модуль обратного отображения и декодирования согласно другому варианту осуществления настоящего изобретения.

Модуль обратного отображения и декодирования, показанный на фиг. 15, соответствует другому варианту осуществления модуля обратного отображения и декодирования, представленного на фиг. 11. Модуль обратного отображения и декодирования, показанный на фиг. 15, может осуществлять операцию, обратную операции модуля кодирования и модуляции представленный на фиг. 14.

Как показано на фиг. 15, модуль обратного отображения и декодирования согласно другому варианту осуществления настоящего изобретения может включать в себя первый блок 15000 для SISO, второй блок 15100 для MISO, третий блок 15200 для MIMO и четвертый блок 15300 для обработки информации перед PLS/после PLS. Кроме того, модуль обратного отображения и декодирования может включать в себя блоки для обработки конвейеров данных одинаково или по-разному согласно конструкции. Блоки с первого по четвертый 15000-15300, показанные на фиг. 15, аналогичны блокам с первого по четвертый 11000-11300, представленным на фиг. 11.

Однако блоки с первого по четвертый 15000-15300, показанные на фиг. 15, отличаются от блоков с первого по четвертый 11000-11300, представленных на фиг. 11, тем, что блок 15010 I/Q-обратного перемежения и обратного поворота присутствует между временным обратным перемежителем и ячеечным обратным перемежителем блоков с первого по четвертый 15000-15300, обратный отобразитель 15020 группировок, включенный в блоки с первого по четвертый 15000-15300, имеет функцию, отличную от блоков с первого по четвертый 11000-11300, представленных на фиг. 11, и третий блок 15200 для MIMO имеет конфигурацию, отличную от третьего блока 11200 для MIMO, представленного на фиг. 11. Нижеследующее описание посвящено этим различиям между блоками с первого по четвертый 15000-15300, показанными на фиг. 15, и блоками с первого по четвертый 11000-11300, представленными на фиг. 11.

Блок 15010 I/Q-обратного перемежения и обратного поворота может осуществлять процесс, обратный процессу, осуществляемому блоком 14020 поворота и I/Q-перемежения, представленным на фиг. 14. Таким образом, блок 15010 I/Q-обратного перемежения и обратного поворота может обратно перемежать составляющие I и Q подвергнутые I/Q-перемежению и переданные устройством для передачи широковещательных сигналов, и совершать обратный поворот комплексных символов, имеющих восстановленные составляющие I и Q.

Блок 15010 I/Q-обратного перемежения и обратного поворота одинаково применим к блокам с первого по четвертый 15000-15300, как описано выше. В этом случае, применяется ли блок 15010 I/Q-обратного перемежения и обратного поворота к четвертому блоку 15300 для обработки информации перед/после PLS, может сигнализироваться посредством вышеописанной преамбулы.

Блок 15020 обратного отобразителя группировок может осуществлять процесс, обратный процессу, осуществляемому блоком 14010 отобразителя группировок, представленным на фиг. 14. Таким образом, блок 15020 обратного отобразителя группировок может обратно отображать ячеечно обратно перемеженные данные, не осуществляя обратный поворот.

Третий блок 15200 для MIMO может включать в себя блок 15210 синтаксического анализа комплексного символа и блок 15220 Q-блочного обратного перемежителя, как показано на фиг. 15.