УРОВЕНЬ ТЕХНИКИ

При одновременном приеме инструкций на считывание и запись данных возникает состояние состязания. Это состояние также может возникнуть, например, когда поток выполняет пакет исполняемых данных из памяти в то же самое время, когда поток записи доставляет данные в память. Это может привести к аварийному прекращению работы компьютера, программной остановке, ошибкам считывания/записи или другим проблемам. В одном техническом решении поток может быть приостановлен в ожидании потока записи для обеспечения данных. Однако приостановка потока может вызвать проблемы производительности для связанных процессов. Например, для одного процесса могут выполняться десятки или сотни потоков, из которых к данным обращается только один или более из них, но приходится приостанавливать все эти потоки, ожидая доставку данных, при каждом сбое потоковой передачи.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Этот раздел в упрощенной форме представляет подборку концепций, которые подробно описываются ниже в разделе «Подробное описание». Этот раздел не предполагается для идентификации ключевых признаков или существенных признаков заявленного предмета изобретения, и не предназначен для его использования с целью ограничения объема заявленного изобретения.

Варианты осуществления изобретения дают возможность доставки исполняемого кода без блокировки путем его дизассемблирования и упорядочивания записей в странице памяти. Это позволяет исполняемому коду оставаться в согласованном состоянии на протяжении всей доставки потоковых данных. Поскольку память находится в согласованном состоянии, другие потоки могут продолжаться, когда в память записывается байт-код. Это позволяет обеспечить более высокий уровень масштабируемости и эффективности функционирования.

Дополнительные варианты осуществления изобретения предусматривают возможность потоковой передачи данных исполняемого кода в пользовательском режиме без приостановки всего процесса или использования компоненты режима ядра операционной системы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для дополнительного разъяснения вышеуказанных и других преимуществ и признаков вариантов осуществления настоящего изобретения далее со ссылками на сопроводительные чертежи представлено более подробное описание вариантов осуществления настоящего изобретения. Очевидно, что на этих чертежах показаны только типовые варианты осуществления изобретения, и их не следует рассматривать как ограничение объема изобретения. Далее изобретение описывается и объясняется с указанием дополнительных специфических особенностей и деталей с использованием сопроводительных чертежей, на которых:

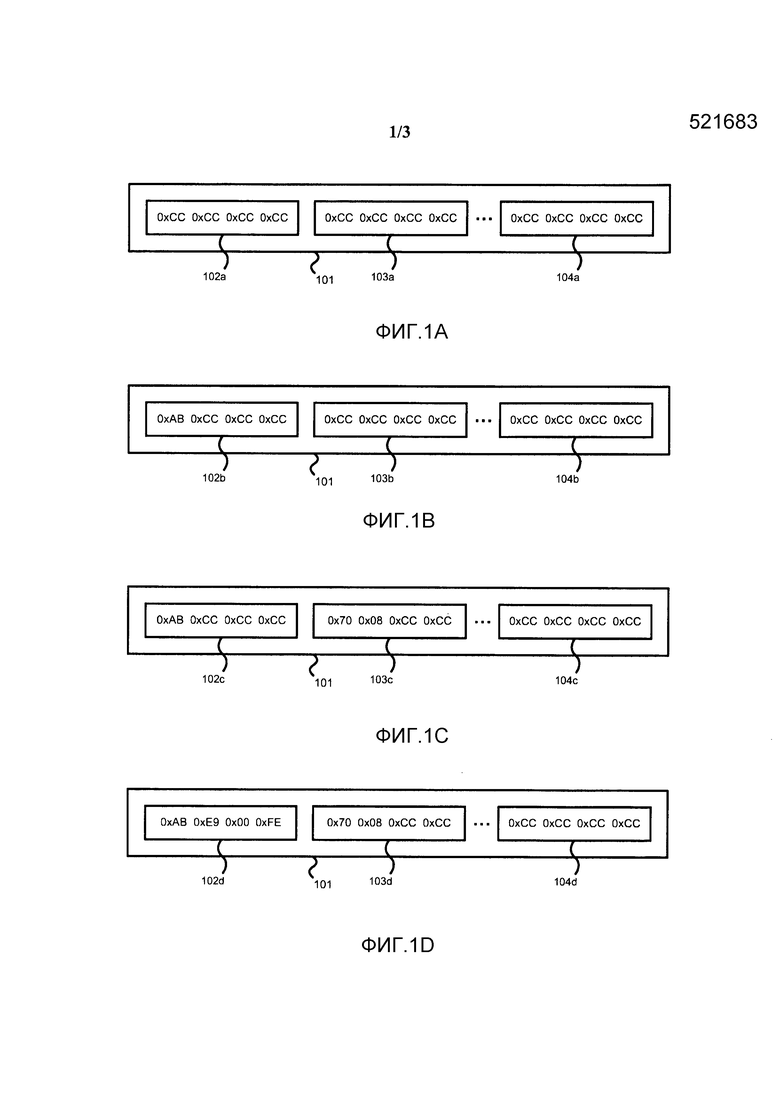

фигуры 1А-1D иллюстрируют порядок записей в память во времени согласно одному варианту осуществления изобретения;

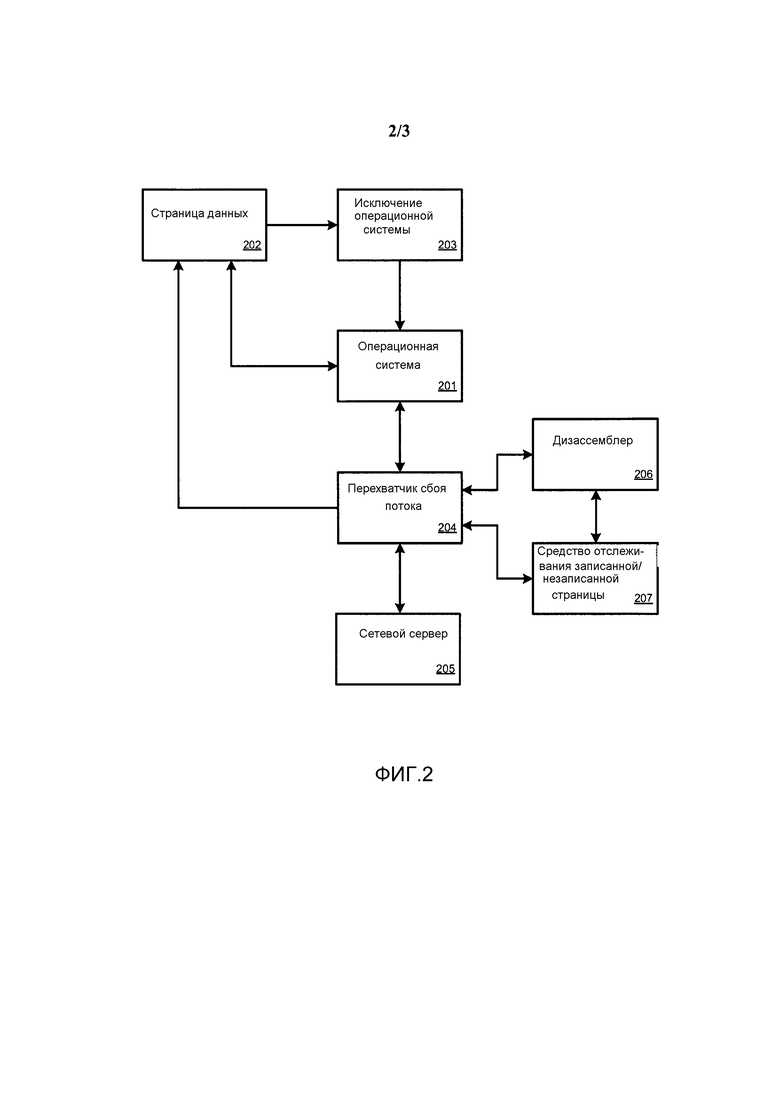

фиг. 2 - иллюстрирует систему для свободной от блокирования потоковой передачи данных исполняемого кода согласно одному варианту осуществления изобретения;

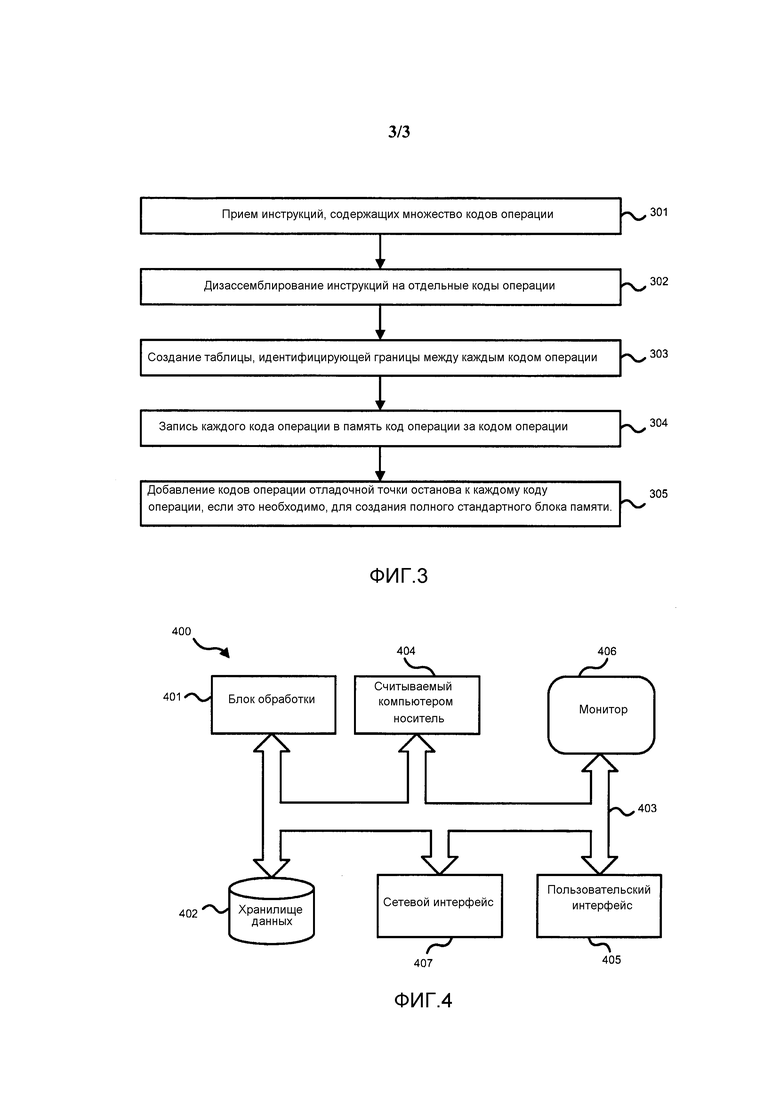

фиг. 3 - блок-схема процесса или способа для потоковой передачи данных исполняемого кода согласно одному варианту осуществления изобретения;

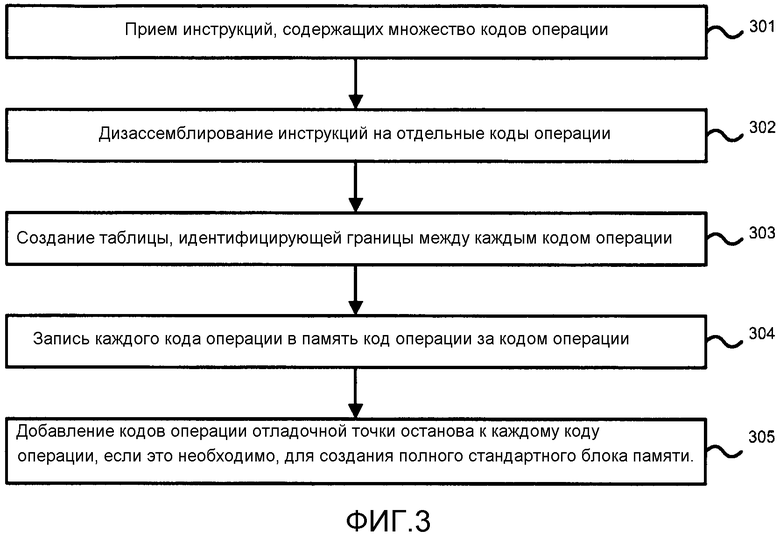

фиг. 4 - пример подходящей вычислительной и сетевой среды для обеспечения свободной от блокирования потоковой передачи данных исполняемого кода.

ПОДРОБНОЕ ОПИСАНИЕ

Описанное здесь свободное от блокирования техническое решение имеет преимущество в отношении двух характеристик современного процессора. Во-первых, процессор обеспечивает запись в тридцати двух битовой или шестидесяти четырех битвой памяти. Это гарантирует, что процессор увидит все тридцать два бита или шестьдесят четыре бита памяти. Во-вторых, процессор имеет однобайтовый код операции (опкод) исключения отладочного останова. Этот код операции отладочного останова позволяет процессору предпринимать повторную попытку считывания и исполнения кодов операции из памяти, не вызывая сбоя вызывающего потока.

В одном варианте код дизассемблируется в памяти перед тем, как инструкции станут доступными процессору. Это дизассемблирование позволяет создать упорядоченный список записей памяти, состоящих из нескольких отдельных тридцати двух битовых или шестидесяти четырех битовых записей. Такое дизассемблирование и анализ можно выполнить либо у клиента, либо на сервере. Выполнение этой операции у клиента позволяет сэкономить на сетевых передачах, но не на затратах, связанных с увеличившимся количеством процессорных циклов, в то время как выполнение этой операции на сервере означает увеличение количества сетевых передач, но потребует меньший объем процессорной обработки на клиентском узле.

При распределении страницы памяти вся страница записывается однобайтовыми кодами исключения. Обработчик сбоя потока поддерживает список страниц и участков, в которые была выполнена запись, или которые оказались недопустимыми.

Коды операции записываются в память с использованием дизассемблированных тридцати двух битовых или шестидесяти четырех битовых блоков, начиная с конца страницы. В альтернативном варианте, можно выполнить анализ дерева ассемблирования для идентификации оконечных кодов операции, представляющих собой коды операции, вызванные другими кодами операции. Оконечные коды операции могут быть идентифицированы путем обхода графа вызова исполнения кода операции. Эти оконечные коды операции могут быть записаны в память первыми.

Для кодов операции, являющихся тридцати двух битовыми или менее (или шестидесяти четырех битовыми или менее в других вариантах осуществления изобретения), весь код операции записывается в память с тем, чтобы процессор мог успешно исполнить упомянутую инструкцию. Если код операции больше тридцати двух бит (или больше шестидесяти четырех бит в других вариантах осуществления изобретения), то тогда сначала записывается «конец» кода операции. Запись конца кода операции обеспечивает следующее: если процессор исполняет упомянутую инструкцию, когда код операции все еще записывается, то тогда процессор сначала исполнит код операции отладочного останова. Это позволяет обработчику сбоя потока закончить запись кода операции, и процессор сможет вновь попытаться исполнить этот код операции. Если тридцати двух битовая (или шестидесяти четырех битовая) запись охватывает более одного кода операции, то тогда записывается код операции отладочного останова для предоставления возможности повторной попытки. Если тридцати двух битовая (или шестидесяти четырех битовая) запись уже сделана, то тогда записывается предыдущее значение, и в этом случае код операции остается допустимым.

В результате записи дизассемблированных кодов операции, разделенных отладочными остановами, процессор столкнется либо с недопустимой отладочной точкой останова, любо с допустимым исполняемым кодом. Если приложение исполняет недопустимую отладочную точку останова, то тогда описанный здесь перехватчик сбоя потока перехватывает исключение до его доставки в приложение. Перехватчик сбоя потока будет ждать, пока память не станет допустимой, а затем предпримет повторную попытку исполнения кода операции. Перехватчик сбоя потока может использовать таблицу страниц и записанных кодов операции для различения точки останова, которая появляется в ходе сбоя потока, для которой потребуется повторная попытка, и точки останова, используемой отладчиком или приложением, которая должна быть возвращена в указанное приложение. В случае допустимого исполняемого кода, приложение его успешно исполнит. В результате, обработчику сбоя потока не придется приостанавливать все потоки, исполняемые в процессе, при доставке результатов сбоя потока.

На фигурах 1А-1D показан порядок записей в память во времени согласно одному варианту осуществления изобретения. Программный код, используемый в этом примере, содержит инструкции 0хАВ 0хЕ9 0х00 0хFE 0х70 0х08…. Дизассемблер разбивает этот код на следующие коды операции:

(1): 0хАВ

(2): 0хЕ9 0х00 0хFE 0х70 0х08

(3): … .

Первый код операции имеет длину один байт, второй код операции имеет длину пять байт, а дополнительные коды операции различной длины идентифицируются аналогичным образом.

Память 101 содержит несколько тридцати двух битовых блоков 101-104. В других вариантах осуществления изобретения блоки памяти могут иметь длину шестьдесят четыре бита или какую-либо другую длину. На фиг. 1А показано исходное состояние в котором вся память 101 заполнена однобайтовыми кодами операции отладочной точки останова (0хСС). Если в данный момент времени поток считывает инструкции из памяти 101, то код операции отладочной точки останова будет побуждать обработчик потока к попытке загрузить код в память 101, после чего поток предпримет повторную попытку считывания кода.

На фиг. 1В первый код операции 0хАВ был считан в тридцати двух разрядный блок 102b. Первый, однобайтовый код операции 0хАВ записан в память 101 с использованием атомарной записи, которая заменяет первый код операции 0хСС. Операция записи нужна для записи тридцати двух бит данных. Поскольку упомянутая инструкция была дизассемблирована перед записью в память, операция записи отслеживает, какие байты в данный момент записываются, и знает, что необходимо заполнить остальные двадцать четыре бита блока 102b посредством 0хСС, чтобы заполнить весь тридцати двух битовый блок. Если процессор исполняет первую инструкцию 0хАВ, это будет успешно выполнено. Однако, если процессор попытается в это же время исполнить вторую инструкцию, то будет считана отладочная точка останова 0хСС, и в работу вступит механизм повторной попытки обработки сбоя потока.

Теперь обработчик сбоя потока должен записать второй код операции (то есть, 0хЕ9 0х00 0хFE 0х70 0х08). Обработчик сбоя потока знает, что предыдущая инструкция (0хАВ) была записана, и знает, как были записаны блоки 102b-104b. Обработчик сбоя потока также знает, какова длина следующего кода, и каким образом его следует записать в память 101. В частности, обработчик сбоя потока знает, что второй пятибайтовый код операции будет записан в блоках 102b и 103b после кода операции 0хАВ. Обработчик сбоя потока также определяет, что второй код операции не впишется в оставшееся пространство в одном тридцати двух битовом блоке 102b. Следовательно, второй код операции должен быть разделен между блоками 102b и 103b памяти.

Как показано на фиг. 1С вторая часть кода операции (то есть, 0х70 0х08) записана в блок 103c (дополненный отладочными точками 0х00 останова для заполнения тридцати двух бит) перед записью первой части кода операции. Благодаря записи второй части кода операции первой, если процессор исполняет код операции после блока 0хАВ, то он столкнется со сбоем отладки (0хСС) и не предпримет попытку обработки «мусора».

После записи второй части кода операции в блок 103с, можно записать в память 101 вторую часть (то есть, 0хЕ9 0х00 0хFE). Как показано на фиг. 1D, указанная первая часть записана первым кодом операции 0хАВ на позиции, которая была ранее выделена в блоке 102d. В этот момент процессор способен успешно исполнить обе инструкции. Этот процесс записи инструкций в память 101 может применяться кода операции за кодом операции, пока вся страница не станет резидентной.

На фиг. 2 показана система для потоковой передачи свободных от блокирования данных исполняемого кода согласно одному варианту осуществления настоящего изобретения. Приложение, выполняющееся на операционной системе 201, пытается выполнить считывание страницы 202 данных из памяти. При вызове нерезидентной страницы исполняемой памяти запускается исключение 203 операционной системы, которое уведомляет операционную систему 201 о том, что данный вызов не пройден. Операционная система 201 отправляет код возврата сбоя считывания в перехватчик 204 сбоя потока, прежде чем приложение увидит этот сбой. Перехватчик 204 сбоя потока просматривает указанную страницу в своей базе данных и определяет, что необходимо извлечь эту страницу. Перехватчик 204 сбоя потока выполняет сетевой вызов, чтобы получить страницу, например, от сетевого сервера 205, и изменяет доступ к этой странице таким образом, чтобы в страницу 202 данных можно было записывать данные.

В существующих системах перехватчику 204 сбоя потока необходимо приостанавливать процесс, который запросил упомянутые данные. Если процесс не приостановлен, то тогда другой поток может исполнить данные на странице 202, как это было записано в память, и этот процесс аварийно завершится при попытке исполнения частичных данных. После записи страницы 202 в память процесс может быть возобновлен перехватчиком сбоя потока, изменяющим исключение операционной системы на «успешно», после чего приложение продолжает выполняться.

В существующих системах этот этап приостановки всего процесса необходим потому, что изменение доступа к странице 202 данных и запись данных на нее не может выполняться на одном этапе. Это означает, что два потока в упомянутом процессе, не могут исполняться при обслуживании сбоя потока.

Существующие системы улучшены здесь посредством добавления дизассемблера 206 и трекера 207 записанной/незаписанной страницы. Дизассемблер 206 отвечает за получение возвращенного байтового кода и его дизассемблирование. Дизассемблер 206 возвращает список смещений, которые содержат границы каждого кода операции. Как отмечалось в примере на фиг. 1, каждый код операции может иметь длину в один или более байтов. Средство 207 отслеживания записанной/незаписанной страницы содержит список смещений, созданных дизассемблером 206, а также список тех смещений, которые были зафиксированы.

Процесс нет необходимости приостанавливать при использовании дизассемблера 206 и средства 207 отслеживания записанной/незаписанной страницы. Вместо этого, после того как запрошенный код вернулся в перехватчик сбоя потока из сервера 205, выполняется вызов дизассемблера для создания карты смещений. Затем эта карта смещений сохраняется перехватчиком 204 сбоя потока, который начинает запись кодов операции на страницу 202 данных код операции за кодом операции, как было описано выше. Перехватчик 204 сбоя потока использует эту карту смещений, чтобы определить границу каждого кода операции. Перехватчик 204 сбоя потока может записать коды операции на страницу 202 данных в любом подходящем порядке, начиная либо с начала, либо с конца списка кодов операции.

При появлении какой-либо конфликтной ситуации, например, если процессор исполняет частично заполненную инструкцию, то тогда будет запущен механизм 203 сбоя операционной системы. Это приведет к вызову операционной системой 201 перехватчика 204 сбоя потока. Перехватчик 204 сбоя потока обращается к трекеру средству 207 отслеживания записанной/незаписанной и записывает сам код операции на страницу 202 данных или ждет, пока другой поток не закончит запись данных. Затем перехватчик 204 сбоя потока предпринимает новую попытку упомянутого исключения.

На фиг. 3 представлена блок-схема процесса или способа потоковой передачи данных исполняемого кода согласно одному варианту осуществления настоящего изобретения. На этапе 301 процессор принимает инструкции, содержащие множество кодов операции. Каждый из кодов операции может содержать один или более байтов данных. На этапе 302 используют дизассемблер для дизассемблирования инструкций на отдельные коды операции. На этапе 303 создают таблицу, идентифицирующую границы каждым кодом операции. Эта таблица может быть сохранена, например, в средстве отслеживания записанной/незаписанной страницы. На этапе 304 каждый код операции записывается в память код операции за кодом операции посредством атомарной записи стандартных блоков памяти. Коды операции могут быть записаны в память, например, перехватчиком сбоя потока.

В некоторых вариантах коды операции отладочной точки останова могут быть записаны во все участки памяти для инициализации памяти. Когда указанные коды операции записаны в память, коды операции отладочной точки останова могут быть добавлены к указанному коду операции для создания полного стандартного блока памяти. Длина стандартного блока памяти может составлять, например, тридцать два бита или шестьдесят четыре бита.

Когда длинный код операции перекрывает два или более стандартных блока памяти, его можно разделить на две части. Вторую часть длинного кода операции записывают во второй блок памяти, а затем в первый блок памяти записывают первую часть длинного кода операции. Такая запись длинного кода операции гарантирует то, что появится отладочная точка останова, если считывание участка памяти выполняется перед записью всего кода операции. Коды операции отладочной точки останова могут быть добавлены ко второй части длинного кода операции для создания полного стандартного блока памяти. Предшествующий код операции может быть записан вместе с первой частью длинного кода операции в первый блок памяти.

Понятно, что этапы 301-305 процесса, показанного на фиг. 3, могут исполняться одновременно и/или последовательно. Кроме того, понятно, что каждый этап может выполняться в любом порядке или может выполняться один раз или с повторами.

На фиг. 4 показан пример подходящей вычислительной и сетевой среды 400, в которой можно реализовать примеры по фигурам 1-3 для обеспечения свободной от блокирования потоковой передачи данных исполняемого кода. Вычислительная среда 400 системы является лишь одним примером подходящей вычислительной среды, не претендующим на ограничение в отношении объема использования или функциональных возможностей изобретения. Изобретение может работать с множеством других сред или конфигураций вычислительных систем общего назначения или специализированных вычислительных систем. Примеры широко известных вычислительных систем, сред и/или конфигураций, которые могут подойти для использования с настоящим изобретением, включают в себя, но не только: персональные компьютеры, компьютеры-серверы, карманные устройства или устройства типа лэптоп, планшетные устройства, мультипроцессорные системы, системы на основе микропроцессоров, телевизионные приставки, электронные системы, программируемые пользователем, сетевые персональные компьютеры, миникомпьютеры, суперкомпьютеры, распределенные вычислительные среды, включающие в себя любую из вышеуказанных систем или устройств, и т.п.

Изобретение может быть описано в общем контексте исполняемых компьютером инструкций, таких как программные модули, исполняемые компьютером. В общем случае программные модули включают в себя стандартные программы, программы, объекты, компоненты, структуры данных и т.д., которые выполняют конкретные задачи или реализуют конкретные типы абстрактных данных. Изобретение также можно практически реализовать в распределенных вычислительных средах, где задачи выполняются удаленными обрабатывающими устройствами, связанными через сеть связи. В распределенной вычислительной среде программные модули могут находиться как на местном, так и на удаленном компьютерном носителе, включая устройства памяти.

Как показано на фиг. 4, примерная система для реализации изобретения включает в себя вычислительное устройство общего назначения в виде компьютера 400. Компоненты компьютера 400 могут включать в себя различные аппаратные компоненты, такие как, но не только: блок 401 обработки, хранилище 402 данных, такое как системная память, и системную шину 403, которая связывает различные системные компоненты, включая хранилище 402 данных, с блоком 401 обработки. Системная шина 403 может представлять собой любую из шинных структур нескольких типов, в том числе шину памяти или контроллер памяти, периферийную шину и локальную шину, использующую любую из множества различных шинных архитектур. Такие архитектуры могут, например, включать в себя, но не только: архитектуру промышленного стандарта (ISA), микроканальную архитектуру (MCA), расширенную архитектуру ISA (EISA), локальную шину Ассоциации по стандартам видеооборудования (VESA), и шину межсоединений периферийных компонентов (PCI) (известную также как шина Mezzanine).

Компьютер 400 обычно включает в себя множество различных считываемых компьютером носителей 404. Считываемый компьютером носитель 404 может представлять собой любой имеющийся носитель, который может быть доступен компьютеру 400, и может включать в себя как энергозависимый, так и энергонезависимый носитель, а также как съемный, так и несъемный носитель, за исключением распространяемых сигналов. В качестве примера, но не как ограничение, считываемый компьютером носитель 404 может содержать компьютерный носитель данных и среду связи. Компьютерный носитель данных включает в себя энергозависимый и энергонезависимый, съемный и несъемный носитель, реализованный любым способом или по любой технологии для сохранения информации, такой как считываемые компьютером инструкции, структуры данных, программные модули или другие данные. Компьютерный носитель данных включает в себя, но не только: ОЗУ (RAM), ПЗУ (ROM), электрически стираемое программируемое ПЗУ (EEPROM), флэш-память, либо память, выполненную по другой технологии, ПЗУ на компакт-диске (CD ROM), цифровые универсальные диски (DVD), либо другое запоминающее устройство на оптическом диске, магнитные кассеты, магнитную ленту, запоминающее устройство на магнитном диске или другие магнитные запоминающие устройства, либо любую другую среду, которую можно использовать для сохранения требуемой информации и которая может быть доступна компьютеру 400. Среда связи обычно несет считываемые компьютером инструкции, структуры данных, программные модули либо другие данные в модулированном сигнале данных, таком как сигнал несущей или другой механизм транспортировки, и включает в себя любую среду для доставки информации. Термин «модулированный сигнал данных» означает сигнал, имеющий одну или более характеристик, установленных или измененных таким образом, чтобы закодировать информацию в этом сигнале. Например, но не как ограничение, среда связи включает в себя проводную среду, такую как проводная сеть или непосредственное проводное соединение, и беспроводную среду, такую как акустическая, радиочастотная (RF), инфракрасная и другие беспроводные среды. В состав считываемых компьютером носителей также следует включить комбинации из любых вышеперечисленных сред. Считываемый компьютером носитель может быть воплощен в виде компьютерного программного продукта, такого как программное обеспечение, хранящееся в компьютерном носителе данных.

Хранилище данных или системная память 402 включает в себя компьютерный носитель данных в виде энергозависимой и/или энергонезависимой памяти, такой как постоянное запоминающее устройство (только для считывания) (ROM) и оперативное запоминающее устройство (с произвольной выборкой) (RAM). Память 402 или считываемый компьютером носитель 404 может быть использована для сохранения страниц данных, списков границ кодов операции, самих кодов операции и т.п. В памяти ROM обычно хранится базовая система ввода/вывода (BIOS), содержащая базовые подпрограммы, которые помогают пересылать информацию между элементами в компьютере 400, например, во время запуска. Память RAM обычно содержит данные и/или программные модули, которые непосредственно доступны и/или обрабатываются в настоящий момент в блоке 401 обработки. Например, но не как ограничение, в хранилище 402 данных хранится операционная система, прикладные программы и другие программные модули и программные данные. Операционная система, действующая в блоке 402 обработки, может поддерживать такие функции, как исключение 203 операционной системы, перехватчик 204 сбоя потока, дизассемблер 206 и/или средство 207 отслеживания записанной/незаписанной страницы (фиг. 2).

Хранилище 402 данных может также включать в себя другие съемные/несъемные, энергозависимые/энергонезависимые компьютерные носители данных. Только в качестве примера хранилище 402 данных может представлять собой накопитель на жестком диске, который осуществляет считывание или запись на несъемный, энергонезависимый магнитный носитель; накопитель на магнитном диске, который осуществляет считывание или запись на съемный энергонезависимый магнитный диск; и дисковод на оптическом диске, который осуществляет считывание или запись на съемный энергонезависимый оптический диск, такой как CD ROM либо другую оптическую среду. Другие съемные/несъемные энергозависимые/энергонезависимые компьютерные носители данных, которые можно использовать в приведенной в качестве примере операционной среде, включают в себя, но не только: кассеты с магнитной лентой, карты флэш-памяти, цифровые универсальные диски, цифровую видеоленту, твердотельное RAM, твердотельное ROM и т.п. Накопители и связанные с ними компьютерные носители данных, обсужденные выше и показанные на фиг. 4, обеспечивают сохранение считываемых компьютером инструкций, структур данных, программных модулей и других данных для компьютера 400.

Пользователь может вводить инструкции и информацию через пользовательский интерфейс 405 или другие устройства ввода, такие как планшет, электронный цифровой планшет, микрофон, клавиатура и/или указательное устройство, известное как «мышь», шаровой манипулятор или воспринимающая касание (сенсорная) панель. Другие устройства ввода могут включать в себя джойстик, игровую приставку, спутниковую антенну, сканер или т.п. Вдобавок, также могут быть использованы устройства голосового ввода, устройства для ввода жестов с использованием рук или пальцев или другой естественный пользовательский интерфейс NUI вместе с соответствующими устройствами ввода, такими как микрофон, камера, планшет, воспринимающая касание панель, управляющая перчатка или датчик иного типа. Эти и другие устройства ввода часто подсоединены к блоку 401 обработки через входной интерфейс 405 пользователя, который соединен с системной шиной 403, но могут быть подсоединены с помощью других интерфейсных и шинных структур, таких как параллельный порт, игровой порт или универсальная последовательная шина (USB). К системной шине 403 через интерфейс, такой как видеоинтерфейс, также подсоединен монитор 406 либо устройство отображения другого типа. Монитор 406 также может составлять единое целое с панелью с воспринимающим касание экраном или т.п. Заметим, что монитор и/или панель с воспринимающим касание экраном могут быть физически связаны с корпусом, в котором размещено вычислительной устройство 400, например, в персональном компьютере планшетного типа. Вдобавок, компьютеры, такие как вычислительное устройство 400, могут также включать в себя другие периферийные устройства вывода, такие как динамики и принтер, которые могут быть подсоединены через периферийный интерфейс вывода или т.п.

Компьютер 400 может работать в сетевой среде или среде облачных вычислений, используя логические соединения 407 с одним или более удаленными устройствами, такими как удаленный компьютер. Удаленный компьютер может представлять собой персональный компьютер, сервер, маршрутизатор, сетевой персональный компьютер, равноправное устройство либо другой известный сетевой узел, причем такой компьютер обычно включает в себя многие или все элементы, описанные выше в связи с компьютером 400. Логические соединения, изображенные на фиг. 4, включают в себя одну или более локальных сетей (LAN) и одну или более глобальных сетей (WAN), но также могут включать другие сети. Такие сетевые среды типичны для офисов, корпоративных компьютерных сетей, интрасетей и Интернет.

При использовании сетевой среды или среды для облачных вычислений компьютер 400 может быть подсоединен к сети общего пользования или частной сети через сетевой интерфейс или адаптер 407. Сетевой интерфейс 407 может обеспечить соединение с удаленным устройством, таким как сетевой сервер 205 (фиг. 2). В некоторых вариантах может быть обеспечен модем либо другое средство для установления связи через сеть. Модем, который может быть встроенным или внешним, может быть подсоединен к системной шине 403 через сетевой интерфейс 407 либо другой подходящий механизм. С сетью через подходящее устройство, такое как точка доступа или равноправный компьютер, может быть связана беспроводная сетевая компонента, содержащая, например, интерфейс и антенну. В сетевой среде программные модули, относящиеся к компьютеру 400 или его частям, могут храниться в удаленном запоминающем устройстве. Очевидно, что показанные сетевые соединения являются лишь примерами, и что могут быть использованы другие средства установления линии связи между упомянутыми компьютерами.

Хотя предмет настоящего изобретения был описан на языке, специфичном для структурных признаков и/или методологических действий, должно быть ясно, что определенное в прилагаемой формуле изобретения изобретение не следует ограничивать указанными специфическими признаками или действиями, описанными выше. Скорее, вышеописанные специфические признаки и действия раскрыты в качестве примеров реализации формулы изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА И СПОСОБ ПРОВЕРКИ ИСПОЛНЯЕМОГО КОДА ПЕРЕД ЕГО ВЫПОЛНЕНИЕМ | 2012 |

|

RU2510074C2 |

| СПОСОБ ПЕРЕВЫЗОВА ОРИГИНАЛЬНОЙ ФУНКЦИИ ПОСЛЕ ЕЕ ПЕРЕХВАТА С СОХРАНЕНИЕМ СТЕКА ПАРАМЕТРОВ | 2013 |

|

RU2546588C2 |

| Способ обнаружения аномальных событий на основании набора сверток безопасных событий | 2017 |

|

RU2673711C1 |

| СПОСОБ СОЗДАНИЯ ОБРАБОТЧИКА СИСТЕМНЫХ ВЫЗОВОВ | 2014 |

|

RU2596577C2 |

| Способ обнаружения аномальных событий по популярности свертки события | 2017 |

|

RU2651196C1 |

| СПОСОБ ВЫЗОВА СИСТЕМНЫХ ФУНКЦИЙ В УСЛОВИЯХ ИСПОЛЬЗОВАНИЯ СРЕДСТВ ЗАЩИТЫ ЯДРА ОПЕРАЦИОННОЙ СИСТЕМЫ | 2014 |

|

RU2585978C2 |

| СИСТЕМЫ И СПОСОБЫ ПРЕДОСТАВЛЕНИЯ РЕЗУЛЬТАТА ТЕКУЩЕЙ КОМАНДЫ ПРОЦЕССОРА ПРИ ВЫХОДЕ ИЗ ВИРТУАЛЬНОЙ МАШИНЫ | 2015 |

|

RU2686552C2 |

| ОБЩАЯ РАСПАКОВКА ПРИЛОЖЕНИЙ ДЛЯ ОБНАРУЖЕНИЯ ВРЕДОНОСНЫХ ПРОГРАММ | 2014 |

|

RU2632163C2 |

| ОБЩАЯ РАСПАКОВКА ПРИЛОЖЕНИЙ ДЛЯ ОБНАРУЖЕНИЯ ВРЕДОНОСНЫХ ПРОГРАММ | 2014 |

|

RU2658132C1 |

| ОТЛАДКА МАШИННОГО КОДА ПУТЕМ ПЕРЕХОДА ОТ ИСПОЛНЕНИЯ В СОБСТВЕННОМ РЕЖИМЕ К ИСПОЛНЕНИЮ В ИНТЕРПРЕТИРУЕМОМ РЕЖИМЕ | 2014 |

|

RU2668973C2 |

Изобретение относится к средствам для потоковой передачи исполняемого кода. Технический результат заключается в предотвращении приостановки потока при каждом сбое потоковой передачи. Принимают инструкции, содержащие множество кодов операции, при этом каждый код операции содержит один или более байтов данных. Дизассемблируют инструкции на отдельные коды операции. Создают таблицу, идентифицирующую границы между каждым кодом операции. Добавляют коды операции отладочной точки останова к коду операции для создания полного стандартного блока памяти. Записывают каждый код операции в память, код операции за кодом операции, посредством атомарной записи стандартных блоков памяти. 3 н. и 15 з.п. ф-лы, 7 ил.

1. Реализуемый компьютером способ для потоковой передачи исполняемого кода, содержащий:

прием инструкций, содержащих множество кодов операции,

при этом каждый код операции содержит один или более байтов данных;

дизассемблирование инструкций на отдельные коды операции;

создание таблицы, идентифицирующей границы между каждым кодом операции;

добавление кодов операции отладочной точки останова к коду операции для создания полного стандартного блока памяти; и

запись каждого кода операции в память, код операции за кодом операции, посредством атомарной записи стандартных блоков памяти.

2. Реализуемый компьютером способ по п. 1, дополнительно содержащий:

запись кодов операции отладочной точки останова во все участки памяти для инициализации памяти.

3. Реализуемый компьютером способ по п. 1, в котором длина стандартного блока памяти составляет тридцать два бита или шестьдесят четыре бита.

4. Реализуемый компьютером способ по п. 1, дополнительно содержащий:

идентификацию, когда длинный код операции будет перекрывать два или более стандартных блока памяти;

запись второй части длинного кода операции во второй блок памяти и

запись первой части длинного кода операции в первый блок памяти.

5. Реализуемый компьютером способ по п. 4, дополнительно содержащий:

добавление кодов операции отладочной точки останова ко второй части длинного кода операции для создания полного стандартного блока памяти.

6. Реализуемый компьютером способ по п. 5, дополнительно содержащий:

запись предшествующего кода операции и первой части длинного кода операции в первый блок памяти.

7. Компьютерная система, содержащая:

процессор;

системную память;

один или более считываемых компьютером носителей данных с хранимыми на них исполняемыми компьютером инструкциями, которые при исполнении одним или более процессорами побуждают процессор к выполнению способа для потоковой передачи исполняемого кода, причем процессор функционирует для:

приема инструкций, содержащих множество кодов операции, при этом каждый код операции содержит один или более байтов данных;

дизассемблирования инструкций на отдельные коды операции;

создания таблицы, идентифицирующей границы между каждым кодом операции;

записи каждого кода операции в память, код операции за кодом операции, посредством атомарной записи стандартных блоков памяти; и

добавления кодов операции отладочной точки останова к коду операции для создания полного стандартного блока памяти.

8. Компьютерная система по п. 7, причем процессор дополнительно функционирует для:

записи кодов операции отладочной точки останова во все участки памяти для инициализации памяти.

9. Компьютерная система по п. 7, при этом длина стандартного блока памяти составляет тридцать два бита или шестьдесят четыре бита.

10. Компьютерная система по п. 7, причем процессор дополнительно функционирует для:

идентификации, когда длинный код операции будет перекрывать два или более стандартных блока памяти;

записи второй части длинного кода операции во второй блок памяти и

записи первой части длинного кода операции в первый блок памяти.

11. Компьютерная система по п. 10, причем процессор дополнительно функционирует для:

добавления кодов операции отладочной точки останова ко второй части длинного кода операции для создания полного стандартного блока памяти.

12. Компьютерная система по п. 10, причем процессор дополнительно функционирует для:

записи предыдущего кода операции и первой части длинного кода операции в первый блок памяти.

13. Компьютерная система по п. 7, дополнительно содержащая:

перехватчик сбоя потока, функционирующий для идентификации, когда запрашиваемая страница данных недоступна; и

извлечения этой страницы данных из удаленного источника.

14. Компьютерная система по п. 7, дополнительно содержащая:

дизассемблер, функционирующий для дизассемблирования инструкций на отдельные коды операций.

15. Компьютерная система по п. 7, дополнительно содержащая:

средство отслеживания страницы, поддерживающей таблицу, которая идентифицирует границы между каждым кодом операции.

16. Считываемый компьютером носитель, хранящий исполняемые компьютером инструкции, которые, при исполнении по меньшей мере одним процессором, побуждают этот по меньшей мере один процессор выполнять способ для потоковой передачи данных исполняемого кода, содержащий:

прием сбоя, указывающего, что страница данных недоступна;

запрос инструкций, включающих в себя эту страницу данных;

прием этих инструкций из удаленного источника, причем инструкции содержат множество кодов операций, причем каждый код операции содержит один или более байтов данных;

дизассемблирование инструкций на отдельные коды операций;

создание таблицы, идентифицирующей границы между каждым кодом операции;

идентификацию, когда длинный код операции будет перекрывать два или более стандартных блока памяти;

запись каждого кода операции в память, код операции за кодом операции, посредством атомарной записи стандартных блоков памяти;

запись второй части длинного кода операции во второй блок памяти и

запись первой части длинного кода операции в первый блок памяти.

17. Считываемый компьютером носитель по п. 16, при этом способ дополнительно содержит добавление кодов операции отладочной точки останова к коду операции для создания полного стандартного блока памяти.

18. Считываемый компьютером носитель по п. 16, при этом длина стандартного блока памяти составляет тридцать два бита или шестьдесят четыре бита.

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| US 6408382 B1, 18.06.2002 | |||

| РАСШИРЕНИЕ НАБОРА КОМАНД С ИСПОЛЬЗОВАНИЕМ 3-БАЙТОВОГО КОДА ОПЕРАЦИИ ПЕРЕХОДА | 2004 |

|

RU2288502C2 |

Авторы

Даты

2017-12-20—Публикация

2013-07-26—Подача