изобретение относится к обработке аудиосигнала и, в частности, к принципу декодирования кодированного аудиосигнала с использованием сниженных вычислительных ресурсов.

Стандарт "Unified speech and audio coding" (USAC) [1] стандартизирует инструмент гармонического расширения полосы, HBE, использующий гармонический транспозитор, и являющийся расширением системы копирования спектральной полосы (SBR), стандартизованной в [1] и [2] соответственно.

SBR синтезирует высокочастотное содержимое аудиосигналов ограниченной ширины полосы с использованием данной низкочастотной части совместно с данной вспомогательной информацией. Инструмент SBR описан в [2], улучшенный SBR, eSBR, описан в [1]. Гармоническое расширение полосы HBE, которое использует фазовые вокодеры, входит в состав eSBR и было разработано во избежание грубости звука, которая часто наблюдается в сигналах, подвергнутых патчированию для улучшающего копирования, поскольку оно осуществляется при обычной обработке SBR. HBE служит, в основном, для сохранения гармонических структур в синтезированной высокочастотной области данного аудиосигнала с применением eSBR.

В то время, как кодер может выбирать использование инструмента HBE, декодер, согласующийся с [1], должен обеспечивать декодирование и применение данных, связанных с HBE.

Пробное прослушивание [3] показало, что использование HBE повышает воспринимаемое качество аудиосигнала декодированных битовых потоков согласно [1].

Инструмент HBE заменяет простое патчирование для улучшающего копирования традиционной системы SBR усовершенствованными процедурами обработки сигнала. Для этого требуются значительные объемы вычислительной мощности и памяти для состояний фильтра и линий задержки. Напротив, сложность патчирования для улучшающего копирования пренебрежимо мала.

Наблюдаемое увеличение сложности при использовании HBE не является проблемой для персональных вычислительных устройств. Однако производители микросхем, проектирующие микросхемы декодеров, налагают жесткие и низкие ограничения по сложности, касающиеся рабочей вычислительной нагрузки и расходования памяти. В противном случае, во избежание грубости звука желательна обработка HBE.

Битовые потоки USAC декодируются, как описано в [1]. Отсюда следует необходимость реализации инструмента декодера HBE, как описано в [1], 7.5.3. Инструмент может сигнализироваться во всех рабочих точках кодека, которые содержат обработку eSBR. Для устройств декодера, которые удовлетворяют профилю и критериям соответствия [1], это означает, что, в целом, вычислительная рабочая нагрузка и расходование памяти в наихудшем случае значительно возрастаЮт.

Фактическое увеличение вычислительной сложности зависит от реализации и платформы. Увеличение расходования памяти в расчете на аудиоканал, в текущей реализации, оптимизированной по памяти, составляет, по меньшей мере, 15 килослов для фактической обработки HBE.

Задачей настоящего изобретения является обеспечение усовершенствованного принципа декодирования кодированного аудиосигнала, менее сложного и, тем не менее, пригодного для обработки существующих кодированных аудиосигналов.

Эта задача решается посредством устройства для декодирования кодированного аудиосигнала по п.1, способа декодирования кодированного аудиосигнала по п.13 или компьютерной программы по п.14.

Настоящее изобретение основано на обнаружении того факта, что принцип аудиодекодирования, требующий сниженных ресурсов памяти, достигается, когда аудиосигнал, состоящий из участков, подлежащих декодированию с использованием режима гармонического расширения полосы и дополнительно содержащий участки, подлежащие декодированию с использованием режима негармонического расширения полосы, декодируется, на протяжении всего сигнала, только в режиме негармонического расширения полосы. Другими словами, даже когда сигнал содержит участки или кадры, которые сигнализируются, подлежащие декодированию с использованием режима гармонического расширения полосы, эти участки или кадры, тем не менее, декодируются с использованием режима негармонического расширения полосы. Для этого предусмотрен процессор для декодирования аудиосигнала с использованием режима негармонического расширения полосы и, дополнительно, контроллер реализован в устройстве, или этап управления реализован в способе декодирования для управления процессором для декодирования аудиосигнала с использованием второго режима негармонического расширения полосы даже когда данные управления расширением полосы, включенные в кодированный аудиосигнал, указывает первый - т.е. гармонический - режим расширения полосы для аудиосигнала. Таким образом, процессор нужно реализовать только с соответствующими аппаратными ресурсами, например, памятью и вычислительной мощностью, допускающими только очень вычислительно эффективный режим негармонического расширения полосы. С другой стороны, аудиодекодер, тем не менее, в позиции для приема и декодирования кодированного аудиосигнала, требующего режим гармонического расширения полосы с приемлемым качеством. Другими словами, для приложений, требующих низких вычислительных ресурсов, контроллер выполнен с возможностью управления процессором для декодирования всего аудиосигнала в режиме негармонического расширения полосы, хотя сам кодированный аудиосигнал требует, в силу включенных данных управления расширением полосы, чтобы, по меньшей мере, несколько участков этого сигнала декодировались с использованием режима гармонического расширения полосы. Таким образом, достигается хороший компромисс между вычислительными ресурсами, с одной стороны, и качеством аудиосигнала, с другой стороны, в то же время поддерживается полная обратная совместимость с кодированными аудиосигналами, требующими обоих режимов расширения полосы. Преимущество настоящего изобретения состоит в снижении вычислительной сложности и необходимой памяти, в частности, декодера USAC. Кроме того, в предпочтительных вариантах осуществления, заранее определенный или стандартизованный режим негармонического расширения полосы модифицируется с использованием данных режима гармонического расширения полосы, передаваемые в битовом потоке для повторного использования данных режима расширения полосы, которые, в основном, не требуются для режима негармонического расширения полосы, насколько возможно, для дополнительного повышения качества аудиосигнала режима негармонического расширения полосы. Таким образом, в этом предпочтительном варианте осуществления предусмотрена альтернативная схема декодирования, для ослабления ухудшения воспринимаемого качества, обусловленного пропуском режима гармонического расширения полосы, который обычно основан на обработке фазовым вокодером, как рассмотрено в стандарте USAC [1].

Согласно варианту осуществления, процессор располагает достаточными ресурсами памяти и обработки для декодирования кодированного аудиосигнала с использованием второго режима негармонического расширения полосы, и при этом ресурсов памяти или обработки достаточно для декодирования кодированного аудиосигнала с использованием первого режима гармонического расширения полосы, когда кодированный аудиосигнал является кодированным стереофоническим или многоканальным аудиосигналом. Напротив, процессор располагает достаточными ресурсами памяти и обработки для декодирования кодированного аудиосигнала с использованием второго режима негармонического расширения полосы и с использованием первого режима гармонического расширения полосы, когда кодированный аудиосигнал является кодированным монофоническим сигналом, поскольку ресурсы для декодирования монофонического сигнала снижены по сравнению с ресурсами для декодирования стереофонического или многоканального сигнала. Следовательно, доступные ресурсы зависят от конфигурации битового потока, т.е. комбинации инструментов, частоты дискретизации и т.д. Например, существует возможность того, что ресурсов достаточно для декодирования монофонического битового потока с использованием гармонического BWE, но процессору не хватает ресурсов для декодирования стереотаксического битового потока с использованием гармонического BWE.

Далее, предпочтительные варианты осуществления рассмотрены в контексте прилагаемых чертежей, в которых:

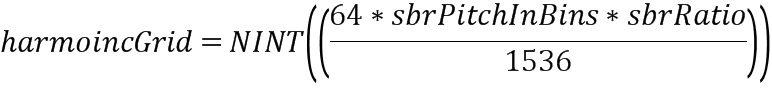

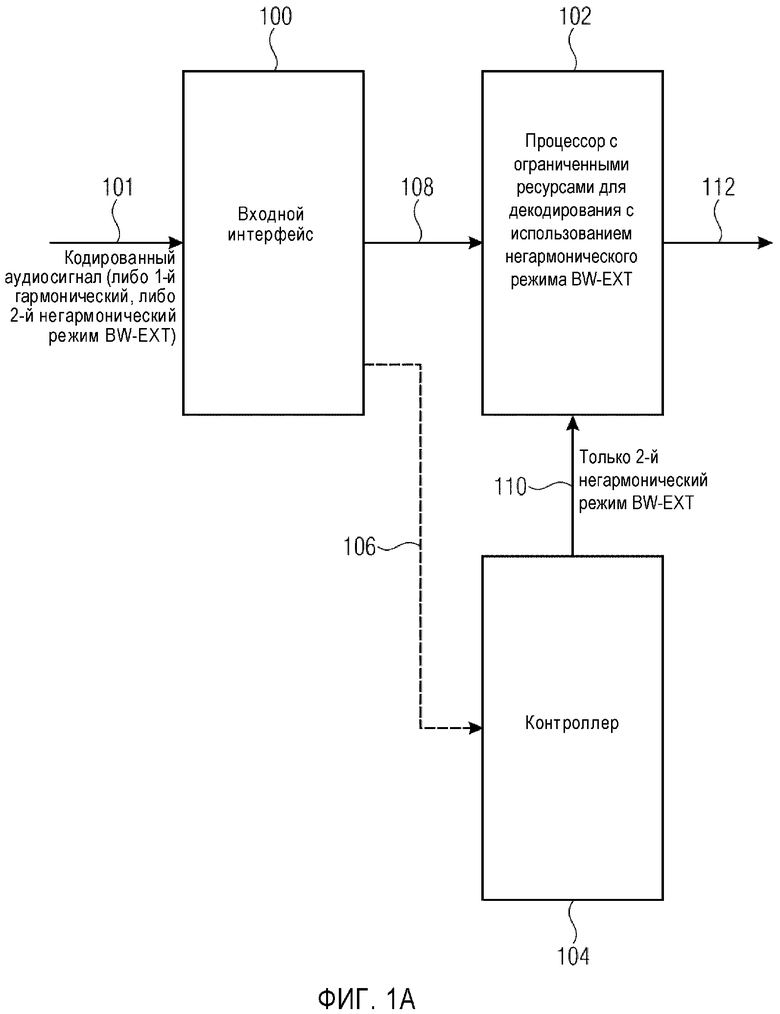

фиг.1a демонстрирует вариант осуществления устройства для декодирования кодированного аудиосигнала с использованием процессора с ограниченными ресурсами;

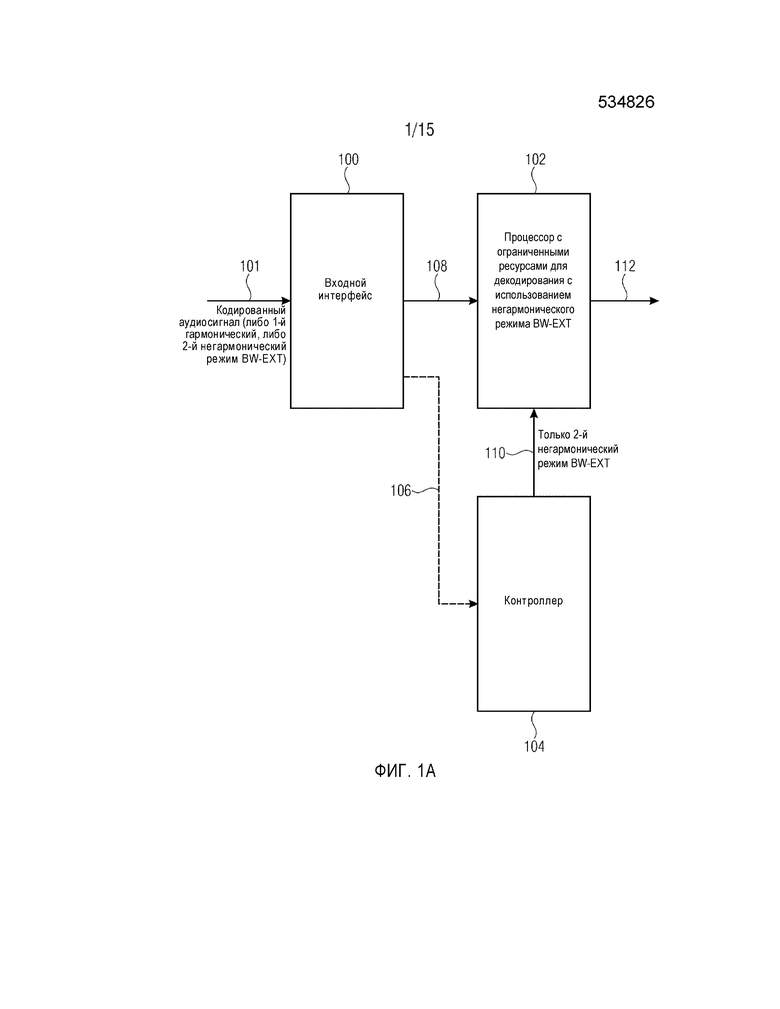

фиг.1b демонстрирует пример кодированных данных аудиосигнала для обоих режимов расширения полосы;

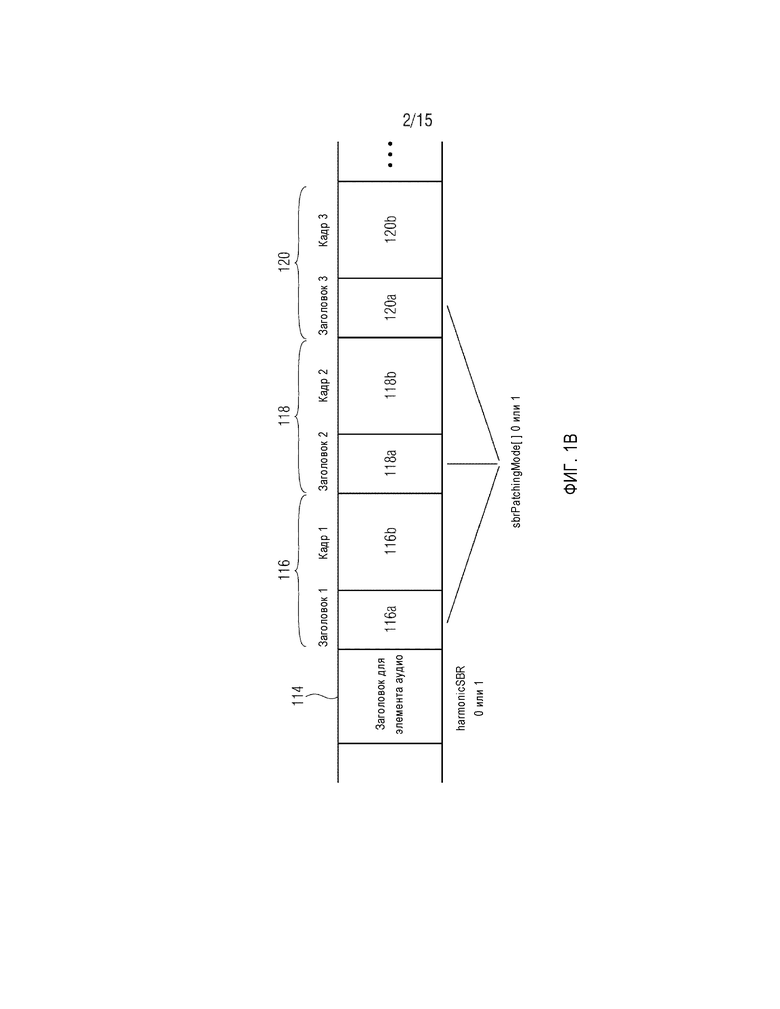

фиг.1c демонстрирует таблицу, иллюстрирующую стандартный декодер USAC и новый декодер;

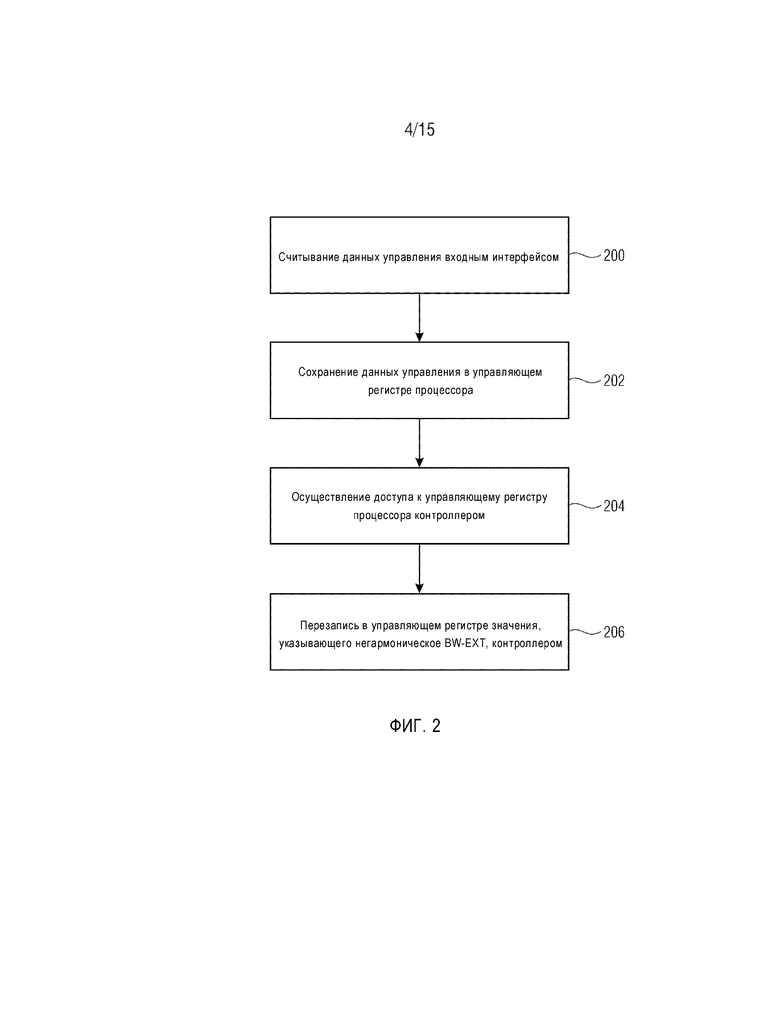

фиг.2 демонстрирует блок-схему операций варианта осуществления для реализации контроллера, показанного на фиг.1a;

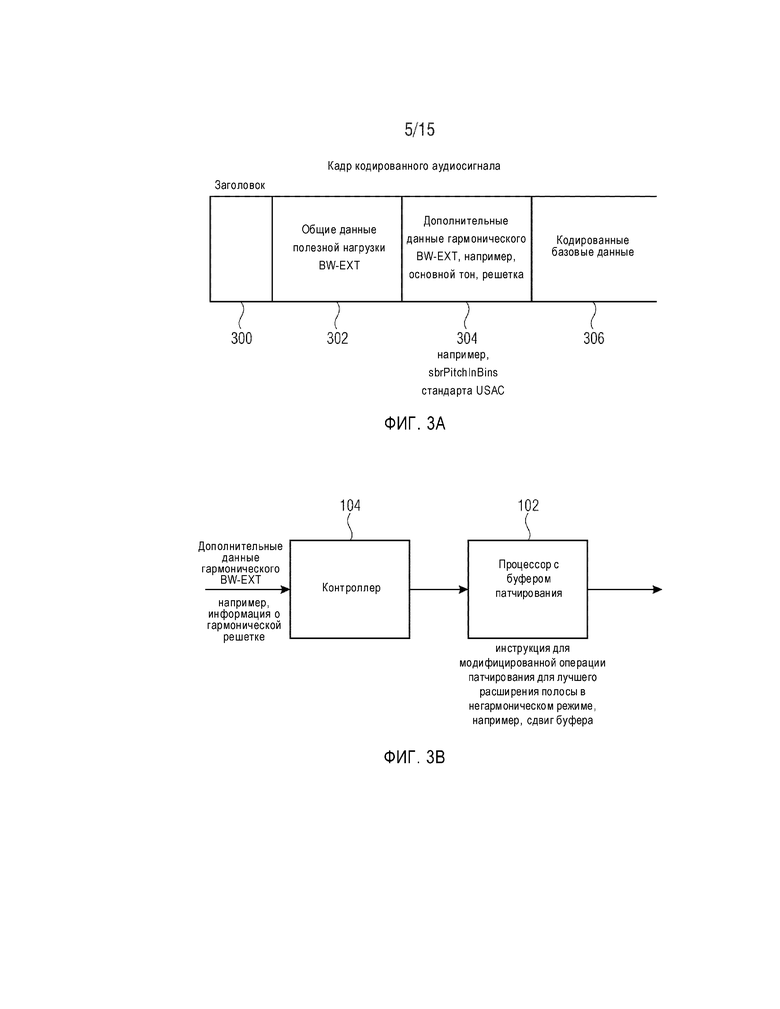

фиг.3a дополнительно демонстрирует структуру кодированного аудиосигнала, имеющего общие данные полезной нагрузки расширения полосы и дополнительные данные гармонического расширения полосы;

фиг.3b демонстрирует реализацию контроллера для модификации стандартного режима негармонического расширения полосы;

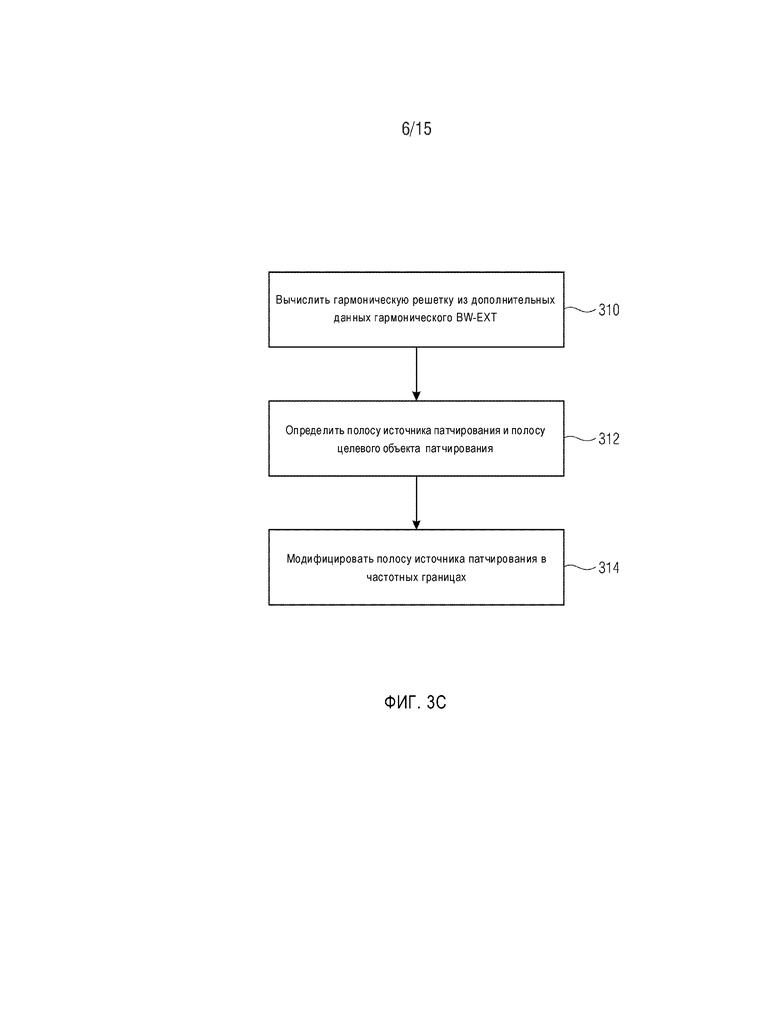

фиг.3c дополнительно демонстрирует реализацию контроллера;

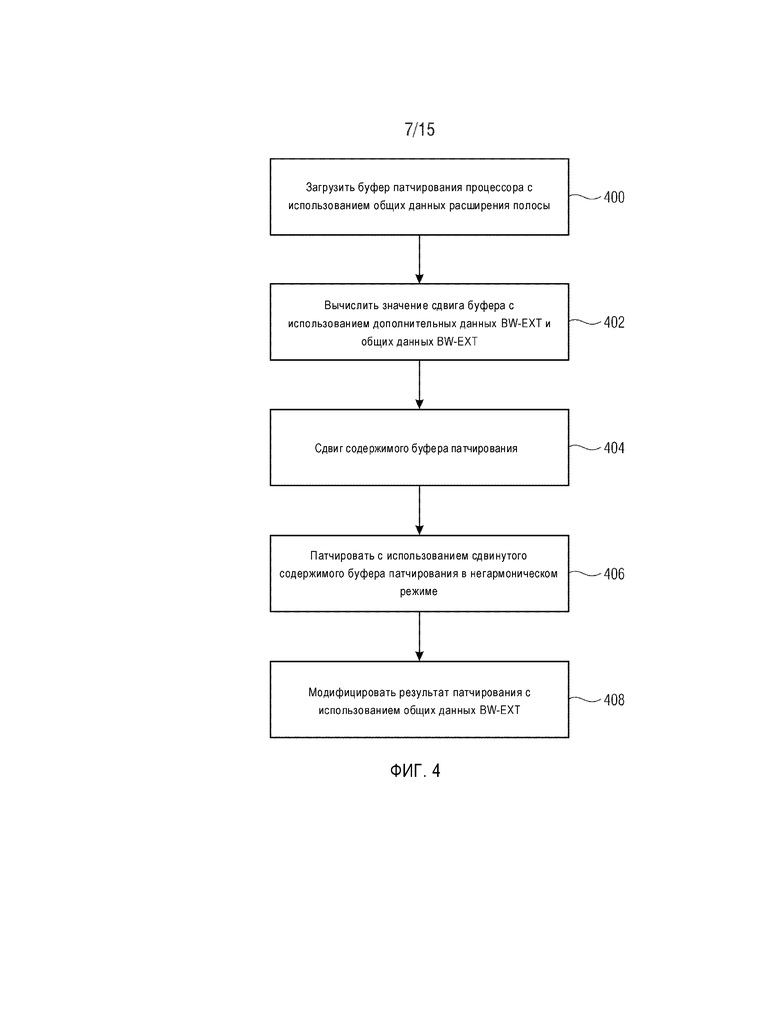

фиг.4 демонстрирует реализацию усовершенствованного режима негармонического расширения полосы;

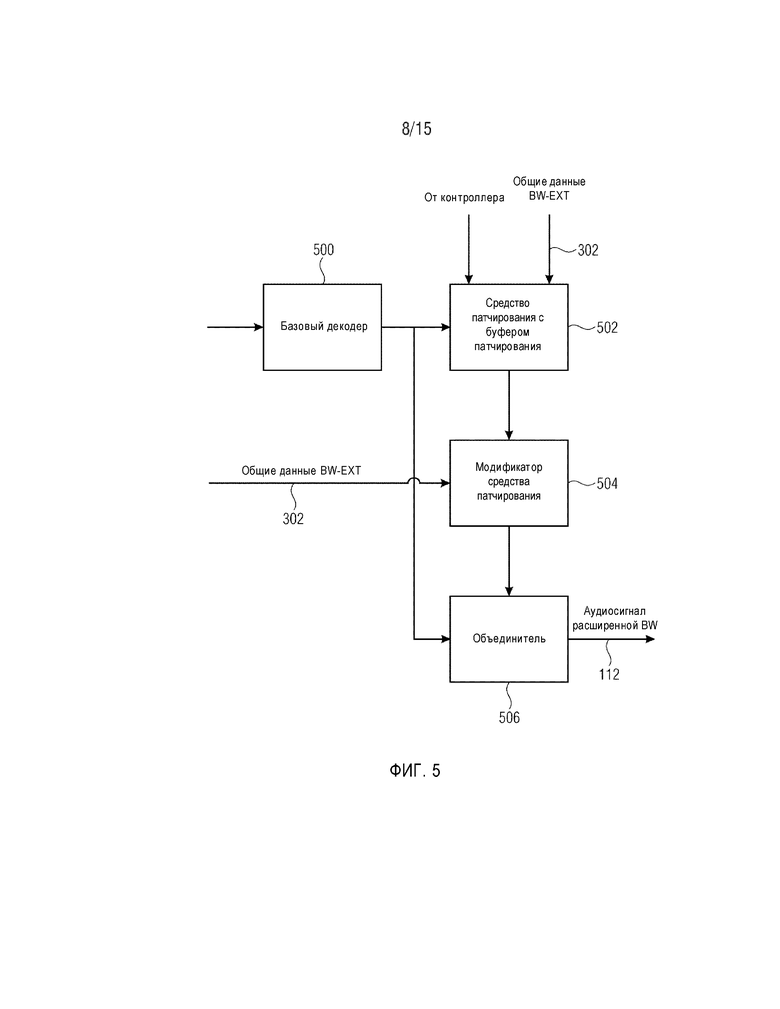

фиг.5 демонстрирует предпочтительную реализацию процессора;

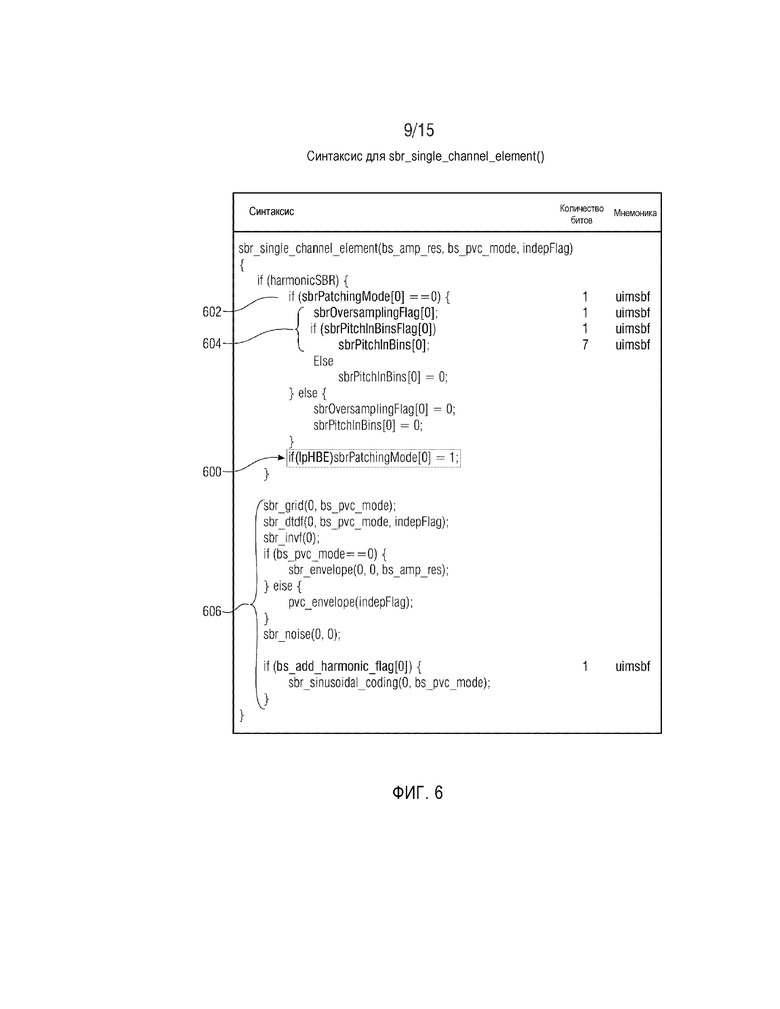

фиг.6 демонстрирует синтаксис процедуры декодирования для одноканального компонента;

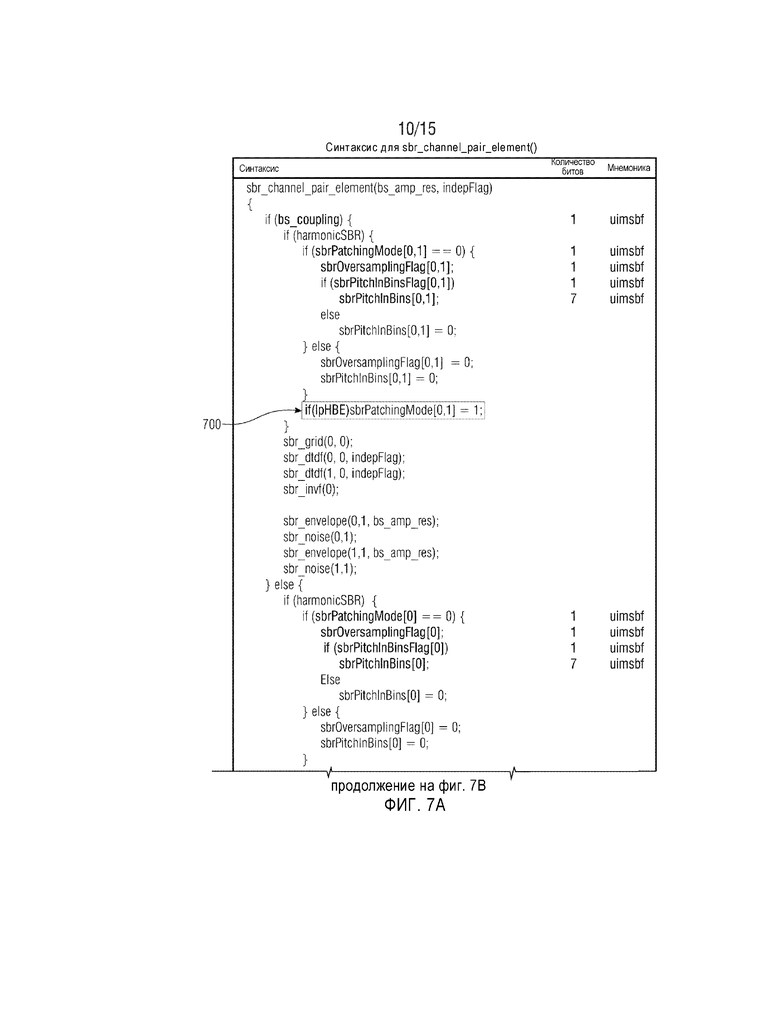

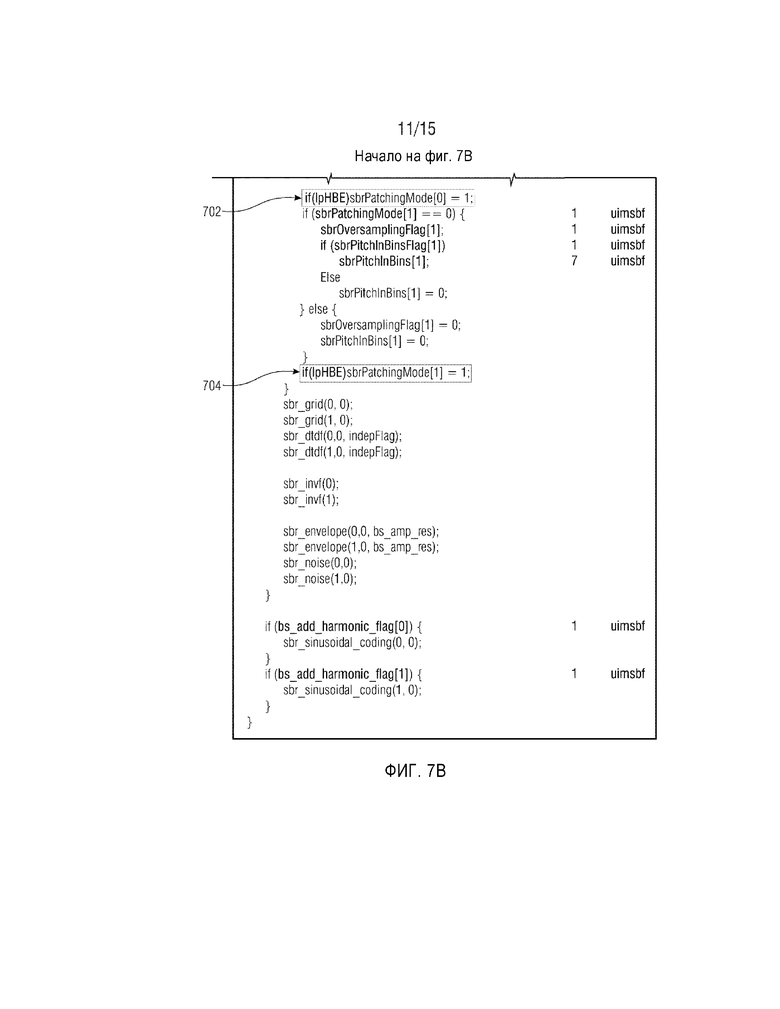

фиг.7a и 7b демонстрируют синтаксис процедуры декодирования для двухканального компонента;

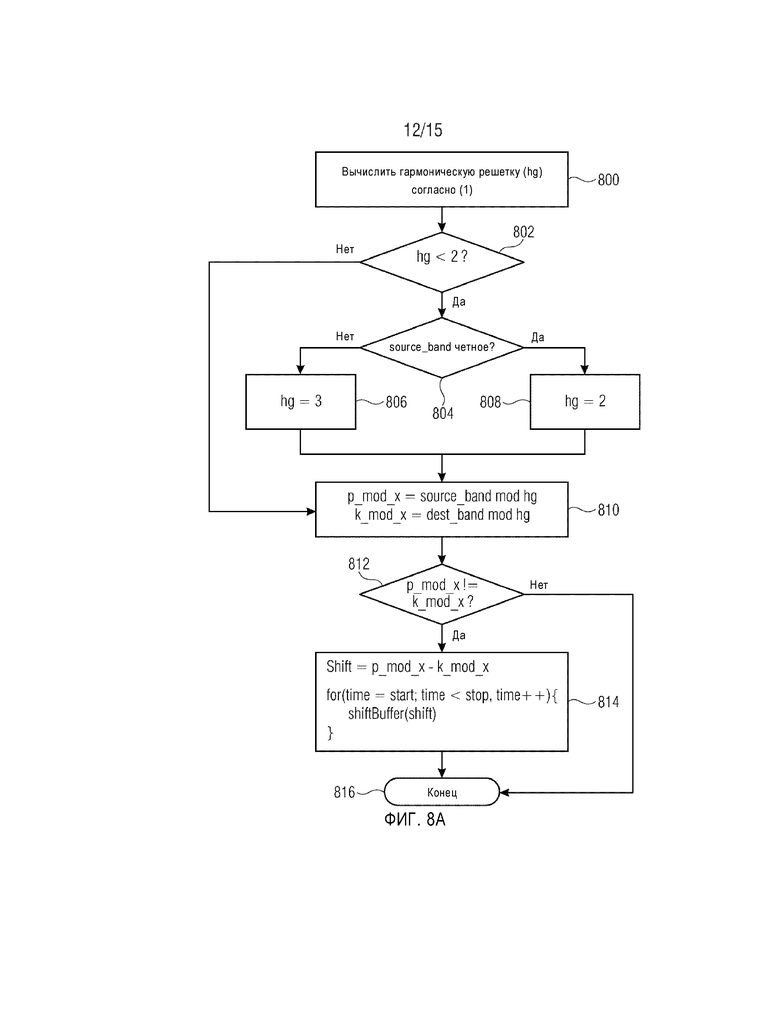

фиг.8a дополнительно демонстрирует реализацию усовершенствованного режим негармонического расширения полосы;

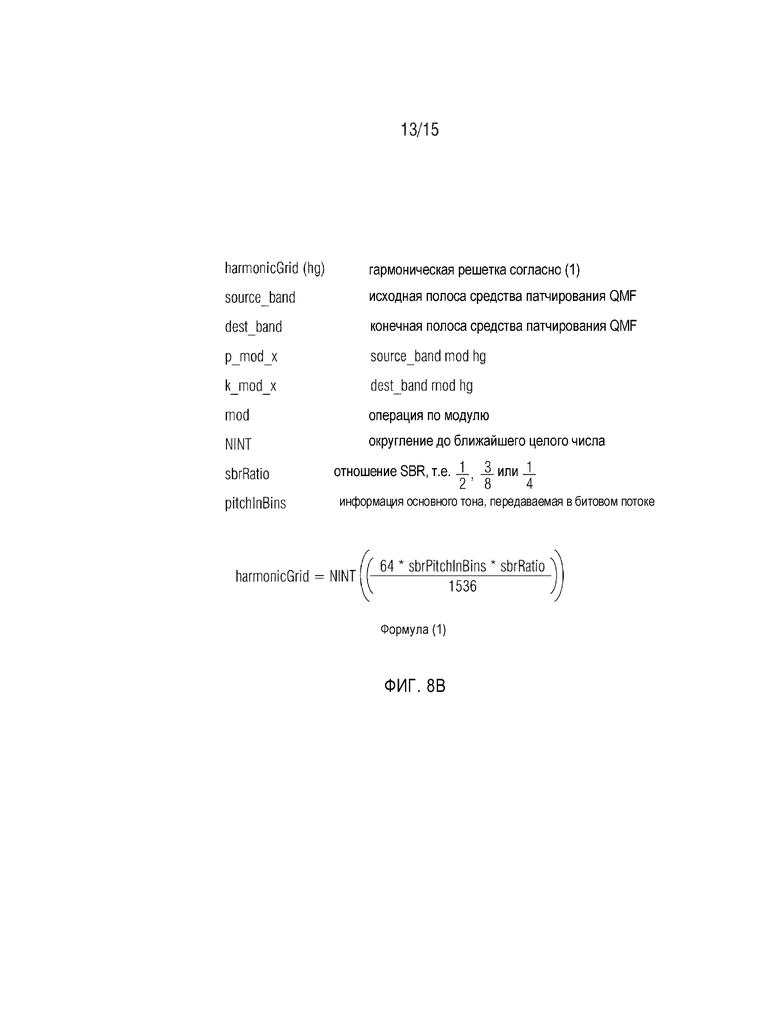

фиг.8b демонстрирует сводку данных, указанных на фиг.8a;

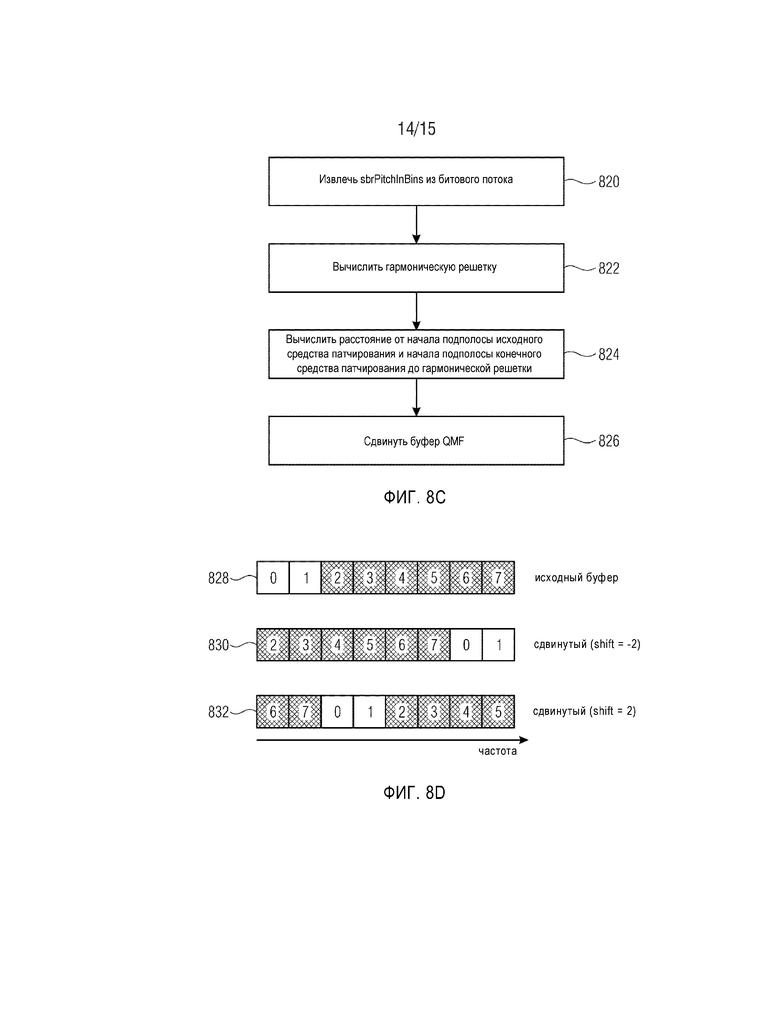

фиг.8c дополнительно демонстрирует реализацию усовершенствованного режима негармонического расширения полосы, осуществляемого контроллером;

фиг.8d демонстрирует буфер патчирования и сдвиг содержимого буфера патчирования; и

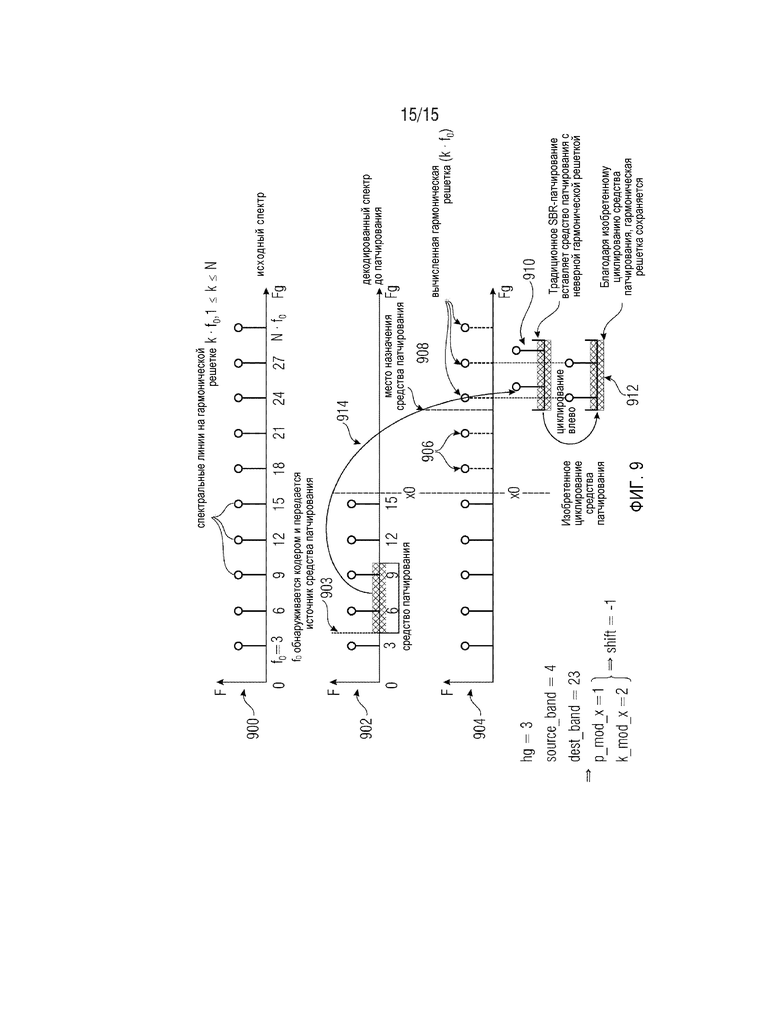

фиг.9 демонстрирует объяснение предпочтительной модификации режима негармонического расширения полосы.

Фиг.1a демонстрирует вариант осуществления устройства для декодирования кодированного аудиосигнала. Кодированный аудиосигнал содержит данные управления расширением полосы, указывающие либо первый режим гармонического расширения полосы, либо второй режим негармонического расширения полосы. Кодированный аудиосигнал вводится на линии 101 во входной интерфейс 100. Входной интерфейс подключен линией 108 с процессором 102 с ограниченными ресурсами. Кроме того, предусмотрен контроллер 104, который, по меньшей мере, в необязательном порядке, подключен к входному интерфейсу 100 линией 106 и который дополнительно подключен к процессору 102 линией 110. Выходной сигнал процессора 102 является декодированным аудиосигналом, как указано позицией 112. Входной интерфейс 100 выполнен с возможностью приема кодированного аудиосигнала, содержащего данные управления расширением полосы, указывающие либо первый режим гармонического расширения полосы, либо второй режим негармонического расширения полосы для кодированного участка, например, кадра кодированного аудиосигнала. Процессор 102 выполнен с возможностью декодирования аудиосигнала только с использованием второго режима негармонического расширения полосы, как указано вблизи линии 110 на фиг.1a. Это гарантируется контроллером 104. Контроллер 104 выполнен с возможностью управления процессором 102 для декодирования аудиосигнала с использованием второго режима негармонического расширения полосы, даже когда данные управления расширением полосы указывают первый режим гармонического расширения полосы для кодированного аудиосигнала.

Фиг.1b демонстрирует предпочтительную реализацию кодированного аудиосигнала в потоке данных или битовом потоке. Кодированный аудиосигнал содержит заголовок 114 для всего элемента аудио, и весь элемент аудио организован в виде последовательных кадров, например кадра 1 116, кадра 2 118 и кадра 3 120. С каждым кадром дополнительно связан заголовок, например, заголовок 1 116a для кадра 1, и данные полезной нагрузки 116b для кадра 1. Кроме того, второй кадр 118, опять же, имеет данные 118a заголовка и данные 118b полезной нагрузки. Аналогично, третий кадр 120, опять же, имеет заголовок 120a и блок 120b данных полезной нагрузки. В стандарте USAC, заголовок 114 имеет флаг “harmonicSBR”. Если этот флаг harmonicSBR равен нулю, то весь элемент аудио декодируется с использованием режима негармонического расширения полосы согласно стандарту USAC, который в этом контексте означает стандарт High Efficiency - AAC (HE-AAC), который является ISO/IEC 1449-3:2009, часть аудио. Если же флаг harmonicSBR имеет значение единица, то разрешен режим гармонического расширения полосы, но затем может сигнализироваться, для каждого кадра, отдельным флагом sbrPatchingMode, который может принимать знание нуль или единица. В этом контексте, обратимся к фиг.1c, где указаны разные значения двух флагов. Таким образом, когда флаг harmonicSBR равен единице, и флаг sbrPatchingMode равен нулю, стандартный декодер USAC действует в режиме гармонического расширения полосы. Однако в этом случае, который указан позицией 130 на фиг.1c, контроллер 104, показанный на фиг.1a, тем не менее, способен управлять процессором 102 для работы в режиме негармонического расширения полосы.

Фиг.2 демонстрирует предпочтительную реализацию процедуры, отвечающей изобретению. На этапе 200, входной интерфейс 100 или любой другой объект в устройстве для декодирования считывает данные управления расширением полосы из кодированного аудиосигнала, и эти данные управления расширением полосы могут представлять собой одно указание на кадр или, если обеспечено, дополнительным указанием на элемент, как рассмотрено в контексте фиг.1b в отношении стандарта USAC. На этапе 202, процессор 102 принимает данные управления расширением полосы и сохраняет данные управления расширением полосы в особом управляющем регистре, реализованном в процессоре 102, показанном на фиг.1a. Затем, на этапе 204, контроллер 104 обращается к этому управляющему регистру процессора и, как указано позицией 206, перезаписывает в управляющем регистре значение, указывающее негармоническое расширение полосы. Это, в порядке примера, проиллюстрировано в синтаксисе USAC для одноканального компонента позицией 600 на фиг.6 или для sbr_channel_pair_element, указанного на этапе 700 на фиг.7a и 702, 704 на фиг.7b, соответственно. В частности, “перезапись”, показанную в блоке 206 на фиг.2, можно реализовать, вставляя строки 600, 700, 702, 704 в синтаксис USAC. В частности, оставшаяся часть фиг.6 соответствует таблице 41 ISO/IEC DIS 23003-3 и фиг.7a, 7b соответствуют таблице 42 ISO/IEC DIS 23003-3. Этот международный стандарт включен сюда в полном объеме посредством ссылки. В стандарте приведено подробное определение всех параметров/значений на фиг.6 и фиг.7a, 7b.

В частности, дополнительная строка в синтаксисе высокого уровня, указанная позицией 600, 700, 702, 704, указывает, что независимо от значения sbrPatchingMode, считываемого из битового потока в 602, флаг sbrPatchingMode, тем не менее, задается равным единице, т.е. сигнализация, дополнительному процессу на декодере, что нужно осуществлять режим негармонического расширения полосы. Важно, строка 600 синтаксиса располагается после считывания на стороне декодера конкретных данных гармонического расширения полосы, состоящих из sbrOversampllingFlag, sbrPitchInBinsFlag и sbrPitchInBins, указанных позицией 604. Таким образом, как показано на фиг.6, и, аналогично, на фиг.7a, кодированный аудиосигнал содержит общие данные полезной нагрузки расширения полосы 606 для обоих режимов расширения полосы, т.е. режим негармонического расширения полосы и режим гармонического расширения полосы, и дополнительные данные, специфические для режима гармонического расширения полосы, проиллюстрированные в позиции 604. Это будет рассмотрено позже в контексте фиг.3a. Переменная “lpHBE” иллюстрирует процедуру, отвечающую изобретению, т.е. режим “маломощного гармонического расширения полосы”, который является режимом негармонического расширения полосы, но с дополнительной модификацией, которая будет рассмотрена позже в отношении “гармонического расширения полосы”.

Предпочтительно, как указано на фиг.1a, процессор 102 является процессором с ограниченными ресурсами. В частности, процессор 102 с ограниченными ресурсами обладает достаточными ресурсами обработки и ресурсами памяти для декодирования аудиосигнала с использованием второго режима негармонического расширения полосы. Однако, в частности, ресурсов памяти или обработки недостаточно для декодирования кодированного аудиосигнала с использованием первого режима гармонического расширения полосы. Как указано на фиг.3a, кадр содержит заголовок 300, общие данные 302 полезной нагрузки расширения полосы, дополнительные данные 304 гармонического расширения полосы, например, информацию об основном тоне, гармонической решетке и т.п. и, дополнительно, кодированные базовые данные 306. Однако порядок элементов данных может отличаться от показанного на фиг.3a. В другом предпочтительном варианте осуществления, на первом месте стоят кодированные базовые данные. Затем следует заголовок 300, имеющий битовый флаг sbrPatchingMode, сопровождаемый дополнительными данными 304 HBE, и, наконец, общие данные 302 расширения BW.

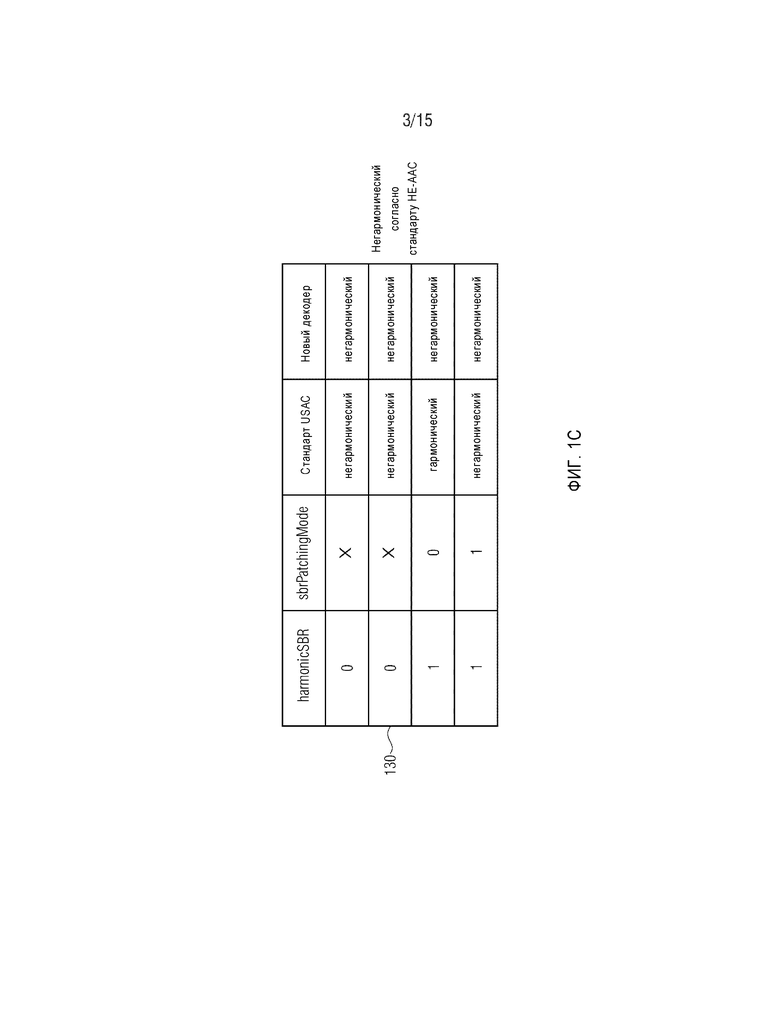

Дополнительные данные гармонического расширения полосы, в примере USAC, рассмотренном в контексте фиг.6, представляют собой элемент 604, информация sbrPitchInBins, состоящая из 7 битов. В частности, как указано в стандарте USAC, данные sbrPitchInBins управляют добавлением членов векторного произведения в гармоническом транспозиторе SBR. sbrPitchInBins является целочисленным значением в пределах от 0 до 127 и представляет расстояние, измеренное в частотных интервалах для 1536-DFT, действующего на частоте дискретизации базового кодера. В частности, было установлено, что с использованием информации sbrPitchInBins, можно определять основной тон или гармоническую решетку. Это проиллюстрировано в формуле (1) на фиг.8b. Для вычисления гармонической решетки, вычисляются значения sbrPitchInBins и sbrRatio, где отношение SBR может быть указанным выше на фиг.8b.

Естественно, в битовый поток могут быть включены другие указания гармонической решетки, основного тона или основной частоты, задающей гармоническую решетку. Эти данные используются для управления первым режимом гармонического расширения полосы и, в одном варианте осуществления настоящего изобретения, могут игнорироваться, в связи с чем осуществляется режим негармонического расширения полосы без каких-либо модификаций. Однако, в других вариантах осуществления, режим прямого негармонического расширения полосы модифицируется с использованием данных управления для режима гармонического расширения полосы, как показано на фиг.3b и др. Другими словами, кодированный аудиосигнал содержит общие данные 302 полезной нагрузки расширения полосы для первого режима гармоническое расширение полосы и второго режима негармонического расширения полосы и дополнительные данные полезной нагрузки 304 для первого режима гармонического расширения полосы. В этом контексте, контроллер 104 проиллюстрированный на фиг.1, выполнен с возможностью использования дополнительных данных полезной нагрузки для управления процессором 102 для модификации операции патчирования, осуществляемой процессором, по сравнению с операцией патчирования во втором режиме негармонического расширения полосы без какой-либо модификации. Для этого, предпочтительно, чтобы процессор 102 содержал буфер патчирования, как показано на фиг.3b, и конкретная реализация буфера, в порядке примера, объяснена со ссылкой на фиг.8d.

В дополнительном варианте осуществления, дополнительные данные полезной нагрузки 304 для первого режима гармонического расширения полосы содержат информацию о гармонической характеристике кодированного аудиосигнала, и эта гармоническая характеристика может представлять собой данные sbrPitchInBins, другие данные гармонической решетки, данные основной частоты или любые другие данные, из которых можно вывести гармоническую решетку или основную частоту или основной тон соответствующего участка кодированного аудиосигнала. Контроллер 104 выполнен с возможностью модификации содержимого буфера патчирования для буфера патчирования, используемого процессором 102 для осуществления операции патчирования при декодировании кодированного аудиосигнала, чтобы гармоническая характеристика патчированного сигнала была ближе к гармонической характеристике, чем сигнал, патчированный без модификации буфера патчирования.

Для этого, обратимся к фиг.9, иллюстрирующей, в позиции 900, исходный спектр, имеющий спектральные линии на гармонической решетке k⋅f0, и гармонические линии проходят от 1 до N. Кроме того, основная частота f0, в этом примере равна 3, в результате чего гармоническая решетка содержит все кратные 3. Кроме того, элемент 902 указывает декодированный базовый спектр до патчирования. В частности, частота x0 разделения указана позицией 16, и указано, что источник патча проходит от частотной линии 4 до частотной линии 10. Начальную и/или конечную частоту источника патча предпочтительно сигнализировать в кодированном аудиосигнале, обычно в виде данных в общих данных 302 полезной нагрузки расширения полосы, согласно фиг.3a. Элемент 904 указывает такую же ситуацию, как в элементе 902, но с дополнительно вычисленной гармонической решеткой k⋅f0 в позиции 906. Кроме того, указано место назначения 908 патча. Это место назначения патча предпочтительно дополнительно включать в общие данные 302 полезной нагрузки расширения полосы согласно фиг.3a. Таким образом, источник патча указывает нижнюю частоту исходного диапазона, как указано позицией 903, и место назначения патча указывает нижнюю границу места назначения патча. В случае применения обычного негармонического патчирования, как указано позицией 910, наблюдается рассогласование между тональными линиями или гармоническими линиями патчированных данных и вычисленной гармонической решеткой 906. Таким образом, традиционное SBR-патчирование или режим прямого негармонического патчирования с USAC или High Efficiency AAC вставляет патч с неверной гармонической решеткой. Для решения этой проблемы, модификация этого прямого негармонического патча осуществляется процессором. Один вариант модификации предусматривает циклирование содержимого буфера патчирования или, другими словами, перемещение гармонических линий в полосе патчирования, но без изменения разнесения по частоте гармонических линий. Другие варианты согласования гармонической решетки патча с вычисленной гармонической решеткой декодированного спектра до патчирования очевидны специалистам в данной области техники. В этом предпочтительном варианте осуществления настоящего изобретения, дополнительные данные гармонического расширения полосы, включенные в кодированный аудиосигнал совместно с общими данными полезной нагрузки расширения полосы, не просто игнорируются, но повторно используются для дополнительного повышения качества аудиосигнала за счет модификации режима негармонического расширения полосы, обычно сигнализируемой в битовом потоке. Тем не менее, ввиду того, что модифицированный режим негармонического расширения полосы по-прежнему является режимом негармонического расширения полосы, опирающимся на операцию улучшающего копирования набора соседних частотных интервалов в набор соседних частотных интервалов, эта процедура не приводит к дополнительному объему ресурсов памяти по сравнению с осуществлением режима прямого негармонического расширения полосы, но значительно повышает качество аудиосигнала для реконструированного сигнала благодаря согласованию гармонических решеток, как указано на фиг.9 позицией 912.

Фиг.3c демонстрирует предпочтительную реализацию, осуществляемую контроллером 104, показанным на фиг.3b. На этапе 310 контроллер 104 вычисляет гармоническую решетку из дополнительных данных гармонического расширения полосы, и для этого можно осуществлять любое вычисление, но в контексте USAC применяется формула (1) на фиг.8b. Кроме того, на этапе 312 определяются полоса источника патчирования и полоса целевого объекта патчирования, т.е. он может содержать, в основном, считывание данных 903 источника патча и данных 908 места назначения патча из общих данных расширения полосы. Однако, в других вариантах осуществления, эти данные могут быть заранее заданными и поэтому могут быть заранее известны декодеру и не подлежать передаче.

На этапе 314, полоса источника патчирования модифицируется в частотных границах, т.е. границы патча для источника патча не измеряются по сравнению с передаваемыми данными. Это может осуществляться либо до патчирования, т.е. когда данные патча относятся к базовому или декодированному спектру до патчирования, указанному позицией 902, или когда содержимое патча уже транспонировано в диапазон более высоких частот, т.е., как показано на фиг.9 позициями 910 и 912, где циклирование осуществляется после патчирования, где патчирование обозначено стрелкой 914.

Это патчирование 914 или “улучшающее копирование” является негармоническим патчированием, что можно видеть на фиг.9, сравнивая ширину источника патча, содержащего шесть приращений частоты, и те же шесть приращений частоты в целевом диапазоне, т.е. в позиции 910 или 912.

Модификация осуществляется таким образом, что частотный участок в полосе источника патчирования, совпадающей с гармонической решеткой, располагается, после патчирования, в целевом частотном участке, совпадающем с гармонической решеткой.

Предпочтительно, как показано на фиг.8d, в процессоре 102 предусмотрен буфер патчирования, показанный в трех различных состояниях 828, 830, 832. Процессор выполнен с возможностью загрузки буфера патчирования, как указано на этапе 400 на фиг.4. Затем контроллер выполнен с возможностью вычисления 402 значения сдвига буфера с использованием дополнительных данных расширения полосы и общих данных расширения полосы. Затем, на этапе 404, содержимое буфера сдвигается на вычисленное значение сдвига буфера. Элемент 830 указывает, когда вычисленное значение сдвига равно “-2”, и элемент 832 указывает состояние буфера, в котором значение сдвига, вычисленное на этапе 404, равно 2, и на этапе 404 осуществляется сдвиг на +2. Затем, как показано на этапе 406 на фиг.4, патчирование осуществляется с использованием сдвинутого содержимого буфера патчирования, и, тем не менее, патчирование осуществляется в негармоническом режиме. Затем, на этапе 408, результат патчирования модифицируется с использованием общих данных расширения полосы. Такие дополнительно используемые общие данные расширения полосы могут быть, как известно из High Efficiency AAC или из USAC, данными спектральной огибающей, данными шума, данными о конкретных гармонических линиях, данными обратной фильтрации и т.д.

Для этого обратимся к фиг.5, иллюстрирующей более детализированную реализацию процессора 102, показанного на фиг.1a. Процессор обычно содержит базовый декодер 500, средство 502 патчирования с буфером патчирования, модификатор 504 патча и объединитель 506. Базовый декодер выполнен с возможностью декодирования кодированного аудиосигнала для получения декодированного спектра до патчирования, показанного позицией 902 на фиг.9. Затем средство 502 патчирования с буфером патчирования осуществляет операцию 914 на фиг.9. Средство 502 патчирования осуществляет модификацию буфера патчирования либо до, либо после патчирования, как рассмотрено в контексте фиг.9. Наконец, модификатор 504 патча использует дополнительные данные расширения полосы для модификации результата патчирования, как показано на этапе 408 на фиг.4. Затем объединитель 506, который может быть, например, объединителем в частотной области в форме набора фильтров для синтеза, объединяет выходной сигнал модификатора 504 патча и выходной сигнал базового декодера 500, т.е. низкополосный сигнал, чтобы, наконец, получить аудиосигнал расширенной полосы в качестве выхода на линии 112, показанной на фиг.1a.

Как уже рассмотрено в контексте фиг.1b, данные управления расширением полосы могут содержать первый объект данных управления для элемента аудио, например, harmonicSBR, проиллюстрированный на фиг.1b, где этот элемент аудио содержит множество кадров 116, 118, 120 аудио. Первый объект данных управления указывает, активен ли первый режим гармонического расширения полосы, для множества кадров. Кроме того, предусмотрен второй объект данных управления, соответствующий режиму SBR-патчирования, например, в стандарте USAC, который обеспечен в каждом из заголовков 116a, 118a, 120a для отдельных кадров.

Входной интерфейс 100, показанный на фиг.1a, выполнен с возможностью считывания первых данных управления для элемента аудио и второго объекта данных управления для каждого кадра из множества кадров, и контроллер 104, показанный на фиг.1a, выполнен с возможностью управления процессором 102 для декодирования аудиосигнала с использованием второго режима негармонического расширения полосы независимо от значения первого объекта данных управления и независимо от значения второго объекта данных управления.

Согласно варианту осуществления настоящего изобретения, и, как показано изменениями синтаксиса на фиг.6 и фиг.7a, 7b, декодеру USAC предписывается пропускать относительно сложное вычисление гармонического расширения полосы. Таким образом, применяется расширение полосы или “маломощное HBE”, если флаг lpHBE, указанный позицией 600 и 700, 702, 704, задан равным ненулевому значению. Флаг lpHBE может устанавливаться декодером по отдельности, в зависимости от доступных аппаратных ресурсов. Нулевое значение означает, что декодер действует полностью в соответствии со стандартом, т.е. по инструкции первого и второго объектов данных управления, показанных на фиг.1b. Если же значение равно единице, то режим негармонического расширения полосы осуществляется процессором, даже когда сигнализируется режим гармонического расширения полосы.

Таким образом, настоящее изобретение предусматривает процессор с более низкой вычислительной сложностью и более низким расходованием памяти совместно с новой процедурой декодирования. Синтаксис битового потока eSBR, заданный в [1], совместно использует общую основу для HBE [1] и традиционного декодирования с SBR [2]. Однако в случае HBE дополнительная информация кодируется в битовый поток. Декодер “HBE низкой сложности” в предпочтительном варианте осуществления настоящего изобретения декодирует данные, кодированные по USAC, согласно [1] и игнорирует всю информацию, относящуюся к HBE. Затем остальные данные eSBR поступают на традиционный алгоритм SBR [2] и интерпретируются им, т.е. данные используются для применения патчирования для улучшающего копирования [2] вместо гармонической транспозиции. Модификация механики декодирования с eSBR, в отношении изменений синтаксиса, проиллюстрировано на фиг.6 и 7a, 7b. Кроме того, в предпочтительном варианте осуществления, конкретная информация HBE, например, информация sbrPitchInBins, переносимая битовым потоком, повторно используется.

При традиционном кодировании USAC данных битового потока значение sbrPitchInBins должно передаваться в кадре USAC. Это значение отражает значение частоты, определенное кодером для передачи информации, описывающей гармоническую структуру текущего кадра USAC. Для использования этого значения без использования функциональных возможностей стандарта HBE, следует применять следующий способ, отвечающий изобретению, этап за этапом:

1. Извлекать sbrPitchInBins из битового потока

См. таблицу 44 и таблицу 45 соответственно на предмет информации о том, как извлекать компонент sbrPitchInBins битового потока из битового потока USAC [1].

2. Вычислять гармоническую решетку согласно формуле (1)

(1)

(1)

3. Вычислять расстояние от начала подполосы исходного патча и начала подполосы конечного патча до гармонической решетки

Блок-схема операций на фиг.8a дает подробное описание алгоритма, отвечающего изобретению, как вычислять расстояние начального и конечного патча до гармонической решетки

harmonicGrid (hg) - гармоническая решетка согласно (1)

source_band - исходная полоса 903 патча QMF, показанная на фиг.9

dest_band - конечная полоса 908 патча QMF, показанная на фиг.9

p_mod_x - source_band mod hg

k_mod_x - dest_band mod hg

mod - операция по модулю

NINT - округление до ближайшего целого числа

sbrRatio - отношение SBR, т.е.  ,

,  или

или

pitchInBins - информация основного тона, передаваемая в битовом потоке

Далее более подробно рассмотрена фиг.8a. Предпочтительно, это управление, т.е. все вычисление осуществляется на контроллере 104, показанном на фиг.1a. На этапе 800, гармоническая решетка вычисляется согласно формуле (1), как показано на фиг.8b. Затем производится определение, ниже ли гармоническая решетка hg чем 2. Если это не так, то управление переходит к этапу 810. Если же определено, что гармоническая решетка ниже чем 2, то на этапе 804 производится определение, является ли значение source_band четным. Если это так, то производится определение, что гармоническая решетка равна 2, но если это не так, то производится определение, что гармоническая решетка равна 3. Затем, на этапе 810, осуществляются вычисления по модулю. На этапе 812, производится определение, отличаются ли два вычисления по модулю. Если результаты идентичны, процедура заканчивается, и если результаты различны, значение сдвига вычисляется, как указано в блоке 814, как разность между двумя результатами вычисления по модулю. Затем, что также проиллюстрировано на этапе 814, осуществляется циклический сдвиг буфера. Напомним, что при применении сдвига предпочтительно рассматривать фазовые соотношения. Управление останавливается в блоке 816.

В итоге, как показано на фиг.8c, процедура в целом содержит этап извлечения информации sbrPitchInBins из битового потока, как указано на этапе 820. Затем контроллер вычисляет гармоническую решетку, как указано на этапе 822. Затем, на этапе 824, вычисляется расстояние от начала подполосы источника и начала подполосы места назначения до гармонической решетки, что соответствует, в предпочтительном варианте осуществления, этапу 810. Наконец, как указано в блоке 826, сдвиг буфера QMF, т.е. циклический сдвиг в области QMF High Efficiency AAC осуществляется негармоническое расширение полосы.

При сдвиге буфера QMF, гармоническая структура сигнала реконструируется согласно передаваемой информации sbrPitchInBins, хотя осуществлялась процедура негармонического расширения полосы.

Хотя некоторые аспекты были описаны в контексте устройства для кодирования или декодирования, ясно, что эти аспекты также представляют описание соответствующего способа, где блок или устройство соответствует этапу способа или признаку этапа способа. Аналогично, аспекты, описанные в контексте этапа способа, также представляют описание соответствующего блока или элемента, или признака соответствующего устройства. Некоторые или все из этапов способа могут выполняться аппаратным устройством, например, микропроцессором, программируемым компьютером или электронной схемой (или с его помощью). В некоторых вариантах осуществления, некоторые один или более из наиболее важных этапов способа могут выполняться таким устройством.

В зависимости от тех или иных требований реализации, варианты осуществления изобретения можно реализовать аппаратными средствами или программными средствами. Реализацию можно осуществлять с использованием нетранзиторного носителя данных, например носителя цифровых данных, например, флоппи-диска, жесткого диска (HDD), DVD, Blu-Ray, CD, ROM, PROM и EPROM, EEPROM или флэш-памяти, на которых сохраняются электронно-считываемые сигналы управления, которые взаимодействуют (или способны взаимодействовать) с программируемой компьютерной системой для осуществления соответствующего способа. Таким образом, носитель цифровых данных может считываться компьютером.

Некоторые варианты осуществления согласно изобретению содержат среду переноса данных, имеющую электронно-считываемые сигналы управления, которая способна взаимодействовать с программируемой компьютерной системой, для осуществления одного из описанных здесь способов.

В общем случае, варианты осуществления настоящего изобретения можно реализовать в виде компьютерного программного продукта с программным кодом, причем программный код предписывает осуществление одного из способов, когда компьютерный программный продукт выполняется на компьютере. Программный код может храниться, например, на машиночитаемом носителе.

Другие варианты осуществления содержат компьютерную программу для осуществления одного из описанных здесь способов, хранящуюся на машиночитаемом носителе.

Другими словами, вариант осуществления способа, отвечающего изобретению, предусматривает, таким образом, компьютерную программу, имеющую программный код для осуществления одного из описанных здесь способов, когда компьютерная программа выполняется на компьютере.

Дополнительный вариант осуществления способа, отвечающего изобретению, предусматривает, таким образом, среду переноса данных (или носитель цифровых данных, или компьютерно-считываемый носитель), где записана компьютерная программа для осуществления одного из описанных здесь способов. Среда переноса данных, носитель цифровых данных или носитель с записью обычно является вещественным и/или невременным.

Дополнительный вариант осуществления способа, отвечающего изобретению, таким образом, предусматривает поток данных или последовательность сигналов, представляющих компьютерную программу для осуществления одного из описанных здесь способов. Поток данных или последовательность сигналов можно, например, сконфигурировать для переноса через соединение с возможностью передачи данных, например, через интернет.

Дополнительный вариант осуществления содержит средство обработки, например, компьютер или программируемое логическое устройство, выполненное с возможностью, или предназначенное для осуществления одного из описанных здесь способов.

Дополнительный вариант осуществления содержит компьютер, на котором установлена компьютерная программа для осуществления одного из описанных здесь способов.

Дополнительный вариант осуществления согласно изобретению содержит устройство или систему, выполненное/ую с возможностью переноса (например, электронного или оптического) компьютерной программы для осуществления одного из описанных здесь способов на приемник. Приемником может быть, например, компьютер, мобильное устройство, запоминающее устройство и т.п. Устройство или система может, например, содержать файловый сервер для переноса компьютерной программы на приемник.

В некоторых вариантах осуществления, программируемое логическое устройство (например, вентильная матрица, программируемая пользователем) может использоваться для осуществления некоторых или всех из функциональных возможностей описанных здесь способов. В некоторых вариантах осуществления, вентильная матрица, программируемая пользователем, может взаимодействовать с микропроцессором для осуществления одного из описанных здесь способов. В общем случае, способы, предпочтительно, осуществляются любым аппаратным устройством.

Вышеописанные варианты осуществления призваны лишь иллюстрировать принципы настоящего изобретения. Следует понимать, что специалисты в данной области техники могут предложить модификации и вариации описанных здесь конфигураций и деталей. Таким образом, они подлежат ограничению только объемом нижеследующей формулы изобретения, но не конкретными деталями, представленными посредством описания и объяснения рассмотренных здесь вариантов осуществления.

Литература

1. ISO/IEC 23003-3:2012: “Unified speech and audio coding”.

2. ISO/IEC 14496-3:2009: “Audio”.

3. ISO/IEC JTCI/SC29/WG11 MPEG2011/N12232: “USAC Verification Test Report”.

Изобретение относится к обработке аудиосигнала. Технический результат изобретения заключается в снижении вычислительной сложности процесса обработки аудиосигнала, требующего сниженных ресурсов памяти. Устройство для декодирования кодированного аудиосигнала (101), содержащего данные управления расширением полосы, указывающие либо первый режим гармонического расширения полосы, либо второй режим негармонического расширения полосы, содержит: входной интерфейс (100) для приема кодированного аудиосигнала; процессор (102) для декодирования аудиосигнала (101) с использованием второго режима негармонического расширения полосы; и контроллер (104) для управления процессором (102) для декодирования аудиосигнала с использованием второго режима негармонического расширения полосы, даже когда данные управления расширением полосы указывают первый режим гармонического расширения полосы для кодированного сигнала. 3 н. и 11 з.п. ф-лы, 17 ил.

1. Устройство для декодирования кодированного аудиосигнала (101), содержащего данные управления расширением полосы, указывающие либо первый режим гармонического расширения полосы, либо второй режим негармонического расширения полосы, содержащее:

входной интерфейс (100) для приема кодированного аудиосигнала, содержащего данные управления расширением полосы, указывающие либо первый режим гармонического расширения полосы, либо второй режим негармонического расширения полосы;

процессор (102) для декодирования аудиосигнала (101) с использованием второго режима негармонического расширения полосы; и

контроллер (104) для управления процессором (102) для декодирования аудиосигнала с использованием второго режима негармонического расширения полосы, даже когда данные управления расширением полосы указывают первый режим гармонического расширения полосы для кодированного сигнала.

2. Устройство по п.1, в котором процессор (102) располагает достаточными ресурсами памяти и обработки для декодирования кодированного аудиосигнала с использованием второго режима негармонического расширения полосы, и при этом ресурсов памяти или обработки недостаточно для декодирования кодированного аудиосигнала с использованием первого режима гармонического расширения полосы.

3. Устройство по п.1,

в котором входной интерфейс (100) выполнен с возможностью чтения данных управления расширением полосы для определения, декодировать ли кодированный аудиосигнал с использованием первого режима гармонического расширения полосы или второго режима негармонического расширения полосы, и сохранения данных управления расширением полосы в управляющем регистре процессора, и

контроллер (104) выполнен с возможностью осуществления доступа к управляющему регистру процессора и перезаписи значения в управляющем регистре процессора значением, указывающим второй режим негармонического расширения полосы, если входной интерфейс (100) сохранил значение, указывающее первый режим гармонического расширения полосы.

4. Устройство по п.1, в котором кодированный аудиосигнал содержит общие данные (302) полезной нагрузки расширения полосы для первого режима гармонического расширения полосы и второго режима негармонического расширения полосы и дополнительные данные (304) полезной нагрузки только для первого режима гармонического расширения полосы, и

контроллер (104) выполнен с возможностью использования дополнительных данных (304) полезной нагрузки для управления процессором (102) для модификации операции патчирования, осуществляемой процессором, по сравнению с операцией патчирования во втором режиме негармонического расширения полосы, причем модифицированная операция патчирования является операцией негармонического патчирования.

5. Устройство по п.4,

в котором дополнительные данные (304) полезной нагрузки содержат информацию о гармонической характеристике кодированного аудиосигнала, и

контроллер (104) выполнен с возможностью модификации содержимого (828, 830, 832) буфера патчирования для буфера патчирования, используемого процессором (102) для осуществления операции патчирования при декодировании кодированного аудиосигнала, чтобы гармоническая характеристика патчированного сигнала была ближе к гармонической характеристике, чем гармоническая характеристика сигнала, патчированного без модификации содержимого буфера патчирования.

6. Устройство по п.4,

в котором контроллер (104) выполнен с возможностью:

вычисления (310) гармонической решетки, указывающей частоту основного тона, из дополнительных данных полезной нагрузки;

определения (312) информации источника патчирования и информации целевого объекта патчирования для полосы источника патчирования, имеющей частотные границы, и полосы целевого объекта патчирования, имеющей частотные границы; и

модификации (314) данных в полосе источника патчирования в частотных границах до или после операции патчирования (914), таким образом, что частотный участок в полосе источника патчирования, совпадающей с гармонической решеткой, располагается, после патчирования (914), в целевом частотном участке (912), совпадающем с гармонической решеткой.

7. Устройство по п.4,

в котором процессор (102) содержит буфер патчирования,

причем процессор выполнен с возможностью загрузки (400) буфера патчирования с использованием общих данных полезной нагрузки расширения полосы,

причем контроллер выполнен с возможностью вычисления (402) значения сдвига буфера с использованием дополнительных данных расширения полосы, указывающих гармоническую решетку кодированного аудиосигнала с использованием информации (903) исходной полосы патча и информации (908) конечной полосы патча,

причем контроллер выполнен с возможностью применения (404) операции сдвига буфера к содержимому буфера; и

процессор (102) выполнен с возможностью генерации (406, 408) патчированных данных с использованием содержимого буфера, сдвинутого на значение сдвига буфера.

8. Устройство по п.7, в котором контроллер выполнен с возможностью применения (404) операции циклического сдвига буфера.

9. Устройство по п.1,

в котором процессор содержит:

базовый декодер (500) для декодирования базового кодированного аудиосигнала (902);

средство (502) патчирования для патчирования исходной частотной области базового кодированного аудиосигнала в целевую частотную область с использованием данных расширения полосы из кодированного аудиосигнала в соответствии с режимом негармонического расширения полосы; и

модификатор (504) патча для модификации патчированного сигнала в целевой частотной области с использованием данных расширения полосы из кодированного аудиосигнала.

10. Устройство по п.1,

в котором данные управления расширением полосы содержат первый объект (114) данных управления для элемента аудио, содержащего множество кадров аудио, причем первый объект данных управления указывает, активен ли первый режим гармонического расширения полосы, для множества кадров, второй объект данных (116a, 118a, 120a) управления для каждого кадра кодированного аудиосигнала, указывающий, активен ли первый режим гармонического расширения полосы, для каждого отдельного кадра кодированного аудиосигнала,

причем входной интерфейс (100) выполнен с возможностью считывания первого объекта данных управления для элемента аудио и второго объекта данных управления для каждого кадра из множества кадров; и

контроллер (104) выполнен с возможностью управления процессором (102) для декодирования аудиосигнала с использованием второго режима негармонического расширения полосы независимо от значения первого объекта данных управления и независимо от значения второго объекта данных управления.

11. Устройство по п.1,

в котором кодированный аудиосигнал является битовым потоком, заданным по стандарту USAC,

причем процессор (102) выполнен с возможностью осуществления второго режима негармонического расширения полосы, заданного по стандарту USAC; и

входной интерфейс выполнен с возможностью синтаксического анализа битового потока, содержащего кодированный аудиосигнал в соответствии со стандартом USAC.

12. Устройство по п.1, в котором процессор (102) располагает достаточными ресурсами памяти и обработки для декодирования кодированного аудиосигнала с использованием второго режима негармонического расширения полосы, и при этом ресурсов памяти или обработки недостаточно для декодирования кодированного аудиосигнала с использованием первого режима гармонического расширения полосы, когда кодированный аудиосигнал является кодированным стереофоническим или многоканальным аудиосигналом; и

процессор (102) располагает достаточными ресурсами памяти и обработки для декодирования кодированного аудиосигнала с использованием второго режима негармонического расширения полосы и с использованием первого режима гармонического расширения полосы, когда кодированный аудиосигнал является кодированным монофоническим сигналом.

13. Способ декодирования кодированного аудиосигнала (101), содержащего данные управления расширением полосы, указывающие либо первый режим гармонического расширения полосы, либо второй режим негармонического расширения полосы, содержащий этапы, на которых:

принимают (100) кодированный аудиосигнал, содержащий данные управления расширением полосы, указывающие либо первый режим гармонического расширения полосы, либо второй режим негармонического расширения полосы;

декодируют (102) аудиосигнал (101) с использованием второго режима негармонического расширения полосы; и

управляют (104) декодированием аудиосигнала таким образом, что второй режим негармонического расширения полосы используется при декодировании, даже когда данные управления расширением полосы указывают первый режим гармонического расширения полосы для кодированного сигнала.

14. Носитель данных, имеющий сохраненную на нем компьютерную программу для осуществления, при выполнении на компьютере, способа декодирования кодированного аудиосигнала по п.13.

| СПОСОБ СТАНОЧНОГО ГРАВИРОВАНИЯ ИЗОБРАЖЕНИЯ НА МЕТАЛЛЕ | 2000 |

|

RU2169670C1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| RU 2011109670 A, 27.09.2012. | |||

Авторы

Даты

2018-02-07—Публикация

2014-11-28—Подача