Перекрестные ссылки на родственные заявки

По настоящей заявке испрашивается приоритет по предварительной патентной заявке США №61/781348, поданной 14 марта 2013 г. и озаглавленной «MODEM ASIC ARCHITECTURE FOR HART COMMUNICATIONS PROTOCOL)), все содержание которой включено в настоящую заявку посредством ссылки.

Область техники, к которой относится изобретение

Настоящее изобретение относится к общей области полевых устройств, используемых в производственно-технологических сетях. Более конкретно настоящее изобретение относится к области обработки сообщений и передачи данных при помощи модулей связи полевых устройств.

Уровень техники

Для управления различными производственными процессами, осуществляемыми на промышленном предприятии, как правило, используется распределенная система управления (Distributed Control System, DCS). На предприятии обычно бывает предусмотрен пункт централизованного управления, в котором установлена компьютерная система, содержащая средства пользовательского ввода/вывода (I/O), средства дискового ввода/вывода и другое периферийное оборудование. С компьютерной системой соединены контроллер и технологическая подсистема ввода/вывода.

Технологическая подсистема ввода/вывода содержит порты ввода/вывода, соединенные с различными полевыми устройствами, установленными по всему предприятию. В число полевых устройств входят аналитическое оборудование различных типов, кремниевые датчики давления, емкостные датчики давления, резистивные датчики температуры, термопары, тензометры, концевые переключатели, выключатели питания, преобразователи расхода, преобразователи давления, емкостные сигнализаторы уровня, весы, преобразователи, установочные приспособления клапанов, модули управления клапанами, силовые приводы, соленоиды и световые индикаторы. Термин «полевые устройства» охватывает все перечисленные типы устройств, а также любые другие устройства, выполняющие функции в распределенной системе управления.

В соответствии с известными технологиями аналоговые полевые устройства обычно соединяются с пунктом управления при помощи токовых петель, образованных из двухпроводных витых пар, причем каждое из устройств соединено с пунктом управления одной двухпроводной витой парой. Аналоговые полевые устройства обладают возможностью реагирования на электрические сигналы или передачи электрических сигналов, параметры которых лежат в пределах определенного диапазона. В типичной конфигурации разность напряжений между двумя проводами пары обычно составляет порядка 20-25 вольт, а сила тока, протекающего в контуре, составляет 4-20 миллиампер. Аналоговое полевое устройство, передающее сигнал в пункт управления, модулирует ток, протекающий в токовом контуре, причем величина тока пропорциональна измеренной технологической переменной. В то же время управление аналоговым полевым устройством, производящим действие под управлением пункта управления, осуществляется с использованием амплитуды тока, протекающего в контуре, которую модулирует порт ввода/вывода технологической системы ввода/вывода, которым, в свою очередь, управляет контроллер. Двухпроводные аналоговые устройства в соответствии с известными технологиями обычно содержат активные электронные элементы, способные принимать из контура до 40 милливатт мощности. Аналоговые полевые устройства, требующие более высокой мощности, обычно соединяются с пунктом управления с использованием четырехпроводного соединения, причем два из четырех проводов используются для подачи питания на такое устройство. Такие устройства, известные в данной области под названием четырехпроводных устройств, не имеют ограничений по мощности, существующих для двухпроводных устройств.

Полевые устройства в соответствии с известными технологиями, как правило, имели либо единственный вход, либо единственный выход, непосредственно соотносящийся к основной функции, выполняемой данным полевым устройством. Например, единственная функция, выполняемая аналоговым резистивным температурным датчиком по известным технологиям, состоит в передаче температуры путем модуляции тока, протекающего в двухпроводной витой паре, а единственная функция, выполняемая аналоговым позиционирующим устройством клапана по известным технологиям, состоит в переключении клапана между открытым и закрытым положениями в соответствии с величиной тока, протекающего в двухпроводной витой паре.

В последнее время в распределенных системах управления начали использовать гибридные системы, в которых цифровые данные накладываются на токовый контур. Одна из таких гибридных систем известна в области систем управления под названием HART (Highway Addressable Remote Transducer - протокол взаимодействия с удаленным датчиком с шинной адресацией) и сходна со спецификацией модема Bell 202. Система HART использует полудуплексный протокол типа «ведущий-ведомый» (master-slave). Как правило, ведущий элемент передает команду и ожидает ответа. При этом ведомый элемент, как правило, ожидает поступления команды и передает ответ при ее получении. Каждая команда или каждый ответ могут быть рассмотрены как сообщения, длина которых может составлять от нескольких байтов до 269 байтов. Сообщение состоит из асинхронных последовательных данных, передаваемых со скоростью 1200 битов в секунду (BPS). Передача производится с использованием частотно-ключевой модуляции (Frequency Shift Keying, FSK), причем логической единице соответствует сигнал с частотой 1200 герц (Гц), а логическому нулю соответствует сигнал с частотой 2200 Гц. Такие сигналы протокола HART модулируются в двухпроводной линии связи, обеспечивающей подачу питания постоянного тока.

В случае использования протокола связи HART центральная или управляющая станция, передающая команду в конкретное полевое устройство, инициирует передачу сообщений, как правило, путем обращения к такому полевому устройству по его уникальному адресу. Такая команда, например, может указывать полевому устройству передать в качестве ответа информацию о своем состоянии, например, текущего зарегистрированного давления или другой информации о состоянии. После приема команды от управляющей станции полевое устройство передает в управляющую станцию ответ, который принимается и обрабатывается. Система HART позволяет управляющей станции производить порядка двух или трех таких транзакций в секунду. Соответственно, хотя протокол HART обеспечивает возможность передачи таких цифровых сообщений при помощи аналоговых носителей, скорость передачи и приема таких сообщений сравнительно низка. Скорость передачи данных входящих и исходящих сообщений HART может требовать обработки таких сообщений процессором с интервалами во избежание чрезмерной задержки выполнения процессором других высокоприоритетных операций. Это, в свою очередь, может требовать использования многочисленных прерываний процессора на каждое сообщение, что приводит к увеличению числа переключений между задачами и других нагрузок на процессор, а также повышает сложность реализации протокола связи в процессоре.

Раскрытие изобретения

В соответствии с одним из примеров осуществления изобретения полевое устройство выполнено с возможностью передачи и приема данных по производственно-технологической сети. Полевое устройство содержит процессор и модуль связи, соединенный с возможностью осуществления связи с производственно-технологической сетью. Модуль связи выполнен с возможностью передачи и приема данных по производственно-технологической сети при помощи первого протокола связи на первой скорости передачи данных. Модуль связи соединен с возможностью осуществления связи с процессором при помощи второго протокола связи на второй скорости передачи данных, большей, чем первая скорость передачи данных.

В соответствии с другим примером осуществления изобретения модуль связи выполнен с возможностью передачи и приема данных по производственно-технологической сети. Модуль связи содержит первый интерфейс связи, второй интерфейс связи, первый приемный буфер и второй приемный буфер. Первый интерфейс связи выполнен с возможностью передачи и приема данных по производственно-технологической сети при помощи первого протокола связи на первой скорости передачи данных. Второй интерфейс связи выполнен с возможностью осуществления связи с процессором при помощи второго протокола связи на второй скорости передачи данных, большей, чем первая скорость передачи данных. Первый приемный буфер выполнен с возможностью сохранения первого объекта сообщения, соответствующего первому сообщению, принятому по производственно-технологической сети. Второй приемный буфер выполнен с возможностью сохранения второго объекта сообщения, соответствующего второму сообщению, принятому по производственно-технологической сети.

В соответствии с другим примером осуществления изобретения способ передачи и приема данных по производственно-технологической сети включает прием модулем связи полевого устройства первого сообщения при помощи первого протокола связи на первой скорости передачи данных. Способ дополнительно включает сохранение модулем связи первого сообщения в первом приемном буфере модуля связи и определение модулем связи того, что 6 первое сообщение содержит целое сообщение в соответствии с первым протоколом связи. Способ дополнительно включает извещение модулем связи процессора полевого устройства о том, что было принято первое сообщение, в ответ на определение того, что первое сообщение содержит целое сообщение и передачу модулем связи первого сообщения в процессор при помощи второго протокола связи на второй скорости передачи данных, большей, чем первая скорость передачи данных.

Краткое описание чертежей

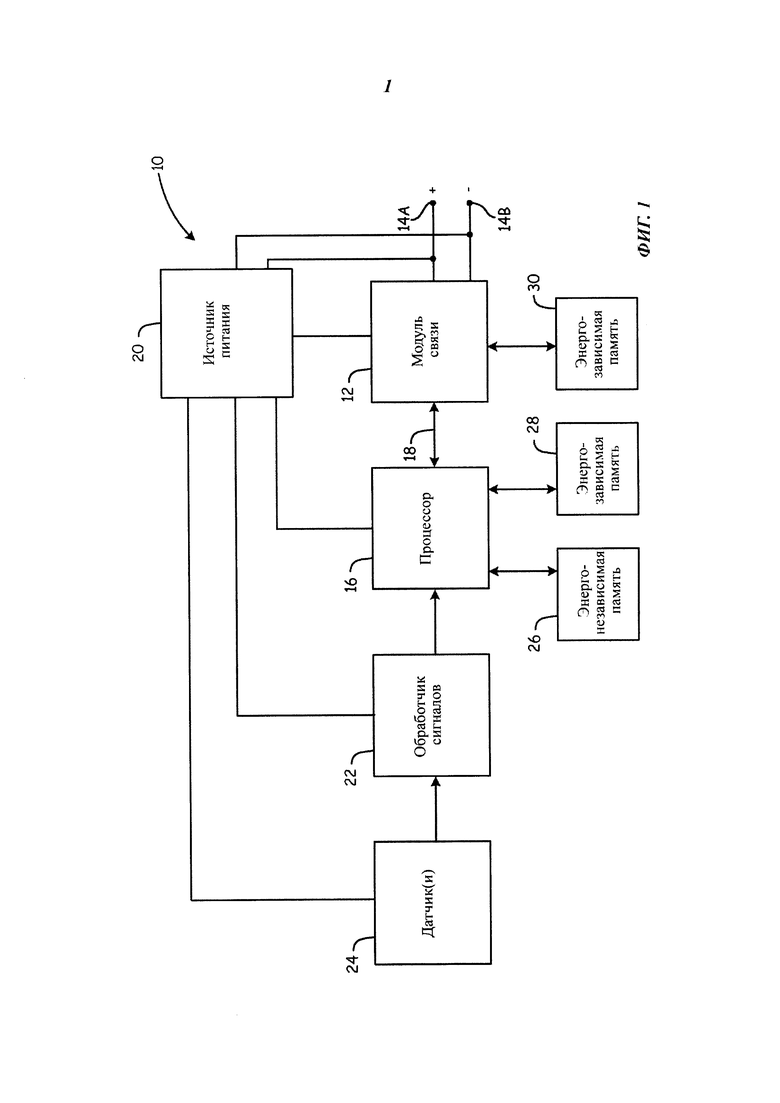

На фиг. 1 представлена схема полевого устройства, содержащего модуль связи, соединенный с возможностью осуществления связи с производственно-технологической сетью с использованием первого интерфейса и соединенный для осуществления связи с процессором с использованием второго интерфейса.

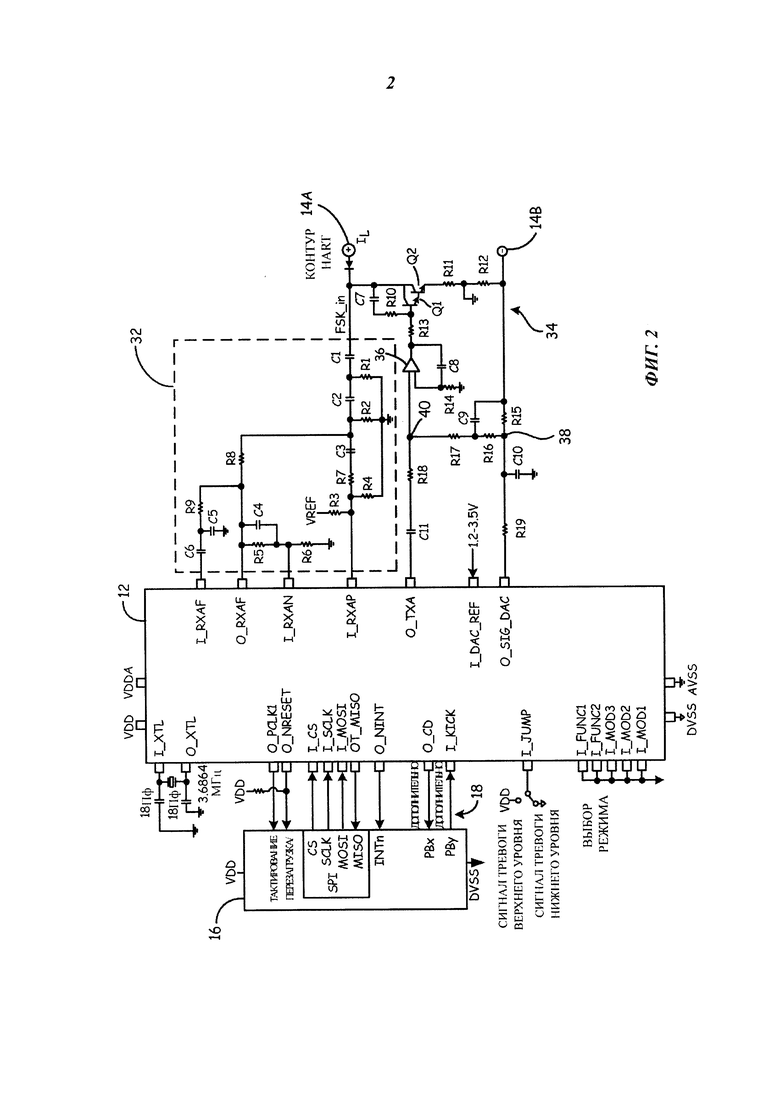

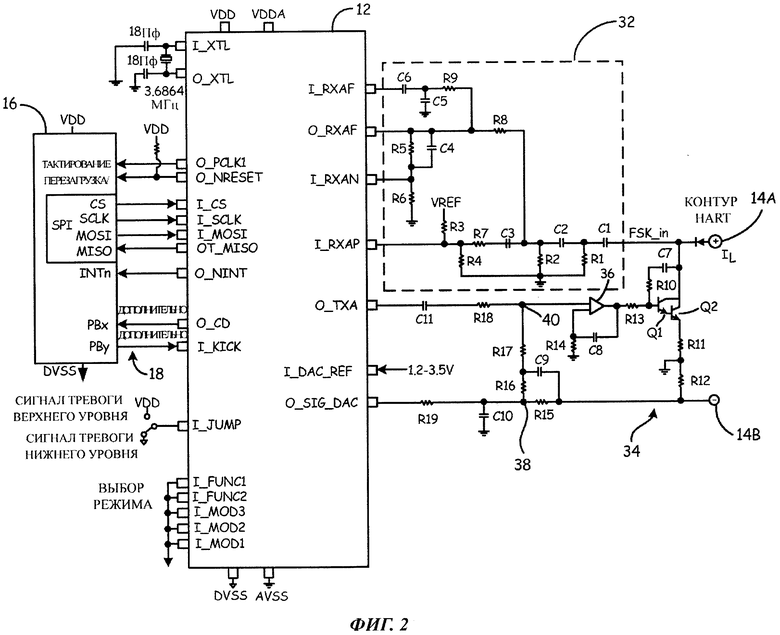

На фиг. 2 представлена схема модуля связи, соединенного для осуществления связи с процессором с использованием протокола последовательного периферийного интерфейса (Serial Peripheral Interface, SPI) и соединенного для передачи и приема данных по производственно-технологической сети с использованием протокола взаимодействия с удаленным датчиком с шинной адресацией (HART).

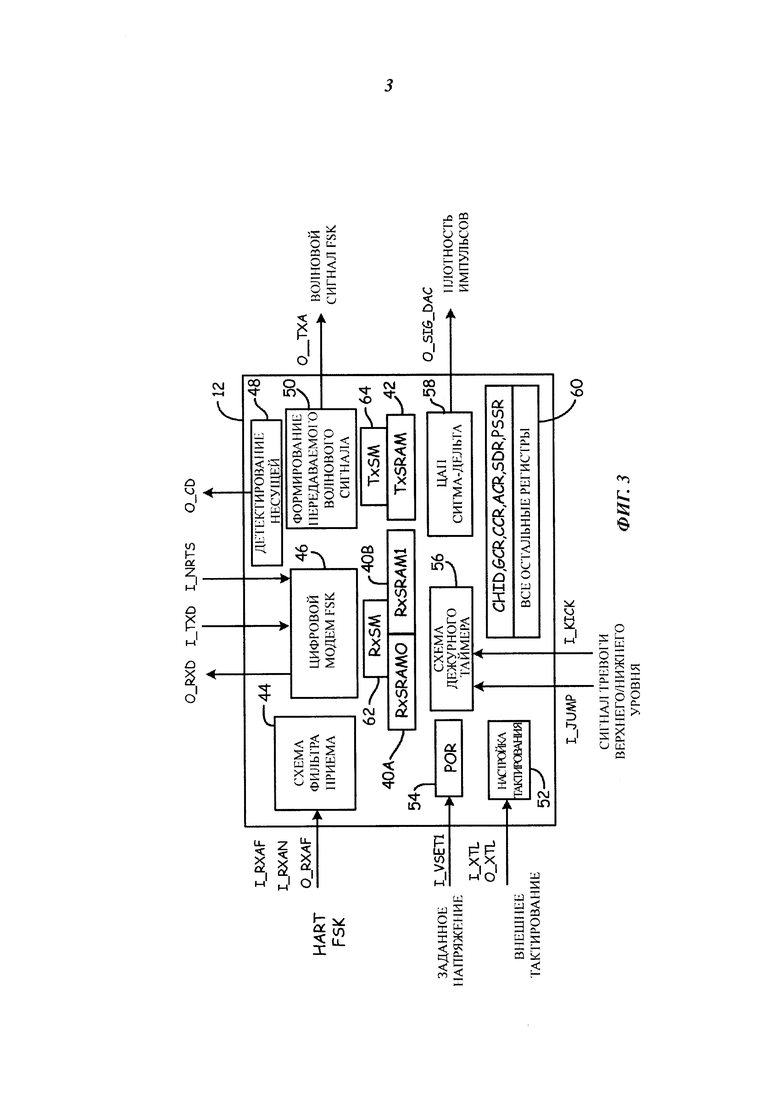

На фиг. 3 представлена схема модуля связи, содержащего буферы сообщений для осуществления связи между процессором и производственно-технологической сетью.

Осуществление изобретения

В соответствии с решением по настоящему изобретению модуль связи, например, модуль связи полевого устройства или другого оборудования, соединен с возможностью осуществления связи с производственно-технологической сетью. Модуль связи содержит первый интерфейс связи и второй интерфейс связи. Первый интерфейс выполнен с возможностью осуществления связи по производственно-технологической сети с помощью первого протокола связи (например, протокола HART) на первой скорости передачи данных, например, равной 1200 битам в секунду. Второй интерфейс связи выполнен с возможностью осуществления связи с процессором с помощью второго протокола связи, например, протокола последовательного периферийного интерфейса (SPI) на второй скорости передачи данных, большей, чем первая скорость передачи данных. Интерфейс с большей скоростью между модулем связи и процессором позволяет процессору получать большее количество данных в единицу времени, что обеспечивает возможность использования меньшего количества прерываний процессора для получения сообщения, принимаемого по производственно-технологической сети. Кроме того, модуль связи может определять уровень ошибочности для принятых сообщений и может обеспечить прерывания процессора так, чтобы осуществлять получение только сообщений, определенных как содержащие некритические ошибки, что обеспечивает дальнейшее уменьшение числа прерываний процессора. Сообщения, принимаемые по производственно-технологической сети, могут быть сохранены в одном или более буферах сообщений модуля связи. Соответственно, модуль связи может обеспечивать прерывание процессора для получения сообщения после приема целого сообщения, вместо обеспечения для каждого сообщения нескольких прерываний процессора. Таким образом, модуль связи, выполненный в соответствии с решением по настоящему изобретению, может уменьшить нагрузку, связанную с переключением процессора между задачами, тем самым позволяя процессору использовать больше времени и/или вычислительных мощностей на задачи, не связанные со связью, например, преобразование и обработку данных. Кроме того, наличие нескольких буферов сообщений может позволить модулю связи сохранять несколько принятых сообщений, например, в случае приема следующего сообщения до получения процессором предыдущего сообщения. Аналогичным образом, в некоторых вариантах осуществления модуль связи может сохранять целое сообщение, предназначенное для передачи по производственно-технологической сети, в буфере передачи, что позволяет модулю связи снять с процессора нагрузку, связанную с задачами передачи сообщений, и передавать целые сообщения без использования для передачи сообщений множества прерываний процессора. Таким образом, технологии в соответствии с настоящим изобретением обеспечивают возможность снижения нагрузки на процессор полевого устройства и повышения устойчивости связи по производственно-технологической сети.

На фиг. 1 представлена блок-схема полевого устройства 10, содержащего модуль 12 связи, соединенный с возможностью осуществления связи с производственно-технологической сетью через положительный вывод 14А и отрицательный вывод 14В (вместе называемые в настоящем описании «выводами 14»), а также соединенный с процессором 16 для осуществления связи через интерфейс 18. Хотя в настоящем описании полевое устройство 10 раскрыто в контексте системы HART, подразумевается, что технологии в соответствии с настоящим изобретением применимы вообще к производственно-технологическим сетям, содержащим полевые устройства, передающие и принимающие данные по такой сети.

Как показано на фиг. 1, полевое устройство 10 может быть соединено с возможностью осуществления связи с производственно-технологической сетью, например, сетью HART, через выводы 14. Выводы 14 обеспечивают интерфейс между полевым устройством 10 и сетью, обеспечивая связь между полевым устройством 10 и контроллером или другим оборудованием, подключенным к сети. Полевое устройство 10 может представлять собой технологический прибор, регистрирующий один или более технологических параметров и выдающий данные, основанные на зарегистрированных параметрах. В некоторых вариантах осуществления полевое устройство 10 может представлять собой технологическое приводное устройство, производящее физические действия в соответствии с командным сообщением, принятым по производственно-технологической сети через выводы 14. В некоторых вариантах осуществления полевое устройство 10 может выполнять как регистрирующие, так и приводные функции.

Как показано на фиг. 1, полевое устройство 10 также может содержать источник 20 питания, схему 22 обработки сигналов, датчики 24, энергонезависимую память 26, энергозависимую память 28 и энергозависимую память 30. Источник 20 питания подает питание на компоненты полевого устройства 10. Например, как показано на фиг. 1, источник 20 питания может получать питание из контура HART (например, мощностью вплоть до 40 милливатт) и подавать питание на такие компоненты как модуль 12 связи, процессор 10, схема 22 обработки сигналов и датчики 24 для обеспечения работы этих компонентов.

Датчики 24 регистрируют один или более технологических параметров или переменных и передают в схему 22 обработки сигналов сигналы датчиков. Сигналы датчиков могут соответствовать одной или более первичным переменным (например, давлению) и/или вторичным переменным (например, температуре). Вторичная переменная может быть использована, например, процессором 16 для корректировки или компенсации сигнала датчика, соответствующего первичной переменной.

Схема 22 обработки сигналов обычно содержит схему аналого-цифрового преобразования, а также средства фильтрации и других операций обработки сигналов для преобразования сигналов датчиков в формат, пригодный для использования процессором 16. Например, схема 22 обработки сигналов может содержать один или более аналого-цифровых преобразователей сигма-дельта и цифровых фильтров для обеспечения подачи в процессор 16 оцифрованных и профильтрованных сигналов датчиков.

Процессор 16 может быть выполнен с возможностью реализации функциональности полевого устройства 10 и/или обработки команд, предназначенных для исполнения им. Например, процессор 16 может быть выполнен с возможностью обработки команд, сохраненных в энергонезависимой памяти 26 и/или в энергозависимой памяти 28, например, команд по созданию и отбору данных, включаемых в сообщения, предназначенных для передачи из полевого устройства 10 по производственно-технологической сети через модуль 12 связи и выводы 14, как более подробно описано ниже. Процессор 16 может представлять собой, например, микропроцессор, контроллер, процессор для цифровой обработки сигналов (Digital Signal Processor, DSP), специализированную интегральную схему (Application Specific Integrated Circuit, ASIC), программируемую пользователем вентильную матрицу (Field-Programmable Gate Array, FPGA) или другую аналогичную отдельную или интегрированную логическую схему.

Энергонезависимая память 26 может быть использована для сохранения программных команд, предназначенных для исполнения процессором 16. В некоторых вариантах осуществления в энергонезависимой памяти 26 могут быть сохранены данные конфигурации, данные калибровки и другая информация, используемая процессором 16 для управления работой полевого устройства 10. В некоторых вариантах осуществления энергонезависимая память 26 может быть выполнена с возможностью сохранения больших объемов информации, чем энергозависимая память, и может быть выполнена с возможностью долговременного хранения информации. Такие элементы энергонезависимой памяти могут представлять собой, например, модули флэш-памяти или модули электрически программируемой памяти (EPROM) или электрически стираемой и программируемой памяти (EEPROM).

Энергозависимая память 28 также может быть выполнена с возможностью сохранения информации в полевом устройстве 10 во время работы. В энергозависимой памяти 28 могут быть сохранены данные, которые могут быть изменены с течением времени (например, в оперативной памяти (RAM) или буферной кэш-памяти). Энергозависимую память 28 можно рассматривать как временную память в том смысле, что основная задача энергозависимой памяти 28 состоит в кратковременном хранении данных. Энергозависимая память может представлять собой, например, оперативную память (Random Access Memory, RAM), динамическую оперативную память (Dynamic Random Access Memory, DRAM), статическую оперативную память (Static Random Access Memory, SRAM) или энергозависимую память иного типа. В некоторых вариантах осуществления программное обеспечение или приложения, исполняемые в полевом устройстве 10, используют энергозависимую память 28 для временного хранения информации во время исполнения соответствующей программы.

Энергозависимая память 30, представленная на схеме подсоединенной к модулю 12 связи, может быть, по существу, аналогична энергозависимой памяти 28. Это означает, что энергозависимая память 30 может представлять собой память типа RAM, DRAM, SRAM или других типов энергозависимой памяти, которые могут быть использованы модулем 12 связи для временного хранения данных во время работы полевого устройства 10. Например, модуль 12 связи может использовать энергозависимую память 30 для сохранения объектов сообщения, соответствующих сообщениям, принимаемым из производственно-технологической сети и/или предназначенным для передачи по производственно-технологической сети, как более подробно описано ниже. Хотя на приведенной схеме представлено полевое устройство 10, содержащее два экземпляра энергозависимой памяти 28 и 30, в некоторых вариантах осуществления полевое устройство 10 может содержать одну энергозависимую память, совместно используемую процессором 16 и модулем 12 связи. В таких случаях полевое устройство 10 может содержать контроллер, обеспечивающий управление доступом к совместно используемой памяти. Хотя память 26, 28 и 30 представлена на схеме в виде элементов, отдельных от процессора 16 и модуля 12 связи, в некоторых вариантах осуществления она может быть интегрирована в одно целое с процессором 16 и/или модулем 12 связи. Например, энергозависимая память 30 может быть интегрирована в одно целое с модулем 12 связи. Аналогичным образом, энергонезависимая память 26 и/или энергозависимая память 28 могут быть интегрированы в одно целое с процессором 16. В некоторых вариантах осуществления модуль 12 связи также может содержать энергонезависимую память, используемую для хранения конфигурации и/или других данных, необходимых для работы модуля 12 связи, или быть соединен с нею.

В некоторых вариантах осуществления энергонезависимая память 26, энергозависимая память 28 и/или энергозависимая память 30 могут быть определены как машиночитаемые носители информации. В некоторых вариантах осуществления машиночитаемые носители информации могут включать постоянные носители информации. Термин «постоянный носитель информации» обозначает носитель информации, не представляющий собой несущую волну или передаваемый сигнал.

Модуль 12 связи соединен с возможностью осуществления связи с производственно-технологической сетью через выводы 14. Модуль 12 связи выполнен с возможностью передачи и приема данных по производственно-технологической сети с использованием протокола связи, например, протокола HART. Модуль 12 связи может представлять собой интегральную схему, например, типа ASIC, комплекс отдельных компонентов, модуль типа FPGA или другую аналогичную интегрированную или дискретную логическую схему.

Используя протокол HART, модуль 12 связи может передавать и принимать (например, базовому устройству и/или от него и/или управляющей станции и/или от нее) сообщения, состоящие из асинхронных последовательных данных, передаваемых со скоростью 1200 битов в секунду. В соответствии с протоколом HART логической единице соответствует сигнал с частотой 1200 Гц, а логическому нулю соответствует сигнал с частотой 2200 Гц. Таким образом, сигналы HART представляют собой сигналы частотно-ключевой модуляции (FSK) с непрерывной фазой, которые демодулируются путем смешивания с частотой свободной генерации локального осциллятора, равной 1700 Гц, с последующей идентификацией фазы результирующего сигнала. Смешивание сигналов HART с частотой 1700 Гц сдвигает по частоте сигналы с частотой 1200 Гц (логические единицы) и сигналы с частотой 2200 Гц (логические нули) в сигналы с частотой +/-500 Гц. Фаза результирующего сигнала либо непрерывно возрастает, что означает, что результирующий сигнал был получен из сигнала с частотой 1200 Гц, либо непрерывно убывает, что означает, что результирующий сигнал был получен из сигнала с частотой 2200 Гц. Побитовое распознавание сигналов протокола HART осуществляется путем регистрации возрастания (логическая единица) или убывания (логический нуль) фазы. Таким образом, модуль 12 связи может модулировать и демодулировать цифровые сигналы на выводах 14 со скоростью передачи данных, равной 1200 битов в секунду, в соответствии с протоколом связи HART.

В соответствии с решением по настоящему изобретению модуль 12 связи также соединен для осуществления связи с процессором 16 через интерфейс 18, причем скорость передачи данных этого соединения выше, чем скорость передачи данных для сообщений, принимаемых через выводы 14. Например, модуль 12 связи может осуществлять связь с процессором 16 через интерфейс 18 с использованием протокола последовательного периферийного интерфейса (SPI) со скоростью передачи данных, достигающей 921,6 килобитов в секунду. В рабочем режиме модуль 12 связи производит демодуляцию сигналов, принятых через выводы 14, и передает данные сообщений в процессор 16 через интерфейс 18. Например, модуль 12 связи может вызывать прерывание процессора 16 для обеспечения выполнения процессором 16 процедуры обслуживания прерывания, предусмотренной для получения сообщения через интерфейс 18. Высокоскоростная связь между модулем 12 связи и процессором 16 позволяет процессору 16 получать большие объемы данных за единицу времени. Соответственно, высокоскоростной интерфейс 18 может обеспечить возможность сокращения числа прерываний процессора 16, необходимого для получения сообщения, по сравнению с числом, которое требовалось бы в случае соединения процессора 16 с модулем 12 связи через более медленный интерфейс.

В некоторых вариантах осуществления модуль 12 связи может сохранять принятые данные сообщений в буфере сообщений (например, в энергозависимой памяти 30) и вызывать прерывание процессора 16 только по приеме целого сообщения. Таким образом, модуль 12 связи может инициировать прерывание процессора 16 один раз на сообщение (например, после получения до тридцати байтов данных), вместо нескольких раз на каждое сообщение, например, после каждых восьми битов принятых данных. В результате модуль 12 связи может способствовать снижению нагрузки по переключению задач на процессор 16, связанной с обслуживанием прерываний, что позволяет процессору 16 выделять больше времени и вычислительной мощности на выполнение других задач, например, на преобразование и обработку данных. Кроме того, в некоторых вариантах осуществления модуль 12 связи может иметь несколько буферов сообщений, каждый из которых соответствует отдельному принятому сообщению. Например, если первое принятое сообщение еще не было получено процессором 16 до приема второго сообщения, модуль 12 связи может сохранить второе сообщение во втором буфере во избежание потери данных или переполнения буфера, что обеспечивает повышение устойчивости связи. В некоторых вариантах осуществления модуль 12 связи может сохранять целое сообщение, предназначенное для передачи по производственно-технологической сети через выводы 14, что позволяет модулю 12 связи производить передачу данных с использованием одного прерывания процессора 16. Таким образом, модуль 12 связи, использующий высокоскоростной интерфейс 18 и/или энергозависимую память 30, может обеспечить снижение рабочей нагрузки на процессор 16 и увеличение устойчивости связи по производственно-технологической сети.

На фиг. 2 схематически представлен один из вариантов осуществления модуля 12 связи, соединенного с процессором 16 через интерфейс 18 и с сетью HART через выводы 14. Как показано на фиг. 2, модуль 12 связи соединен с выводами 14 (и, следовательно, с сетью HART) через входные выводы I_RXAF, I_RXAN и I_RXAP и выходные выводы O_RXAF, O_ТХА и O_SIG_DAC. Таким образом, выводы I_RXAF, I_RXAN, I_RXAP, O_RXAF, O_ТХА и O_SIG_DAC образуют интерфейс, посредством которого модуль 12 связи связан с выводами 14, соединенными с токовым контуром сети HART.

Модуль 12 связи соединен со схемой 32 фильтра интерфейса, обозначенной пунктирными линиями, через выводы I_RXAF, O_RXAF, I_RXAN и I_RXAP. Схема 32 фильтра интерфейса содержит сопротивления R1-R9 и емкости С1-С6, реализующие фильтрование входящих сигналов, принятых через сеть HART. В рабочем режиме сигналы FSK HART, принятые на входе через токовый контур на вводах 14, проходят через схему 32 фильтра интерфейса, которая осуществляет фильтрование и преобразование принятых сигналов.

Как показано на схеме, модуль 12 связи соединен со схемой 34 управления током через выходные выводы O_ТХА и O_SIG_DAC. Схема 34 управления током содержит сопротивления R10-R19, емкости С7-С11, транзисторы Q1 и Q2, а также операционный усилитель 36. Схема 34 управления током выполнена с возможностью управления постоянным током IL, протекающим от вывода 14А к выводу 14В, так, чтобы тот отражал значение технологической переменной, зарегистрированное датчиками 24 (фиг. 1), например, путем регулирования величины тока IL в пределах от четырех до двадцати миллиампер. Кроме того, схема 34 управления током накладывает сигнал FSK переменного тока на сигнал постоянного тока для передачи сообщений по сети HART в соответствии с протоколом HART.

Например, как показано ниже на фиг. 3, модуль 12 связи может содержать цифро-аналоговый преобразователь (ЦАП), преобразующий цифровую информацию (например, цифровую информацию, сохраненную в одном или более буферах сообщений, сигналы датчиков, преобразованные в цифровой формат для обработки процессором 16, или другую цифровую информацию) в аналоговое напряжение. В рабочем режиме модуль 12 выдает сигнал с широтно-импульсной модуляцией, среднее значение напряжения которого на выводе O_SIG_DAC зависит от технологической переменной, зарегистрированной одним или более датчиками 24 (фиг. 1), преобразованной в цифровое значение и обработанной схемой 22 обработки сигналов (фиг. 1), обработанной процессором 16 и принятой модулем 12 связи через интерфейс 18.

Как показано на фиг. 2, напряжение, выдаваемое через вывод O_SIG_DAC, через сопротивления R19, R16 и R17 поступает на положительный (т.е. неинвертирующий) вход операционного усилителя 36. Напряжение, поступающее на положительный вход операционного усилителя 36, основано не только напряжении, выдаваемом с вывода O_SIG_DAC, но комбинируется с напряжением обратной связи, возникающим на сопротивлении R12 обратной связи, подключенном между землей и отрицательным выводом 14В. Соответственно, увеличение тока IL приводит к росту напряжения на сопротивлении R12 обратной связи. Отрицательное напряжение поступает через сопротивление R15 и соединяется с сигналом от O_SIG_DAC в узле 38, тем самым комбинируя положительное напряжение с O_SIG_DAC с отрицательным напряжением обратной связи, поступающим через сопротивления R16 и R17 на положительный вход операционного усилителя 36.

Выход операционного усилителя 36 связан через емкость С8 с инвертирующим (т.е. отрицательным) входом операционного усилителя 36. Сопротивление R14 обеспечивает фильтрование, которое снижает скорость изменения напряжения на отрицательном входе операционного усилителя 36 в соответствии с постоянной времени RC-контура, образованного емкостью С8 и сопротивлением R14, что способствует предотвращению размывания сигнала. Выход операционного усилителя 36 также поступает через сопротивление R13 на базу транзистора Q1, который совместно с транзистором Q2 образует пару Дарлингтона. Ток базы управляет токами коллектора и эмиттера транзистора Q1. С эмиттера транзистора Q1 ток поступает на базу транзистора Q2, второго транзистора пары Дарлингтона. Ток базы второго транзистора управляет величиной тока, протекающего от коллектора к эмиттеру второго, более крупного транзистора Q2, тем самым управляя величиной тока, протекающего от положительного вывода 14А к отрицательному выводу 14В. Таким образом, схема 34 управления током реализует возможность задания базового постоянного тока, протекающего в токовом контуре HART, в зависимости от сигнала на выходе модуля 12 связи на выводе O_SIG_DAC.

Кроме того, схема 34 управления током выполнена с возможностью наложения сигнала FSK переменного тока на сигнал постоянного тока для передачи сообщений по сети HART в соответствии с протоколом HART. Например, как описано выше, модуль 12 связи может передавать и принимать сообщения, состоящие из асинхронных последовательных данных, переданных со скоростью 1200 битов в секунду, причем логической единице соответствует сигнал с частотой 1200 Гц, а логическому нулю - сигнал с частотой 2200 Гц. В рабочем режиме модуль 12 связи выводит на выходной вывод O_ТХА волновой сигнал переменного тока, причем такой волновой сигнал переменного тока содержит либо сигнал с частотой 1200 Гц (т.е. логическую единицу), либо сигнал с частотой 2200 Гц (т.е. логический нуль). Сигнал переменного тока проходит через емкость С11 и сопротивление R18 в узел 40, в котором на неинвертирующий положительный вход операционного усилителя 36 поступает управляющий токовый сигнал IL. Таким образом, сигнал, передаваемый с O_ТХА, накладывается на уровень постоянного тока, установленный в токовом контуре через выводы 14. Поскольку передаваемый сигнал осциллирует между положительным и отрицательным значениями амплитуды, он изменяет моментальный уровень постоянного тока в токовом контуре, в то же время обеспечивая соответствие среднего уровня тока в контуре управляющему постоянному току IL. Соответственно, модуль 12 связи обеспечивает отсутствие искажений сигналом HART значений силы тока, отражающих величины технологической переменной, выводимые полевым устройством.

Кроме того, как показано для варианта осуществления по фиг. 2, модуль 12 связи соединен с процессором 16 через входные выводы I_CS, I_SCLK, I_MOSI, I_KICK и выходные выводы O_PCLK1, O_NRESET, OT_MISO, O_NINT и O_CD. Выходной вывод O_PCLK1, на который модулем 12 связи может быть выведен сигнал программируемого тактового генератора, соединен с входным выводом CLOCK процессора 16. Например, как показано на схеме, модуль 12 связи может дополнительно содержать выводы I_XTL и O_XTL. В некоторых вариантах осуществления входной вывод I_XTL может получать тактовый сигнал от осциллятора, например, от осциллятора с частотой 3,6864 MHz, представленного на фиг. 2. В других примерах осуществления модуль 12 связи может принимать внешний тактовый сигнал через вывод O_XTL. В таких вариантах осуществления входной вывод I_XTL может быть привязан к нижнему уровню. Принятый тактовый сигнал (например, принятый через вывод I_XTL или O_XTL) может быть использован для задания тактовой частоты модуля 12 связи, причем тактовая частота может быть равна принятой тактовой частоте или быть равна доле принятой тактовой частоты, например, одной восьмой принятой тактовой частоты, одной четвертой принятой тактовой частоты или другой доле принятой тактовой частоты. Вычисленная тактовая частота может быть подана в процессор 16 через выходной вывод O_PCKL1. Выходной вывод O_NRESET, соединенный с входным выводом RESET процессора 16, может быть использован для перезагрузки процессора 16, например, в случае невозможности передачи процессором 16 данных в схему дежурного таймера модуля 12 связи. Например, как показано на схеме, входной вывод I_KICK модуля 12 связи может быть соединен с выходным выводом РВу процессора 16. Процессор 16 может выводить через выходной вывод РВу данные (например, один или более битов), принятые модулем 12 связи через входной вывод I_KICK. В ответ на определение того, что через вывод I_KICK данные не принимались в течение предельного времени, схема дежурного таймера модуля 12 связи (представлена на фиг. 3) может подавать в процессор 16 команду перезагрузки через вывод O_NRESET, причем такая команда перезагрузки вызывает перезагрузку процессора 16.

Каждый из контактов I_FUNC1, I_FUNC2, I_MOD3, I_MOD2 и I_MOD1 выбора режима может быть заземлен по мере необходимости, причем комбинация таких заземлений определяет режим работы модуля 12 связи. Например, модуль 12 связи может быть выполнен с возможностью работы в одном из нескольких режимов, например, в полнофункциональном режиме, в частично модифицированном режиме, в базовом режиме модема или в чисто цифровом режиме. Модуль 12 связи может конфигурировать одну или более функциональных и/или физических характеристик модуля 12 связи в соответствии с указанным режимом. Например, в ответ на определение того, что комбинация контактов I_FUNC1, I_FUNC2, I_MOD3, I_MOD2 и I_MOD1 выбора режима указывает на полнофункциональный режим работы, модуль 12 связи может задействовать все физические компоненты и/или все функциональные характеристики модуля 12 связи. В другом примере в ответ на определение того, что указан частично модифицированный режим, модуль 12 связи может отключать функции буферизации сообщений и/или физические компоненты, связанные с выполнением таких функций (например, один или более модулей энергозависимой памяти). В случае определения того, что указан чисто цифровой режим, модуль 12 связи может отключать аналоговые схемы, например, цифро-аналоговые преобразователи и т.п. (т.е. прекращать подачу электропитания на такие компоненты). В ответ на определение того, что указан базовый режим модема, модуль 12 связи может реализовывать только функции модема, например, путем отключения цифро-аналоговых выходов и использования пробуждающего контакта для указания, когда требуется работа модуля 12 связи. Наличие различных режимов работы может обеспечить совместимость модуля 12 связи с различными вариантами осуществления протокола HART, а также снижение энергопотребления в результате отключения физических компонентов, не требуемых при работе в указанном функциональном режиме.

Как показано на фиг. 2, входной вывод I_CS выбора чипа модуля 12 связи соединен с выходным выводом CS выбора чипа процессора 16. Входной вывод I_SCLK тактов последовательных данных модуля 12 связи соединен с выходным выводом SCKL тактов последовательных данных процессора 16. Кроме того, входной вывод I_MOSI «выход ведущего - вход ведомого» (master-out-slave-in) модуля 12 связи соединен с выходным выводом MOSI «выход ведущего - вход ведомого» процессора 16. Выходной вывод OT_MISO «вход ведущего - выход ведомого» (master-in-slave-out) модуля 12 связи соединен с входным выводом «вход ведущего - выход ведомого» процессора 16. Выводы I_CS, I_SCLK, I_MOSI и OT_MOSI модуля 12 связи, соединенные с выводами CS, SCKL, MOSI и MISO процессора 16, могут образовывать интерфейс между модулем 12 связи и процессором 16, выполненный с возможностью осуществления через протокол последовательного периферийного интерфейса (SPI). Такие интерфейсы часто называют шиной SPI. Однако, хотя настоящий пример описан в применении к протоколу SPI, для связи между модулем 12 связи и процессором 16 также могут быть использованы и другие интерфейсы и протоколы. Например, в другом примере осуществления для связи между модулем 12 связи и процессором 16 может быть использован интерфейс последовательной связи (Serial Communications Interface, SCI). Вообще говоря, связь между модулем 12 связи и процессором 16 может быть осуществлена с использованием любого протокола связи, обеспечивающего скорость передачи данных, большую скорости передачи данных для производственно-технологической сети.

Шина SPI обычно работает с одним ведущим устройством и одним или более ведомыми устройствами. В примере, проиллюстрированном на фиг. 2, процессор 16 может быть сконфигурирован в качестве ведущего устройства, а модуль 12 связи может быть сконфигурирован в качестве ведомого устройства. Соответственно, модуль 12 связи принимает через входной вывод I_MOSI данные, переданные процессором 16 через выходной вывод MOSI. Аналогичным образом, процессор 16 принимает через входной вывод MISO данные, переданные модулем 12 связи через выходной вывод OT_MISO. Связь между процессором 16 и модулем 12 связи по шине SPI может осуществляться со скоростью передачи данных, меньшей или равной максимальной тактовой частоте этих устройств. Например, модуль 12 связи может передавать в процессор 16 по шине SPI данные, например, сообщения, принятые по сети HART через выводы 14, (т.е. сообщения, принятые со скоростью передачи 1200 битов в секунду). Аналогичным образом, модуль 12 связи может принимать от процессора 16 по шине SPI сообщения, предназначенные для передачи по сети HART. Передача данных по шине SPI может быть осуществлена со скоростью, большей скорости передачи данных сообщений по сети HART (например, со скоростью передачи данных, большей 1200 битов в секунду), например, со скоростью передачи данных до 921,6 килобита в секунду.

В рабочем режиме в конфигурации по данному варианту осуществления модуль 12 связи принимает сообщения HART через выводы 14 на входных выводах I_RXAF, I_RXAN и I_RXAP. Модуль 12 связи производит демодуляцию принятых сигналов, профильтрованных схемой 32 фильтра интерфейса, для получения последовательных данных, принятых со скоростью передачи данных, равной 1200 битам в секунду. Модуль 12 связи может сохранить принятые данные и/или информацию, соответствующую принятым данным, в одном или более буферах сообщений, как более подробно описано ниже.

В ответ на прием порогового количества данных (например, порогового количества битов, порогового количества байтов, целого сообщения или другого порогового количества данных) модуль 12 связи может передать в процессор 16 указание, инициирующее получение принятых данных в процессоре 16. Например, как показано на фиг. 2, модуль 12 связи может содержать вывод O_NINT прерывания, соединенный с вводом INTn прерывания процессора 16. Модуль 12 связи может передать в процессор 16 уведомление, инициирующее задействование процессором 16 процедуры обслуживания прерывания процессора 16, например, путем регулировки напряжения на выводе O_NINT прерывания между напряжением, соответствующим логическому нулю, (например, напряжением нижнего уровня, равным нулю вольт или близким к этому значению) и напряжением, соответствующим логической единице (например, напряжением верхнего уровня, равным 3,3 вольта или близким к этому значению). Например, в примере, проиллюстрированном на фиг. 2, вывод O_NINT может иметь активное состояние нижнего уровня, что означает, что когда вывод O_NINT находится в состоянии верхнего уровня (соответствующем логической единице), запрос прерывания отсутствует, а когда вывод O_NINT находится в состоянии нижнего уровня (соответствующем логическому нулю), запрашивается прерывание. В других примерах осуществления вывод O_NINT может иметь активное состояние верхнего уровня, означая, что напряжение верхнего уровня указывает запрос прерывания, а напряжение нижнего уровня указывает, что прерывание не запрашивается.

В рабочем режиме модуль 12 связи обеспечивает запуск выводом O_NINT процедуры обслуживания прерывания процессора 16 для обслуживания прерывания. Кроме того, модуль 12 связи может указывать тип прерывания и/или информацию, соответствующую принятому сообщению, через регистры модуля 12 связи. Такая информация, соответствующая принятому сообщению, может содержать информацию о статусе сообщения, информацию об ошибках, число байтов данных в принятом сообщении или другую информацию, соответствующую принятому сообщению. В ответ на прием указания на прерывание через вывод INTn прерывания процессор 16 инициирует обмен данными для получения принятого сообщения по шине SPI. Например, в соответствии с протоколом SPI процессор 16 может обеспечить на выводе CS сигнала выбора чипа, принимаемый модулем 12 связи через входной вывод I_CS, для инициации связи SPI. Кроме того, процессор 16 может передать через выходной вывод SCKL данные для настройки скорости передачи данных, принимаемые модулем 12 связи через входной вывод I_SCLK. Затем производится передача данных между процессором 16 и модулем 12 связи на скорости передачи данных, установленной через выводы SCLK и I_SCLK.

Процессор 16 передает через вывод MOSI процессора 16 данные, подтверждающие установку битов в регистре прерываний модуля 12 связи. В ответ на прием подтверждения модуль 12 отключает вывод O_NINT. Процессор 16 может определить наличие или отсутствие ошибок в принятом сообщении путем считывания одного или более битов регистра статуса принятого сообщения модуля 12 связи. Таким образом, модуль 12 связи может определить наличие или отсутствие ошибок в принятом сообщении, например, путем проверки подтверждения цельности сообщения контрольным байтом. В некоторых вариантах осуществления модуль 12 связи может установить один или более битов регистра, например, регистра статуса принятого сообщения, для извещения процессора 16 о типе и/или наличии ошибки. Кроме того, модуль 12 связи может установить один или более битов регистра, например, регистра числа принятых байтов, для указания числа байтов данных, содержащихся в принятом сообщении и/или объекте сообщения, содержащем сообщение и информацию, соответствующую сообщению (например, информацию о типе сообщения, информацию о статусе сообщения, информацию заголовка сообщения, информацию преамбулы сообщения или информацию других типов). Процессор 16 может считывать регистр числа принятых байтов (через выводы MOSI и MISO) для определения числа байтов данных, содержащихся в принятом сообщении и/или в объекте сообщения. В некоторых вариантах осуществления модуль 12 связи может принимать решение о необходимости извещения процессора 16 о принятом сообщении (например, путем задействования вывода O_NINT прерывания) на основании статуса ошибки принятого сообщения. Например, как более подробно описано ниже, в модуле 12 связи может быть осуществлен конечный автомат, определяющий статус ошибки принятых сообщений, например, ошибку кадрирования, ошибку четности, ошибку промежутков, ошибку потери детектирования несущей, ошибку контрольного байта или другие подобные ошибки. В некоторых вариантах осуществления модуль 12 связи может определять, соответствует ли статус ошибки неустранимой или устранимой ошибке. В таких вариантах осуществления модуль 12 связи может выводить в процессор 16 извещение о принятом сообщении в случае соответствия статуса ошибки устранимой ошибке и не производить вывода извещения о принятом сообщении в случае соответствия статуса ошибки неустранимой ошибке.

В ответ на прием извещения о принятом сообщении (например, в форме прерывания через вывод INTn процессора 16) процессор 16 инициирует обмен данными по шине SPI для получения данных принятого сообщения из модуля 12 связи. Например, процессор 16 может передавать через вывод MOSI данные, принимаемые модулем 12 связи через вывод I_MOSI, причем эти данные указывают объем данных (например, число байтов), которые следует передать из модуля 12 связи в процессор 16. Затребованный объем данных может содержать весь объем данных, указанный в регистре числа принятых байтов, или его часть. Таким образом, процессор 16 может получить целое сообщение и/или объект сообщения в рамках одной транзакции или получить сообщение и/или объект сообщения в рамках нескольких транзакций. В некоторых вариантах осуществления скорость передачи данных в транзакциях по шине SPI позволяет процессору 16 получить целое сообщение и/или объект сообщения в пределах временного кадра, выделяемого процессором 16 для обслуживания прерывания, что позволяет процессору 16 получить весь объем данных в ответ на одно прерывание процессора 16. Соответственно, решение по настоящему изобретению может способствовать снижению нагрузки по переключению процессора 16 между задачами, которое может быть вызвано обслуживанием нескольких прерываний.

В ответ на прием от процессора 16 данных, инициирующих транзакцию, модуль 12 связи передает указанное число байтов данных сообщения в процессор 16 через вывод OT_MISO. Процессор 16 принимает переданные данные через вывод MISO процессора 16. Кроме того, данные, передаваемые модулем 12 связи, могут содержать один или более байтов и/или битов, указывающих на то, что было передано целое сообщение (например, целый кадр протокола HART). Такие байты и/или биты можно считать индикатором конца сообщения (ЕОМ, end-of-message). В ответ на прием индикатора ЕОМ процессор 16 передает извещение о приеме сообщения, например, путем установки одного или более битов в регистре подтверждения приема сообщения модуля 12 связи, чем завершает транзакцию по получению данных сообщения, принятого по сети HART.

Процессор 16 может передавать данные (например, данные сообщений, данные технологических переменных или данные других типов) по сети HART путем передачи данных в модуль 12 связи по шине SPI. Например, процессор 16 может выводить данные сообщений через выходной вывод MOSI, с которого они могут быть приняты модулем 12 связи через входной вывод I_MOSI. Процессор 16 может выводить через вывод MOSI команду включения передачи (принимаемую через входной вывод I_MOSI). В ответ на прием команды включения передачи модуль 12 связи может произвести передачу данных сообщения через выводы 14 путем преобразования цифровых данных сообщения в аналоговый ток с его последующей модуляцией и выводом через выходной вывод O_ТХА и схему 34 управления током, как было описано выше. По завершении передачи всех данных сообщения модуль 12 связи может подать в процессор 16 подтверждение завершения передачи сообщения, например, путем включения вывода O_NINT и записи одного или более битов регистра статуса прерывания, считываемого процессором 16, причем такие один или более битов сообщают о завершении передачи. В ответ процессор 16 может выдать в модуль 12 связи ответное подтверждение, например, путем записи одного или более битов регистра подтверждения прерывания, считываемого модулем 12 связи. В некоторых вариантах осуществления модуль 12 связи может отключать вывод O_NINT по получении от процессора 16 такого подтверждения.

В некоторых вариантах осуществления модуль 12 связи может сохранять целое сообщение и/или объект сообщения, предназначенный для передачи по сети HART, в буфере сообщений модуля 12 связи, как более подробно описано ниже. Таким образом, модуль 12 связи может позволить процессору 16 передать целое сообщение, предназначенное для передачи по сети HART, в пределах времени, выделенного на обслуживание одного прерывания, что способствует снижению нагрузки по переключению процессора 16 между задачами.

Как указано в настоящем описании, модуль 12 связи может передавать и принимать данные сообщений по производственно-технологической сети с использованием первого протокола (например, протокола HART) на первой скорости передачи данных (например, равной 1200 битам в секунду). Модуль 12 связи может сохранять данные сообщений (например, данные принятых сообщений и/или данные сообщений, предназначенных для передачи по производственно-технологической сети) в одном или более буферах сообщений. В ответ на прием по производственно-технологической сети порогового количества данных (например, порогового количества байтов, целого кадра протокола HART или других количеств данных) модуль 12 связи может выдавать процессору 16 извещение о необходимости получения данных сообщения. В некоторых вариантах осуществления модуль 12 связи может выдавать процессору 16 извещение о необходимости получения данных сообщения в соответствии со статусом ошибки принятого сообщения, например, определяющего неустранимый или устранимый характер ошибки. Процессор 16 может получить данные сообщений и передать данные, предназначенные для передачи по производственно-технологической сети, с использованием второго протокола связи (например, протокола SPI) на второй скорости передачи данных (например, до 921,6 килобита в секунду), большей, чем первая скорость передачи данных первого протокола. Соответственно, процессор 16 может передать в модуль 12 связи и/или получить от него большее количество данных за единицу времени, что позволяет процессору 16 получать принятые сообщения и передавать сообщения в ответ на меньшее количество прерываний (например, одно прерывание). Таким образом, решение по настоящему изобретению позволяет снизить нагрузку по переключению процессора 16 между задачами, что позволяет процессору 16 выделять большее время и/или большую вычислительную мощность на задачи, не связанные со связью, например, обработку сигналов и/или преобразование данных.

На фиг. 3 представлена блок-схема одного из вариантов осуществления модуля 12 связи, содержащего буферы 40А и 40В принятых сообщений и буфер 42 передаваемых сообщений для осуществления связи между процессором (например, процессором 16 по фиг. 1-2) и производственно-технологической сетью (например, сетью HART). Как показано на фиг. 3, модуль 12 связи может дополнительно содержать схему 44 приемного фильтра, цифровой модем 46 FSK, схему 48 обнаружения несущей, схему 50 формирования передаваемого волнового сигнала, схему 52 тактовой конфигурации, схему 54 перезагрузки при включении питания (Power On Reset, POR), схему 56 дежурного таймера, ЦАП 58 сигма-дельта и регистры 60.

Схема 54 POR принимает заданное напряжение, подаваемое через вывод I_VSET1. Схема POR может содержать компаратор или другую аналогичную схему для сравнения аналогового напряжения, принимаемого модулем 12 связи (например, от источника 20 питания по фиг. 1) с напряжением, принимаемым через вывод VSET1. В ответ на определение того, что принимаемое аналоговое напряжение меньше чем напряжение, принимаемое через вывод VSET1, схема 54 POR производит перезагрузку (сброс) модуля 12 связи в исходное состояние, например, путем отключения и повторного включения питания компонентов модуля 12 связи. Соответственно, схема 54 POR производит перезагрузку модуля 12 связи при включении питания и в случае падения аналогового напряжения питания модуля 12 связи ниже заданного напряжения (например, для инициализации и защиты от снижений напряжения).

Схема 52 тактовой конфигурации принимает сигналы тактового цикла через выводы I_XTL и O_XTL. Например, как описано выше со ссылками на фиг. 2, схема 52 тактовой конфигурации может принимать тактовый сигнал от осциллятора через вывод I_ХТ1_. В других вариантах осуществления схема 52 тактовой конфигурации может принимать тактовый сигнал от внешнего тактового генератора через вывод O_ХТ1_, а вывод I_ХТ1_ может быть завязан на нижний уровень. Принятый тактовый сигнал может быть использован для задания тактовой частоты модуля 12 связи.

Схема 56 дежурного таймера принимает через вывод I_JUMP информацию о конфигурации аварийного состояния, а через вывод I_KICK-данные, указывающие действия процессора. Например, схема 56 дежурного таймера может быть выполнена с возможностью выдачи команды перезагрузки в ответ на отсутствие принимаемых данных (например, битового переключателя) от процессора через вывод I_KICK в течение предельного промежутка времени (например, половины секунды, одной секунды, двух секунд или другого предельного промежутка времени). Кроме того, схема 56 дежурного таймера может быть выполнена с возможностью выдачи сигнала тревоги в случае обнаружения отсутствия работы процессора (например, через вывод I_KICK), обнаружения ошибки тактирования, сбоя или другого нарушения достоверности тактовых сигналов или других подобных событий. Сигнал тревоги, выдаваемый схемой 56 дежурного таймера, может быть по меньшей мере частично основан на состоянии сигнала, принимаемого через вывод I_JUMP. Например, если напряжение на выводе I_JUMP превышает пороговое напряжение (т.е. чрезмерно велико), схема 56 дежурного таймера может выдавать сигнал тревоги путем обеспечения выдачи из ЦАП 58 сигма-дельта сигнала с максимальным коэффициентом заполнения импульса, например, с 50-процентным коэффициентом заполнения импульса на частоте 230,4 кГц. В другом примере, если напряжение на выводе I_JUMP меньше порогового напряжения (т.е. чрезмерно мало), схема 56 дежурного таймера может выдавать сигнал тревоги, обеспечивая выдачу из ЦАП 58 сигма-дельта постоянного сигнала нижнего или верхнего уровня. ЦАП 58 сигма-дельта может быть соединен с пунктом управления по сети HART и, таким образом, выдавать сигнал тревоги для контроллера и/или управляющего персонала.

Схема 44 приемного фильтра принимает сигналы FSK HART через выводы I_RXAF, I_RXAN и O_RXAF. Схема 48 обнаружения несущей выявляет присутствие в принятом сигнале сигнала FSK HART и выводит извещение об обнаружении несущего сигнала через вывод O_CD (например, в процессор), например, путем установки напряжения на выводе O_CD в состояние, соответствующее логической единице (например, активное состояние верхнего уровня).

Сигналы FSK HART, принятые и обработанные схемой 44 приемного фильтра, направляются в цифровой модем 46 FSK, который в некоторых вариантах осуществления производит демодуляцию сигналов FSK (содержащих частоты 1200 и 2200 Гц) и воспроизводит цифровой сигнал без возврата к нулю (Non-Return-to-Zero, NRZ). В других вариантах осуществления, например, в которых модуль 12 связи работает в функциональном частично-модифицированном режиме работы, цифровой модем 46 FSK принимает через вывод I_TXD цифровые данные (например, от процессора) в формате NRZ. Сигнал NRZ направляется в схему 62 приемного конечного автомата, которая реализует логику конечного автомата, определяющую информацию, соответствующую принятому сообщению, (например, информацию о статусе, информацию об ошибках или другую информацию) и сохраняет такую информацию либо в буфере 40А сообщений, либо в буфере 40В сообщений. Буферы 40А и 40В сообщений могут храниться в энергозависимой памяти модуля 12 связи, например, в энергозависимой памяти 30 (по фиг. 1). Буферы 40А и 40В сообщений могут сохранять объекты сообщения, причем объекты сообщения содержат данные принятого сообщения, а также информацию, соответствующую данным принятого сообщения, например, информацию о статусе (например, информацию о статусе ошибок), определенную приемным конечным автоматом 62, информацию заголовка сообщения, информацию преамбулы сообщения или другую информацию, соответствующую принятому сообщению. Таким образом, модуль 12 связи сохраняет данные принятого сообщения в одном из буферов 40А и 40В сообщений, а приемный конечный автомат 62 определяет и сохраняет информацию, соответствующую принятому сообщению, в соответствующем буфере 40А или 40В сообщений, причем комбинация данных принятого сообщения и информации, соответствующей данным сообщения, определяет объект сообщения.

В рабочем режиме, соответствующем решению по настоящему изобретению, модуль 12 связи сохраняет данные принятого сообщения в приемном буфере 40А и определяет размер принятых данных (например, число байтов), который обновляется в регистре числа принятых байтов в регистрах 60. Кроме того, информация, соответствующая принятому сообщению, например, информация заголовка сообщения, информация о статусе, определенная приемным конечным автоматом 62, и другая подобная информация также сохраняются в приемном буфере 40А. В некоторых вариантах осуществления в ответ на прием порогового количества байтов и/или полного сообщения (например, полного кадра протокола HART) модуль 12 выдает процессору (например, процессору 16 по фиг. 1 и 2) извещение о необходимости получения процессором данных принятого сообщения. Например, как было описано выше со ссылками на фиг. 2, модуль 12 связи может задействовать прерывание процессора для обеспечения выполнения процессором процедуры обслуживания прерывания, инициирующей транзакцию данных для получения данных сообщения через второй интерфейс (например, интерфейс SPI). В случае приема модулем 12 связи данных последующих сообщений до получения процессором принятого объекта сообщения, сохраненного в буфере 40А сообщений, модуль 12 связи может сохранить такие данные последующего сообщения в буфере 40В сообщений, что повышает устойчивость связи благодаря возможности предотвращения ошибок, связанных с потерей данных и/или переполнением буфера. Хотя на схемах представлены два буфера 40А и 40В сообщений, в некоторых вариантах осуществления модуль 12 связи может содержать более двух буферов сообщений. Например, модуль 12 связи может содержать три, четыре, пять или более буферов сообщений для дальнейшего повышения устойчивости связи.

В некоторых вариантах осуществления данные, сохраненные в буфере 40В сообщений, могут быть переданы в процессор после передачи данных из буфера 40А сообщений. В некоторых вариантах осуществления модуль 12 связи выполнен с возможностью передачи данных только из буфера 40А сообщений, так что перед такой передачей данных данные передаются из буфера 40В сообщений в буфер 40А сообщений или изменяется определение буферов сообщений так, чтобы поменять местами идентификаторы буферов 40А и 40В сообщений. Таким образом, модуль 12 связи может назначить один из буферов 40А и 40В сообщений активным буфером. Таким образом, активным буфером сообщений может быть тот буфер сообщений, из которого производится передача данных.

В некоторых вариантах осуществления модуль 12 связи может задействовать прерывание процессора для обеспечения получения процессором данных принятого сообщения на основе статуса ошибки данных принятого сообщения. Например, приемный конечный автомат 62 может определять статус ошибки принятых сообщений (например, по мере приема данных сообщений). В число таких статусов ошибки входят в частности, но не исключительно, ошибки кадрирования, ошибки четности, ошибки промежутков, ошибки потери детектирования несущей и ошибки контрольного байта.

Ошибка кадрирования может соответствовать случаю отсутствия определения и/или неверного положения стопового бита в принятом сообщении. Ошибка четности может соответствовать случаю отсутствия определения и/или неверного значения бита четности в принятом сообщении, например, бита четности, указывающего на отрицательную четность (т.е. нечетное число единиц в байте) при указанной положительной четности (т.е. четном числе единиц в байте), или бита четности, указывающего на положительную четность при указанной отрицательной четности. Например, отрицательная четность может соответствовать биту четности, значение которого равно 1, а положительная четность - биту четности, значение которого равно 0. В протоколе связи может быть указана отрицательная четность, положительная четность или отсутствие четности. Например, в случаях, в которых в протоколе связи HART указана отрицательная четность, наличие в принятом байте данных бита четности, значение которого равно 0, что соответствует положительной четности, может соответствовать ошибке четности. В случаях, в которых указана положительная четность, наличие бита четности, значение которого равно 1 (что соответствует положительной четности) может соответствовать ошибке четности.

Ошибка промежутков может соответствовать случаю неполучения в составе сообщения стартового бита после приема стопового бита в течение порогового промежутка времени, например, порогового промежутка времени, равного 12,5 миллисекунды. Ошибка потери детектирования несущей может соответствовать случаю детектирования слабого сигнала несущей до ожидаемого стопового бита или контрольного байта принимаемого сообщения. Ошибка контрольного байта может соответствовать случаю несоответствия значения контрольного байта, определенного приемным конечным автоматом 62 для принятого сообщения, и значения контрольного байта, содержащегося в принятом сообщении. Например, приемный конечный автомат 62 может определить значение контрольного байта принятого сообщения равным результату операции исключающего ИЛИ над всеми байтами принятого сообщения. Модуль 12 связи может сравнить определенное таким образом значение контрольного байта со значением контрольного байта, содержащимся в принятом сообщении, и установить наличие ошибки контрольного байта в случае несоответствия определенного таким образом значения контрольного байта принятому значению контрольного байта.

Модуль 12 связи может определить статус ошибки как статус неустранимой ошибки или статус устранимой ошибки. Например, статус ошибки кадрирования, соответствующий ошибке кадрирования, обнаруженной в любом байте разделов разграничителя, адреса или счетчика байтов принятого сообщения, можно считать статусом неустранимой ошибки кадрирования. Ошибки кадрирования, обнаруженные в других частях принятого сообщения, можно считать устранимыми ошибками кадрирования. В некоторых вариантах осуществления ошибки четности, обнаруженные в разделе разграничителя, в разделе адреса или в разделе счетчика байтов принятого сообщения, можно считать неустранимыми ошибками четности, а нарушения четности, обнаруженные в разделах данных принятого сообщения, можно считать устранимыми ошибками четности. В некоторых вариантах осуществления нарушения промежутков, ошибки потери детектирования несущей и ошибки контрольных байтов можно считать неустранимыми ошибками. В других вариантах осуществления все ошибки можно считать неустранимыми ошибками. В других вариантах осуществления все ошибки можно считать устранимыми ошибками.

Модуль 12 связи может определять, следует ли задействовать прерывание процессора для получения принятого сообщения, в зависимости от определенного таким образом статуса ошибки сообщения. Например, модуль 12 связи может задействовать прерывание процессора в случае определения, что статус ошибки, соответствующей данному сообщению, является статусом устранимой ошибки, и не задействовать прерывание процессора в ответ на определение того, что статус ошибки представляет собой статус неустранимой ошибки. Таким образом, модуль 12 связи может обеспечить дальнейшее сокращение числа прерываний и ч соответствующей нагрузке, связанной с переключением процессора между задачами, предупреждая прерывание процессора для получения искаженных и/или недействительных сообщений.

Как показано в варианте осуществления по фиг. 3, модуль 12 связи дополнительно содержит буфер 42 передачи и конечный автомат 64 передачи, который может определять статус и другую информацию, соответствующие сообщению, сохраненному в буфере 42 передачи сообщения. В буфере 42 передачи может быть сохранен объект сообщения, содержащий данные сообщения, предназначенного для передачи по сети HART, а также информацию, соответствующую передаваемому сообщению. Например, модуль 12 связи может сохранять буфер 42 передачи в энергозависимой памяти 30 по фиг. 1. В некоторых вариантах осуществления буфер 42 передачи может сохранять целое сообщение (например, целый кадр протокола HART).

В рабочем режиме ЦАП 58 сигма-дельта преобразует данные технологической переменной, предназначенные для передачи по сети HART, в аналоговое напряжение. Такое аналоговое напряжение, выводимое через вывод O_SIG_DAC, используют для управления постоянным током в контуре HART. Кроме того, схема 50 формирования передаваемого волнового сигнала формирует модулированный сигнал переменного, выводимый через вывод O_ТХА, который накладывается на постоянный ток для индикации сигнала протокола HART, как было описано выше.

Таким образом, модуль 12 связи может сохранять данные сообщений в одном или более буферах сообщений, что повышает устойчивость связи и снижает нагрузку по переключению процессора полевого устройства между задачами. Соответственно, решение по настоящему изобретению позволяет такому процессору выделять больше времени и/или вычислительной мощности на задачи, не связанные со связью, например, на обработку и/или преобразование данных.

Хотя настоящее изобретение было раскрыто в вышеприведенном описании со ссылками на один или несколько конкретных примеров вариантов его осуществления, специалисту в данной области должно быть ясно, что в него могут быть внесены различные изменения, а его элементы могут быть заменены на эквивалентные, не выходящие за пределы сущности изобретения. Кроме того, для адаптации решения по изобретению к конкретным ситуациям или материалам могут быть предусмотрены различные модификации, не выходящие за пределы сущности изобретения. Таким образом, изобретение следует считать не ограниченным описанными частными вариантами его осуществления, но охватывающим все варианты осуществления, определенные прилагаемыми пунктами формулы изобретения.

Группа изобретений относится к полевым устройствам. Технический результат – уменьшение нагрузки на процессор устройства и повышение качества связи с процессором устройства. Для этого предложено полевое устройство, которое выполнено с возможностью передачи и приема данных по производственно-технологической сети. Полевое устройство содержит процессор и модуль связи, соединенный с возможностью осуществления связи с производственно-технологической сетью. Модуль связи выполнен с возможностью передачи и приема данных по производственно-технологической сети при помощи первого протокола связи на первой скорости передачи данных. Модуль связи соединен с возможностью осуществления связи с процессором при помощи второго протокола связи на второй скорости передачи данных, большей, чем первая скорость передачи данных. 3 н. и 17 з.п. ф-лы, 3 ил.

1. Полевое устройство, выполненное с возможностью передачи и приема данных по производственно-технологической сети, содержащее

процессор; и

модуль связи, соединенный с возможностью осуществления связи с производственно-технологической сетью, причем модуль связи выполнен с возможностью передачи и приема данных по производственно-технологической сети при помощи первого протокола связи на первой скорости передачи данных и соединен с возможностью осуществления связи с процессором при помощи второго протокола связи на второй скорости передачи данных, большей, чем первая скорость передачи данных,

при этом модуль связи содержит

первый приемный буфер, выполненный с возможностью сохранения первого объекта сообщения, соответствующего первому сообщению, принятому модулем связи по производственно-технологической сети; и

второй приемный буфер, выполненный с возможностью сохранения второго объекта сообщения, соответствующего второму сообщению, принятому модулем связи по производственно-технологической сети,

причем первый объект сообщения содержит первое сообщение и информацию, соответствующую первому сообщению; и

второй объект сообщения содержит второе сообщение и информацию, соответствующую второму сообщению.

2. Полевое устройство по п. 1, отличающееся тем, что модуль связи выполнен с возможностью определения по меньшей мере части информации, соответствующей первому сообщению, и по меньшей мере части информации, соответствующей второму сообщению;

причем модуль связи выполнен с возможностью ввода определенной таким образом части информации, соответствующей первому сообщению, в первый объект сообщения и ввода определенной таким образом части информации, соответствующей второму сообщению, во второй объект сообщения.

3. Полевое устройство по п. 2, отличающееся тем, что модуль связи реализует приемный конечный автомат, сконфигурированный с возможностью определения части информации, соответствующей первому сообщению, и части информации, соответствующей второму сообщению.

4. Полевое устройство по п. 1, отличающееся тем, что модуль связи выполнен с возможностью вывода извещения о приеме сообщения, причем извещение о приеме сообщения обеспечивает запуск Процессором процедуры обслуживания прерывания для получения по меньшей мере одного из первого и второго объектов сообщения из модуля связи при помощи второго протокола связи.

5. Полевое устройство по п. 4, отличающееся тем, что модуль связи выполнен с возможностью определения того, следует ли выводить извещение о приеме сообщения, на основании статуса ошибки активного объекта сообщения из числа первого и второго объектов сообщения.

6. Полевое устройство по п. 5, отличающееся тем, что модуль связи выполнен с возможностью определения необходимости вывода извещения о приеме сообщения на основании определения того, что статус ошибки активного объекта сообщения из числа первого и второго объектов сообщения содержит статус устранимой ошибки.

7. Полевое устройство по п. 5, отличающееся тем, что модуль связи выполнен с возможностью определения необходимости отказа от вывода извещения о приеме сообщения на основании определения того, что статус ошибки активного объекта сообщения из числа первого и второго объектов сообщения содержит статус неустранимой ошибки.

8. Полевое устройство по п. 4, отличающееся тем, что модуль связи выполнен с возможностью вывода извещения о приеме сообщения в процессор в ответ на прием целого сообщения по производственно-технологической сети.

9. Полевое устройство по п. 8, отличающееся тем, что модуль связи выполнен с возможностью сохранения второго сообщения во втором буфере сообщений в ответ на определение того, что получение извещения о приеме сообщения не было подтверждено процессором.

10. Полевое устройство по п. 4, отличающееся тем, что модуль связи соединен с процессором через вывод прерываний;

причем модуль связи выполнен с возможностью вывода извещения о приеме сообщения путем регулировки напряжения на выводе прерываний.

11. Полевое устройство по п. 1, отличающееся тем, что модуль связи содержит буфер передачи, выполненный с возможностью сохранения объекта сообщения, соответствующего сообщению, принятому модулем связи из процессора при помощи второго протокола связи, причем объект сообщения содержит сообщение, принятое из процессора, и информацию, соответствующую сообщению, принятому из процессора;

при этом модуль связи выполнен с возможностью передачи объекта сообщения по производственно-технологической сети при помощи второго протокола связи.

12. Полевое устройство по п. 11, отличающееся тем, что буфер передачи выполнен с возможностью сохранения целого сообщения, предназначенного для передачи по производственно-технологической сети;

причем модуль связи выполнен с возможностью передачи по производственно-технологической сети целого сообщения в ответ на прием целого сообщения из процессора.

13. Полевое устройство по п. 1, отличающееся тем, что

первый протокол связи включает протокол взаимодействия с удаленным датчиком с шинной адресацией (HART);

а второй протокол связи включает протокол последовательного периферийного интерфейса (SPI).

14. Модуль связи, выполненный с возможностью передачи и приема данных по производственно-технологической сети, содержащий

первый интерфейс связи, выполненный с возможностью передачи и приема данных по производственно-технологической сети при помощи первого протокола связи на первой скорости передачи данных;

второй интерфейс связи, выполненный с возможностью осуществления связи с процессором при помощи второго протокола связи на второй скорости передачи данных, большей, чем первая скорость передачи данных;

первый приемный буфер, выполненный с возможностью сохранения первого объекта сообщения, соответствующего первому сообщению, принятому по производственно-технологической сети; и

второй приемный буфер, выполненный с возможностью сохранения второго объекта сообщения, соответствующего второму сообщению, принятому по производственно-технологической сети,

при этом модуль связи выполнен с возможностью соединения с процессором через вывод прерываний;

а также с возможностью вывода извещения о приеме сообщения в процессор через вывод прерываний в ответ на прием целого сообщения по производственно-технологической сети, при этом извещение о приеме сообщения обеспечивает выполнение процессором получения по меньшей мере одного из числа первого и второго объектов сообщения через второй интерфейс связи,

причем второй интерфейс связи содержит вывод типа «выход ведущего - вход ведомого» (MOSI) и вывод типа «вход ведущего - выход ведомого» (MISO);

а модуль связи выполнен с возможностью приема данных из процессора через вывод MOSI и передачи данных в процессор через вывод MISO и с возможностью передачи по меньшей мере одного из первого и второго объектов сообщений через вывод MISO в ответ на прием подтверждения приема сообщения через вывод MOSI.

15. Модуль связи по п. 14, отличающийся тем, что модуль связи выполнен с возможностью сохранения второго сообщения во втором буфере объектов сообщения в ответ на определение того, что подтверждение приема сообщения не было принято через вывод MOSI.

16. Модуль связи по п. 14, отличающийся тем, что дополнительно содержит буфер передачи, выполненный с возможностью сохранения третьего объекта сообщения, соответствующего третьему сообщению, принятому через вывод MOSI;

причем модуль связи выполнен с возможностью передачи третьего объекта сообщения по производственно-технологической сети через первый интерфейс связи.

17. Модуль связи по п. 16, отличающийся тем, что модуль связи выполнен с возможностью передачи третьего объекта сообщения через первый интерфейс связи в ответ на определение того, что третий объект сообщения представляет собой целое сообщение.

18. Способ передачи и приема данных по производственно-технологической сети, включающий:

прием модулем связи полевого устройства первого сообщения при помощи первого протокола связи на первой скорости передачи данных;

сохранение модулем связи первого сообщения в первом приемном буфере модуля связи;

определение модулем связи того, что первое сообщение содержит целое сообщение в соответствии с первым протоколом связи;

извещение модулем связи процессора полевого устройства о том, что было принято первое сообщение, в ответ на определение того, что первое сообщение содержит целое сообщение;

передачу модулем связи первого сообщения в процессор при помощи второго протокола связи на второй скорости передачи данных, большей, чем первая скорость передачи данных;

прием модулем связи из процессора третьего сообщения при помощи второго протокола связи;

определение модулем связи того, что третье сообщение содержит целое сообщение в соответствии с первым протоколом связи; и

передачу модулем связи третьего сообщения по производственно-технологической сети в ответ на определение того, что третье сообщение содержит целое сообщение.

19. Способ по п. 18, отличающийся тем, что дополнительно включает:

прием модулем связи по меньшей мере части второго сообщения при помощи первого протокола связи до передачи первого сообщения в процессор при помощи второго протокола связи; и

сохранение модулем связи второго сообщения во втором приемном буфере модуля связи.

20. Способ по п. 18, отличающийся тем, что извещение процессора о том, что первое сообщение было принято, включает регулировку напряжения вывода прерываний, соединяющего модуль связи с процессором.

| US 5828901 A, 27.10.1998 | |||

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 6947438 B1, 20.09.2005 | |||

| ИЗМЕНЯЕМЫЙ ПОЛЕВОЙ ПРИБОР ДЛЯ АВТОМАТИЗАЦИИ ПРОЦЕССОВ | 2003 |

|

RU2327113C2 |

Авторы

Даты

2018-06-19—Публикация

2014-03-13—Подача