ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее изобретение относится к технологии изготовления жидкокристаллических дисплеев и более конкретно к подложке матрицы тонкопленочных транзисторов и способу ее изготовления, а также к жидкокристаллическому дисплею.

ПРЕДПОСЫЛКИ ДЛЯ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

[0002] С развитием информационного общества быстро возрастает спрос на плоские дисплеи. Жидкокристаллические дисплеи (ЖК-дисплеи) имеют преимущества небольшого размера, низкого потребления энергии и отсутствия излучения, и, таким образом, ЖК-дисплеи доминируют на рынке плоских дисплеев. Однако между изготовителями ЖК-дисплеев также существует жесткая конкуренция. Таким образом, решение задач повышения качества отображения, уменьшения дефектности продукции и снижения стоимости изготовления становятся важной гарантией выживания в условиях жесткой конкуренции. В ЖК-дисплеях обычно используют тонкопленочные транзисторы в качестве драйвера для достижения таких эффектов отображения как высокая скорость, высокая яркость и высокая контрастность.

[0003] Обычно основные способы изготовления тонкопленочных транзисторов с нижним затвором могут включать литографический процесс с четырьмя масками (4 маски) или литографический процесс с пятью масками (5 масок). Способ "5 масок" включает литографический процесс формирования электродов затворов (с использованием маски затворов), литографический процесс формирования активного слоя (с использованием активной маски), литографический процесс формирования электродов истока/стока (с использованием маски истоков/стоков), литографический процесс формирования межслойных переходных отверстий (с использованием маски переходных отверстий) и литографический процесс формирования электродов пикселей (с использованием маски пикселей). Каждый литографический процесс включает осаждение тонкой пленки, травление (включая сухое травление или жидкое травление) и удаление слоя фоторезиста. Таким образом, до завершения процесса "5 масок" процесс, включающий следующие подпроцессы: осаждение тонкой пленки, фототравление, проявление и удаление слоя фоторезиста, повторяют 5 раз.

[0004] Процесс "4 маски" был разработан как модификация процесса "5 масок". Активная маска и маска истоков/стоков могут быть объединены в одной маске путем использования фототравления серого тона (с использованием маски серого тона), полутонового фототравления (с использованием полутоновой маски) или процесса однощелевой маски (с использованием однощелевой маски). То есть, с одной маской посредством регулирования процесса травления можно достигнуть такого же результата травления как с активной маской и маской истоков/стоков.

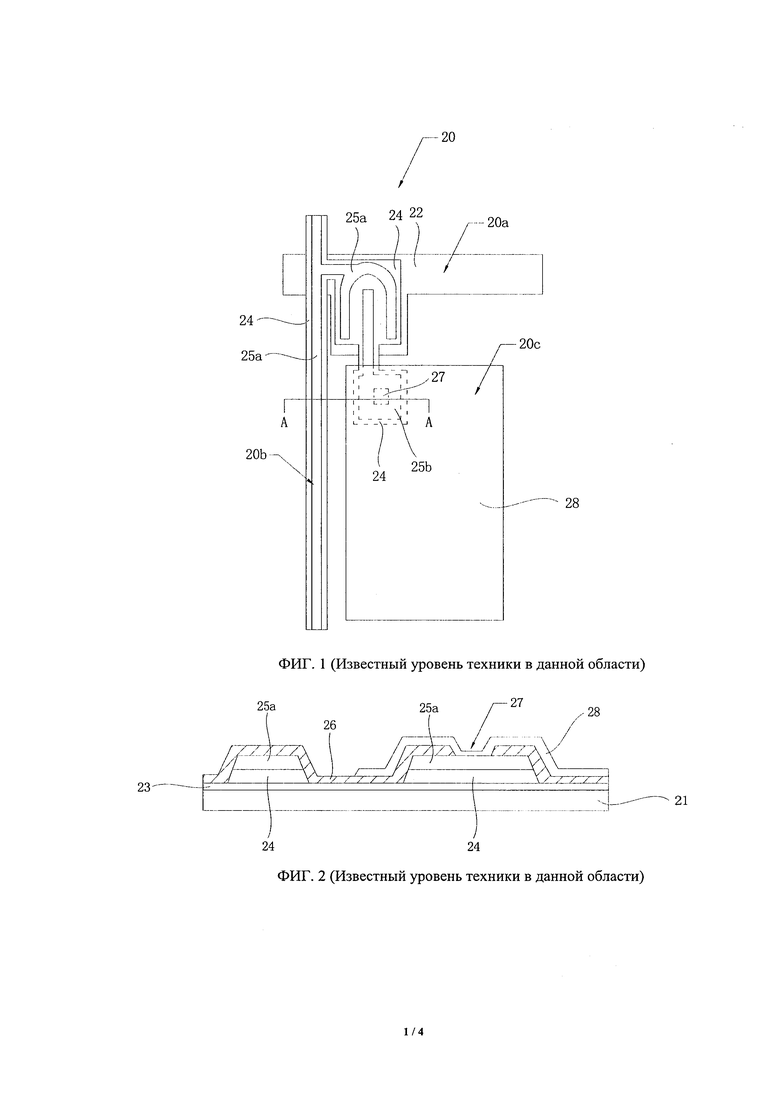

[0005] На Фиг. 1 представлен схематический вид спереди подложки матрицы тонкопленочных транзисторов, изготовленной известным способом с четырьмя масками. На Фиг. 2 представлен схематический вид в разрезе по линии А-А с Фиг. 1. Со ссылкой на Фиг. 1 и 2, подложка 20 матрицы тонкопленочных транзисторов включает область 20а расположения затворов, область 20b расположения электродов данных и область 20с расположения электродов пикселей. Подложка 20 матрицы тонкопленочных транзисторов включает стеклянную подложку 21. На стеклянной подложке 21 последовательно сформированы: металлический слой 22 затворов, диэлектрический слой 23 затворов, активный слой 24, состоящий из аморфного кремния (a-Si), металлический слой 25а истоков и металлический слой 25b стоков, выполненные на активном слое 24, пассивирующий слой 26, проходное отверстие 27, выполненное над металлическим слоем 25b стоков в пассивирующем слое 26, и прозрачный (из оксида индия, легированного оловом, ITO) слой 28 электродов пикселей. Прозрачный слой 28 электродов пикселей соединен с металлическим слоем 25b стоков посредством межслойного проходного отверстия 27.

[0006] Область 20b расположения электродов данных включает диэлектрический слой 23 затворов, активный слой 24, состоящий из аморфного кремния (a-Si), металлический слой 25а истоков на активном слое 24 и пассивирующий слой 26, последовательно выполненные на стеклянной подложке 21. Область 20с расположения электродов пикселей включает диэлектрический слой затворов 23, активный слой 24, состоящий из аморфного кремния (a-Si), металлический слой 25а истоков на активном слое 24, пассивирующий слой 26, проходное отверстие 27, выполненное в пассивирующем слое 26, и прозрачный слой 28 электродов пикселей, последовательно выполненные на стеклянной подложке 21. Прозрачный слой 28 электродов пикселей соединен с металлическим слоем 25b стоков посредством проходного отверстия 27.

[0007] Поскольку аморфный кремний, используемый для формирования активного слоя 24, относится к типу полупроводниковых материалов, активный слой 24 будет производить фототок под сильным светом, излучаемым модулем подсветки ЖК-дисплея, и фототок будет изменять напряжение возбуждения пикселей, подаваемое прозрачным слоем 28 электродов пикселей для жидких пикселей. В заключение, во время процесса испытаний эксплуатационных характеристик происходит искажение отображения на ЖК-дисплее, в частности может легко появиться сложное явление зависания изображения.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

[0008] Для решения технических проблем, существующих в известном уровне техники, цель настоящего изобретения заключается в том, чтобы предложить подложку матрицы тонкопленочных транзисторов, которая включает область расположения электродов пикселей и область расположения электродов данных. Подложка матрицы тонкопленочных транзисторов также включает прозрачный слой электродов пикселей, выполненный в области расположения электродов пикселей, а также включает первый металлический слой, первый диэлектрический слой, слой аморфного кремния, второй металлический слой, второй диэлектрический слой, выполненные в области расположения электродов пикселей, и область расположения электродов данных. Первый диэлектрический слой покрывает первый металлический слой. Слой аморфного кремния, второй металлический слой и второй диэлектрический слой последовательно выполнены на первом диэлектрическом слое. Прозрачный слой электродов пикселей соединен с вторым металлическим слоем посредством проходного отверстия, выполненного в области электродов пикселей второго диэлектрического слоя.

[0009] Помимо этого подложка матрицы тонкопленочных транзисторов также включает слой фоторезиста, расположенный между первым диэлектрическим слоем и слоем аморфного кремния.

[0010] Помимо этого, слой фоторезиста является красным слоем фоторезиста, зеленым слоем фоторезиста или синим слоем фоторезиста.

[0011] Еще одна цель настоящего изобретения заключается в том, чтобы предложить способ изготовления подложки матрицы тонкопленочных транзисторов. Способ включает следующие этапы: А) формирование первого металлического слоя в области расположения электродов пикселей и области расположения электродов данных с использованием первой фотомаски; В) осаждение первого диэлектрического слоя; С) формирование второго металлического слоя на первом диэлектрическом слое с использованием второй фотомаски; D) осаждение второго диэлектрического слоя; Е) выполнение проходного отверстия в области расположения электродов пикселей второго диэлектрического слоя с использованием третьей фотомаски; F) формирование прозрачного слоя электродов пикселей на области расположения электродов пикселей второго диэлектрического слоя с использованием четвертой фотомаски, при этом прозрачный слой электродов пикселей соединен с областью расположения электродов пикселей второго металлического слоя посредством проходного отверстия.

[0012] Помимо этого, перед этапом С), способ также включает этап осаждения слоя фоторезиста на первом диэлектрическом слое.

[0013] Помимо этого, слой фоторезиста является красным слоем фоторезиста, зеленым слоем фоторезиста или синим слоем фоторезиста.

[0014] Еще одна цель настоящего изобретения заключается в том, чтобы предложить жидкокристаллический дисплей, который включает описанную выше подложку матрицы тонкопленочных транзисторов.

[0015] В вариантах осуществления настоящего изобретения первый металлический слой сформирован ниже слоя аморфного кремния. Поскольку первый металлический слой состоит из непрозрачного металлического материала, первый металлический слой может блокировать лучи интенсивного света, создаваемые модулем подсветки ЖК-дисплея, и слой аморфного кремния защищен от облучения лучами интенсивного света. Таким образом, слой аморфного кремния не создает фототок и не изменяет напряжение возбуждения пикселей, подаваемое на прозрачный слой электродов пикселей, и не создает искажений на ЖК-дисплее. Другими словами, явление зависания изображения не возникает. Помимо этого, присутствует слой фоторезиста, выполненный между первым диэлектрическим слоем и слоем аморфного кремния, и слой фоторезиста имеет малую имеет малую диэлектрическую постоянную и большую толщину. Таким образом, слой фоторезиста увеличивает интервал между первым металлическим слоем и вторым металлическим слоем. Емкость между первым металлическим слоем и вторым металлическим слоем значительно снижена Поэтому можно избежать состояния недостаточной подзарядки или ошибки в подзарядке пикселей, которые могут быть вызваны большой резистивно-емкостной задержкой (RC-задержкой), и повысить качество отображения ЖК-дисплея.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0016] Со ссылками на следующие фигуры чертежей описаны вышеуказанные и другие аспекты, характеристики и преимущества вариантов осуществления настоящего изобретения, которые в результате станут более понятными. На чертежах показано следующее.

[0017] Фиг. 1 - схематический вид спереди подложки матрицы тонкопленочных транзисторов, изготовленной по способу "4 маски" из известного уровня техники.

[0018] Фиг. 2 - схематический вид в разрезе по линии А-А с Фиг. 1.

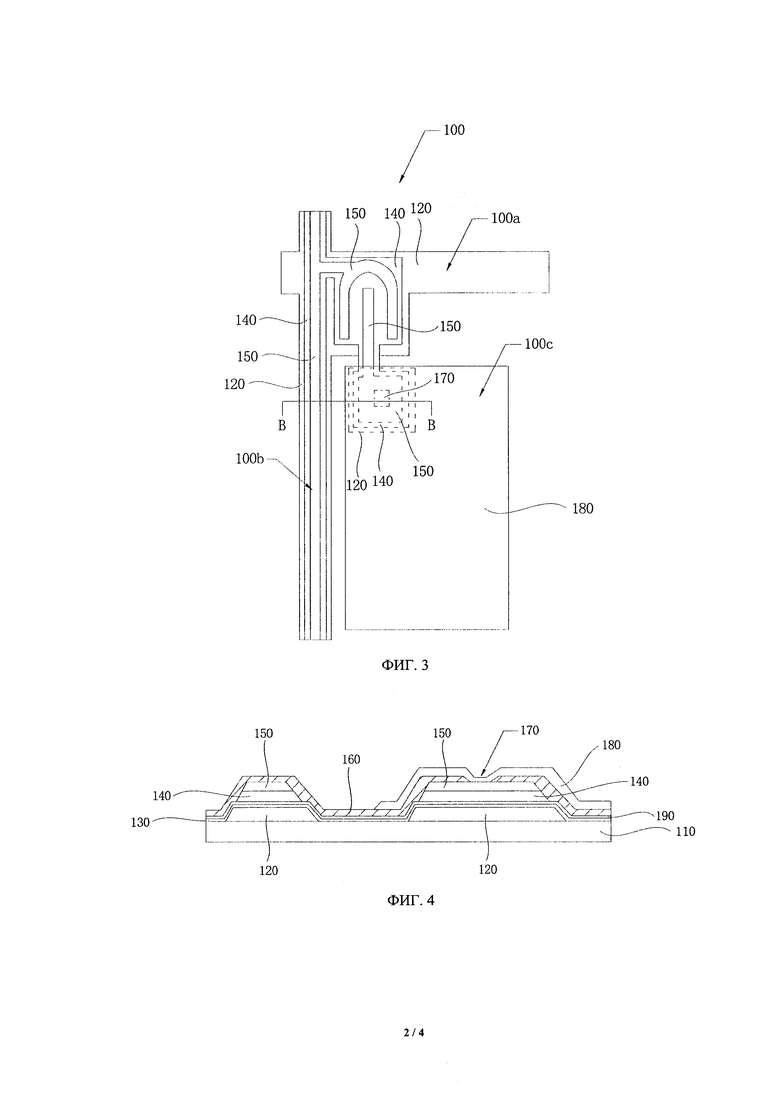

[0019] Фиг. 3 - схематический вид спереди подложки матрицы тонкопленочных транзисторов согласно одному варианту осуществления настоящего изобретения.

[0020] Фиг. 4 - схематический вид в разрезе по линии В-В с Фиг. 3.

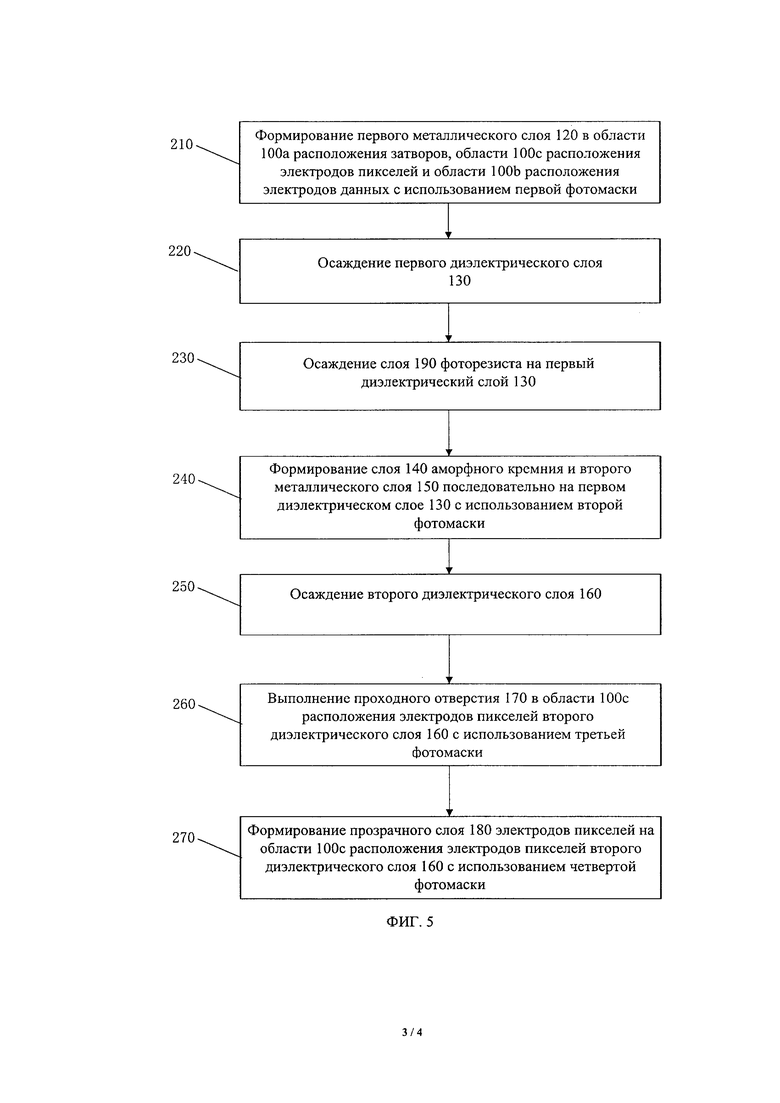

[0021] Фиг. 5 - технологическая схема способа изготовления подложки матрицы тонкопленочных транзисторов согласно одному варианту осуществления настоящего изобретения.

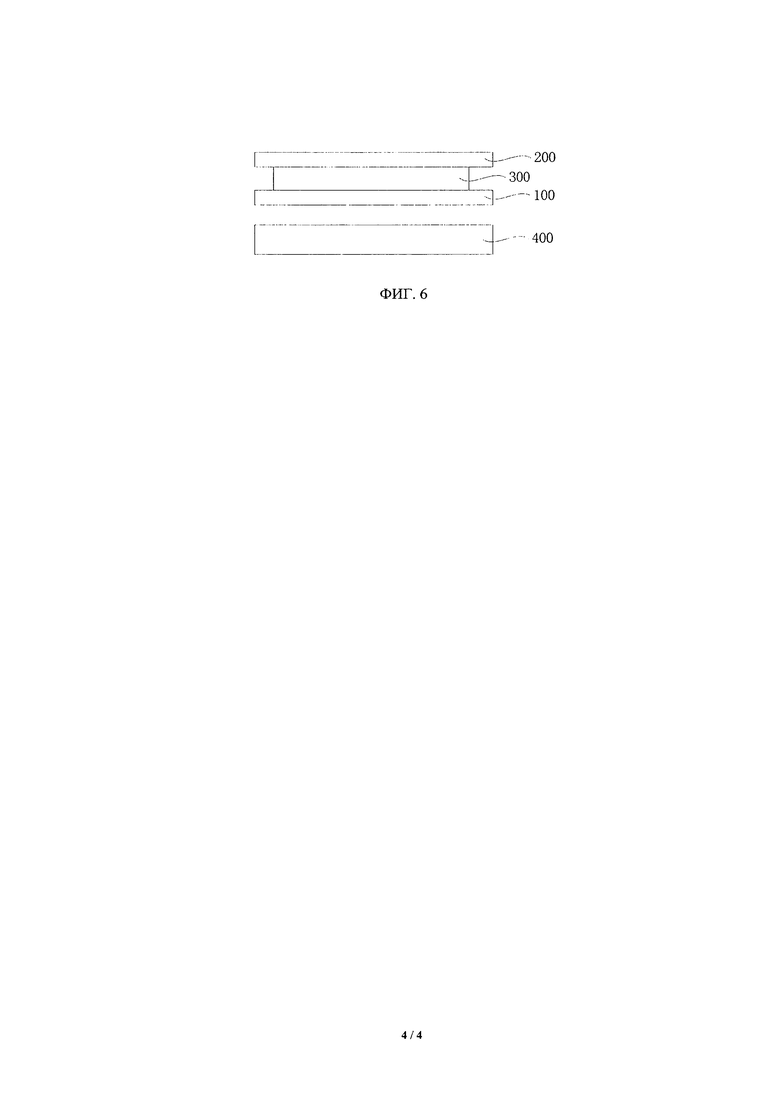

[0022] Фиг. 6 - схематический вид жидкокристаллического дисплея согласно одному варианту осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0023] Далее варианты осуществления настоящего изобретения будут описаны со ссылками на чертежи. Однако для реализации настоящего изобретения также можно использовать много других способов, и настоящее изобретение не должно истолковываться только как описанные варианты осуществления. Наоборот, варианты осуществления представлены для объяснения принципов и способов практического применения настоящего изобретения, чтобы позволить средним специалистам в данной области техники понять варианты осуществления настоящего изобретения и осуществить модификации в этих вариантах осуществления для того, чтобы они подходили к конкретному применению.

[0024] Следует сказать, что термины "первый" и "второй" использованы для описания разных элементов. Однако эти элементы не ограничены этими терминами. Эти термины использованы только для того, чтобы отличать один элемент от другого.

[0025] На Фиг. 3 представлен схематический вид спереди подложки матрицы тонкопленочных транзисторов согласно одному варианту осуществления настоящего изобретения. На Фиг. 4 представлен схематический вид в разрезе по линии В-В с Фиг. 3.

[0026] Со ссылкой на Фиг. 3 и 4, подложка матрицы тонкопленочных транзисторов 100, предлагаемая в одном варианте осуществления настоящего изобретения, включает область 100а расположения электродов затворов, область 100b расположения электродов данных и область 100с расположения электродов пикселей.

[0027] Подложка матрицы тонкопленочных транзисторов 100 также включает подложку (например, стеклянную подложку) 110 и первый металлический слой (т.е., металлический слой затворов) 120, первый диэлектрический слой (т.е., диэлектрический слой затворов) 130, покрывающий первый металлический слой 120, аморфный слой (т.е., активный слой) 140, второй металлический слой 150, покрывающий слой 140 аморфного кремния, второй диэлектрический слой (или пассивирующий слой) 160, проходное отверстие 170 и прозрачный слой 180 электродов пикселей (т.е., слой оксида индия, легированного оловом), последовательно сформированные на подложке 110 в указанном порядке. Часть второго металлического слоя 150 в области 110с расположения электродов пикселей является металлическим слоем стоков, и часть второго металлического слоя 150 в области 100а расположения затворов или области 100с расположения электродов данных является металлическим слоем истоков. Проходное отверстие выполнено над металлическим слоем стоков во втором диэлектрическом слое 160. Прозрачный слой 180 электродов пикселей соединен с металлическим слоем стоков посредством проходного отверстия 170.

[0028] Согласно данному варианту осуществления, в области 110а расположения затворов подложка 100 матрицы тонкопленочных транзисторов включает первый металлический слой 120, первый диэлектрический слой 130, слой аморфного кремния 140, второй металлический слой 150 (то есть, металлический слой истоков на слое 140 аморфного кремния) и второй диэлектрический слой 160, выполненный на подложке 110, в указанном порядке. В области 100b расположения электродов данных подложка 100 матрицы тонкопленочных транзисторов включает первый металлический слой 120, первый диэлектрический слой 130, слой 140 аморфного кремния, второй металлический слой 150 (то есть, металлический слой истоков на слое 140 аморфного кремния) и второй диэлектрический слой 160, сформированный на подложке 110 в указанном порядке. В области 100с расположения электродов пикселей подложка 100 матрицы тонкопленочных транзисторов включает первый металлический слой 120, первый диэлектрический слой 130, слой 140 аморфного кремния, второй металлический слой 150 (то есть, металлический слой стоков на слое 140 аморфного кремния), второй диэлектрический слой 160, проходное отверстие 170 над металлическим слоем стоков и во втором диэлектрическом слое и прозрачный слой 180 электродов пикселей, сформированный на подложке 110 в указанном порядке. Прозрачный слой 180 электродов пикселей соединен с металлическим слоем стоков посредством проходного отверстия 170.

[0029] Как сказано выше, в каждой области есть первый металлический слой 120 ниже слоя аморфного кремния 140. Поскольку первый металлический слой 120 состоит из непрозрачного металлического материала, то первый металлический слой 120 может блокировать лучи интенсивного света, излучаемые модулем подсветки ЖК-дисплея, и слой 140 аморфного кремния защищен от облучения лучами интенсивного света. Таким образом, слой 140 аморфного кремния не производит фототок и не изменяет напряжение возбуждения пикселей, подаваемое на прозрачный слой электродов пикселей, и не создает искажения отображения на ЖК-дисплее. Другими словами, явление зависания изображения на ЖК-дисплее не происходит.

[0030] Помимо этого, подложка 100 матрицы тонкопленочных транзисторов данного варианта осуществления также включает слой 190 фоторезиста. Слой 190 фоторезиста сформирован между первым диэлектрическим слоем 130 и слоем 140 аморфного кремния. Помимо этого, слой 190 фоторезиста сформирован в каждой области. Слой 190 фоторезиста имеет малую диэлектрическую постоянную и большую толщину. Таким образом, слой 190 фоторезиста увеличивает интервал между первым металлическим слоем 120 и вторым металлическим слоем 150. Емкость между первым металлическим слоем 120 и вторым металлическим слоем 150 значительно уменьшена. Поэтому можно избежать состояния недостаточной подзарядки или ошибки в подзарядке пикселей, которые могут быть вызваны большой резистивно-емкостной задержкой (RC-задержкой), и качество отображения ЖК-дисплея повышено. В данном варианте осуществления слой 190 фоторезиста может быть красным слоем фоторезиста, зеленым слоем фоторезиста или синим слоем фоторезиста.

[0031] Далее описан способ изготовления подложки матрицы тонкопленочных транзисторов согласно одному варианту осуществления настоящего изобретения. На Фиг. 5 представлена технологическая схема способа изготовления подложки матрицы тонкопленочных транзисторов согласно данному варианту осуществления.

[0032] Со ссылкой на Фиг. 3-5, на этапе 210 первый металлический слой 120 формируют в области 100а расположения затворов, области 100 с расположения электродов пикселей и области 100b расположения электродов данных с использованием первой фотомаски. На этапе 210 первую металлическую пленку осаждают на подложку 110, и затем эту первую металлическую пленку экспонируют с использованием первой фотомаски, проявляют и травят, используя способ жидкостного травления. Первый металлический слой 120 формируют после удаления слоя фоторезиста с первой металлической пленки. Первой металлической пленкой может быть металлическая пленка из Та, МоТа, MoW или Аl.

[0033] В) На этапе 220 осаждают первый диэлектрический слой 130. Здесь первый диэлектрический слой 130 также именуется как диэлектрический слой затворов, и его осаждают на каждую область первого металлического слоя 120 и на часть подложки 110, которая не покрыта первым металлическим слоем 120.

[0034] На этапе 240 слой 140 аморфного кремния и второй металлический слой 150 последовательно формируют на первом диэлектрическом слое 130 с использованием второй фотомаски. Здесь второй металлический слой 150 в области 100а расположения затворов и области 100b расположения электродов данных является металлическим слоем истоков, и второй металлический слой 150 в области 100с расположения электродов пикселей является металлическим слоем стоков. На этапе 240 слой аморфного кремния и вторую металлическую пленку осаждают на первый диэлектрический слой 130, и затем вторую металлическую пленку экспонируют, используя вторую фотомаску, проявляют и травят, используя жидкостный способ травления и сухой способ травления. Слой 140 аморфного кремния (активный слой) и второй металлический слой 150 формируют после удаления фоторезиста с второй металлической пленки.

[0035] На этапе 250 осаждают второй диэлектрический слой 160. Здесь второй диэлектрический слой 160 также именуется пассивирующим слоем. Второй диэлектрический слой 160 осаждают на второй металлический слой 150 во всех областях, а также осаждают на части первого диэлектрического слоя 130, которые не покрыты слоем 140 аморфного кремния и вторым металлическим слоем 150.

[0036] На этапе 260 проходное отверстие 170 выполняют в области 100с расположения электродов пикселей второго диэлектрического слоя 160 с использованием третьей фотомаски. На этапе 260 второй диэлектрический слой 160 экспонируют, используя третью фотомаску, проявляют, травят, используя сухой способ травления, и затем фоторезист удаляют с второго диэлектрического слоя 160, чтобы выполнить проходное отверстие 170.

[0037] На этапе 270 прозрачный слой 180 электродов пикселей (слой оксида индия, легированного оловом) формируют на области 100с расположения электродов пикселей второго диэлектрического слоя 160 с использованием четвертой фотомаски. Прозрачный слой 180 электродов пикселей соединен с вторым металлическим слоем 150 (т.е., металлическим слоем стоков) посредством проходного отверстия 170. На этапе 270 прозрачную пленку электродов пикселей осаждают на второй диэлектрический слой 160. Осажденную прозрачную пленку электродов пикселей экспонируют, используя четвертую фотомаску, проявляют, травят, используя способ жидкостного травления, и затем удаляют фоторезист, чтобы удалить части прозрачной пленки электродов пикселей в области 100с расположения электродов пикселей, оставляя части прозрачной пленки электродов пикселей в области 100с расположения электродов пикселей. Оставшаяся прозрачная пленка электродов пикселей формирует прозрачный слой 180 электродов пикселей в области 100с расположения электродов пикселей.

[0038] Дополнительно в данном варианте осуществления способ согласно варианту осуществления настоящего изобретения может также включать этап 230 перед этапом 240. На этапе 230 слой 190 фоторезиста осаждают на первый диэлектрический слой 130. Здесь слой 190 фоторезиста осаждают на первый диэлектрический слой 130 во всех областях расположения. В данном варианте осуществления слой 190 фоторезиста может быть красным слоем фоторезиста, зеленым слоем фоторезиста или синим слоем фоторезиста.

[0039] На Фиг. 6 представлен схематический вид ЖК-дисплея согласно одному варианту осуществления настоящего изобретения.

[0040] Со ссылкой на Фиг. 6, ЖК-дисплей данного варианта осуществления включает панель ЖК-дисплея и модуль 400 подсветки, расположенный напротив панели ЖК-дисплея. Модуль 400 подсветки является источником освещения панели ЖК-дисплея, и панель ЖК-дисплея использует свет от модуля 400 подсветки, чтобы отображать изображения. Панель ЖК-дисплея может включать следующие компоненты: описанную выше подложку 100 матрицы тонкопленочных транзисторов, вторую подложку 200 (т.е., подложку фоторезиста), которая включает черную матрицу и выравнивающий слой, слой 300 жидкого кристалла, введенный между подложкой 100 матрицы тонкопленочных транзисторов и второй подложкой 200. Подложка 100 матрицы тонкопленочных транзисторов и вторая подложка 200 расположены напротив друг друга.

[0041] Поскольку вторая подложка 200 в данном варианте осуществления такая же как и в известном уровне техники, то конструкция второй подложки 200 может быть описана в соответствующей области техники и здесь детализирована не будет. Модуль 400 подсветки в данном варианте осуществления также может быть известным модулем подсветки, конструкция модуля 400 подсветки может быть описана в соответствующей области техники и здесь детализирована не будет.

[0042] Хотя настоящее изобретение описано со ссылками на варианты осуществления, средние специалисты в данной области техники поймут, что форма или детали варианта осуществления могут быть изменены, но без нарушения сущности и объема настоящего изобретения, которые ограничены пунктами формулы изобретения или их эквивалентами.

Подложка матрицы тонкопленочных транзисторов включает область расположения электродов пикселей, область расположения электродов данных, прозрачный слой электродов пикселей, сформированный в области расположения электродов пикселей, первый металлический слой, первый диэлектрический слой, слой аморфного кремния, второй металлический слой, второй диэлектрический слой, сформированные в области расположения электродов пикселей и области расположения электродов данных. Первый диэлектрический слой покрывает первый металлический слой. Слой аморфного кремния, второй металлический слой и второй диэлектрический слой последовательно выполнены на первом диэлектрическом слое. Прозрачный слой электродов пикселей соединен со вторым металлическим слоем посредством проходного отверстия, выполненного в области электродов пикселей второго диэлектрического слоя. Подложка матрицы тонкопленочных транзисторов включает слой фоторезиста, сформированный между первым диэлектрическим слоем и слоем аморфного кремния. Кроме того, также предложены способ изготовления подложки матрицы тонкопленочных транзисторов и жидкокристаллический дисплей, включающий подложку матрицы тонкопленочных транзисторов. Изобретение обеспечивает получение тонкопленочных транзисторов для жидкокристаллических дисплеев с обеспечением таких эффектов отображения, как высокая скорость, высокая яркость и высокая контрастность. 3 н. и 3 з.п. ф-лы, 6 ил.

1. Подложка матрицы тонкопленочных транзисторов, включающая:

область расположения электродов пикселей и область расположения электродов данных;

подложку матрицы тонкопленочных транзисторов, также включающую прозрачный слой электродов пикселей, сформированный в области расположения электродов пикселей и включающий первый металлический слой, первый диэлектрический слой, слой аморфного кремния, второй металлический слой, второй диэлектрический слой, выполненный в области расположения электродов пикселей и области расположения электродов данных;

первый диэлектрический слой, покрывающий первый металлический слой;

слой аморфного кремния, второй металлический слой и второй диэлектрический слой, последовательно сформированные на первом диэлектрическом слое;

прозрачный слой электродов пикселей, соединенный со вторым металлическим слоем посредством проходного отверстия, выполненного в области электродов пикселей второго диэлектрического слоя,

отличающаяся тем, что

включает слой фоторезиста, сформированный между первым диэлектрическим слоем и слоем аморфного кремния.

2. Подложка матрицы тонкопленочных транзисторов по п. 1, отличающаяся тем, что слой фоторезиста является красным слоем фоторезиста, зеленым слоем фоторезиста или синим слоем фоторезиста.

3. Способ изготовления подложки матрицы тонкопленочных транзисторов, включающий:

А) формирование первого металлического слоя в области расположения электродов пикселей и области расположения электродов данных с использованием первой фотомаски;

B) осаждение первого диэлектрического слоя;

C) формирование второго металлического слоя на первом диэлектрическом слое с использованием второй фотомаски;

D) осаждение второго диэлектрического слоя;

E) выполнение проходного отверстия в области расположения электродов пикселей второго диэлектрического слоя с использованием третьей фотомаски;

F) формирование прозрачного слоя электродов пикселей на области расположения электродов пикселей второго диэлектрического слоя с использованием четвертой фотомаски, отличающийся тем, что прозрачный слой электродов пикселей соединен с областью расположения электродов пикселей второго металлического слоя посредством проходного отверстия,

причем перед выполнением этапа (С) выполняют этап осаждения слоя фоторезиста на первый диэлектрический слой.

4. Способ по п. 3, отличающийся тем, что слой фоторезиста является красным слоем фоторезиста, зеленым слоем фоторезиста или синим слоем фоторезиста.

5. Жидкокристаллический дисплей, включающий подложку матрицы тонкопленочных транзисторов, вторую подложку напротив подложки матрицы тонкопленочных транзисторов и слой жидкого кристалла, введенный между подложкой матрицы тонкопленочных транзисторов и второй подложкой;

причем подложка матрицы тонкопленочных транзисторов включает область расположения электродов пикселей и область расположения электродов данных;

и причем подложка матрицы тонкопленочных транзисторов также включает прозрачный слой электродов пикселей, сформированный в области расположения электродов пикселей, а также включает первый металлический слой, первый диэлектрический слой, слой аморфного кремния, второй металлический слой, второй диэлектрический слой, сформированные в области расположения электродов пикселей и области расположения электродов данных;

и причем первый диэлектрический слой покрывает первый металлический слой;

и причем слой аморфного кремния, второй металлический слой и второй диэлектрический слой последовательно выполнены на первом диэлектрическом слое;

и причем прозрачный слой электродов пикселей соединен со вторым металлическим слоем посредством проходного отверстия, выполненного в области электродов пикселей второго диэлектрического слоя,

отличающийся тем, что подложка матрицы тонкопленочных транзисторов также включает слой фоторезиста, сформированный между первым диэлектрическим слоем и слоем аморфного кремния.

6. Жидкокристаллический дисплей по п. 5, отличающийся тем, что слой фоторезиста является красным слоем фоторезиста, зеленым слоем фоторезиста или синим слоем фоторезиста.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| CN 103178119 A, 26.06.2013 | |||

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| US 6869833 B1, 22.03.2005 | |||

| ПОДЛОЖКА АКТИВНОЙ МАТРИЦЫ И ЖИДКОКРИСТАЛЛИЧЕСКОЕ ДИСПЛЕЙНОЕ УСТРОЙСТВО | 2008 |

|

RU2439639C1 |

Авторы

Даты

2018-09-12—Публикация

2014-10-10—Подача