Область техники

Изобретение относится к области твердотельной электроники, в частности к способам формирования изоляции активной части полевых транзисторов с трехмерной структурой затвора (FinFET).

Уровень техники

При проектировании современных СБИС на основе FinFET предъявляются требования по минимизации энергопотребления. Статическая составляющая энергопотребления, в первую очередь, определяется значением тока утечки смыкания областей пространственного заряда (ОПЗ) стока и истока FinFET, протекающего в подзатворной области. Существует два подхода компенсации или полного подавления данного типа тока утечки: (1) формирование высоколегированной области на пути распространения ОПЗ стока и истока, что приводит к уменьшению размера ОПЗ и предотвращает их смыкание и (2) формирование изоляции между активной областью транзистора и подложкой.

Из предшествующего уровня техники известен способ изоляции, заключающийся в формировании области высокой концентрации примесных атомов, локализованной в плоскости основания тела транзистора FinFET (US 20110169101 A1 «Fin Field Effect Transistor (FINFET)», Taiwan Semiconductor Manufacturing Co Ltd (TSMC), заявлен 16 сентября 2008 года и опубликован 10 сентября 2009 года). Недостатком данного метода являются высокие производственные затраты, обусловленные неизбежной интеграцией целого ряда сопутствующих технологических операций в маршрут изготовления КМОП СБИС.

Также известен способ изоляции активной области транзистора посредством использования КНИ пластин (US 6413802 B1 «Finfet transistor structures having a double gate channel extending vertically from a substrate and methods of manufacture», University of California, заявлен 23 октября 2000 года и опубликован 2 июля 2002 года). Изолирующей областью в данном методе является сплошной слой захороненного диэлектрика, формируемого на этапе изготовления КНИ пластин. К недостаткам данного метода относятся высокая стоимость КНИ пластин, а также низкая эффективность отвода тепла от активной области транзистора.

Кроме того, известен способ локального окисления Si основания тела FinFET сквозь прилегающие участки щелевой изоляции (US 9349658 B1 «Methods of forming fin isolation regions on finFET semiconductor devices using an oxidation-blocking layer of material)), GlobalFoundries Inc International Business Machines Corp, заявлен 29 января 2015 года и опубликован 25 мая 2016 года). В данном способе формирование локальной изолирующей области происходит за счет перекрытия встречно направленных фронтов окисления противоположных граней основания тела транзистора. Недостатками метода являются высокий температурный режим процесса окисления, что приводит к появлению статических неконтролируемых механических напряжений в конструкции транзистора, а также «клювообразного)) вида границы раздела активной части тела транзистора с изолирующей областью, приводящего к увеличению тока утечки и повышению тепловыделения.

Наиболее близким по техническому решению, принятому за прототип, является способ формирования диэлектрической области изоляции активной части FinFET с использованием жертвенного слоя (US 9041062 B2 «Silicon-on-nothing FinFETs», International Business Machines Corp, заявлен 19 сентября 2013 года и опубликован 26 мая 2015 года). Жертвенный слой в данном методе входит в состав структуры тела транзистора и состоит из материала, имеющего высокую селективность травления по отношению к материалу активной части транзистора и подложки, что позволяет прецизионно удалить жертвенный слой и сформировать на его месте изоляционную область. К недостаткам метода относится необходимость предварительного формирования гетероструктуры на исходной подложке, что ввиду различий постоянных решетки материалов гетероструктуры будет приводить к появлению в активной части тела транзистора механических напряжений или дефектов, например в виде прорастающих дислокаций, и, как следствие, деградации характеристик транзистора. Кроме того, недостатком метода является интеграция в маршрут изготовления транзисторной структуры группы процессов по созданию и удалению фиктивного затвора, обеспечивающего механическую поддержку активной части тела транзистора при удалении жертвенного слоя.

Раскрытие изобретения

Задачей предполагаемого изобретения является формирование изоляции активной части полевых транзисторов с трехмерной структурой затвора (FinFET) с целью подавления тока утечки смыкания ОПЗ стока и истока. В качестве решения данной задачи предложен способ формирования локальной захороненной диэлектрической области изоляции активной части транзисторов с трехмерной структурой затвора (FinFET), включающий в себя изготовление тела транзистора на поверхности полупроводниковой подложки, формирование полости между активной частью тела транзистора и подложкой, а также заполнение сформированной полости диэлектрическим материалом, отличающийся от прототипа тем, что тело транзистора изготавливается на подложке, не имеющей скрытых слоев, расположение полости между активной частью тела транзистора и подложкой пространственно локализовано на ограниченном участке в продольном направлении основания тела транзистора, предлагается иная совокупность и последовательность выполнения операций: формирование слоя жесткой маски на поверхности подложки; группа процессов формирования активной части тела транзистора; конформное осаждение диэлектрического слоя по всей поверхности подложки; анизотропное травление диэлектрического слоя преимущественно в направлении плоскости подложки (создание спейсеров); формирование основания тела транзистора путем травления материала подложки по жесткой маске; вскрытие окон на боковой поверхности основания тела транзистора в процессе литографии; сквозное травление материала основания тела транзистора сквозь вскрытые окна; заполнение образованной полости диэлектрическим материалом.

Жесткая маска несет функцию защиты поверхности активной части тела транзистора, но одновременно данный слой может служить и стоппером в процессе химико-механической планаризации на дальнейших стадиях формирования транзисторной структуры. Как правило, в технологии микроэлектроники в качестве такого слоя используется Si3N4, имеющий в качестве подслоя SiO2. Однако допускается использование и других диэлектрических материалов.

Группа процессов формирования активной части тела транзистора включает в себя операцию фотолитографии, выполненную в соответствии с LELE, SADP или любой другой методикой создания топологического рисунка, а также операцию сухого травления материала подложки по жесткой маске на глубину H+W, где Н - значение высоты активной части тела транзистора, заложенное при физико-конструктивном проектировании транзистора, a W - ширина активной части тела транзистора. В качестве материала диэлектрического слоя предпочтительно использовать Si3N4.

Вместо двухстадийной процедуры формирования тела транзистора (формирование активной части и основания разделены процессом создания спейсеров) может быть использована одностадийная схема, представляющая собой следующую последовательность операций: формирование тела транзистора, формирование диэлектрического разделительного слоя на основе, например, SiO2 до уровня активной части тела транзистора, создание спейсеров, удаление диэлектрического разделительного слоя, вскрытие окон на боковой поверхности основания тела транзистора в процессе литографии, сквозное травление материала основания тела транзистора сквозь вскрытые окна, заполнение образованной полости диэлектрическим материалом.

Указанная совокупность отличительных признаков позволяет достичь технического результата, заключающегося в возможности использования гомогенной подложки, не требуя формирование скрытых слоев в ее объеме, упрощении процедуры формирования изоляции активной части транзисторов от подложки, отсутствии необходимости формирования фиктивного затвора и прочих дополнительных поддерживающих элементов.

Осуществление изобретения

Осуществление предлагаемого способа поясняется чертежами.

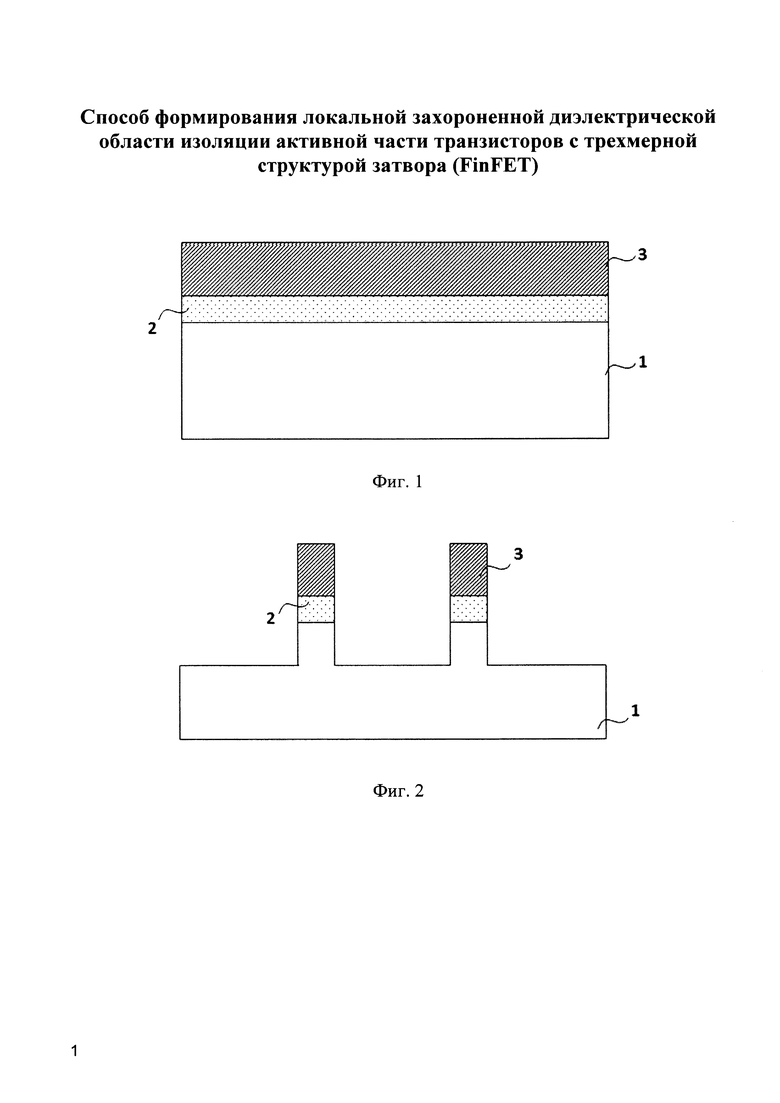

На Фиг. 1 представлена полупроводниковая подложка 1, а также сформированные на ее поверхности слой жесткой маски на основе 3 и подслой диоксида кремния 2.

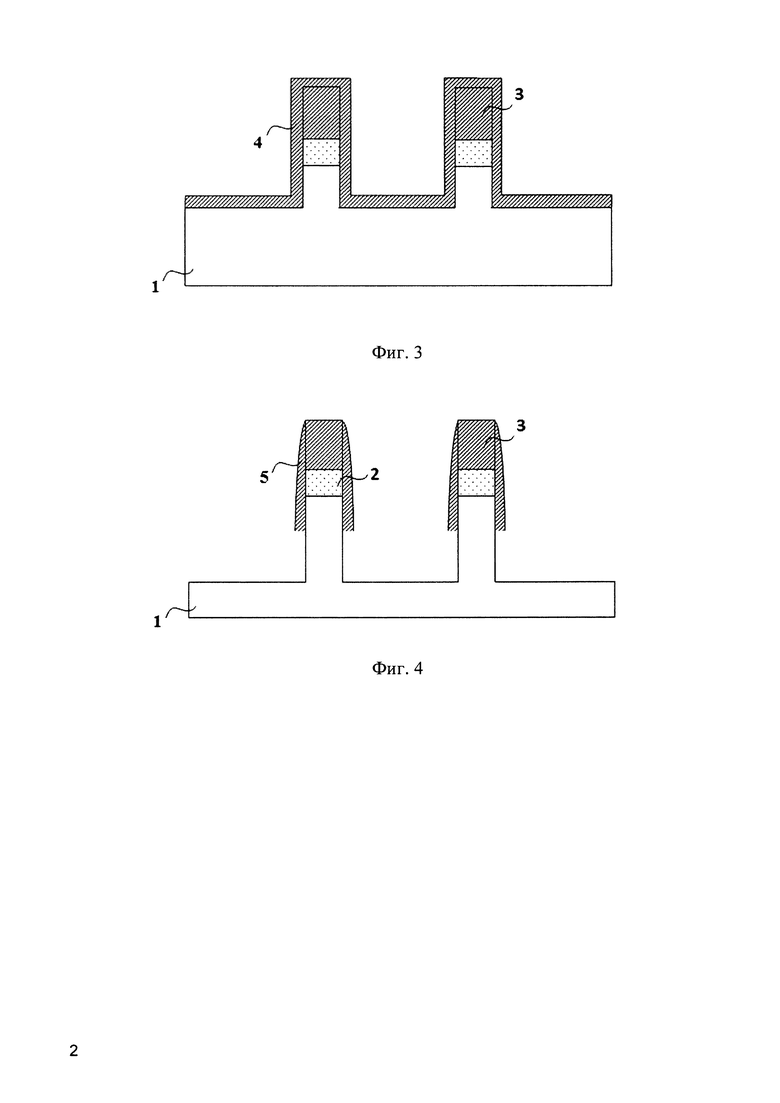

На Фиг. 2 представлен вид сформированной активной части тела транзистора в процессе сухого травления по жесткой маске.

На Фиг. 3 представлен результат конформного осаждения диэлектрического материала 4 в области сформированной активной части тела транзистора.

На Фиг. 4 представлена структура тела транзистора после создания спейсеров 5 и формирования основания тела транзистора путем травления материала подложки по жесткой маске 3.

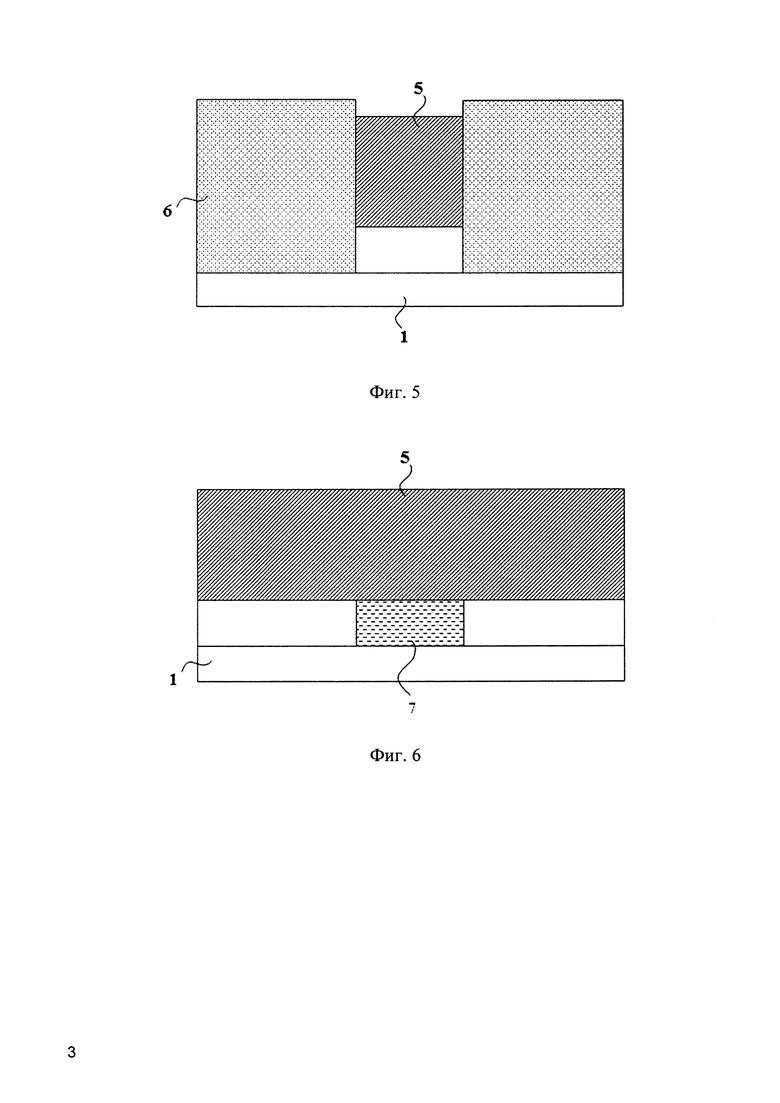

На Фиг. 5 представлен вид с боку тела транзистора после осаждения резиста 6 и вскрытие окон на боковой поверхности основания тела транзистора в процессе литографии.

На Фиг. 6 представлен вид с боку тела транзистора после сквозного травления материала основания тела транзистора сквозь вскрытые окна на боковой поверхности основания и заполнения образованной полости диэлектрическим материалом 7.

В качестве примера формирования локальной захороненной диэлектрической области изоляции активной части транзисторов с трехмерной структурой затвора (FinFET) можно предложить следующую технологию. Методом химического осаждения из газовой фазы при температуре 300°C на Si подложке осаждается тонкий слой SiO2 толщиной 15 нм, затем, при температуре осаждения 250°C осаждается слой Si3N4 толщиной 100 нм. С помощью проекционной фотолитографии и операции сухого травления через жесткую маску, в материале подложки формируется периодическая структура канавок на расстоянии 90 нм друг от друга, глубиной 160-170 нм и шириной 90 нм. По всей поверхности полученных структур методом химического осаждения из газовой фазы усиленного плазмой при температуре процесса 250°C конформно осаждается пленка Si3N4 толщиной 20 нм. Далее формируются спейсеры за счет анизотропного травления пленки Si3N4 преимущественно в направлении плоскости подложки. В процессе сухого травления материала подложки через жесткую маску на глубину 50 нм формируется основание тела транзистора. Далее в процессе фотолитографии проводится вскрытие окон в резисте на боковой поверхности основания тела транзистора. Методом жидкостного химического травления сквозь вскрытые окна в основании тела транзистора формируется полость, которая заполняется диэлектрическим материалом методом SoG.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВОГО НАНОТРАНЗИСТОРА С КОНТАКТАМИ ШОТТКИ С УКОРОЧЕННЫМ УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2012 |

|

RU2504861C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ПЛАНАРНОГО ДВУХЗАТВОРНОГО МОП-ТРАНЗИСТОРА НА КНИ ПОДЛОЖКЕ | 2003 |

|

RU2312422C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS-ТРАНЗИСТОРНЫХ КРИСТАЛЛОВ С МНОГОСЛОЙНОЙ ДРЕЙФОВОЙ ОБЛАСТЬЮ СТОКА | 2024 |

|

RU2819581C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРО- И НАНОПРИБОРОВ НА ЛОКАЛЬНЫХ ПОДЛОЖКАХ | 2004 |

|

RU2267832C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА С УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2003 |

|

RU2237947C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ T-ОБРАЗНОГО ГАЛЬВАНИЧЕСКОГО ЗАТВОРА В ВЫСОКОЧАСТОТНОМ ПОЛЕВОМ ТРАНЗИСТОРЕ | 2020 |

|

RU2746845C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ НАНОРАЗМЕРНЫХ ПРОВОЛОЧНЫХ КРЕМНИЕВЫХ СТРУКТУР | 2010 |

|

RU2435730C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНОГО НИТРИД-ГАЛЛИЕВОГО ПОЛЕВОГО ТРАНЗИСТОРА | 2017 |

|

RU2668635C1 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| КОНСТРУКЦИЯ ДИСКРЕТНОГО СВЧ LDMOS-ТРАНЗИСТОРНОГО КРИСТАЛЛА С УСОВЕРШЕНСТВОВАННОЙ ЭКРАНИРУЮЩЕЙ ШИНОЙ ИСТОКА | 2024 |

|

RU2819579C1 |

Изобретение относится к области твердотельной электроники, в частности способам формирования изоляции активной части полевых транзисторов с трехмерной структурой затвора (FinFET). Сущностью изобретения является способ формирования захороненной диэлектрической области изоляции активной части FinFET от подложки, характеризующейся тем, что область изоляции локализована в ограниченном объеме тела транзистора, позволяя конструкции обладать высокой механической прочностью. Изобретение обеспечивает подавление тока утечки смыкания областей пространственного заряда стока и истока. 6 ил.

Способ формирования локальной захороненной диэлектрической области изоляции активной части транзисторов с трехмерной структурой затвора (FinFET), включающий в себя изготовление тела транзистора на поверхности полупроводниковой подложки, формирование полости между активной частью тела транзистора и подложкой, а также заполнение сформированной полости диэлектрическим материалом, отличающийся тем, что тело транзистора изготавливается на подложке, не имеющей скрытых слоев, расположение полости между активной частью тела транзистора и подложкой пространственно локализовано на ограниченном участке в продольном направлении основания тела транзистора, а для изготовления тела транзистора на поверхности полупроводниковой подложки и формирования полости между активной частью тела транзистора и подложкой проводят следующие операции: формирование слоя жесткой маски на поверхности подложки, группа процессов формирования активной части тела транзистора, конформное осаждение диэлектрического слоя по всей поверхности подложки, анизотропное травление диэлектрического слоя преимущественно в направлении плоскости подложки, обеспечивающее создание спейсеров, формирование основания тела транзистора путем травления материала подложки по жесткой маске, вскрытие окон на боковой поверхности основания тела транзистора в процессе литографии, сквозное травление материала основания тела транзистора сквозь вскрытые окна, после чего проводят заполнение образованной полости диэлектрическим материалом.

| US 20150028426 A1, 29.01.2015 | |||

| US 6949768 B1, 27.09.2005 | |||

| US 20160087103 A1, 24.03.2016 | |||

| US 6413802 B1, 02.07.2002 | |||

| US 9041062 B2, 26.05.2015 | |||

| US 9349658 B1, 24.05.2016 | |||

| US 20160079428 A1, 17.03.2016 | |||

| US 20160343572 A1, 24.11.2016. |

Авторы

Даты

2018-10-19—Публикация

2017-09-05—Подача