Общая область техники

Настоящее изобретение относится к электрическим приводам управления полетом и, в частности, к способу проверки неразрывности передачи данных между главным входным блоком и главным выходным блоком.

Уровень техники

Электрические приводы управления полетом представляют собой усовершенствование традиционных механических приводов управления полетом.

Появление быстродействующих цифровых вычислительных устройств позволило осуществлять дополнительный этап компьютерной обработки команд управления полетом, на котором пилот только задает общее движение летательного аппарата, после чего вычислительное устройство осуществляет управление необходимыми движениями рулей в зависимости от высоты полета, от скорости и т.д. В настоящее время существует множество «полностью компьютеризированных» самолетов, рулями которых управляет вычислительное устройство.

До настоящего времени очень мало вертолетов управляются электрическими приводами управления полетом, и ни один из них не имеет электрических приводов управления полетом на полностью цифровой платформе.

Действительно, движение вертолета является более сложным, чем движение самолета. Вертолет перемещается при помощи двух винтов, которые одновременно обеспечивают подъемную силу и перемещение. В то время как на самолете эти две функции разделены (что обеспечивает тягу по одной оси), вертолет не может двигаться только в одном направлении и всегда сталкивается с шестью степенями свободы. Любое изменение ориентации лопастей винтов влияет одновременно на тягу, на подъемную силу, на лобовое сопротивление, на мощность и на эффект вращения летательного аппарата вокруг своей оси, и оба винта должны компенсировать свое соответствующее влияние.

Для разработки такой платформы, которая может быть основана на трехканальной или четырехканальной (для избыточности) архитектуре, необходимо предусмотреть коммуникационные связи между всеми вычислительными блоками системы с более высокими характеристиками по сравнению со всеми существующими в настоящее время.

Поскольку применение является очень критическим (целостность до 10-10 и доступность до 10-10), эти коммуникационные связи непременно должны быть надежными, защищенными и выдерживающими сложные условия окружающей среды (в частности, молнию).

Кроме того, в системе авионики (тем более вертолетной) вес имеет первостепенное значение и, в частности, вес проводки. Поэтому очень важно максимально сократить число линий связи, внешних относительно каждого вычислительного устройства.

Наконец, поскольку все больше возрастают объем информации и общая потребность в эффективности системы управления полетом, необходимо, чтобы эти коммуникационные связи обеспечивали высокую пропускную способность и как можно меньшую латентность, чего не могут обеспечить предлагаемые в настоящее время системы.

Наиболее распространенной в настоящее время цифровой шиной является ARINC-429. Однако она имеет ряд недостатков: ее пропускная способность является явно недостаточной (100 кбит/с, тогда как необходимо 15 Мбит)с), и ее стойкость к окружающей среде (в частности, к молнии) является низкой. Шина 1553 имеет те же проблемы.

Для преодоления этих трудностей была предложена архитектура AFDX (Avionics Full Duplex switched Ethernet, полиодуплексная коммутируемая сеть Ethernet для авионики), которая представляет собой избыточную сеть Ethernet повышенной надежности. Ее пропускная способность, стойкость к окружающей среде и надежность являются приемлемыми, но она является исключительно дорогой, и ее характеристики латентности хуже, чем у ARINC-429.

Желательно располагать надежной и защищенной связью для передачи данных, стойкой к сложным условиям окружающей среды (в частности, к молнии и восприимчивости управления), не требующей избыточности проводки, имеющей стоимость ниже связи ARINC-429, с пропускной способностью не менее 15 Мбит/с и с латентностью менее 50 мкс, и являющейся совместимой с существующим тестовым и доводочным оборудованием.

Раскрытие изобретения

Первым объектом настоящего изобретения является способ проверки неразрывности передачи данных между главным входным блоком и главным выходным блоком, при этом способ отличается тем, что содержит следующие этапы:

(а) При помощи модуля обработки данных главного входного блока генерируют первый фрейм, содержащий предназначенный для передачи пакет данных и избыточный циклический код указанного пакета, и передают в интерфейсный модуль главного входного блока;

(b) При помощи указанного интерфейсного модуля главного входного блока первый фрейм включают во второй фрейм, дополнительно содержащий избыточный циклический код первого фрейма;

(c) Передают второй фрейм в интерфейсные модули главного выходного блока и по меньшей мере одного вспомогательного входного блока;

(d) При помощи интерфейсных модулей главного выходного блока и по меньшей мере одного вспомогательного входного блока из второго фрейма извлекают первый фрейм; и передают в модули обработки данных главного выходного блока и указанного по меньшей мере одного вспомогательного входного блока;

(e) При помощи модуля обработки данных главного входного блока извлекают пакет из первого фрейма; и при помощи модуля обработки данных указанного по меньшей мере одного вспомогательного входного блока извлекают избыточный циклический код пакета;

(f) При помощи указанного интерфейсного модуля главного входного блока включают избыточный циклический код пакета в третий фрейм;

(g) Передают третий фрейм в интерфейсный модуль указанного по меньшей мере одного вспомогательного входного блока;

(h) При помощи интерфейсного модуля указанного по меньшей мере одного вспомогательного входного блока из третьего фрейма извлекают избыточный циклический код пакета; и передают в модуль обработки данных указанного по меньшей мере одного вспомогательного входного блока;

(i) При помощи модуля обработки данных указанного по меньшей мере одного вспомогательного входного блока сравнивают каждый из избыточных циклических кодов, извлеченных из первого фрейма и третьего фрейма; и только если сравнение дает положительный результат, подтверждают неразрывность передачи данных в главный выходной блок.

Согласно другим предпочтительным и не ограничительным отличительным признакам:

- этап (с) содержит также передачу второго фрейма в интерфейсный модуль по меньшей мере одного вспомогательного выходного блока; этап (d) содержит извлечение первого фрейма из второго фрейма при помощи интерфейсного модуля указанного по меньшей мере одного вспомогательного выходного блока; и этап (е) содержит извлечение пакета из первого фрейма при помощи модуля обработки данных указанного по меньшей мере одного вспомогательного выходного блока;

- способ содержит дополнительный этап (j), на котором передают пакет, извлеченный модулем обработки данных указанного по меньшей мере одного вспомогательного выходного блока, в модуль обработки данных главного выходного блока; при помощи модуля обработки данных главного выходного блока сравнивают каждый из полученных пакетов и, только если результат сравнения является положительным, подтверждают неразрывность передачи данных в главный выходной блок;

- предназначенный для передачи пакет является первым пакетом, генерируемым модулем обработки данных главного входного блока на основании данных управления, при этом этап (е) содержит извлечение пакета из первого фрейма при помощи модуля обработки данных указанного по меньшей мере одного вспомогательного входного блока; и способ дополнительно содержит генерирование второго пакета на основании тех же данных управления, что и для первого пакета, при помощи модуля обработки данных указанного по меньшей мере одного вспомогательного входного блока; при помощи модуля обработки данных указанного по меньшей мере одного вспомогательного входного блока сравнивают первый пакет и второй пакет; и, только если результат сравнения является положительным, подтверждают неразрывность передачи данных в главный выходной блок;

- способ включает в себя осуществление следующих этапов:

(α) При помощи модуля обработки данных указанного по меньшей мере одного вспомогательного входного блока генерируют четвертый фрейм, содержащий второй пакет и избыточный циклический код указанного второго пакета, и передают в интерфейсный модуль указанного по меньшей мере одного вспомогательного входного блока;

(β) При помощи указанного интерфейсного модуля указанного по меньшей мере одного вспомогательного входного блока четвертый фрейм включают в пятый фрейм, дополнительно содержащий избыточный циклический код четвертого фрейма;

(γ) Передают пятый фрейм в интерфейсный модуль главного входного блока;

(δ) При помощи интерфейсного модуля главного входного блока извлекают четвертый фрейм из пятого фрейма и передают в модуль обработки данных главного входного блока;

(ε) При помощи модуля обработки данных главного входного блока извлекают второй пакет из четвертого фрейма;

(ζ) При помощи модуля обработки данных главного входного блока сравнивают первый пакет и второй пакет; и, только если результат сравнения является положительным, подтверждают неразрывность передачи данных в главный выходной блок.

- второй и третий фреймы соответствуют стандарту High-Level Data Link Control (Управление линией передачи данных высокого уровня);

- входные блоки и выходные блоки физически соединены через единую проводную связь;

- указанная проводная связь соответствует стандарту RS-485.

Вторым объектом изобретения является вычислительное устройство управления полетом, содержащее главный входной блок, главный выходной блок и по меньшей мере один вспомогательный входной блок, при этом блоки выполнены с возможностью осуществления способа, являющегося первым объектом изобретения.

Третьим объектом изобретения является система управления полетом летательного аппарата, содержащая по меньшей мере три вычислительных устройства, являющиеся вторым объектом изобретения, при этом входные блоки вычислительных устройств принимают данные управления полетом по меньшей мере от одного органа управления летательным аппаратом, и выходные блоки вычислительных устройств выдают команды управления по меньшей мере в одно исполнительное устройство летательного аппарата.

Согласно другим предпочтительным и не ограничительным отличительным признакам:

- каждый входной блок вычислительного устройства соединен с выходными блоками других вычислительных устройств.

Четвертым и пятым объектами изобретения являются компьютерный программный продукт, содержащий командные коды с целью осуществления способа, являющегося первым объектом изобретения, для проверки неразрывности передачи данных между главным входным блоком и главным выходным блоком; и средства записи, считываемые компьютерным устройством, на которых компьютерный программный продукт содержит командные коды с целью осуществления способа, являющегося первым объектом изобретения, для проверки неразрывности передачи данных между главным входным блоком и главным выходным блоком.

Краткое описание чертежей

Другие отличительные признаки и преимущества настоящего изобретения будут более очевидны из нижеследующего описания предпочтительного варианта выполнения. Это описание представлено со ссылками на прилагаемые чертежи, на которых:

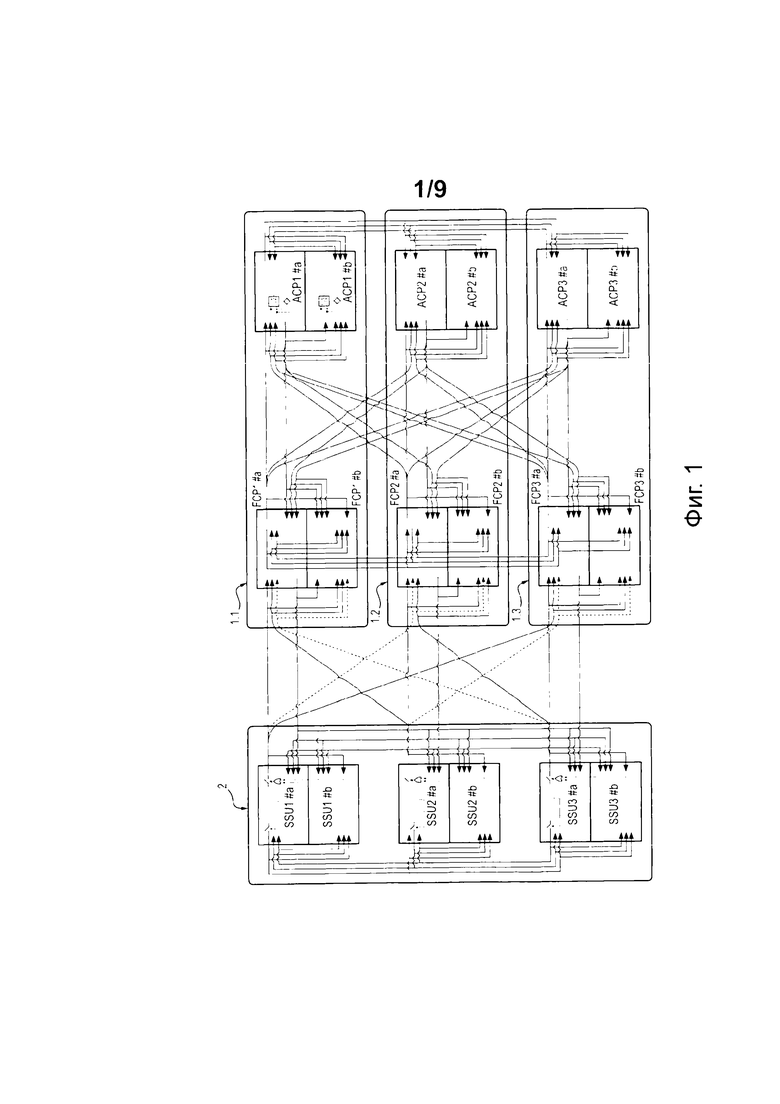

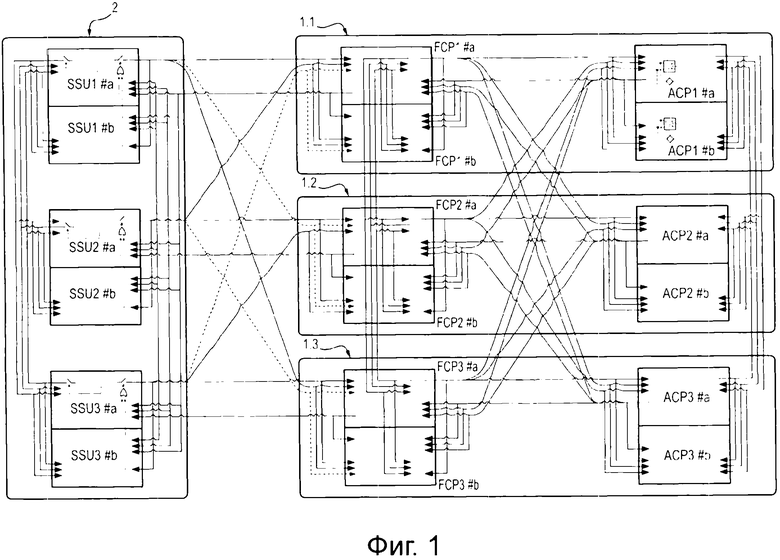

Фиг. 1 - архитектура системы управления полетом, в которой осуществляют заявленный способ.

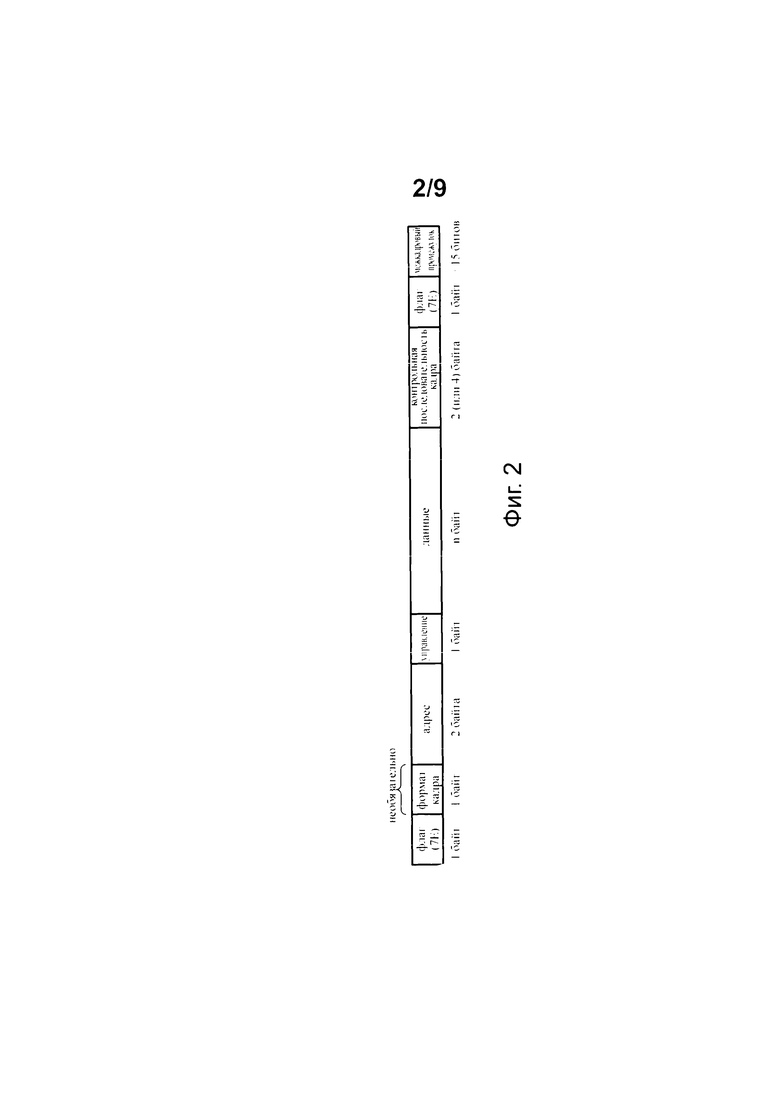

Фиг. 2 - схема примера фрейма HDLC, используемого в рамках заявленного способа.

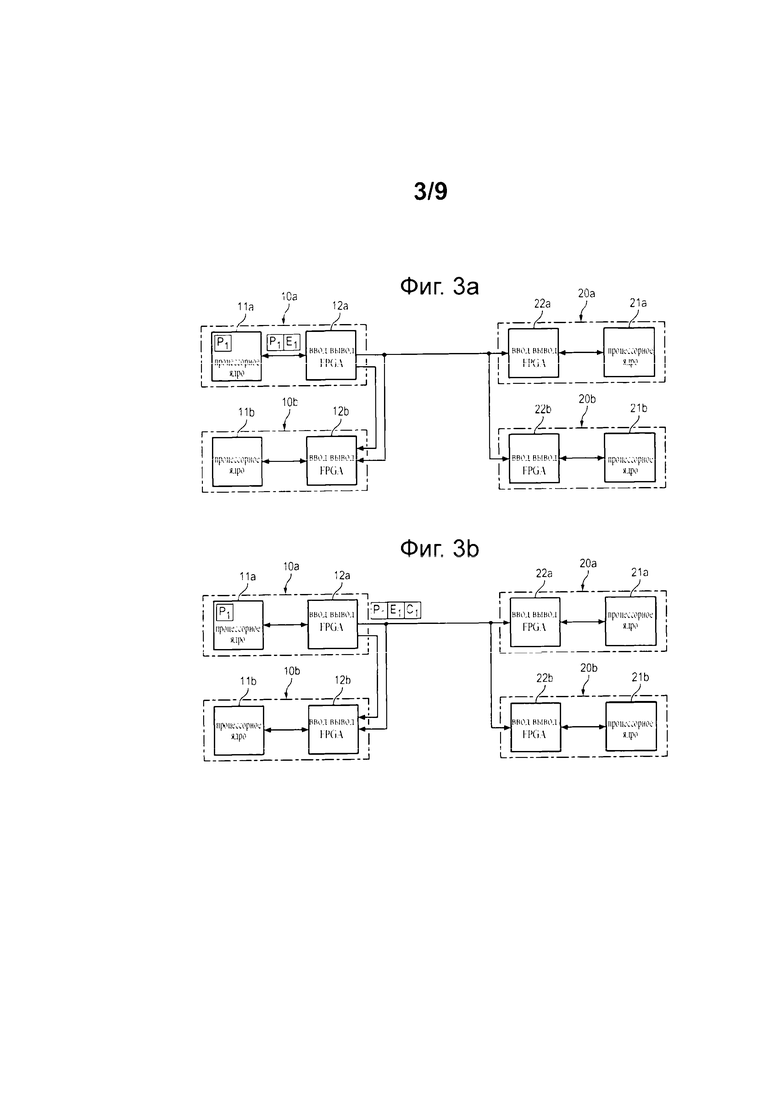

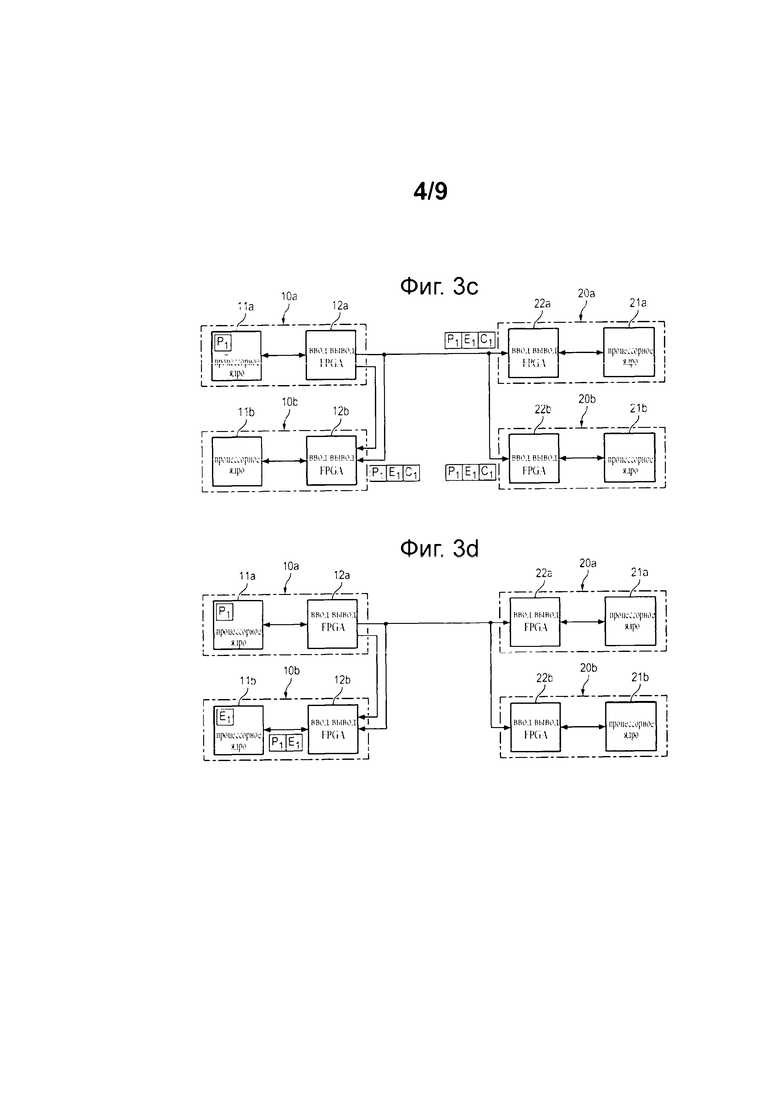

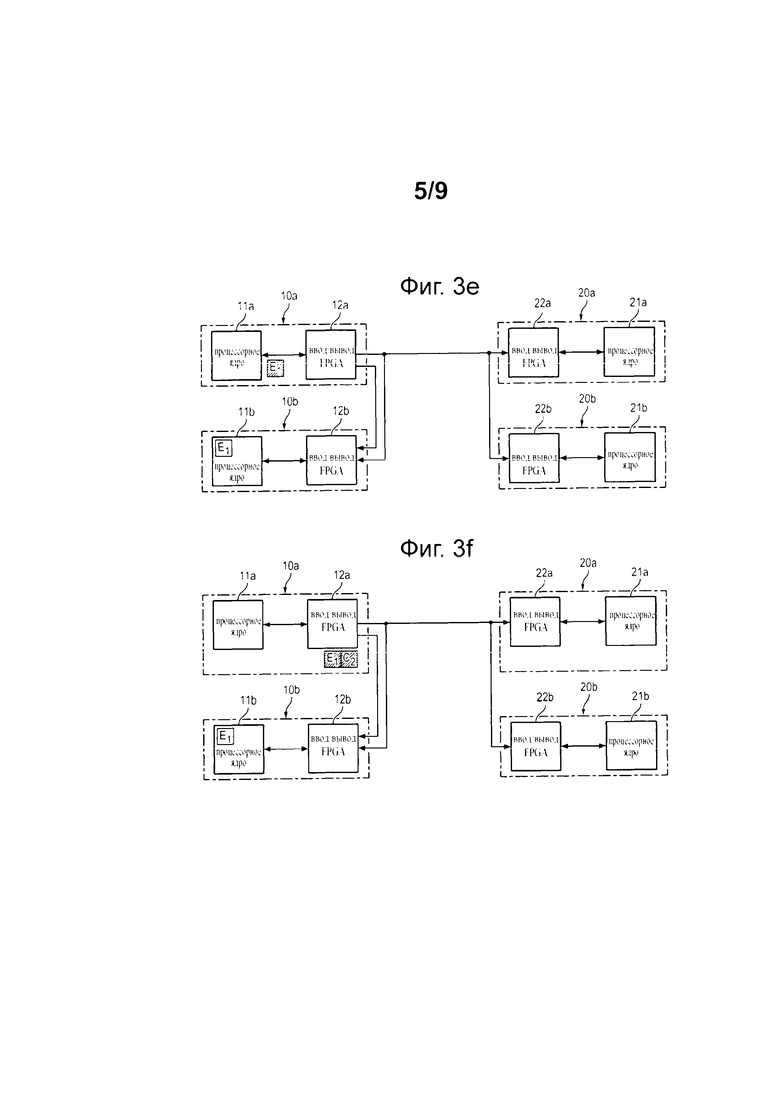

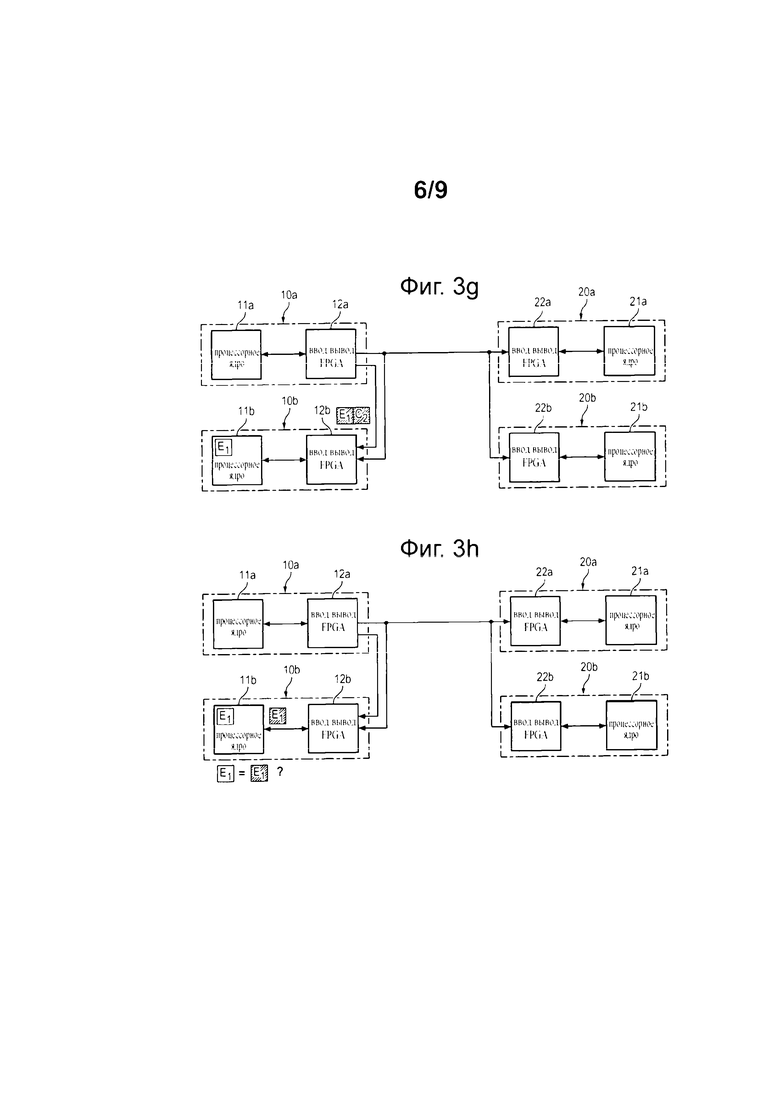

Фиг. 3а-h - этапы примера проверки неразрывности передачи данных в предпочтительном варианте осуществления заявленного способа.

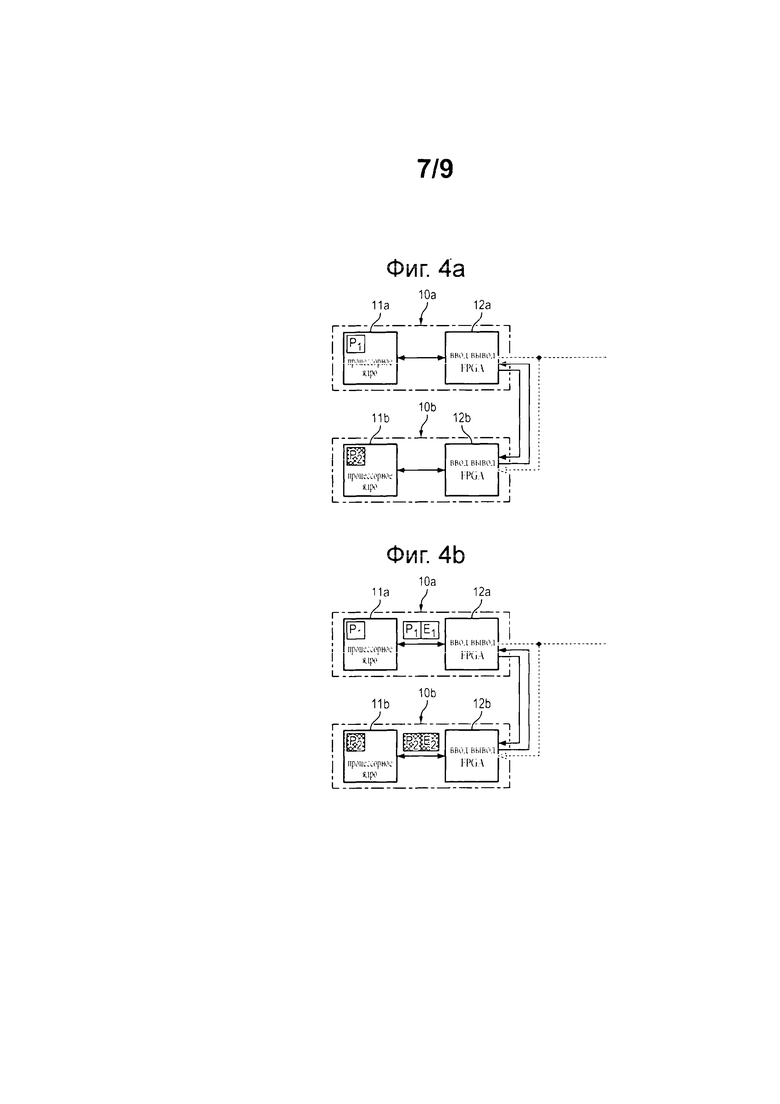

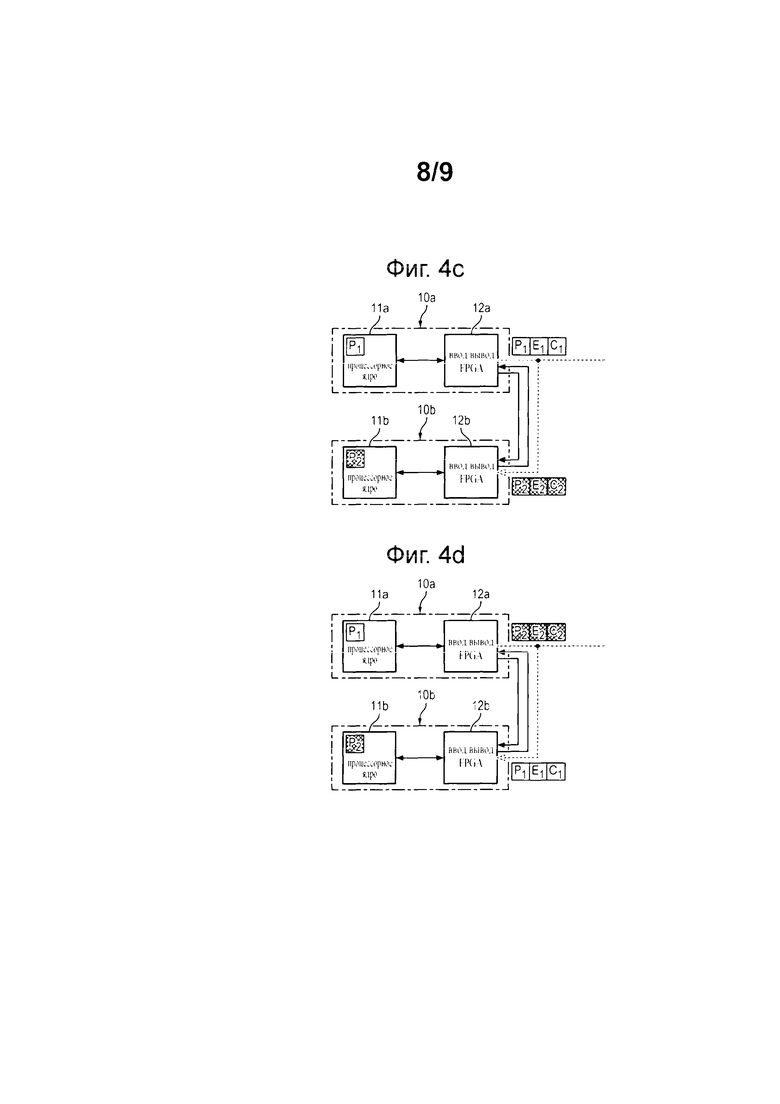

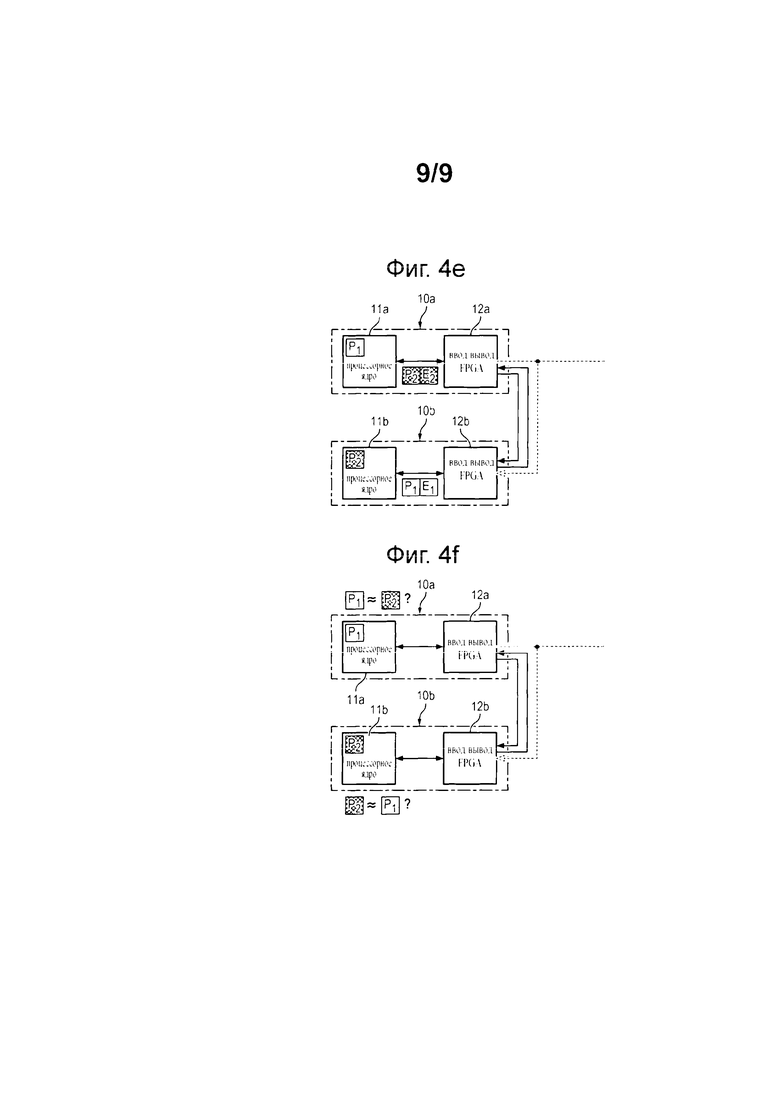

Фиг. 4а-f - этапы примера проверки целостности генерированных данных в предпочтительном варианте осуществления заявленного способа.

Подробное описание

Архитектура

Упомянутый стандарт ARINC-429 представляет собой норму, которая описывает одновременно архитектуру, электрический интерфейс и протокол для передачи цифровых данных. Он основан на «симплексной» связи, то есть на односторонней связи 1-в направлении-N, которая будет утроена или учетверена (таким образом, чтобы получить «трехканальные» или «четырехканальные» архитектуры). Таким образом, даже при отказе N-1 линий связи система будет продолжать работать.

Задачей настоящего способа является простое и достаточно защищенное использование физических интерфейсов и протоколов, отличных от стандарта ARINC-429, с одновременным сохранением его топологии, чтобы сохранить преимущества ARINC-429 и одновременно улучшить его характеристики, в частности, с точки зрения пропускной способности, латентности и стойкости к окружающей среде.

Как показано на фиг. 1, настоящий способ осуществляют в системе типа FCS (“Flight Control System”, система управления полетом) летательного аппарата (в частности, вертолета), содержащей одно или несколько вычислительных устройств 1 (избыточных) FCC (“Flight Control Calculator”, вычислительное устройство управления полетом). Каждое вычислительное устройство можно рассматривать как «линию» передачи команд управления полетом от пилота на аэродинамические рули, то есть различные элементы летательного аппарата, позволяющие изменять его траекторию и приводимые в действие исполнительными устройствами. Пилот действует на органы управления (например, на ручку управления), генерируя данные управления полетом, передаваемые модулем 2 (SSU, “Side Stick Unit”, то есть блок мини-рукоятки, который обозначает ручку, позволяющую приводить в действие рули летательного аппарата) в линии 1.

На фиг. 1 показана, в частности, триплексная архитектура с первой линией 1.1, второй линией 1.2 и третьей линией 1.3 Линии являются идентичными.

Под «линией» следует понимать автономный узел из нескольких взаимосвязанных блоков 10, 20, из которых по меньшей мере один блок 10 является «входным» (FCP, “Flight Control Processor”, процессор управления полетом) и по меньшей мере один блок 20 является «выходным» (ACP, “Actuator Control Processor”, процессор управления исполнительными устройствами).

Каждый входной блок 10 получает на входе данные управления полетом (выражающие общее движение летательного аппарата, задаваемое пилотом) и генерирует данные контроля полета (выражающие действия, производимые на уровне органов летательного аппарата), которые проходят в летательном аппарате. Каждый выходной блок 20 (удаленный, находящийся на уровне исполнительных устройств) принимает данные контроля полета и генерирует команды контроля исполнительных устройств таким образом, чтобы активно перемещать рули (например, увеличивая угол атаки лопастей рулевого винта, если пилот хочет изменить ориентацию вертолета).

Внутри одной линии блоки 10, 20 продублированы в соответствии с архитектурой COM/MON (“Command, Monitoring”, команда/контроль). В частности, предусмотрены главный входной блок 10а и по меньшей мере один вспомогательный входной блок 10b. Аналогично предусмотрены (как показано на фиг. 1 и на следующих фигурах) главный выходной блок 20а и по меньшей мере один вспомогательный выходной блок 20b. Главные блоки 10а, 20а являются задающими блоками, тогда как вспомогательные блоки 10b, 20b получают копии данных, принимаемых главными блоками 10а, 20а, и служат только для мониторинга и проверки данных, выдаваемых главными блоками 10а, 20а.

Каждый блок 10а, 10b, 20a, 20b содержит модуль 11a, 11b, 21a, 21b обработки данных (как правило, процессор, который производит обработку данных) и интерфейсный модуль 12a, 12b, 22a, 22b (как правило, FPGA, “Field-Programmable Gate Array” (программируемая вентильная матрица), который управляет связью с другими блоками). Оба модуля могут быть соединены через локальную коммуникационную связь.

В дальнейшем тексте настоящего описания будет рассмотрен пример линии 1, содержащей четыре блока 10a, 10b, 20a, 20b: главный входной блок 10а, вспомогательный входной блок 10b, главный выходной блок 20а и вспомогательный выходной блок 20b. Как будет показано ниже, линии 1 отличаются тем, что входные лобки 10 соединены с выходными блоками 20 только одной физической связью (одной проводкой), что позволяет существенно уменьшить вес и снизить стоимость. Несмотря на единственную проводку, настоящий способ позволяет гарантировать неразрывность передачи данных внутри линии 1. Иначе говоря, можно с вероятностью ошибки 10-10 гарантировать, что данные, переданные от главного входного блока 10а в главный выходной блок 20а будут достоверными.

Следует отметить, как показано на фиг. 1, что можно предусмотреть поперечные проводки от одной линии 1.1, 1.2, 1.3 к другой (чтобы обеспечивать беспрерывную работу каждой линии 1, даже если проводка, принадлежащая к одной линии, физически повреждена, например, от выстрелов, если летательный самолет является военным). Даже с этими поперечными проводками число предусматриваемых физических связей остается меньше, чем в известных решениях.

Предпочтительно физические интерфейсы (hardware) внутри линии 1 соответствуют стандарту RS-485 (согласно которому пропускная способность может достигать Мбит/с) и предпочтительно оснащены гальваническими развязками, которые полностью обеспечивают ему стойкость к молнии и к электромагнитным явлениям (и, следовательно, отличную стойкость по отношению к окружающей среде). Хотя стандарт RS-485 не предназначен специально для электрических приводов управления полетом, настоящий способ позволяет гарантировать полную надежность.

Проверка неразрывности передачи данных

Настоящий способ позволяет убедиться, что пакет Р1, выработанный модулем 11а обработки данных главного входного блока 10а, передан без изменений в модуль 21а обработки данных главного выходного блока 20а. Описанный ниже отличительный признак способа предполагает, что пакет Р1 надлежащим образом генерирован модулем 11а обработки данных (на основании данных управления полетом). Однако, как будет пояснено ниже, в факультативном варианте осуществления способ включает в себя проверку целостности данных, генерированных модулем 11а обработки данных (и, следовательно, пакета Р1).

Протокол, применяемый для передачи данных (между входным 10 и выходным 20 блоками, то есть между интерфейсными модулями 12, 22, при этом необходимо отметить, что можно использовать любой формат для передачи между модулем обработки и интерфейсным модулем внутри одного блока), предпочтительно соответствует стандарту HDLC (“High-Level Data Link Control” (управление линией передачи данных высокого уровня), стандарт ISO/IEC 13239:2002). Используемый блок является фреймом (“Frame”) со структурой, показанной на фиг. 2. Каждый фрейм ограничен двумя идентичными флагами (“flag”) и содержит поле данных (“data”) на 20-32 байт. Адресное поле используют в качестве идентификатора сообщения на 2 байта, и оно эквивалентно «метке» ARINC-429. Контрольное поле на 1 байт не используют. Между двумя фреймами находятся по меньшей мере 15 бит значения «1». Фреймами, относящимися к настоящему способу, являются второй фрейм Т2, третий фрейм Т3 и, возможно, пятый фрейм Т5.

Способ начинается с показанного на фиг. 3а этапа (а) генерирования модулем 11а обработки данных главного входного блока 10а первого фрейма Т1 (в любом формате), содержащего пакет Р1 предназначенных для передачи данных и избыточный циклический код Е1 указанного пакета Р1. Таким образом, Т1=Р1+Е1. Избыточный циклический код Е1 (часто называемый контрольной суммой (“checksum”)) пакета Р1 получают при помощи Избыточного Циклического Кода (CRC), в частности, благодаря известной процедуре хеширования. Специалист в данной области может применить CRC-16-CCITT на 2 байта. Этот фрейм Т1 передают, в частности, через локальную коммуникационную связь в интерфейсный модуль 12а главного входного блока 10а.

На этапе (b), показанном на фиг. 3b, этот интерфейсный модуль 12а упаковывает первый фрейм Т1 во второй фрейм Т2 (который на этот раз предпочтительно соответствует описанному выше формату, показанному на фиг. 2), дополнительно содержащий избыточный циклический код С1 первого фрейма Т1. Иначе говоря, поле данных второго фрейма Т2 состоит из пакета Р1 и соответствующего CRC Е1. CRC С1 может быть такого же типа, что и CRC Е1, или, например, CRC-32-IEEE на 4 байта.

На этапе (с), показанном на фиг. 3с, второй фрейм Т2 передают (через проводку) по меньшей мере в интерфейсный модуль 22а главного выходного блока 20а и в интерфейсный модуль 12b вспомогательного входного блока 10b. В случае наличия по меньшей мере одного вспомогательного выходного блока 20b (как в данном примере) второй фрейм Т2 тоже передают в его интерфейсный модуль 22b.

Каждый интерфейсный модуль 22а, 22b, 12b извлекает на этапе (d) первый фрейм Т1 из второго фрейма Т1 (отделяя идентификатор фрейма и CRC С1) и передает его в соответствующие модули 21а, 21b, 11b обработки данных.

При этом на этапе (е), показанном на фиг. 3d, модуль 11b обработки данных вспомогательного входного блока 10b извлекает избыточный циклический код Е1 пакета Р1, тогда как модуль 21а обработки данных главного выходного блока 20а (и, в случае необходимости, модуль 21b обработки данных вспомогательного выходного блока 20b) извлекает пакет Р1 из первого фрейма Т1. Следует отметить, что парадоксальным образом модуль 11b обработки данных вспомогательного входного блока 10b может проигнорировать пакет Р1 и обратить внимание только на избыточный циклический код Е1 пакета Р1 (в отличие от того, что происходит с выходной стороны), поскольку, как будет показано ниже, это позволит вспомогательному входному блоку 10b осуществить тест неразрывности передачи. Смысл состоит в том, что, поскольку проводка является единственной, если вспомогательный входной блок 10b правильно принял избыточный циклический код Е1 пакета Р1, то можно предположить, что это относится и к самому пакету Е1, так как CRC является перевернутой копией Р1, причем для всех адресатов. Действительно, если ошибка происходит в момент передачи (на уровне интерфейсного модуля 12а) или раньше (на уровне модуля 11а обработки данных), то все передачи Е1 будут ошибочными. Однако в описанных ниже вариантах осуществления применяют дополнительные тесты. На этой стадии, показанной на фиг. 3е, каждый из входных модулей 11а, 11b обработки данных имеет версию CRC Е1.

Таким образом, на этапе (f), показанном на фиг. 3f, интерфейсный модуль 12а главного входного блока 10а включает на этот раз избыточный циклический код Е1 пакета Р1 (который выдан модулем 11а обработки данных) в третий фрейм Т3. Иначе говоря, поле данных фрейма Т3 не содержит Р1 (и на практике содержит только Е1). Этот третий фрейм дополнительно содержит избыточный циклический код C1’ избыточного циклического кода Е1 пакета Р1 (аналогично коду CRC С1). Необходимо отметить, что коды CRC С1 и C1’ являются разными, так как хешированные данные не являются одинаковыми.

На этапе (g), показанном на фиг. 3g, третий фрейм Т3 передают (через проводку) в интерфейсный модуль 12b вспомогательного входного блока 10b (выходные блоки 20а, 20b не являются адресатами этого фрейма).

Аналогично тому, что было произведено на этапе (d), интерфейсный модуль 12b извлекает на этапе (h) код CRC Е1 из третьего фрейма Т3 (отделяя идентификатор фрейма и CRC C1’) и передает его в соответствующий модуль 11b обработки данных.

Последний располагает при этом двумя версиями CRC Е1 (кодом, извлеченным из первого фрейма Т1, и кодом, извлеченным из третьего фрейма Т3) и может их сравнить (бит за битом) на этапе (i), показанном на фиг. 3h. Неразрывность передачи данных в главный выходной блок 20а подтверждают, только если результат сравнения является положительным, иначе говоря, если оба кода Е1 являются идентичными, что свидетельствует о нормальных передачах второго и третьего фреймов Т2, Т3 (в противном случае по меньшей мере один из двух CRC был бы другим). На этой стадии модуль 21а обработки данных главного выходного блока 20а может быть уверен, что пакет Р1 был передан без ошибки.

Следует отметить, что в случае по меньшей мере одного вспомогательного выходного блока 20b способ может содержать дополнительный этап (j) передачи пакета Р1, извлеченного модулем 21b обработки данных вспомогательного выходного блока 20b, в модуль 21а обработки данных главного выходного блока 20а. Как и на этапе (i), модуль 11b обработки данных по меньшей мере одного вспомогательного входного блока 10b сравнивает каждый из принятых пакетов Р1, при этом неразрывность передачи данных в главный выходной блок 20а подтверждают, только если результат сравнения является положительным, иначе говоря, если оба пакета Р1 являются идентичными, что свидетельствует о нормальных «выходных» распаковках второго фрейма Т2 (в противном случае по меньшей мере один из двух Р1 был бы другим).

Проверка целостности генерированных данных

Описанные выше этапы позволяют убедиться, что пакет Р1 был передан надлежащим образом, но не позволяют убедиться, что этот пакет Р1 является корректным. Согласно предпочтительному варианту осуществления, способ содержит этапы проверки (простой или двойной) целостности данных, генерированных модулем 11а обработки данных главного входного блока 10а (на основании данных управления полетом).

Для этого предназначенный для передачи пакет Р1 назначают в качестве первого пакета, который будут сравнивать с мониторинговым пакетом Р2. Действительно, в этом случае способ содержит генерирование модулем 11b обработки данных вспомогательного входного блока 10b второго пакета Р2 на основании тех же данных управления полетом, что и для первого пакета Р1, как показано на фиг. 4а.

При простой проверке вышеупомянутый этап (е) содержит извлечение пакета Р1 из первого фрейма Т1 модулем 21а обработки данных указанного по меньшей мере одного вспомогательного входного блока 10b (можно напомнить, как было указано выше, что на этапе (е) извлекали CRC Е1 пакета Р1).

Модуль 11b обработки данных вспомогательного входного блока 10b может осуществить новое сравнение, на этот раз первого пакета Р1 и второго пакета Р2. При этом неразрывность передачи данных в главный выходной блок 20а подтверждают, только если результат сравнения является положительным, то есть Р1 и Р2 являются идентичными, что свидетельствует о правильной передаче пакета Р1.

В предпочтительном варианте осуществления способ содержит дополнительные этапы, показанные на фигурах, для осуществления двойной проверки пакета Р1. Описанные ниже этапы можно осуществлять перед вышеупомянутыми этапами (а)-(i) или одновременно с ними. Необходимо отметить, что пакет Р1 можно генерировать два раза, чтобы один раз проверить целостность генерирования данных и затем второй раз проверить неразрывность передачи данных. Предпочтительно оба теста совмещают, чтобы выиграть время.

На этапе (α) (который может быть осуществлен одновременно с похожим на него этапом (а)), показанном на фиг. 4b, модуль 11b обработки данных вспомогательного входного блока 10b генерирует четвертый фрейм Т4, содержащий второй пакет Р2 и избыточный циклический код Е2 указанного второго пакета Р2. Таким образом, Т4=Р2+Е2. Этот фрейм Т4 (который нормально должен быть идентичным с первым фреймом Т1) передают в интерфейсный модуль 12b вспомогательного входного блока 10b.

На этапе (β) (который может быть осуществлен одновременно с похожим на него этапом (b)), показанном на фиг. 4с, этот интерфейсный модуль 12b включает четвертый фрейм Т4 в пятый фрейм Т5 (который опять предпочтительно соответствует формату, описанному выше со ссылками на фиг. 2), дополнительно содержащий избыточный циклический код С2 четвертого фрейма Т4. Иначе говоря, поле данных пятого фрейма Т5 содержит пакет Р2 и соответствующий CRC Е2, и этот пятый фрейм нормально должен быть идентичным с вторым фреймом Т2.

На этапе (γ) (который может быть осуществлен одновременно с похожим на него этапом (с)), показанном на фиг. 4d, передают пятый фрейм Т5 (либо через ту же проводку, либо через прямую связь, так как все входные модули 10 расположены близко) в интерфейсный модуль 12а главного входного блока 10а.

На этапе (δ) (который может быть осуществлен одновременно с похожим на него этапом (d)) интерфейсный модуль 12а извлекает четвертый фрейм Т4 из пятого фрейма Т5 (отделив идентификатор фрейма и CRC С2) и передает его в соответствующий модуль 11а обработки данных.

На этапе (ε) (который может быть осуществлен одновременно с похожим на него этапом (е)), показанном на фиг. 4е, модуль 11а обработки данных главного входного блока 10а извлекает второй пакет Р2 из четвертого фрейма Т4.

Этот последний модуль имеет при этом две версии предназначенного для передачи пакета (первый пакет Р1, извлеченный из первого фрейма Т1, и его копию Р2, извлеченную из четвертого фрейма Т4) и может их сравнить на этапе (ζ) (который может быть осуществлен одновременно с похожим на него вышеупомянутым сравнением на уровне модуля 11b обработки данных вспомогательного входного блока 10b), показанном на фиг.4f. Неразрывность передачи данных во вспомогательный входной блок 10b подтверждают, только если результат сравнения является положительным, иначе говоря, если пакет Р1 и пакет Р2 являются идентичными, то есть генерирование каждого из этих пакетов (на основании одних и тех же данных) было произведено надлежащим образом. На этой стадии модуль 11а обработки данных главного входного блока 10а может быть уверен, что пакет Р1 был генерирован (и, следовательно, передан) без ошибки.

Вычислительное устройство FCC и система FCS

Вторым объектом изобретения является вычислительное устройство 1 управления полетом типа FCC, иначе говоря «линия», содержащая главный входной блок 10а, главный выходной блок 20а и по меньшей мере один вспомогательный входной блок 10b (и предпочтительно по меньшей мере один вспомогательный выходной блок 20b), при этом блоки выполнены с возможностью осуществления способа, являющегося первым объектом изобретения.

Блоки 10а, 10b, 20a, 20b одной линии 1 являются, как было указано выше, физически соединенными через единственную проводную связь, в частности проводную связь, соответствующую стандарту RS-485.

Третьим объектом изобретения является система управления полетом (типа FCS) летательного аппарата (в частности, вертолета), содержащая по меньшей мере три вычислительных устройства 1.1, 1.2, 1.3, являющихся вторым объектом изобретения, чтобы получить архитектуру, показанную на фиг. 1.

Входные блоки 10а, 10b вычислительных устройств 1.1, 1.2, 1.3 принимают данные управления полетом по меньшей мере от одного органа управления летательным аппаратом (ручка, педаль и т.д.), и выходные блоки 20а, 20b вычислительных устройств 1.1, 1.2, 1.3 выдают команды контроля по меньшей мере в одно исполнительное устройство летательного аппарата (домкраты, действующие на рули, и т.д.). Предпочтительно каждый входной блок 10а, 10b вычислительного устройства 1.1, 1.2, 1.3 соединен с выходными блоками 20а, 20b других вычислительных устройств 1.1, 1.2, 1.3, и/или все входные блоки 10а, 10b вычислительных устройств 1.1, 1.2, 1.3 (соответственно все выходные блоки 20а, 20b вычислительных устройств 1.1, 1.2, 1.3) соединены между собой.

Таким образом, летательный аппарат содержит систему управления полетом, органы управления и исполнительные устройства.

Компьютерный программный продукт

Третьим и четвертым объектами изобретения являются компьютерный программный продукт, содержащий командные коды с целью осуществления (в частности, на средствах 11а, 11b, 21a, 21b обработки данных блоков) способа проверки неразрывности передачи данных между главным входным блоком 10а и главным выходным блоком 20а, а также средства записи (в частности, запоминающее устройство блоков), считываемые компьютерным устройством, на которых записан этот компьютерный программный продукт.

Изобретение относится к средствам проверки неразрывности передачи данных между главным входным блоком и главным выходным блоком. Технический результат заключается в повышении надежности передачи данных. Генерируют, при помощи модуля обработки данных главного входного блока, первый фрейм, подлежащий передаче пакет данных и избыточный циклический код указанного пакета. Инкапсулируют первый фрейм во второй фрейм, дополнительно содержащий избыточный циклический код первого фрейма. Включают избыточный циклический код указанного пакета в третий фрейм. Сравнивают, при помощи модуля обработки данных по меньшей мере одного вспомогательного входного блока, каждый из избыточных циклических кодов, извлеченных из первого фрейма и третьего фрейма. Подтверждают неразрывность передачи данных в главный выходной блок, только если сравнение дает положительный результат. 4 н. и 8 з.п. ф-лы, 16 ил.

1. Способ проверки неразрывности передачи данных между главным входным блоком (10а) и главным выходным блоком (20а), содержащий этапы, на которых:

(а) генерируют, при помощи модуля (11а) обработки данных главного входного блока (10а), первый фрейм (Т1), содержащий подлежащий передаче пакет (Р1) данных и избыточный циклический код (Е1) указанного пакета (Р1), и передают их в интерфейсный модуль (12а) главного входного блока (10а);

(b) инкапсулируют, при помощи указанного интерфейсного модуля (12а) главного входного блока (10а), первый фрейм (Т1) во второй фрейм (Т2), дополнительно содержащий избыточный циклический код (С1) первого фрейма (Т1);

(c) передают второй фрейм (Т2) в интерфейсные модули (22а, 12b) главного выходного блока (20а) и по меньшей мере одного вспомогательного входного блока (10b);

(d) извлекают, при помощи интерфейсных модулей (22а, 12b) главного выходного блока (20а) и указанного по меньшей мере одного вспомогательного входного блока (10b), первый фрейм (Т1) из второго фрейма (Т2) и передают его в модули (21а, 11b) обработки данных главного выходного блока (20а) и указанного по меньшей мере одного вспомогательного входного блока (10b);

(e) извлекают при помощи модуля (21а) обработки данных главного выходного блока (20а) указанный пакет (Р1) из первого фрейма (Т1) и извлекают при помощи модуля (21а) обработки данных указанного по меньшей мере одного вспомогательного входного блока (10b) избыточный циклический код (Е1) указанного пакета (Р1);

(f) инкапсулируют при помощи указанного интерфейсного модуля (12а) главного входного блока (10а) избыточный циклический код (Е1) указанного пакета (Р1) в третий фрейм (Т3);

(g) передают третий фрейм в интерфейсный модуль (12b) указанного по меньшей мере одного вспомогательного входного блока (10b);

(h) извлекают при помощи интерфейсного модуля (12b) указанного по меньшей мере одного вспомогательного входного блока (10b) избыточный циклический код (Е1) указанного пакета (Р1) из третьего фрейма (Т3) и передают его в модуль (11b) обработки данных указанного по меньшей мере одного вспомогательного входного блока (10b);

(i) сравнивают, при помощи модуля (11b) обработки данных указанного по меньшей мере одного вспомогательного входного блока (10b), каждый из избыточных циклических кодов (Е1), извлеченных из первого фрейма (Т1) и третьего фрейма (Т3), и подтверждают неразрывность передачи данных в главный выходной блок (20а), только если сравнение дает положительный результат.

2. Способ по п. 1, в котором на этапе (с) дополнительно передают второй фрейм (Т2) в интерфейсный модуль (22b) по меньшей мере одного вспомогательного выходного блока (20b); на этапе (d) извлекают первый фрейм (Т1) из второго фрейма (Т2) при помощи интерфейсного модуля (22b) указанного по меньшей мере одного вспомогательного выходного блока (20b); и на этапе (е) извлекают пакет (Р1) из первого фрейма (Т1) при помощи модуля (21b) обработки данных указанного по меньшей мере одного вспомогательного выходного блока (20b).

3. Способ по п. 2, дополнительно содержащий этап (j), на котором передают пакет (Р1), извлеченный модулем (21b) обработки данных указанного по меньшей мере одного вспомогательного выходного блока (20b), в модуль (21а) обработки данных главного выходного блока (20а); сравнивают, при помощи модуля (21а) обработки данных главного выходного блока (20а), каждый из полученных пакетов (Р1) и подтверждают неразрывность передачи данных в главный выходной блок (20а), только если результат сравнения является положительным.

4. Способ по любому из пп. 1-3, в котором подлежащий передаче пакет (Р1) является первым пакетом, генерируемым модулем (11а) обработки данных главного входного блока (10а) на основании данных управления, при этом на этапе (е) извлекают пакет (Р1) из первого фрейма (Т1) при помощи модуля (21а) обработки данных указанного по меньшей мере одного вспомогательного входного блока (10b); при этом способ дополнительно содержит этапы, на которых генерируют второй пакет (Р2) на основании тех же данных управления, что первый пакет (Р1), при помощи модуля (11b) обработки данных указанного по меньшей мере одного вспомогательного входного блока (10b); сравнивают, при помощи модуля (11b) обработки данных указанного по меньшей мере одного вспомогательного входного блока (10b), первый пакет (Р1) и второй пакет (Р2); и подтверждают неразрывность передачи данных в главный выходной блок (20а), только если результат сравнения является положительным.

5. Способ по любому из пп. 1-4, содержащий этапы, на которых:

(α) генерируют, при помощи модуля (11b) обработки данных указанного по меньшей мере одного вспомогательного входного блока (10b), четвертый фрейм (Т4), содержащий второй пакет (Р2) и избыточный циклический код (Е2) указанного второго пакета (Р2) и передают их в интерфейсный модуль (12b) указанного по меньшей мере одного вспомогательного входного блока (10b);

(β) инкапсулируют, при помощи указанного интерфейсного модуля (12b) указанного по меньшей мере одного вспомогательного входного блока (10b), четвертый фрейм (Т4) в пятый фрейм (Т5), дополнительно содержащий избыточный циклический код (Е2) четвертого фрейма (Т4);

(γ) передают пятый фрейм (Т5) в интерфейсный модуль (12а) главного входного блока (10а);

(δ) извлекают, при помощи интерфейсного модуля (12а) главного входного блока (10а), четвертый фрейм (Т4) из пятого фрейма (Т5) и передают его в модуль (11а) обработки данных главного входного блока (10а);

(ε) извлекают, при помощи модуля (11а) обработки данных главного входного блока (20а), второй пакет (Р2) из четвертого фрейма (Т4);

(ζ) сравнивают, при помощи модуля (11а) обработки данных главного входного блока (10а), первый пакет (Р1) и второй пакет (Р2) и подтверждают неразрывность передачи данных в главный выходной блок (20а), только если результат сравнения является положительным.

6. Способ по любому из пп. 1-5, в котором второй и третий фреймы (Т2, Т3) соответствуют стандарту Управления линией передачи данных высокого уровня (HDLC).

7. Способ по любому из пп. 1-6, в котором входные блоки (10а, 10b) и выходные блоки (20а, 20b) физически соединены через единую проводную связь.

8. Способ по п. 7, в котором указанная проводная связь соответствует стандарту RS-485.

9. Вычислительное устройство (1) управления полетом, содержащее главный входной блок (10а), главный выходной блок (20а) и по меньшей мере один вспомогательный входной блок (10b), при этом блоки выполнены с возможностью осуществления способа по любому из пп. 1-8.

10. Система управления полетом летательного аппарата, содержащая по меньшей мере три вычислительных устройства (1.1, 1.2, 1.3) по п. 9, при этом входные блоки (10а, 10b) вычислительных устройств (1.1, 1.2, 1.3) принимают данные управления полетом по меньшей мере от одного органа управления летательным аппаратом, а выходные блоки (20а, 20b) вычислительных устройств (1.1, 1.2, 1.3) выдают команды управления по меньшей мере в одно исполнительное устройство летательного аппарата.

11. Система по п. 10, в которой каждый входной блок (10а, 10b) вычислительного устройства (1.1, 1.2, 1.3) соединен с выходными блоками (20а, 20b) других вычислительных устройств (1.1, 1.2, 1.3).

12. Средства записи, считываемые компьютерным устройством, на которых компьютерный программный продукт содержит командные коды для осуществления способа по любому из пп. 1-8 проверки неразрывности передачи данных между главным входным блоком (10а) и главным выходным блоком (20а).

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| US 7877627 B1, 25.01.2011 | |||

| ИЗМЕРИТЕЛЬ ЗАПЫЛЕННОСТИ ВОЗДУХА | 2008 |

|

RU2383005C2 |

Авторы

Даты

2019-01-16—Публикация

2015-11-26—Подача