Область техники, к которой относится изобретение

Настоящее изобретение относится к процессору обработки данных и к способу обработки данных и, в частности, к процессору обработки данных и к способу обработки данных, например, которые способствуют правильной обработке потока.

Уровень техники

Например, в качестве примера стандарта цифровой широковещательной передачи, упоминается широковещательная передача видеоданных (DVB)-S2, используемая в Европе (Непатентный документ 1).

Список литературы

Непатентный документ

Непатентный документ 1: DVB-S.2: ETSIEN 302 307 VI.2.1 (2009-08)

Раскрытие изобретения

Задачи, решаемые изобретением

Технология для передачи потока с высокой скоростью передачи данных при цифровой широковещательной передаче данных представляет собой технологию связывания каналов (СВ), в которой поток с высокой скоростью передачи данных разделяют на потоки во множестве каналов для передачи на одну сторону передачи, и потоки по каналам реконструируют как исходный поток с высокой скоростью передачи данных на стороне приема.

В настоящее время выполняется разработка стандарта, называемого DVB-S2x (или DVB. 2 evo), в качестве улучшенного DVB-S2. Обсуждается возможность использования технологии СВ в DVB-S2x.

Однако детали технологии СВ не были до сих пор определены. Это может привести к ошибке при правильной обработке потока, когда используется технология СВ при цифровой широковещательной передаче, такой как DVB-S2x.

В учетом представленного выше, настоящее изобретение способствует правильной обработке потока.

Решения задачи

Первый процессор обработки данных, в соответствии с настоящим изобретением, включает в себя: модуль разделения для разделения входного потока, сформированного множеством пакетов, на разделенные потоки по множеству каналов, включающие в себя пакеты входного потока с заданной плотностью, посредством распределения каждого из пакетов входного потока в канал из каналов и распределения нулевых пакетов (NP) по всем другим каналам, кроме этого канала.

Первый способ обработки данных, в соответствии с настоящим изобретением, включает в себя этапы, на которых: разделяют входной поток, сформированный множеством пакетов, на разделенные потоки по множеству каналов, включающие в себя пакеты входного потока, с заданной плотностью, путем распределения каждого из пакетов входного потока в канал из каналов и распределения нулевых пакетов (NP) по всем другим каналам, кроме этого канала.

В описанных выше в первом процессоре обработки данных и в первом способе обработки данных, каждый из пакетов входного потока распределяют в один из множества каналов, а нулевые пакеты (NP) распределяют по другим каналам. Это разделяет входной поток на разделенные потоки по множеству каналов, включающих в себя пакеты входного потока с заданной плотностью.

Второй процессор обработки данных, в соответствии с настоящим изобретением, включает в себя: модуль разделения для разделения входного потока, сформированного множеством пакетов, на разделенные потоки по множеству каналов, включающих в себя пакеты входного потока с заданной плотностью, посредством распределения каждого из пакетов входного потока в канал из каналов и распределения нулевых пакетов (NP) по всем каналам, другим, чем этот канал; и модуль обработки для обработки потока, переданного из устройства передачи.

Второй способ обработки данных, в соответствии с настоящим изобретением, включает в себя этапы, на которых: обрабатывают поток, передаваемый от устройства передачи, при этом устройство передачи включает в себя модуль разделения, который разделяет входной поток, сформированный множеством пакетов, на разделенные потоки по множеству каналов, включающих в себя пакеты входного потока с заданной плотностью, путем распределения каждого из пакетов входного потока в канал из каналов и распределения нулевых пакетов (NP) по всем каналам, другим, чем этот канал.

Второй процессор обработки данных и способ обработки данных, описанные выше, обрабатывают поток, передаваемый из устройства передачи. Устройство передачи включает в себя модуль разделения для разделения входного потока, сформированного множеством пакетов, на множество разделенных потоков, включая в себя пакеты входного потока с заданной плотностью, путем распределения каждого из пакетов входного потока на один из множества каналов и распределения нулевых пакетов (NP) по другим каналам.

Следует отметить, что процессор обработки данных может представлять собой независимое устройство или может представлять собой внутренний блок, включенный в устройство.

Эффекты изобретения

В соответствии с настоящим изобретением, поток можно обрабатывать соответствующим образом.

Следует отметить, что настоящее изобретение не обязательно ограничено эффектами, описанными здесь, и может представлять собой любой один из описанных здесь эффектов.

Краткое описание чертежей

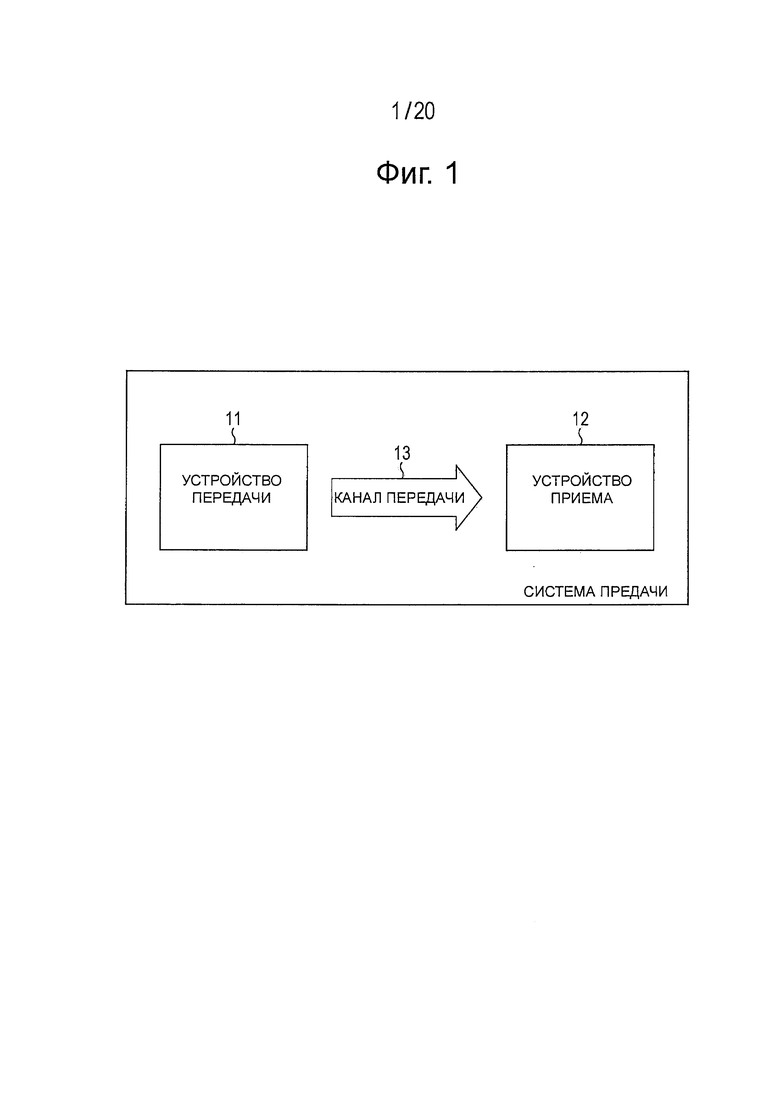

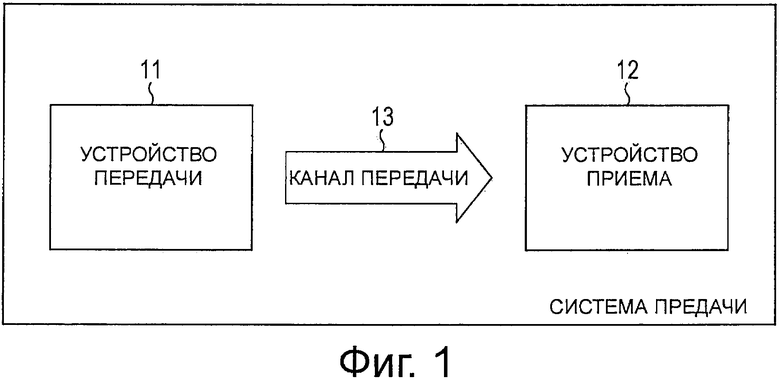

На фиг. 1 показана блок-схема примерной конфигурации в соответствии с вариантом осуществления системы передачи, в которой используется настоящее изобретение.

На фиг. 2 показана блок-схема примерной конфигурации устройства 11 передачи.

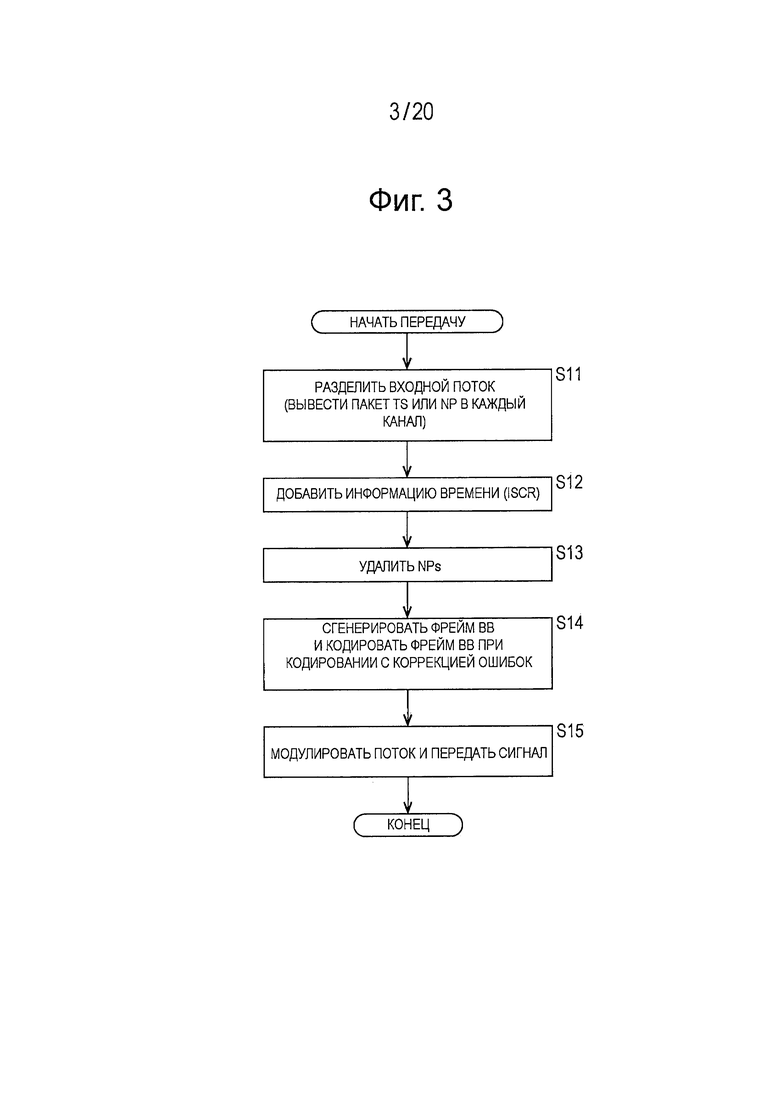

На фиг. 3 показана пояснительная блок-схема последовательности операций обработки (обработки передачи), выполняемой устройством 11 передачи.

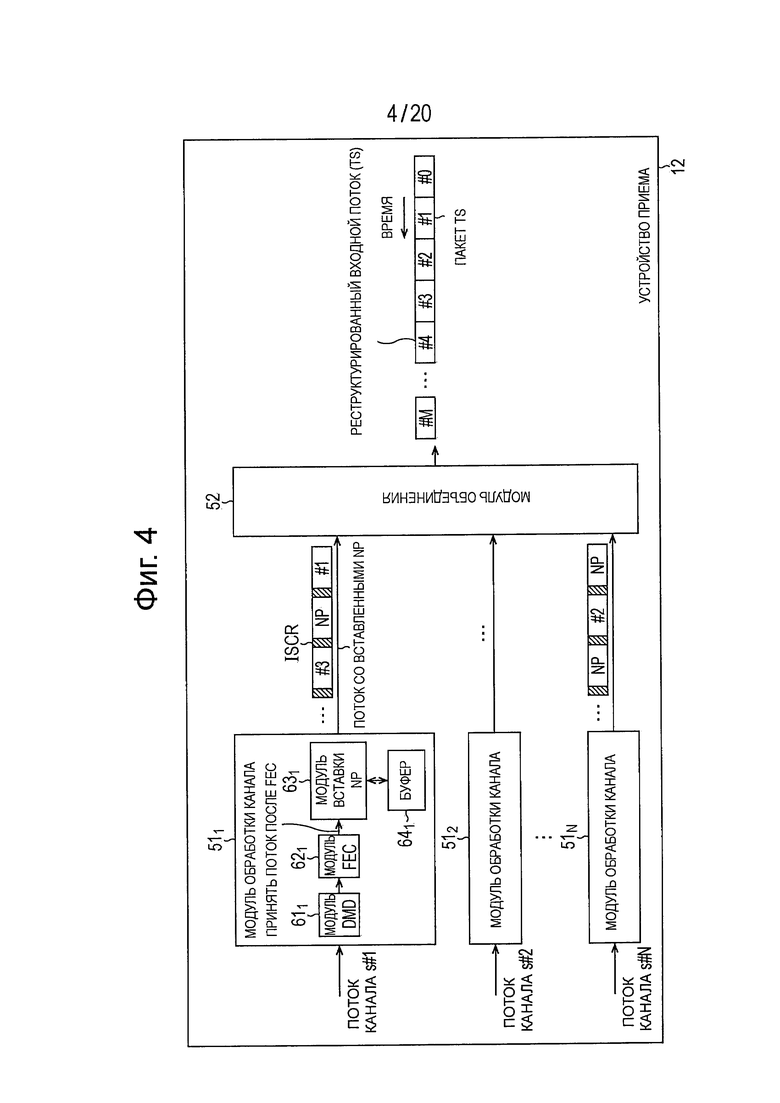

На фиг. 4 показана блок-схема примерной конфигурации устройства 12 приема.

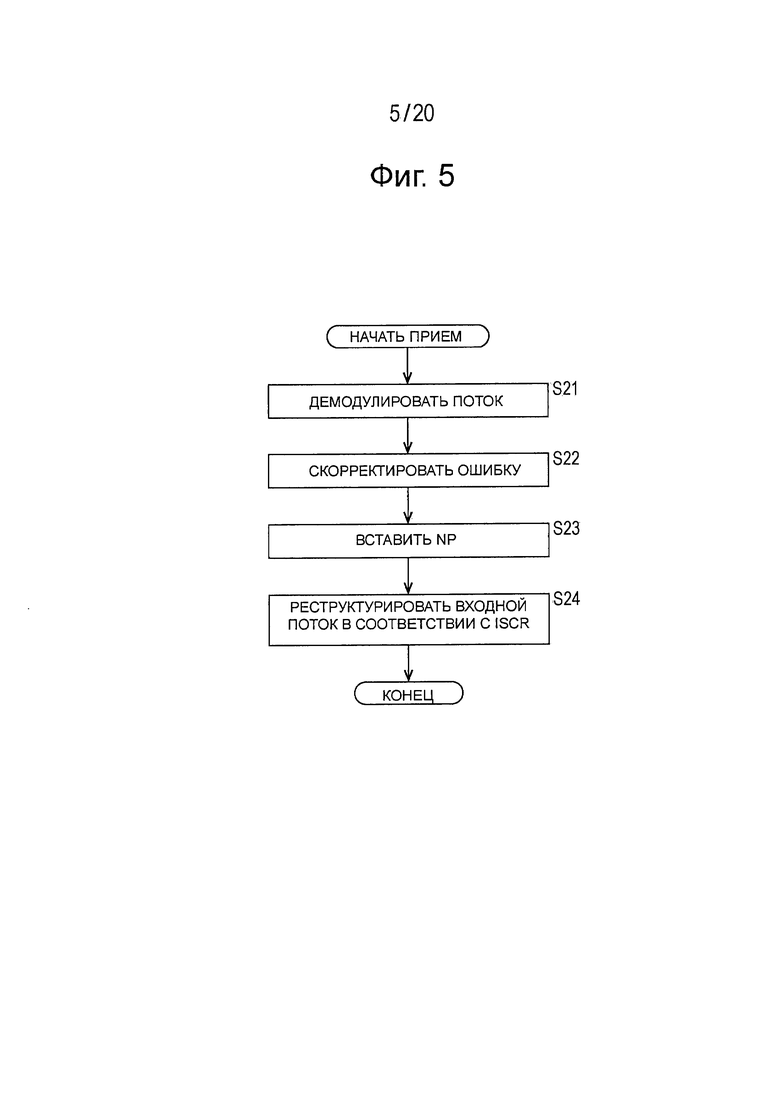

На фиг. 5 показана пояснительная блок-схема последовательности операций обработки (обработка приема), выполняемой устройством 12 приема.

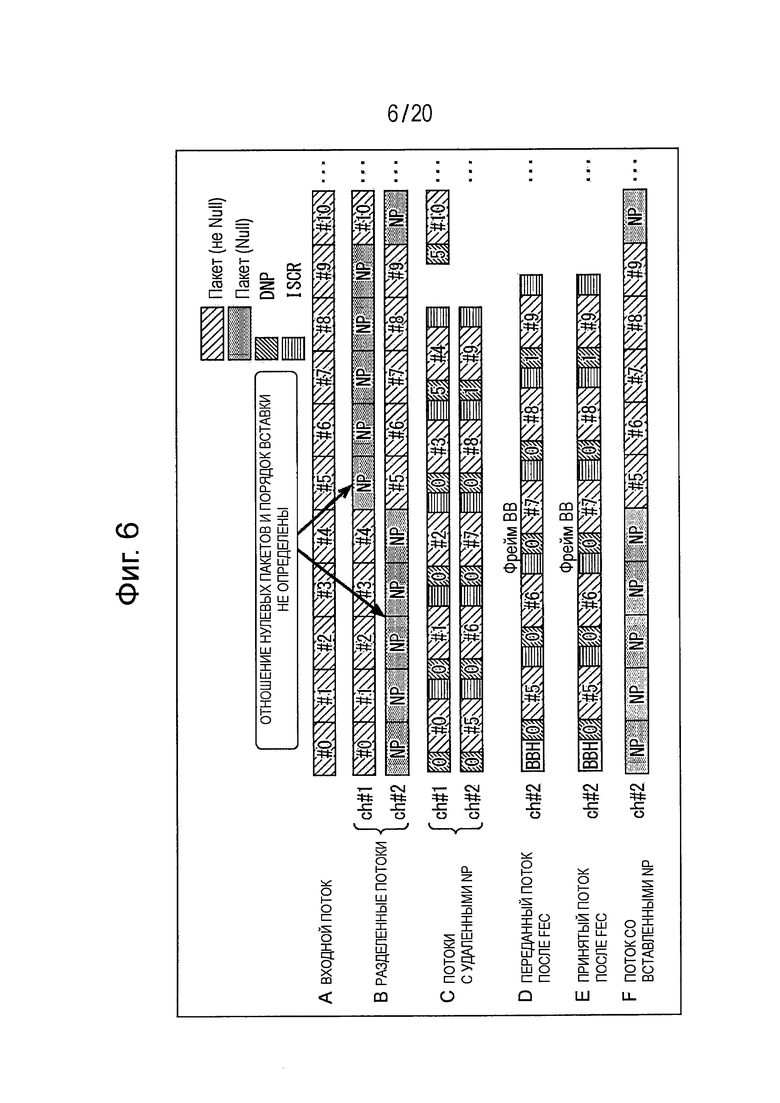

На фиг. 6 показана схема примерного потока, обрабатываемого в системе передачи.

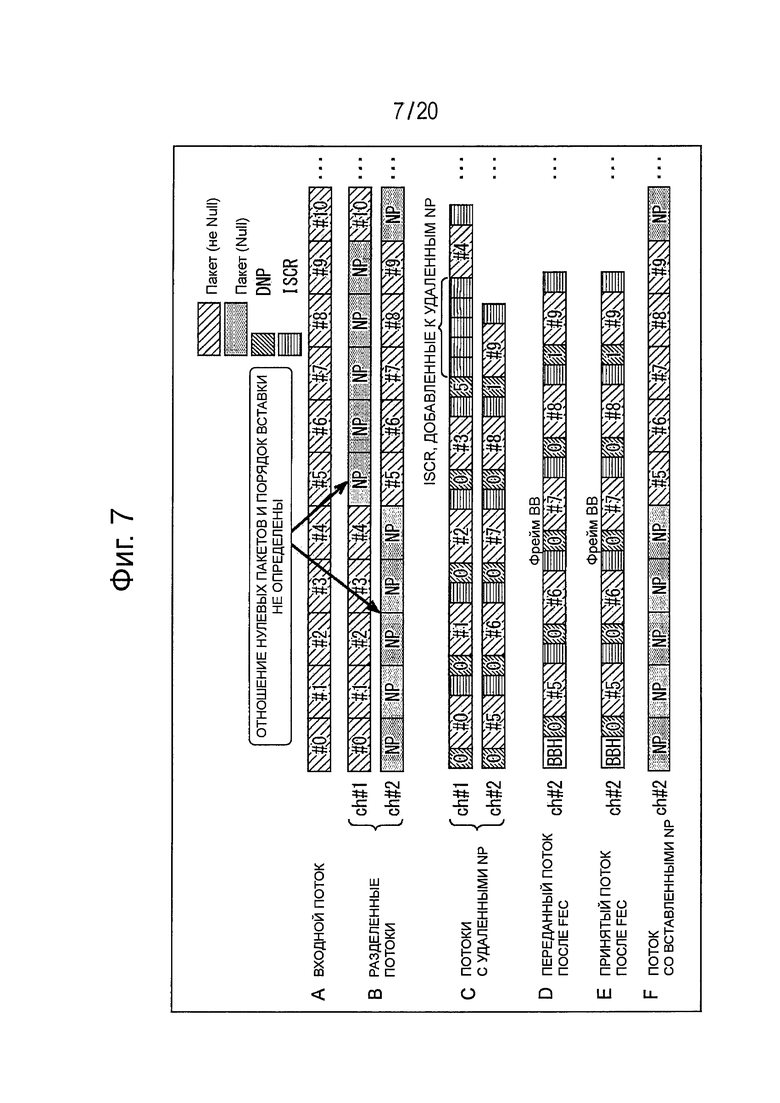

На фиг. 7 показана схема примерного потока, обрабатываемого в системе передачи.

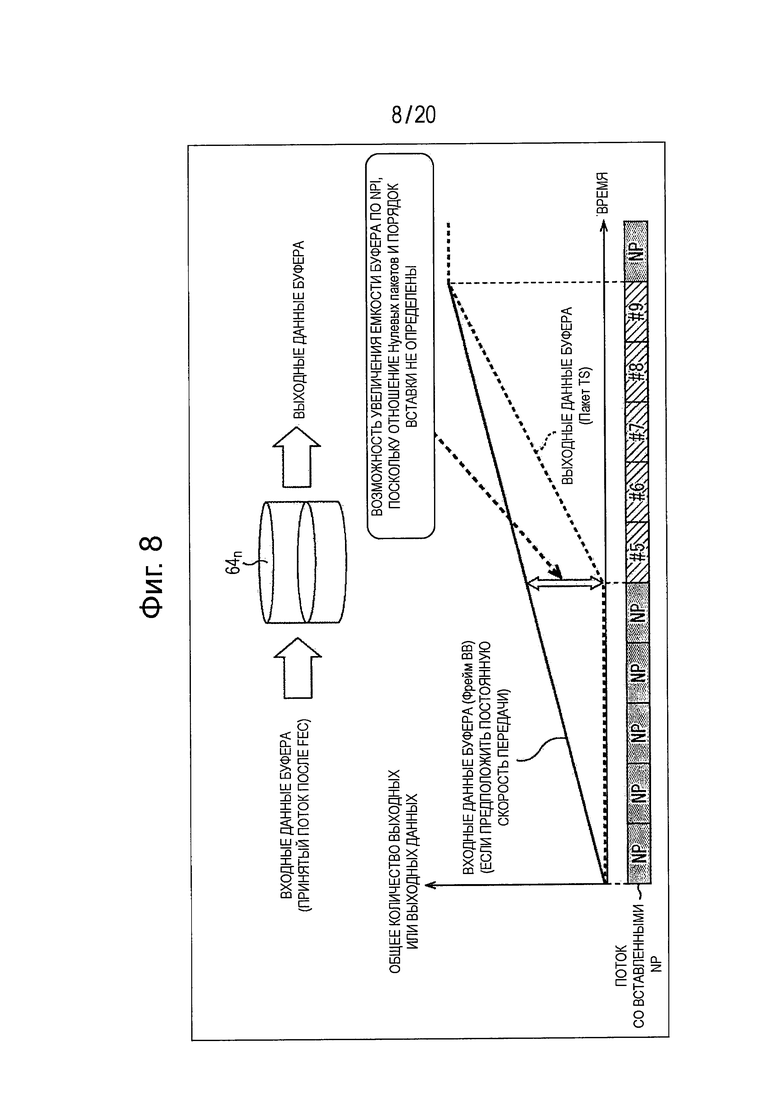

На фиг. 8 показана схема, поясняющая, что модуль 63n вставки NP в приемном устройстве 12 восстанавливает синхронизированный поток в канале ch#n, как поток со вставленными в NP в канале ch#n.

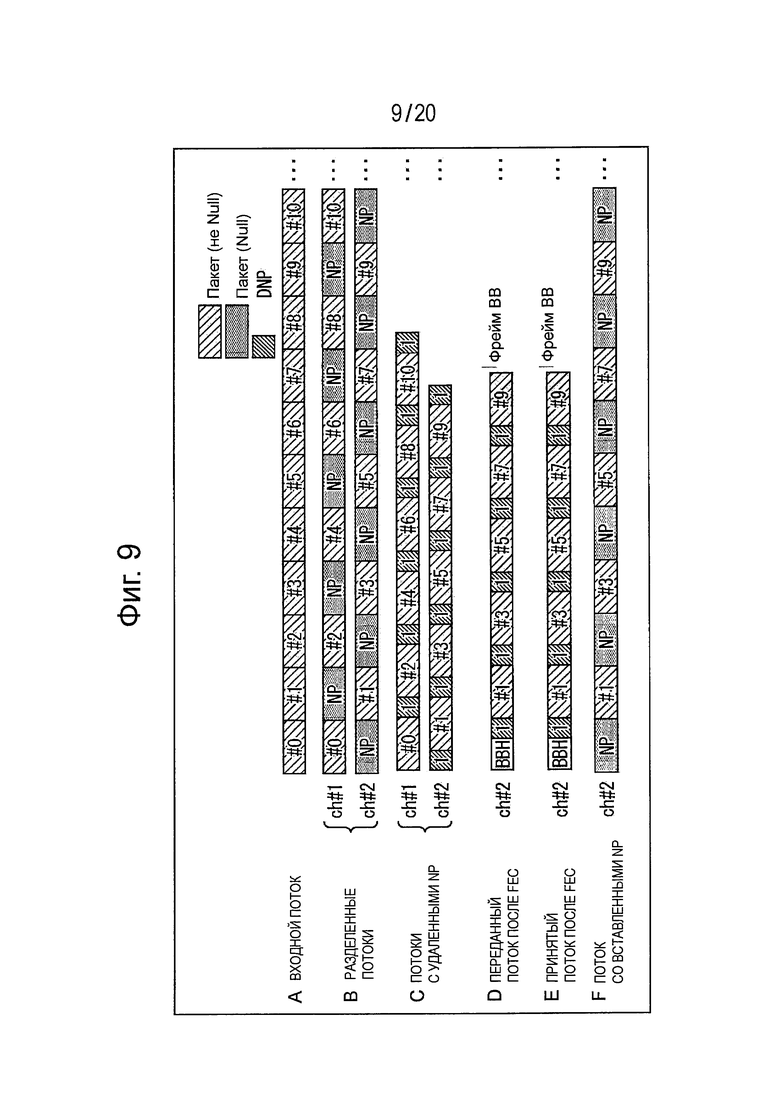

На фиг. 9 показана схема примерного потока, обрабатываемого в системе передачи, когда используется способ вставки NP.

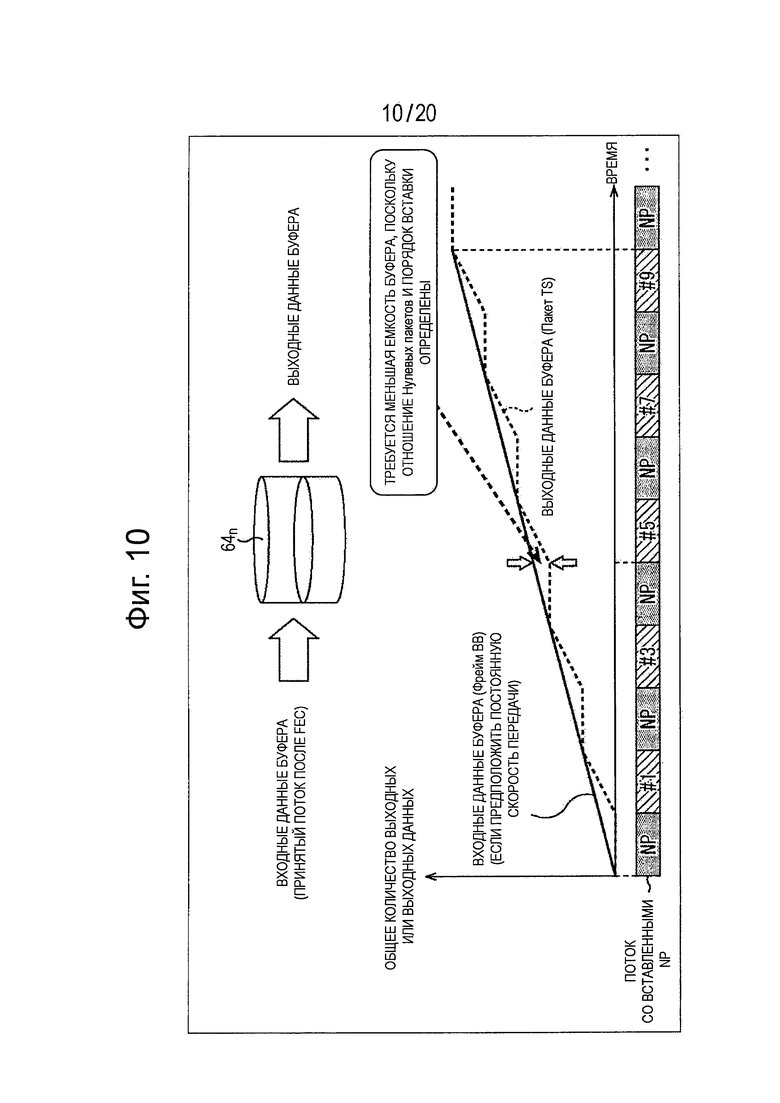

На фиг. 10 показана схема примерного временного изменения общей суммы входных данных буфера и общей суммы выходных данных буфера, когда используется способ вставки NP.

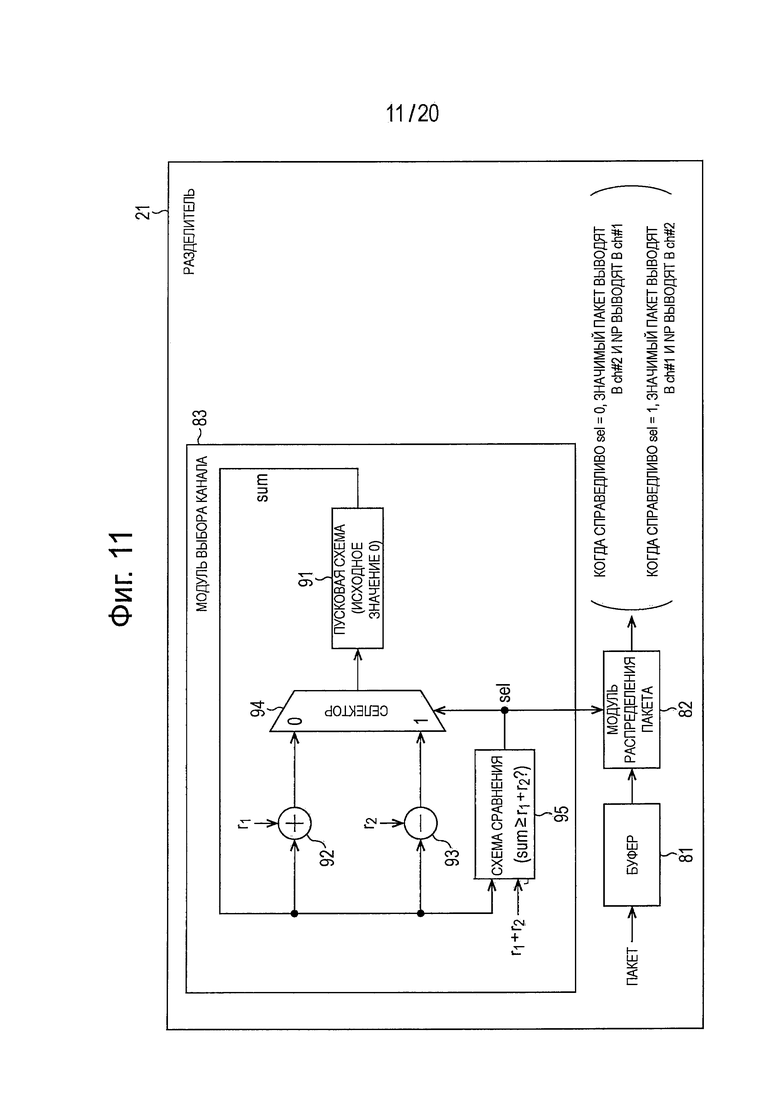

На фиг. 11 показана блок-схема первой примерной конфигурации разделителя 21.

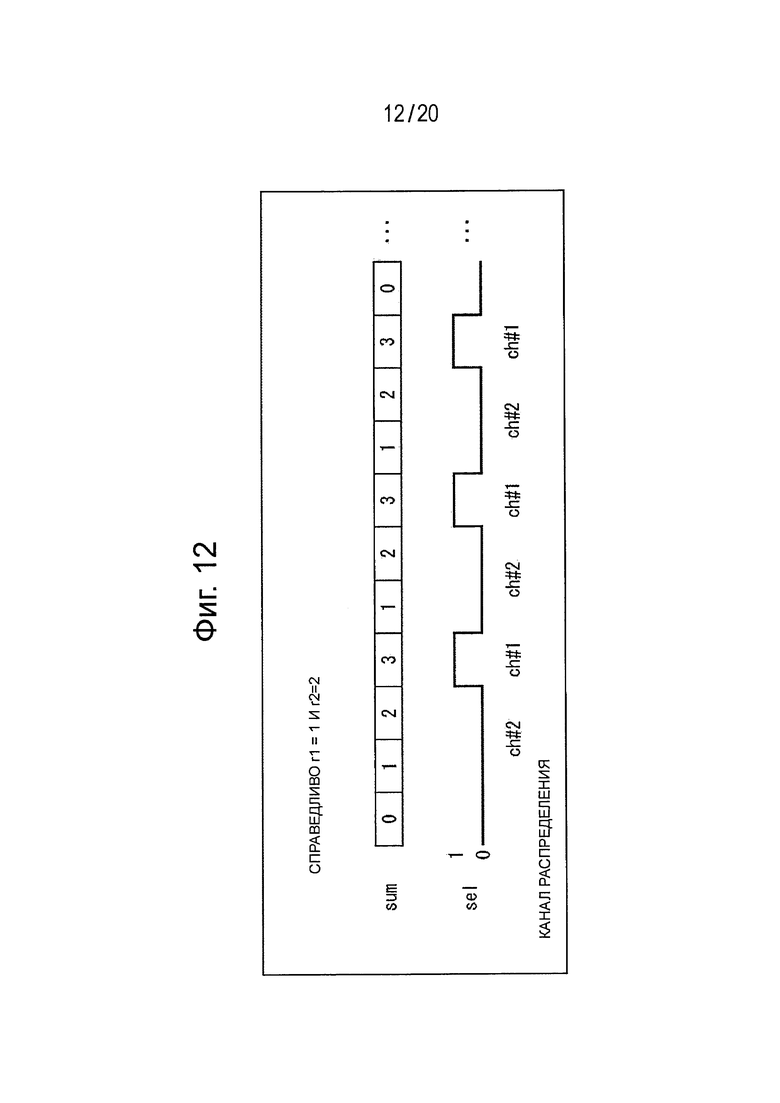

На фиг. 12 показана пояснительная схема операции разделителя 21.

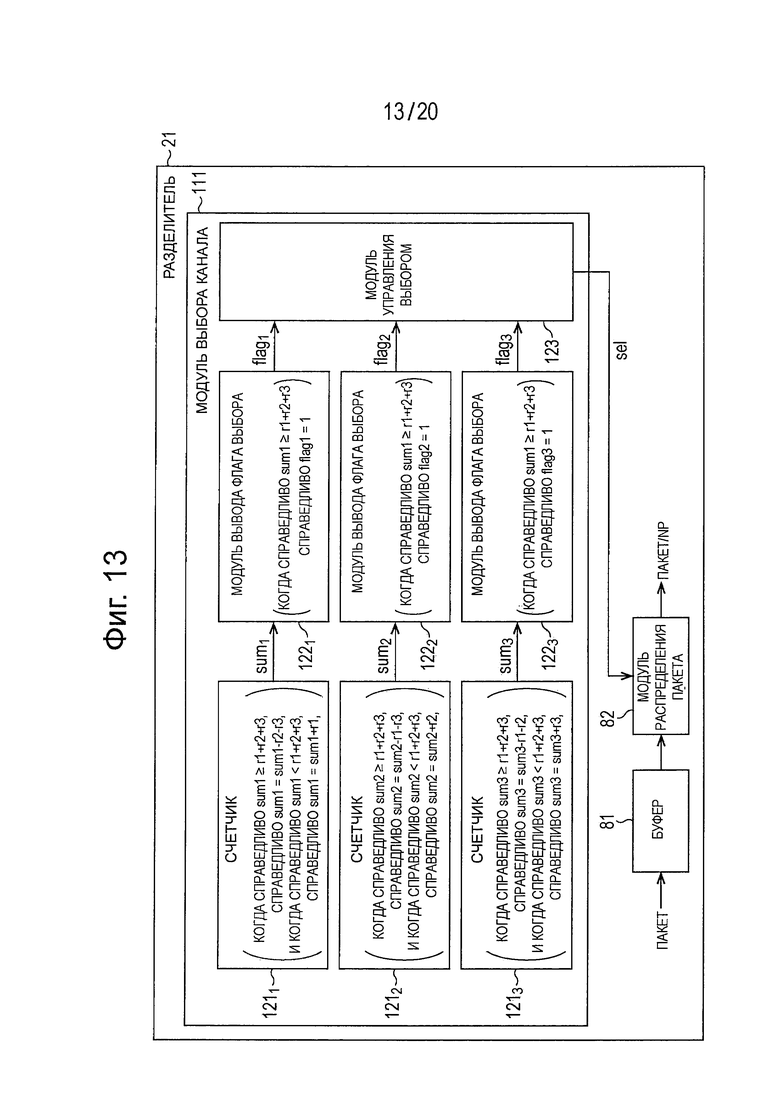

На фиг. 13 показана блок-схема второй примерной конфигурации разделителя 21.

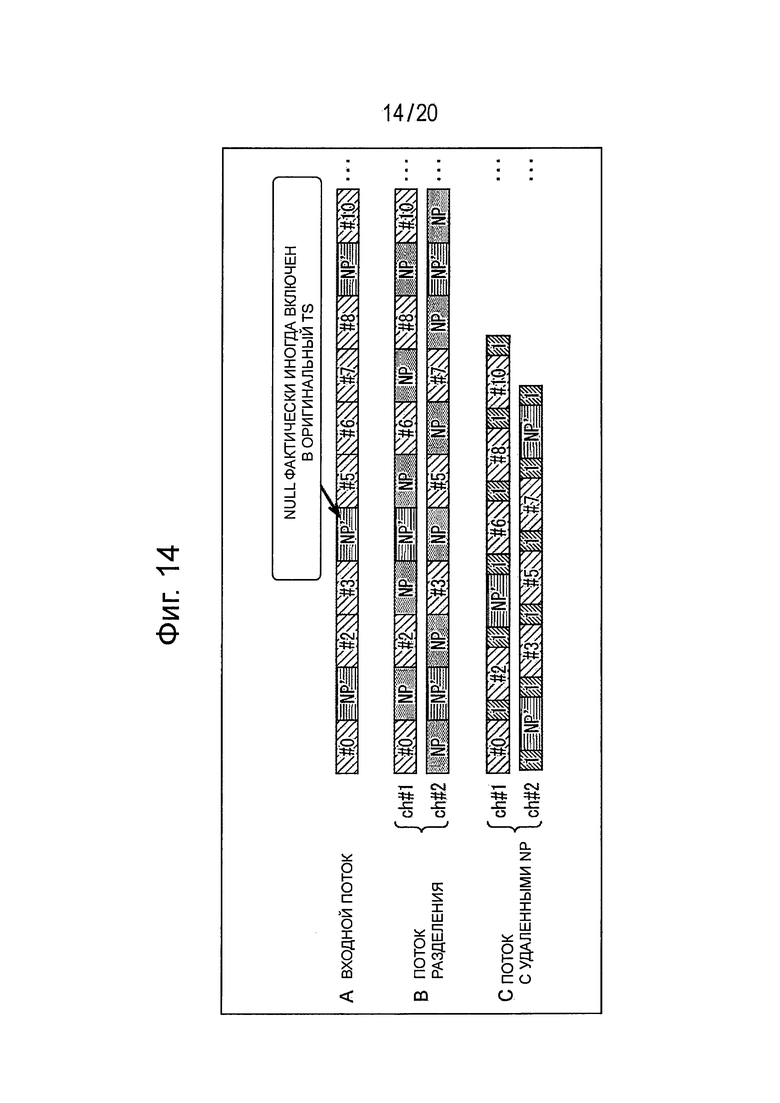

На фиг. 14 показана пояснительная схема примерной обработки, когда устройство 11 передачи обрабатывает входной поток, включающий в себя NP.

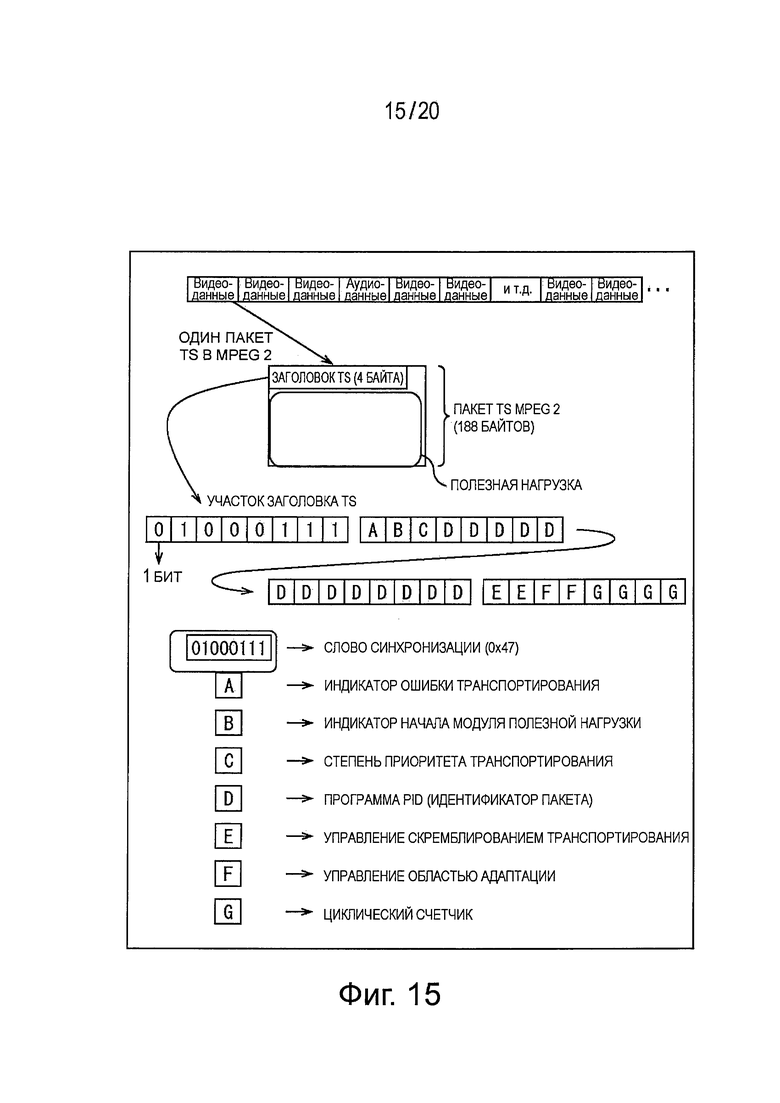

На фиг. 15 показана пояснительная схема примерного способа для распознавания NP, вставленного разделителем 21, от NP', изначально включенного во входной поток.

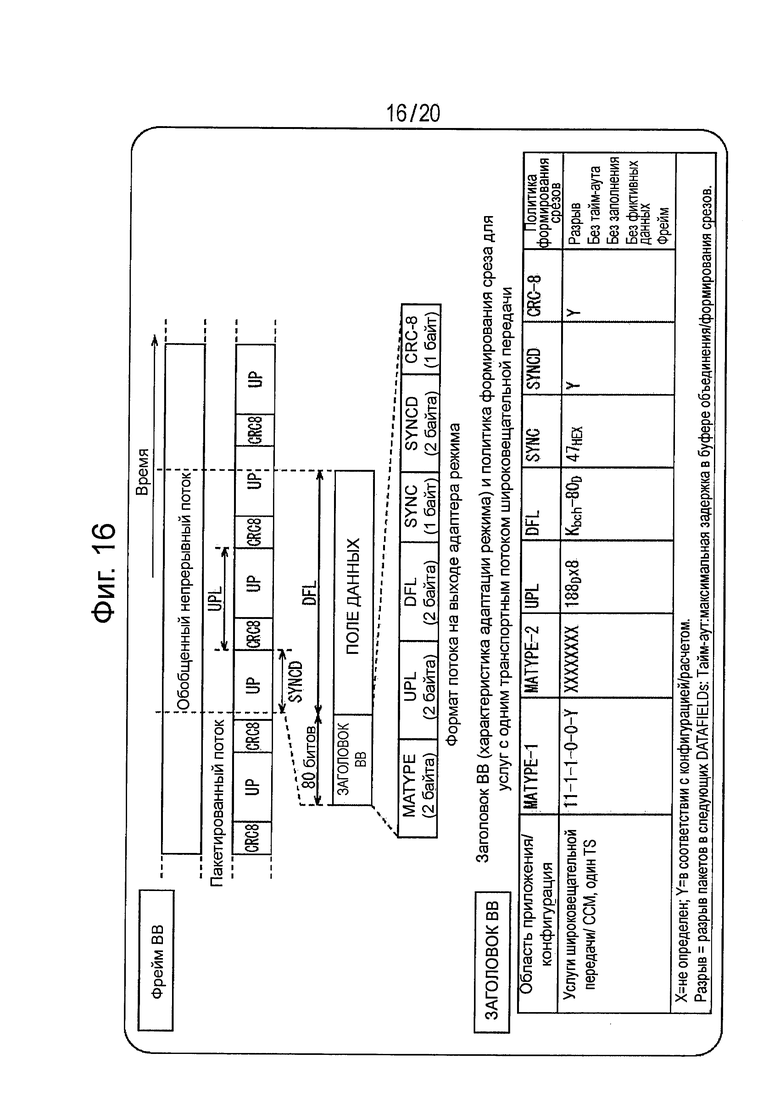

На фиг. 16 показана пояснительная схема идентификатора размера, обозначающего размер DNP.

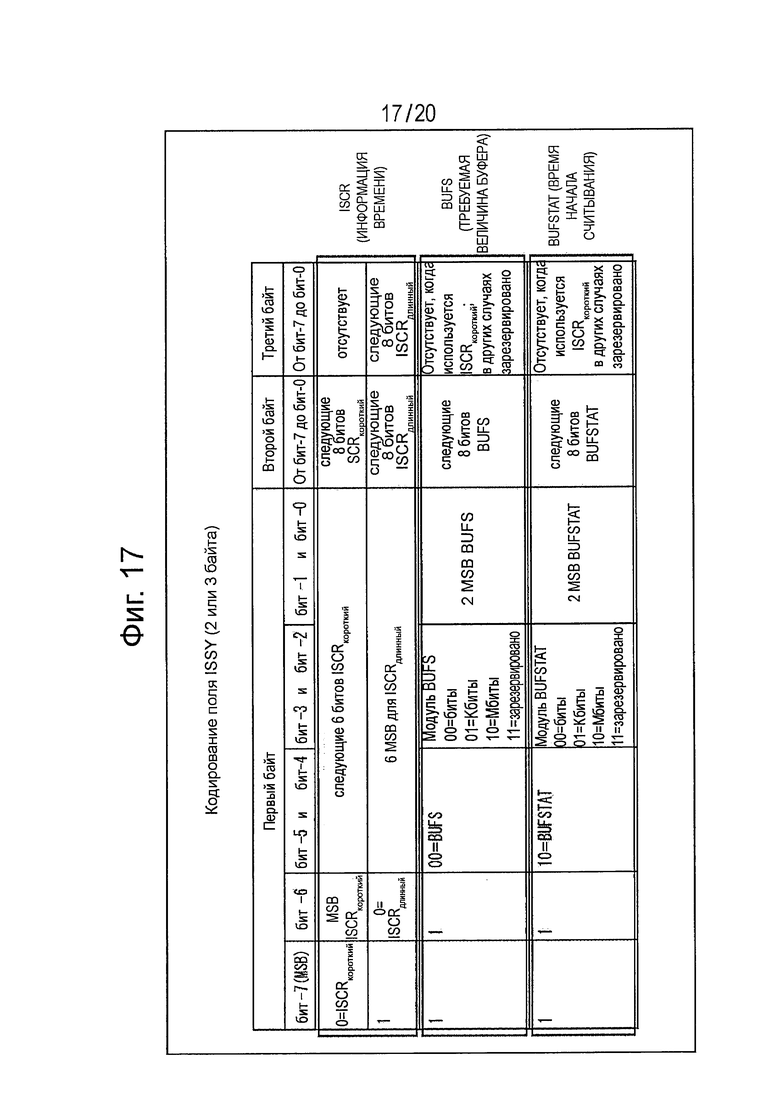

На фиг. 17 показана схема формата ISSY.

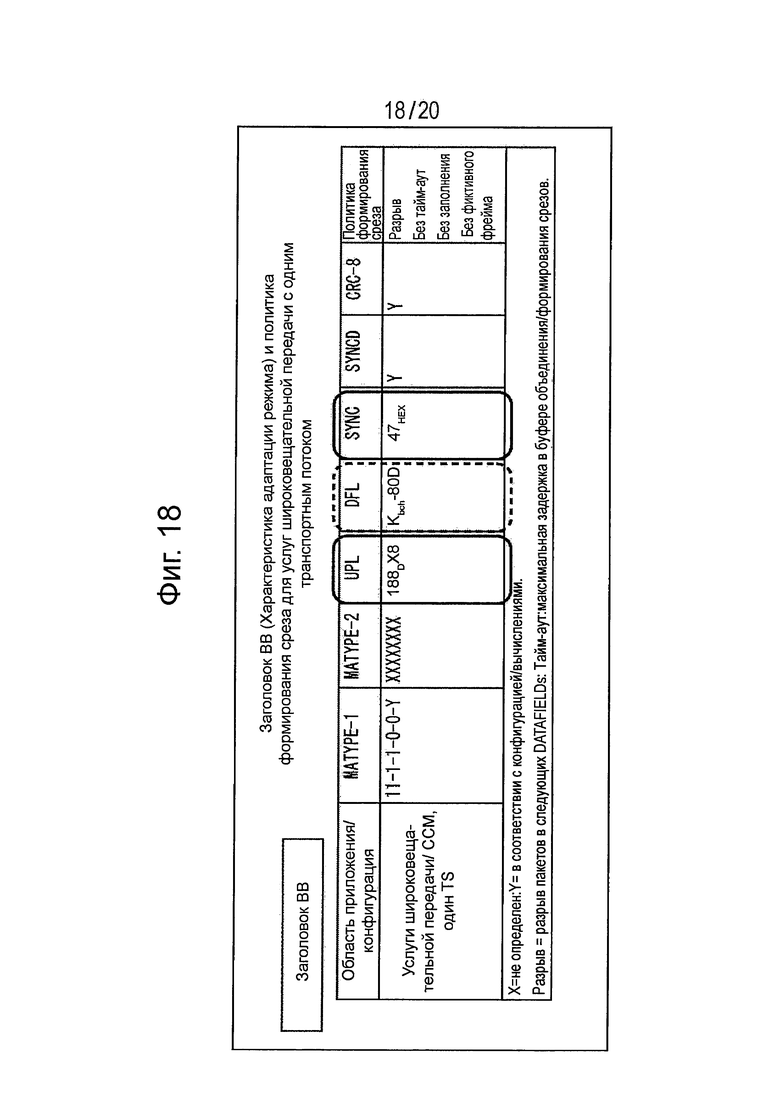

На фиг. 18 показана схема формата заголовка ВВ.

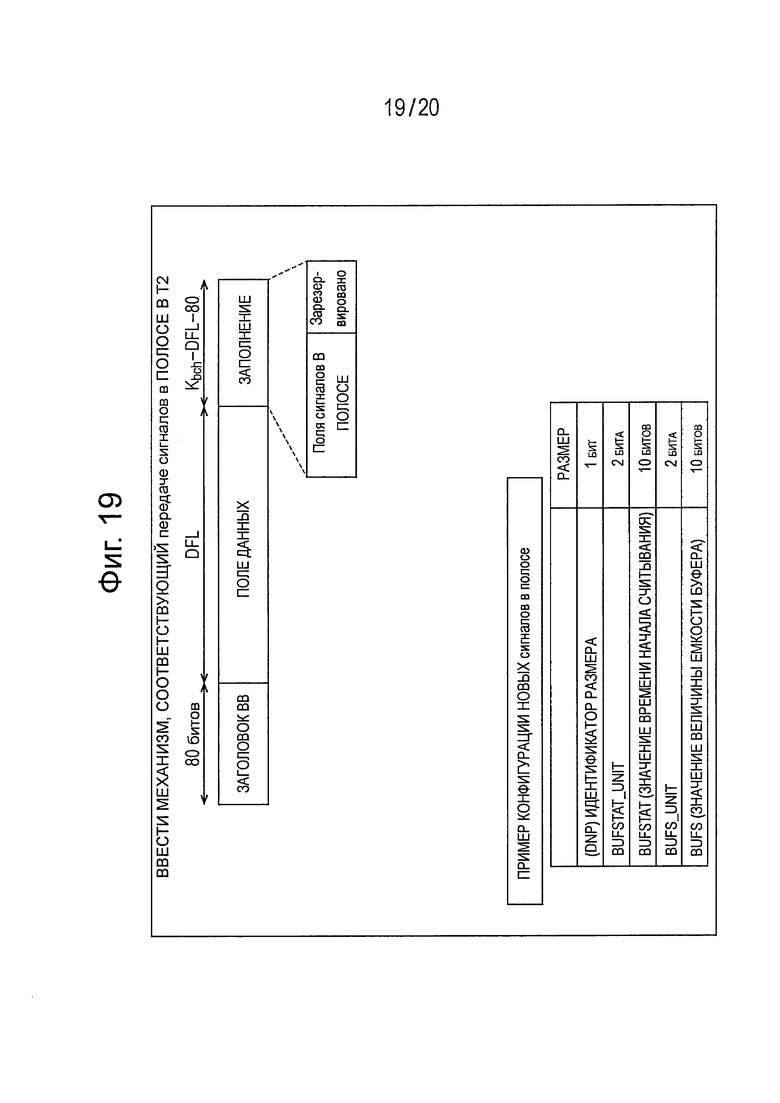

На фиг. 19 показана пояснительная схема способа передачи идентификатор размера, BUFS и BUFSTAT.

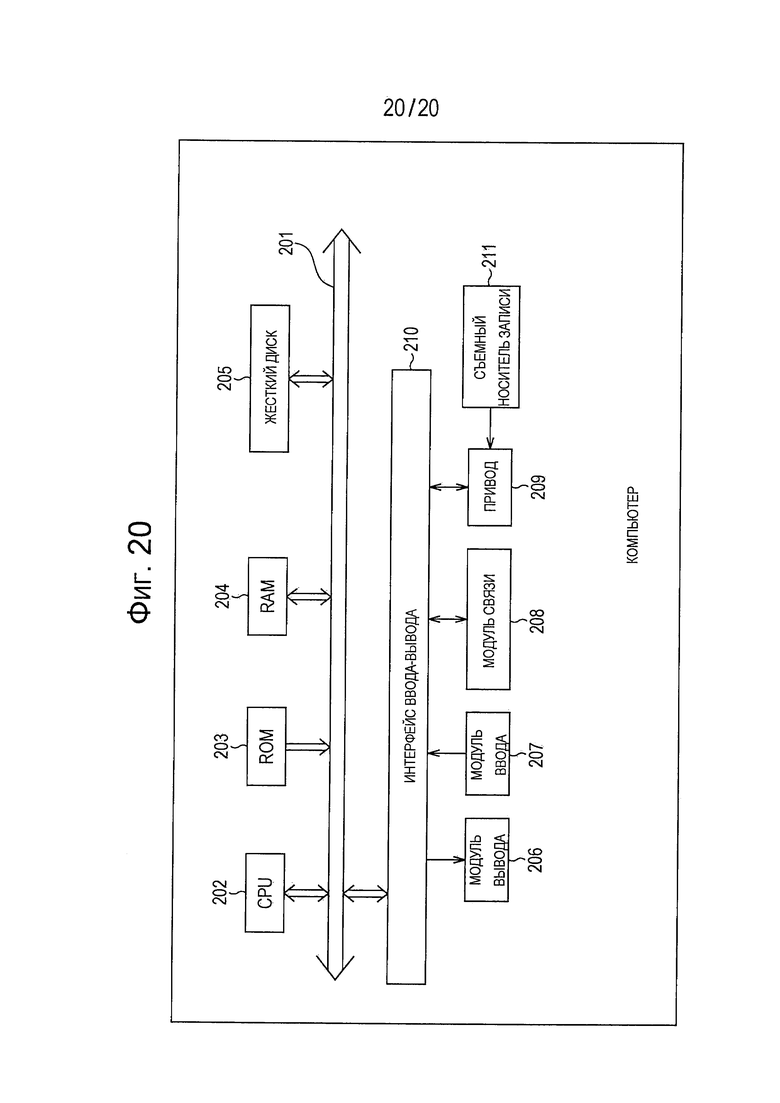

На фиг. 20 показана блок-схема примерной конфигурации варианта осуществления компьютера, в котором используется настоящее изобретение.

Осуществление изобретения

Вариант осуществления системы передачи, в которой используется настоящее изобретение

На фиг. 1 показана блок-схема варианта осуществления системы передачи, в которой используется настоящее изобретение (система представляет собой логическое соединение множества устройств, и при этом не имеет значения, размещены ли все эти устройства в корпусе).

Как представлено фиг. 1, система передачи включает в себя устройство 11 передачи и устройство 12 приема.

Устройство 11 передачи выполняет передачу (цифровую широковещательную передачу) (передачу данных), например, широковещательную передачу телевизионной программы. Другими словами, устройство 11 передачи передает поток данных, предназначенных для передачи, например, данных изображения и аудиоданных программы, путем разделения потока на потоки по множеству каналов и передачи этих потоков через канал 13 передачи, такой как спутниковая, наземная или кабельная (проводная) широковещательная передача с использованием технологии СВ.

Устройство 12 приема принимает потоки по каналам, переданным из устройства 11 передачи через канал 13 передачи, и восстанавливает и выводит исходный поток.

Пример конфигурации устройства 11 передачи

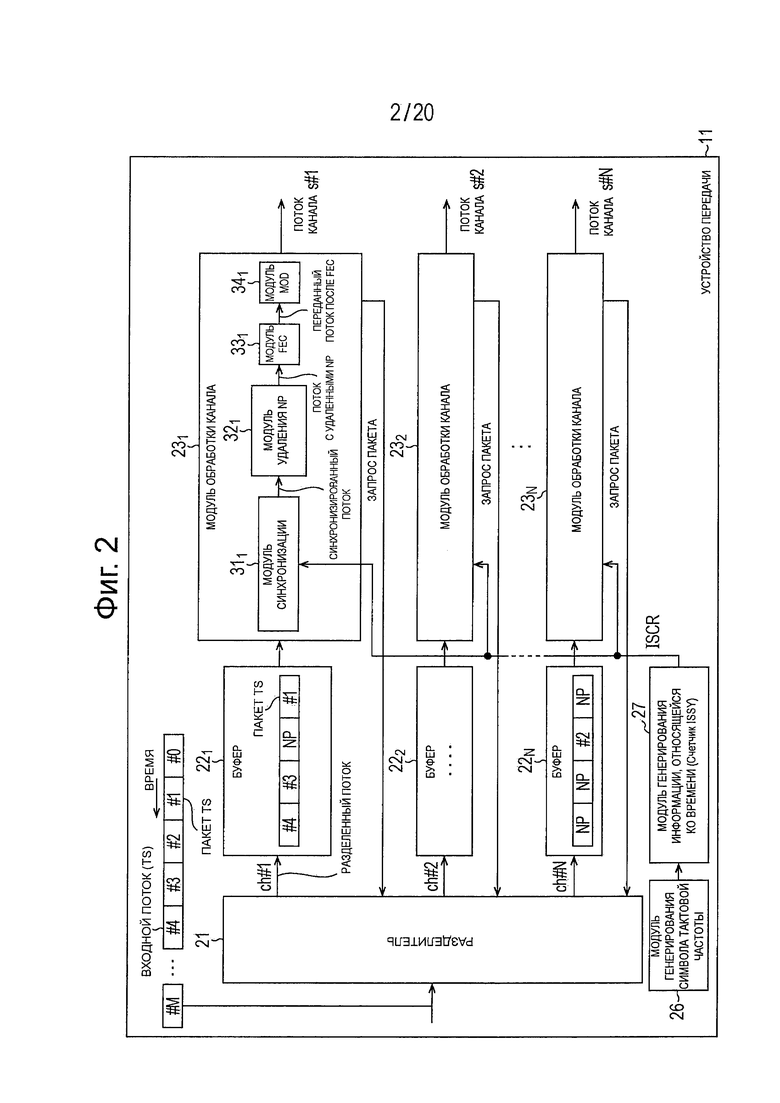

На фиг. 2 показана блок-схема примера конфигурации устройства 11 передачи, представленного на фиг. 1.

Как представлено на фиг. 2, устройство 11 передачи включает в себя разделитель 21, N буферов от 221 до 22N, N модулей от 231 до 23N обработки канала, модуль 26 генерирования тактовой частоты символа и модуль 27 генерирования информации, относящейся ко времени.

Поток, предназначенный для передачи, например, транспортный поток (TS) с высокой скоростью передачи данных, например, 100 Мегабит в секунду (Мбит/с), подают, как входной поток, в устройство 11 передачи. TS включает в себя, например, множество пакетов TS…, #0, #1…. Устройство 11 передачи разделяет входной поток на разделенные потоки по N (или меньшему количеству) каналов, как множество каналов, и передает потоки, используя технологию СВ.

Входной поток подают в разделитель 21. Разделитель 21 принимает подаваемый входной поток и делит поток на разделенные потоки по N (или меньше) каналам от ch#1 до ch#N.

Другими словами, разделитель 21 повторяет распределение каждого TS пакета входного потока по одному из N каналов от ch#1 до ch#N и нулевых пакетов (NP) по всем другим каналам. Это разделяет входной поток на разделенные потоки из N каналов от ch#1 до ch#N.

Разделитель 21 подает (пакеты) разделенного потока по каналу ch#n (n-ому каналу) в буфер 22n в ответ на запрос из модуля 23n обработки канала (запрос пакета).

В буфере 22n, например, используя принцип первым прибыл - первым обслужен (FIFO), последовательно сохраняют (пакеты) разделенного потока по каналу ch#n, передаваемому из разделителя 21 и последовательно подают сохраненный разделенный поток по каналу ch#n в модуль 23n обработки канала.

Модуль 23n обработки канала обрабатывает разделенный поток по каналу ch#n из буфера 22n, и передает поток s#1 канала по каналу ch#n, который представляет собой результат обработки.

Модуль 23n обработки канала включает в себя модуль 31n синхронизации, модуль 32n удаления нулевого пакета (NP), модуль 33n прямой коррекции ошибок (FEC) и модуль 34n модуляции (MOD).

Разделенный поток по каналу ch#n из буфера 22n и информацию, относящуюся ко времени, из модуля 27 генерирования информации, относящейся ко времени, передают в модуль 31n синхронизации. Информация, относящаяся ко времени, представляет собой, например, информацию о времени, когда передают пакет. Информация, относящаяся ко времени, представляет собой, например, опорное время входного потока (ISCR), обозначающее время, когда передают пакет. ISCR представляет собой синхронизатор входного потока (ISSY), определенный в DVB-S2.

Модуль 31n синхронизации добавляет ISCR к концу каждого пакета разделенного потока по каналу ch#n из буфера 22n. ISCR подают из модуля 27 генерирования информации, относящейся ко времени, когда каждый пакет подают в модуль 31n синхронизации. Затем модуль 31n синхронизации передает полученный в результате поток, как поток синхронизации, по каналу ch#n в модуль 32n удаления NP.

Модуль 32n удаления NP удаляет NP из синхронизированного потока, по каналу ch#n (разделенного потока, в котором добавлен ISCR к каждому пакету) из модуля 31n синхронизации. Модуль 32n удаления NP передает полученный в результате поток, как поток с удаленными NP, по каналу ch#n в модуль 33n FEC.

Как описано выше, модуль 32n удаления NP удаляет NP из синхронизированного потока. В результате, скорость передачи данных полученного в результате потока с удаленным NP уменьшена от скорости передачи данных входного потока на удаленные NP. Таким образом, поток с удаленными NP по каналу может быть передан с более узкой шириной полосы передачи, чем ширина полосы передачи, в которой передают входной поток.

Модуль 33n FEC функционирует, как модуль генерирования, который генерирует поток в фрейме ВВ, определенном, например, в DVB-S2, путем добавления заголовка основной полосы (ВВ) к одному или больше пакетам в потоке с удаленным NP по каналу ch#n, передаваемом из модуля 32n удаления NP, и добавления сигналов в полосе, определенной, например, в DVB-T2, в соответствии с необходимостью.

Кроме того, модуль 33n FEC кодирует фрейм ВВ, используя кодирование с коррекцией ошибок, например, кодирование ВСН или кодирование LDPC. Затем модуль 33n FEC предоставляет полученный в результате поток в фрейм ВВ, как переданный поток после FEC по каналу ch#n в модуль 34n MOD.

Модуль 34n MOD отображает в символической форме переданный поток после FEC по каналу ch#n из модуля 33n FEC в модуле с заданным количеством битов, и модулирует символы, используя квадратурную модуляцию. Затем модуль 34n MOD передает сигналы, полученные путем модуляции символов, используя квадратурную модуляцию, как поток s#n канала для канала ch#n.

Модуль 26 генерирования тактовой частоты символа генерирует тактовую частоту символа, которая представляет собой тактовую частоту, со скоростью передачи символов, и предоставляет тактовую частоту символа в модуль 27 генерирования информации, относящейся ко времени.

Модуль 27 генерирования информации, относящейся ко времени, генерирует ISSY, такой как ISCR, как информацию, относящуюся ко времени, в синхронизации с тактовой частотой символа из модуля 26 генерирования тактовой частоты символа, и предоставляет ISSY в (модули от 311 до 31N синхронизации) модулей 231 - 23N обработки канала. Таким образом, один и тот же ISSY, такой как ISCR, каждый раз предоставляют во все модули от 231 до 23N обработки канала.

Обработка передачи

На фиг. 3 показан пример блок-схемы последовательности операций обработки (обработки передачи), которую выполняет устройство 11 передачи, представленное на фиг. 2.

На этапе S11, разделитель 21 разделяет входной поток, подаваемый в него, на разделенные потоки по N каналам от ch#1 до ch#N, путем распределения каждого пакета TS входного потока на один из N каналов от ch#1 до ch#N и распределения NP по всем другим каналам. Каждый из разделенных потоков представляет собой смешанный поток пакетов TS и NP. Разделитель 21 передает разделенный поток по каналу ch#n в буфер 22n.

В буфере 22n последовательно сохраняют разделенный поток по каналу ch#n, передаваемому из разделителя 21, и последовательно передают сохраненный разделенный поток по каналу ch#n в модуль 23n обработки канала. Обработка переходит с этапа S11 на этап S12.

На этапе S12, модуль 31n синхронизации в модуле 23n обработки канала добавляет ISCR, предоставляемый из модуля 27 генерирования информации, относящейся ко времени, к концу каждого пакета в разделенном потоке канала ch#n из буфера 22n. Модуль 31n синхронизации предоставляет полученный поток, как синхронизированный поток, по каналу ch#n, в модуль 32n удаления NP. Обработка переходит на этап S13.

На этапе S13, модуль 32n удаления NP удаляет NP из синхронизированного потока по каналу ch#n (разделенный поток, в котором ISCR добавлен к каждому пакету) модуля 31n синхронизации. Модуль 32n удаления NP подает полученный в результате поток, как поток с удаленными NP, по каналу ch#n в модуль 33n FEC. Обработка переходит на этап S14.

На этапе S14 модуль 33n FEC генерирует поток во фрейме ВВ, путем добавления заголовка ВВ к одному или больше пакетам в потоке с удаленными NP по каналу ch#n, предоставленному из модуля 32n удаления NP, и также путем добавления сигналов в полосе, если необходимо.

Модуль 33n FEC кодирует фрейм ВВ, используя кодирование с коррекцией ошибок. Модуль 33n FEC предоставляет полученный в результате фрейм ВВ, как переданный поток после FEC по каналу ch#n в модуль 34n MOD. Обработка переходит с этапа S14 на этап S15.

На этапе S15, модуль 34n MOD модулирует переданный поток после FEC по каналу ch#n из модуля 33n FEC в квадратурной модуляции. Затем, модуль 34n MOD передает сигнал, полученный путем модуляции потока в квадратурной модуляции, как поток s#n канала для канала ch#n. Затем обработка заканчивается.

Следует отметить, что обработка передачи на этапах S11 - S15, представленных на фиг. 3, выполняется, используя конвейерную обработку.

Как описано выше, устройство 11 передачи изменяет входной поток на поток с удаленными NP путем разделения входного потока на разделенные потоки по N каналам от ch#1 до ch#N, которые представляют собой смешанные потоки пакетов TS и NP, и путем удаления NP из разделенных потоков канала ch#n. Затем устройство 11 передачи передает поток с удаленными NP.

В результате, скорость передачи данных потока с удаленными NP по каждому каналу ch#n уменьшается от скорости передачи данных входного потока на удаленные NP. Таким образом, входной поток с высокой скоростью передачи данных может быть передан с множеством каналов передачи, полоса пропускания передачи которых не является настолько широкой.

Кроме того, схема, которая не выполняет обработку с очень высокой скоростью, может использоваться, как модуль 33n FEC, который кодирует поток (фрейм ВВ, сгенерированный из потока) с удаленными NP канала ch#n при кодировании с коррекцией ошибок.

Пример конфигурации устройства 12 приема

На фиг. 4 показана блок-схема примера конфигурации устройства 12 приема, представленного на фиг. 1.

На фиг. 4, устройство 12 приема включает в себя N модулей от 511 до 51N обработки канала и модуль 52 слияния.

Модуль 51n обработки канала принимает и обрабатывает поток s#n канала по каналу ch#n, переданному из устройства 11 передачи.

Другими словами, модуль 51n обработки канала включает в себя модуль 61n демодуляции (DMD), модуль 62n FEC, модуль 63n вставки NP и буфер 64n.

Модуль 61n DMD принимает поток s#n канала по каналу ch#n, переданному из устройства 11 передачи, и демодулирует поток s#n канала по каналу ch#n, используя демодуляцию, соответствующую модуляции, выполняемую модулем 34n MOD, представленным на фиг. 2. Модуль 61n DMD предоставляет сигнал по каналу ch#n, полученный путем демодуляции потока s#n канала в модуль 62n FEC.

Модуль 62n FEC восстанавливает поток с удаленными NP в формате фрейма ВВ, предусмотренном модулем 33n FEC, показанным на фиг. 2, путем декодирования кода с коррекцией ошибок, используя коррекцию ошибок, соответствующую кодированию с коррекцией ошибок, в модуле 33n FEC, представленном на фиг. 2, для демодулированного сигнала по каналу ch#n из модуля 61n DMD. Модуль 62n FEC предоставляет восстановленный поток, как принятый поток после FEC по каналу ch#n в модуль 63n вставки NP.

Модуль 63n вставки NP предоставляет принятый поток после FEC по каналу ch#n из модуля 62n FEC в буфер 64n для сохранения принятого потока после FEC в буфере 64n.

Модуль 63n вставки NP соответствующим образом вставляет NP в принятый поток после FEC, а именно, в поток с удаленными NP (в формате фрейма ВВ), путем вывода пакетов принятого потока после FEC, сохраненного в буфере 64n, или NP, в соответствии с необходимостью.

Благодаря такой вставке, модуль 63n вставки NP восстанавливает синхронизированный поток канала ch#n, предоставляемый из модуля 31n синхронизации, в модуль 32 удаления NP на фиг. 2, и предоставляет восстановленный поток, как поток со вставленными NP, по каналу ch#n в модуль 52 слияния.

Поток со вставленными NP по каналу ch#n представляет собой поток, полученный путем восстановления синхронизированного потока по каналу ch#n, предоставляемому из модуля 31n синхронизации в модуль 32 удаления NP. Таким образом, ISCR добавляют в конце каждого пакета в потоке со вставленными NP по каналу ch#n.

В буфере 64n временно сохраняют пакеты в принятом потоке после FEC канала ch#n, предоставляемого из модуля 63n вставки NP, в соответствии с управлением модулем 63n вставки NP, и считывают сохраненные пакеты.

Модуль 52 слияния реконструирует и выводит входной поток, сформированный множеством пакетов TS #0, #1… путем размещения, в порядке времени передачи, представленном ISCR, других пакетов, чем NP, вставленные модулями от 631 по 63N вставки NP среди пакетов потоков со вставленными NP по каналам от ch#1 до ch#N, в соответствии с ISCR, добавленным к концу каждого пакета в потоках со вставленными NP по каналам от ch#1 до ch#N, предоставляемым из модулей от 631 по 63N вставки NP в модули 511 по 51N обработки канала.

Обработка приема

На фиг. 5 показана пояснительная блок-схема последовательности операций обработки (обработки приема) при приеме в устройстве 12, представленном на фиг. 4.

На этапе S21, модуль 61n DMD модуля 51n обработки канала принимает и демодулирует поток s#n канала по каналу ch#n, переданный из устройства 11 передачи. Модуль 61n DMD подает сигнал по каналу ch#n, полученный в результате демодуляции канала, поток s#n в модуль 62n FEC. Затем обработка переходит на этап S22.

На этапе S22 модуль 62n FEC восстанавливает поток с удаленными NP в формате фрейма ВВ, путем коррекции ошибок в демодулированном сигнале по каналу ch#n из модуля 61n DMD, и предоставляет восстановленный поток с удаленными NP, как принятый поток после FEC по каналу ch#n в модуль 63n вставки NP. Обработка переходит на этап S23.

На этапе S23, модуль 63n вставки NP предоставляет принятый поток после FEC по каналу ch#n из модуля 62n FEC в буфер 64n для сохранения принятого потока в буфере 64n. Модуль 63n вставки NP восстанавливает синхронизированный поток по каналу ch#n, который представляет собой принятый поток после FEC (поток с удаленными NP (в формате фрейма ВВ)), к которому NP были добавлены соответствующим образом, путем вывода пакетов в принимаемом потоке после FEC, сохраненном в буфере 64n или NP, и предоставляет восстановленный поток, как поток со вставленными NP по каналу ch#n, в модуль 52 слияния.

Затем обработка переходит с этапа S23 на этап S24. Модуль 52 слияния реконструирует и выводит входной поток, сформированный множеством пакетов TS…, #0, #1… в соответствии с ISCR, добавленным в конце каждого пакета, в потоки со вставленными NP по каналам от ch#1 по ch#N, предоставляемым из модулей от 631 по 63N вставки NP. Затем обработка заканчивается.

Следует отметить, что обработка на этапах от S21 по S24 на фиг. 5 выполняется в виде конвейерной обработки.

Поток, который обрабатывает система передачи

На фиг. 6 показана схема примерного потока, который обрабатывает система передачи, представленная на фиг. 1.

Следует отметить, что количество N каналов равно двум на фиг. 6.

В позиции А на фиг. 6 показан примерный входной поток, который предоставляют в разделитель 21 в устройстве 11 передачи (фиг. 2).

Входной поток сформирован из множества пакетов TS #0, #1….

В позиции В на фиг. 6 показан пример разделенных потоков, подаваемых в модуль 31n синхронизации из разделителя 21 через буфер 22n в устройстве 11 передачи (фиг. 2).

Разделитель 21 разделяет входной поток на два разделенных потока по двум каналам от ch#1 по ch#2 путем распределения каждого пакета TS во входном потоке в позиции А на фиг. 6 в один из двух каналов от ch#1 до ch#2, и распределения NP в другой канал.

Например, разделитель 21 последовательно распределяет TS пакеты от #0 до #4 во входном потоке в позиции А на фиг. 6 в канал ch#1, и последовательно распределяет пять NP в канал ch#2, и затем последовательно распределяет пакеты от #5 до #9 TS в канал ch#2, и последовательно распределяет пять NP в канал ch#1. После этого разделитель 21 аналогично распределяет пакеты TS во входном потоке в один из этих двух каналов ch#1 и ch#2, и распределяет NP в другой канал. Как описано выше, разделитель 21 делит входной поток на разделенные потоки из двух каналов ch#1 и ch#2 в позиции В на фиг. 6.

В позиции С на фиг. 6 показан пример потока с удаленными NP, предоставляемого из модуля 32n удаления NP в модуле 33n FEC в устройстве 11 передачи (фиг. 2).

Модуль 31n синхронизации изменяет разделенный поток по каналу ch#n, предоставляемый разделителем 21, на синхронизированный поток по каналу ch#n, путем добавления ISCR к концу каждого пакета в разделенном потоке по каналу ch#n.

Модуль 32n удаления NP изменяет синхронизированный поток канала ch#n на поток с удаленными NP по каналу ch#n, путем удаления NP из синхронизированного потока по каналу ch#n.

Когда модуль 32 удаления NP изменяет синхронизированный поток по каналу ch#n на поток с удаленными NP по каналу ch#n, путем удаления NP из синхронизированного потока по каналу ch#n, модуль 32n удаления NP добавляет, например, нулевые пакеты с удаленным одним байтом (DNP), который обозначает количество NP, удаленных между пакетом и следующим пакетом, к верхней части каждого пакета в потоке с удаленными NP по каналу ch#n.

В позиции С на фиг. 6 показаны потоки с удаленными NP по каналам ch#1 и ch#2, предоставленными из разделенных потоков по каналам ch#1 и ch#2 в позиции В на фиг. 6, соответственно.

Каждый из потоков с удаленными NP каналов ch#1 и ch#2 представляет собой поток, полученный путем добавления ISCR в конце каждого пакета в разделенных потоках по каналам ch#1 и ch#2 в позиции В на фиг. 6, путем удаления NP вместе с ISCR, добавленными к NP, и путем добавления DNP к верхней части каждого пакета (каждого пакета, оставшегося после удаления NP).

Например, NP, удаленные модулем 32n удаления NP, отсутствуют (ноль) между пакетами #0 и #1 в разделенном потоке по каналу ch#1. Таким образом, DNP в верхней части пакета #0 равен нулю.

Например, существуют пять NP, удаленных модулем 32n удаления NP, между пакетами #4 и #10 разделенного потока по каналу ch#1. Таким образом, количество DNP в верхней части пакета #4 равно пяти.

В позиции D на фиг. 6 показан пример передаваемого потока после FEC по каналу ch#2, который модуль 332 FEC в устройстве 11 передачи (фиг. 2) предоставляет из потока с удаленными NP по каналу ch#2 в позиции С на фиг. 6.

Переданный поток после FEC по каналу ch#2 представляет собой поток в фрейме ВВ, полученный путем использования одного или больше пакетов (включая в себя ISCR и DNP, добавленные к каждому из пакетов) в потоке с удаленными NP по каналу ch#2 в позиции С на фиг. 6, как поле данных (полезная нагрузка) и добавления заголовка ВВ к полю данных. В позиции D на фиг. 6 пакеты от #5 до #9 размещены в поле данных фрейма ВВ.

Следует отметить, что сигналы, передаваемые в полосе (или заполнение), добавляют в конце фрейма ВВ, если необходимо. Однако иллюстрация передачи сигналов в полосе не представлена на фиг. 6.

В позиции Е на фиг. 6 показан пример принятого потока после FEC по каналу ch#2, передаваемому из модуля 622 FEC в модуль 632 вставки NP в устройстве 12 приема (фиг. 4).

Как описано со ссылкой на фиг. 4, модуль 622 FEC восстанавливает поток с удаленными NP в формате фрейма ВВ, предоставляемом модулем 332 FEC на фиг. 2, и предоставляет восстановленный поток, как принятый поток после FEC, по каналу ch#2 в модуль 632 вставки NP.

Таким образом, принятый поток после FEC по каналу ch#2 идентичен потоку с удаленными NP по каналу ch#2 в формате фрейма ВВ, а именно, переданному потоку после FEC по каналу ch#2, показанному в позиции D на фиг. 6.

В позиции F на фиг. 6 показан пример потока со вставленными NP по каналу ch#2, предоставляемого из модуля 632 вставки NP в модуль 52 слияния в устройстве 12 приема (фиг. 4).

Поток со вставленными NP по каналу ch#2 в позиции F на фиг. 6 представляет собой поток, полученный путем вставки NP такое количество раз, каково "число, обозначенное DNP, включенным в принятый поток после FEC по каналу ch#2, в пакеты (последовательность), включенные в фрейм ВВ принятого потока после FEC по каналу ch#2 в позиции Е на фиг. 6.

Пять NP вставляют перед пакетом #5, который находится на вершине фрейма ВВ принимаемого потока после FEC по каналу ch#2 в позиции Е на фиг. 6 в потоке со вставленными NP по каналу ch#2 в позиции F на фиг. 6. DNP, который обозначает вставку пяти NP, добавляют в верхней части последнего пакета в фрейм ВВ (не представлен) непосредственно перед фреймом ВВ принимаемого потока после FEC по каналу ch#2, который представлен в позиции Е на фиг. 6.

DNP, включенный в принимаемый поток после FEC по каналу ch#2 в позиции Е на фиг. 6 удаляют, когда модуль 632 вставки NP изменяет принимаемый поток после FEC по каналу ch#2 в позиции Е на фиг. 6 на поток со вставленными NP по каналу ch#2 в позиции F на фиг. 6.

Следует отметить, что поток со вставленным NP по каналу ch#2 в позиции F на фиг. 6 представляет собой поток, получаемый путем восстановления синхронизированного потока по каналу ch#2, предоставляемому из модуля 31n синхронизации в модуль 32 удаления NP на фиг. 2, как описано со ссылкой на фиг. 4, и, таким образом, ISCR добавлены в конце каждого пакета в потоке со вставленными NP по каналу ch#2 в позиции F на фиг. 6. Однако иллюстрация ISCR не представлена в позиции F на фиг. 6.

В частности, поток с удаленными NP по каналу ch#n (n=1, или 2 на фиг. 6) в позиции С на фиг. 6 представляет собой поток, получаемый путем добавления ISCR в конце каждого пакета в разделенных потоках каналов ch#n в позиции В на фиг. 6, путем удаления NP вместе с ISCR, добавленными к NP, и путем добавления DNP к вершине каждого пакета.

Когда модуль 32n удаления NP в устройстве 11 передачи удаляет NP из синхронизированного потока по каналу ch#n и также удаляет ISCR, добавленные к NP, как описано выше, в модуле 63n вставки NP в устройстве 12 приема трудно восстановить синхронизированный поток по каналу ch#n, предоставляемый модулем 31n синхронизации на фиг. 2, как поток со вставленными NP по каналу ch#n.

Другими словами, когда ISCR добавляют в конце каждого пакета, в синхронизированном потоке по каналу ch#n, предоставляемому модулем 31n синхронизации в устройстве 11 передачи, и модуль 32n удаления NP удаляет ISCR, добавленные к NP вместе с NP из синхронизированного потока по каналу ch#n, модуль 63n вставки NP в устройстве 12 приема может восстанавливать NP, удаленные модулем 32'n удаления NP путем вставки NP в соответствии с DNP; однако, в модуле 63n вставки NP трудно восстанавливать ISCR, удаленные вместе с NP модулем 32n удаления NP.

В качестве способа для восстановления ISCR, удаленных вместе с NP модулем 32n удаления NP, существует, например, способ, в котором модуль 63n вставки NP восстанавливает ISCR, добавленный к NP для вставки, путем оценки ISCR из ISCR, добавленных в пакеты непосредственно перед и после NP, предназначенных для вставки модулем 63n вставки NP, например, с интерполяцией.

Однако в способе не обязательно точно восстанавливают ISCR, удаленный вместе с NP модулем 32n удаления NP.

Учитывая представленное выше, когда модуль 32n удаления NP в устройстве 11 передачи удаляет NP из синхронизированного потока по каналу ch#n, модуль 32n удаления NP может сохранять ISCR, добавленные к NP, без удаления ISCR:

Это позволяет модулю 63n вставки NP в устройстве 12 приема точно восстанавливать синхронизированный поток по каналу ch#n, предоставляемый модулем 31n синхронизации на фиг. 2, а именно, поток, полученный путем добавления ISCR, который добавил модуль 31n синхронизации на фиг. 2 к каждому пакету в разделенном потоке по каналу ch#n, как поток со вставленным NP по каналу ch#n.

Как описано выше, на фиг. 7 показана схема примерного потока, который обрабатывает система передачи на фиг. 1, когда модуль 32n удаления NP в устройстве 11 передачи удаляет NP из синхронизированного потока по каналу ch#n, и оставляет ISCR, добавленные к NP, без удаления ISCR.

Следует отметить, что на фиг. 7 количество N каналов равно двум, аналогично фиг. 6.

Позиции А и В, и D-F на фиг. 7 аналогичны позициям А и В, и D-F на фиг. 6, соответственно. Таким образом, описания их будут исключены.

В позиции С на фиг. 7 представлены потоки с удаленными NP для каналов ch#1 и ch#2, полученные из разделенных потоков каналов ch#1 и ch#2 в позиции В на фиг. 7, соответственно.

В позиции С на фиг. 7, поток с удаленными NP по каналу ch#1 представляет собой поток, полученный путем добавления ISCR к концу каждого пакета, в разделенном потоке по каналу ch#1 в позиции В на фиг. 7, путем удаления NP при сохранении ISCR, добавленных к NP, и добавления DNP к верхней части каждого пакета.

После того, как NP будут удалены, в то время как ISCR, добавленные к NP, сохранены, как описано выше, ISCR, добавленные к удаленным NP, существуют без добавления к концу пакетов в потоке с удаленными NP по каналу ch#1 в позиции С на фиг. 7.

Восстановление синхронизированного потока по каналу ch#n с помощью модуля 63n вставки NP

На фиг. 8 показана схема, поясняющая, что модуль 63n вставки NP в устройстве 12 приема (фиг. 4) восстанавливает синхронизированный поток по каналу ch#n, как поток со вставленными NP по каналу ch#n.

Как описано со ссылкой на фиг. 4, модуль 63n вставки NP соответствующим образом вставляет NP в принимаемый поток после FEC (поток с удаленными NP (в формате фрейма ВВ)), путем предоставления и сохранения принятого потока после FEC по каналу ch#n из модуля 62 FEC в буфер 64n, и затем выводит пакеты в принятом потоке после FEC, сохраненном в буфере 64n или NP. Такая вставка восстанавливает синхронизированный поток по каналу ch#n, как поток со вставленными NP по каналу ch#n.

Другими словами, самый старший пакет среди пакетов, которые записывает (сохраняет) модуль 63n вставки NP в буфер 64n и которые не считывают из буфера 64n в принимаемом потоке после FEC по каналу ch#n из модуля 62n FEC, представляет собой значимый пакет, который должен быть обозначен.

Модуль 63n вставки NP вставляет NP в принятый поток после FEC по каналу ch#n из модуля 62n FEC, выводя NP в таком же количестве, которое равно числу, обозначенному DNP, добавленному к значимому пакету, и затем выводит значимый пакет и восстанавливает синхронизированный поток по каналу ch#n, как поток со вставленными NP по каналу ch#n.

Таким образом, после того, как пакет в принятом потоке после FEC по каналу ch#n, записанному в буфер 64n, будет определен как значимый пакет, необходимо сохранять пакет в буфере 64n до тех пор, пока не будет закончен вывод NP в таком количестве, которое представлено числом, обозначенным DNP, добавленным к значимому пакету.

Вводимые данные, (предоставляемые) и записываемые в буфер 64n, называются входными данными буфера, и данные, считываемые и выводимые из буфера 64n, называются выходными данными буфера.

На фиг. 8 иллюстрируются примерные временные вариации общего количества входных данных буфера и общего количества выходных данных буфера.

Входные данные буфера представляют собой принимаемый поток после FEC по каналу ch#n. Для упрощения описания, предполагается, что входные данные буфера представляют собой ввод с постоянной скоростью передачи данных.

В этом примере, общий объем данных входных данных буфера увеличивается с постоянным наклоном, представленным сплошной линией на фиг. 8.

С другой стороны, общее количество данных выходных данных буфера изменяется, в соответствии с пунктирной линией, представленной на фиг. 8, в зависимости от NP, вставленных в принимаемый поток после FEC по каналу ch#n, когда синхронизированный поток по каналу ch#n восстанавливают, как поток со вставленными NP по каналу ch#n.

Другими словами, общее количество выходных данных буфера увеличивается, когда модуль 63n вставки NP выводит пакеты в принимаемом потоке после FEC, сохраненном в буфере 64n, как входные данные буфера, поскольку пакеты в принимаемом потоке после FEC считывают из буфера 64n, в то время как модуль 63n вставки NP выводит пакеты в принимаемом потоке после FEC, сохраненном в буфере 64n, и NP.

Однако общее количество выходных данных буфера не изменяется (увеличивается), когда модуль 63n вставки NP выводит NP, поскольку пакеты в принимаемом потоке после FEC не считывают из буфера 64n.

Когда модуль 63n вставки NP последовательно вставляет множество NP в синхронизированный поток по каналу ch#n, восстановленному как поток со вставленными по NP по каналу ch#n, а именно, в разделенный поток по каналу ch#n, предоставляемый разделителем 21 в устройстве 11 передачи (фиг. 2), общее количество выходных данных буфера не изменяется. Это связано с тем, что пакеты в принимаемом потоке после FEC не считывают из буфера 64n, когда модуль 63n вставки NP продолжает выводить NP в период, в который множество NP расположено последовательно.

Общее количество данных входных данных буфера увеличивается с постоянным наклоном, как описано выше. Таким образом, когда общее количество выходных данных буфера не меняется, разница между общим количеством входных данных буфера и общим количеством выходных данных буфера (ниже называется также общей разницей количества) увеличивается.

Общая разница количества представляет собой количество данных для данных, сохраненных в буфере 64n. Таким образом, максимальная общая разница количества представляет собой объем буфера, который должен иметь буфер 64n.

Общая разница количества увеличивается в период, в который NP расположены последовательно в разделенном потоке по каналу ch#n, предоставляемому разделителем 21, как описано выше, поскольку общее количество выходных данных буфера не изменяется.

Таким образом, когда NP могут быть свободно вставлены, без предписания (определения) способа вставки NP, в котором разделитель 21 вставляет NP в разделенный поток по каналу ch#n (например, отношение NP, которые должны быть вставлены в каждый канал, или порядок, в котором NP вставляют в каждый канал), буфер 64n в устройстве 12 приема должен иметь большой объем буфера. Это может увеличить стоимость устройства 12 приема.

Когда объем буфера в буфере 64n, в устройстве 12 приема меньше, чем общая разность количества, это приводит к переполнению буфера 64n. Это может привести к ошибке в модуле 63n вставки NP, с невозможностью правильной обработки принимаемого потока после FEC по каналу ch#n из модуля 62n FEC (для восстановления синхронизированного потока по каналу ch#n, в виде потока со вставленными NP по каналу ch#n).

Учитывая представленное выше, способ вставки NP, описанный для системы передачи на фиг. 1, состоит в том, что разделитель 21 разделяет входной поток на потоки разделения каналов от ch#1 по ch#N, включающие в себя пакеты входного потока с заданной плотностью.

В соответствии со способом вставки NP, NP сглаживают и вставляют в разделенные потоки каналов от ch#1 до ch#N таким образом, что NP не вставляют только в части потоков.

Это позволяет устранить необходимость в большом объеме буфера для буфера 64n в устройстве 12 приема, как описано выше, вследствие того факта, что множество NP последовательно вставляют в разделенный поток канала ch#n.

Скорость передачи данных потока с удаленными NP по каналу ch#n, который подают в модуль 33n FEC, в устройстве 11 передачи, должна представлять собой заданную скорость данных, которая ниже, чем или равна скорости обработки (скорость FEC) модуля 33n FEC. Это связано с тем, что, когда скорость передачи данных потока с удаленными NP по каналу ch#n превышает скорость обработки модуля 33n FEC, для модуля 33n FEC трудно правильно обрабатывать поток с удаленными NP по каналу ch#n.

Скорость передачи данных потока с удаленными NP по каналу ch#n, который подают в модуль 33n FEC, в устройстве 11 передачи, представляет собой пропускную способность поля данных во фрейме ВВ, генерируемом модулем 33n FEC (данные, из которых был удален заголовок ВВ в фрейме ВВ). Скорость передачи данных определяют в соответствии со скоростью передачи символов, схемой модуляции для квадратурной модуляции, выполняемой модулем 34n MOD, кодом коррекции ошибок, используемым модулем 33n FEC, или включенным/выключенным пилотным сигналом для модулированного сигнала, предоставляемого модулем 34n MOD.

Если предположить, что скорость передачи данных потока с удаленными NP по каналу ch#n, предоставляемому в модуль 33n FEC в устройстве 11 передачи ранее была определена, как заданная скорость передачи данных, которая ниже чем или равна скорости обработки модуля 33n FEC, способ вставки NP можно описать таким образом, что отношение NP, которые разделитель 21 вставляет в каналы от ch#1 до ch#N, является идентичными отношениям обратных величин заданных скоростей передачи данных в потоке с удаленными NP для каналов от ch#1 до ch#N.

В соответствии с предписанным способом вставки NP, можно предотвратить возникновение ошибки в модуле 33n FEC для соответствующей обработки потока с удаленными NP по каналу ch#n, с учетом того факта, что множество NP вставлены в канал ch#n', и это уменьшает количество NP, вставляемых в другой канал ch#n, и, таким образом, скорость передачи данных потока с удаленными NP по каналу ch#n становится выше, чем скорость обработки модуля 33n FEC по каналу ch#n.

Другими словами, когда способ вставки NP описан таким образом, что отношение NP, которые разделитель 21 вставляет в каналы от ch#1 до ch#N, является идентичным отношениям обратных величин заданных скоростей передачи данных потока с удаленными NP по каналам от ch#1 до ch#N, скорости передачи данных потоков с удаленными NP по каналам от ch#1 до ch#N становятся скоростями передачи данных, которые ниже чем или равны скоростям обработки модулей 33n FEC, заранее определенным для каналов от ch#1 до ch#N, соответственно. Это обеспечивает для модуля 33n FEC возможность правильной обработки потока с удаленными NP по каналу ch#n.

На фиг. 9 показана схема примерного потока, который обрабатывает система передачи на фиг. 1, когда используется способ вставки NP, как описано выше.

Следует отметить, что количество N каналов равно двум на фиг. 9, аналогично фиг. 6.

Кроме того, иллюстрация ISCR исключена на фиг. 9.

В позиции А на фиг. 9 показан пример входного потока, подаваемого в разделитель 21 в устройстве 11 передачи (фиг. 2).

Позиция А на фиг. 9 аналогична позиции А на фиг. 6.

В позиции В на фиг. 9 показаны примеры разделенных потоков, подаваемых из разделителя 21 в устройстве 11 передачи (фиг. 2) в модуль 31n синхронизации через буфер 22n.

В соответствии со способом вставки NP, разделитель 21 разделяет входной поток на разделенные потоки двух каналов ch#1 и ch#2 таким образом, чтобы пакеты во входном потоке включены с заданной плотностью, путем распределения пакетов TS во входном потоке в позиции А на фиг. 9 на один из двух каналов от ch#1 и ch#2, и распределения NP по другим каналам.

В позиции В на фиг. 9 отношения обратных величин заданных скоростей передачи данных потоков с удаленными NP по каналам ch#1 и ch#2 составляет, например, 1 к 1.

Таким образом, разделитель 21 разделяет входной поток на разделенные потоки каналов ch#1 и ch#2 таким образом, что отношения NP, вставленных в каналы ch#1 и ch#2, составляют 1 к 1.

Другими словами, в позиции В на фиг. 9, разделитель 21 распределяет пакет #0 TS во входном потоке на канал ch#1, и распределяет NP в канал ch#2. После этого разделитель 21 распределяет пакет #2 TS во входном потоке в канал ch#2, и распределяет NP в канал ch#1. Разделитель 21 распределяет пакеты TS во входном потоке поочередно в каналы ch#1 и ch#2, и поочередно распределяет NP в каналы ch#1 и ch#2. Это разделяет входной поток на разделенные потоки каналов ch#1 и ch#2.

В результате, пакеты входного потока включены в оба разделенные потоки по каналам ch#1 и ch#2 с постоянной плотностью (плотность, при которой 0,5 пакета входного потока включено в пакет разделенного потока в позиции В на фиг. 9).

В позиции С на фиг. 9 показаны примеры потоков с удаленными NP, подаваемыми из модуля 32n удаления NP в модуль 33n FEC в устройстве 11 передачи (фиг. 2).

Модуль 31n синхронизации изменяет разделенный поток канала ch#n, подаваемого разделителем 21, на синхронизированный поток по каналу ch#n.

Модуль 32n удаления NP изменяет синхронизированный поток по каналу ch#n на поток с удаленными NP по каналу ch#n, путем удаления NP из синхронизированного потока и вставки DNP.

В позиции С на фиг. 9 представлены потоки с удаленными NP по каналам ch#1 и ch#2, получаемые из разделенных потоков по каналам ch#1 и ch#2 в позиции В на фиг. 9, соответственно.

В позиции D на фиг. 9 показан пример передаваемого потока после FEC по каналу ch#2, измененного из потока с удаленными NP по каналу ch#2 в позиции С на фиг. 9 модулем 332 FEC в устройстве 11 передачи (фиг. 2).

Передаваемый поток после FEC по каналу ch#2 представляет собой поток фрейма ВВ, в котором заголовок ВВ добавлен к одному или больше пакетам потока с удаленными NP по каналу ch#2 в позиции С на фиг. 9.

В позиции Е на фиг. 9 представлен пример принимаемого потока после FEC по каналу ch#2, предоставляемому из модуля 622 FEC в модуль 632 вставки NP в устройстве 12 приема (фиг. 4).

Как описано со ссылкой на фиг. 4, модуль 622 FEC восстанавливает поток с удаленными NP в формате фрейма ВВ, предоставляемого модулем 332 FEC на фиг. 2, и предоставляет восстановленный поток, как принятый поток после FEC, по каналу ch#2 в модуль 632 вставки NP.

Таким образом, принимаемый поток после FEC по каналу ch#2 идентичен потоку с удаленными NP в формате фрейма ВВ по каналу ch#2, а именно, передаваемый поток после FEC на каналу ch#2 в позиции D на фиг. 9.

В позиции F на фиг. 9 показан пример потока со вставленными NP по каналу ch#2, предоставляемого из модуля 632 вставки NP в модуль 52 слияния в устройстве 12 приема (фиг. 4).

Поток со вставленными NP по каналу ch#2 в позиции F на фиг. 9 представляет собой поток, получаемый путем вставки NP такое количество раз, которое соответствует номеру, обозначенному DNP, включенному в принимаемый поток после FEC по каналу ch#2 в пакеты (последовательность), включенные в фрейм ВВ принимаемого потока после FEC по каналу ch#2 в позиции Е на фиг. 9, и удаления DNP.

На фиг. 10 показана схема примерного изменения по времени общего количества входных данных буфера и общего количества выходных данных буфера, когда способ вставки NP, описанный выше, используется в разделителе 21.

Аналогично фиг. 8 на фиг. 10 предполагается, что входные данные буфера, которые представляют собой принимаемый поток после FEC по каналу ch#n, вводят с постоянной скоростью передачи данных. В этом примере общее количество данных входных данных буфера увеличивается с постоянным наклоном, представленным сплошной линией, показанной на фиг. 10.

С другой стороны, используя способ вставки NP входной поток разделяют на разделенные потоки по каналам от ch#1 по ch#N, включающим в себя пакеты входного потока с постоянной плотностью.

Таким образом, пакеты входного потока присутствуют с постоянной плотностью в синхронизированном потоке по каналу ch#n, который модуль 63n вставки NP в устройстве 12 приема восстанавливает, как поток со вставленным NP по каналу ch#n из разделенных потоков канала ch#n.

Таким образом, когда модуль 63n вставки NP восстанавливает синхронизированный поток по каналу ch#n, как поток со вставленными NP по каналу ch#n, пакеты, сохраненные в буфере 64n, считывают через средние интервалы. Это увеличивает общее количество выходных данных буфера за средние интервалы, как представлено пунктирной линией на фиг. 10.

Это позволяет устранить потребность в буфере большого объема, в качестве буфера 64n, ввиду того факта, что модуль 63n вставки NP последовательно выводит NP и пакеты, не считанные из буфера 64n, когда модуль 63n вставки NP восстанавливает синхронизированный поток по каналу ch#n, как поток со вставленными NP по каналу ch#n, и это увеличивает общую разность количества между общим количеством данных входных данных буфера и общим количеством данных выходных данных буфера.

Следует отметить, что на фиг. 10 иллюстрируется общее количество выходных данных буфера, когда разделитель 21 разделяет входной поток на разделенные потоки по каналам ch#1 и ch#2, поочередно включающие в себя NP и пакеты входного потока, один за другим, как представлено в позиции В на фиг. 9.

Пример конфигурации разделителя 21

На фиг. 11 показана блок-схема первой примерной конфигурации разделителя 21, который разделяет входной поток на разделенные потоки в соответствии со способом вставки NP, описанным выше.

Другими словами, на фиг. 11 иллюстрируется пример конфигурации разделителя 21, когда разделитель 21 разделяет входной поток на разделенные потоки из двух каналов ch#1 и ch#2.

На фиг. 11 разделитель 21 включает в себя буфер 81, модуль 82 распределения пакета и модуль 83 выбора канала.

Пакеты во входном потоке подают в буфер 81. В буфере 81 последовательно сохраняют предоставленные пакеты входного потока.

Модуль 83 выбора канала передает сигнал выбора sel, используемый для выбора канала, в который распределяют пакет в модуле 82 распределения пакетов.

Модуль 82 распределения пакетов считывает самый старый пакет среди пакетов, сохраненных в буфере 81, как значимый пакет, который следует обозначить. Кроме того, модуль 82 распределения пакета выбирает канал, в который должен быть распределен значимый пакет, как канал распределения, в соответствии с сигналом sel выбора из модуля 83 выбора канала, и распределяет (выводит) значимый пакет в канал распределения.

На фиг. 11 модуль 82 распределения пакета выбирает один из двух каналов ch#1 и ch#2, в качестве канала распределения, и распределяет значимый пакет в канал распределения.

Модуль 82 распределения пакета распределяет (выводит) NP в канал, который был не выбран, как канал распределения.

Модуль 83 выбора канала включает в себя схему 91 защелки, арифметические модули 92 и 93, селектор 94 и схему 95 сравнения.

Модуль 83 выбора канала генерирует сигнал sel выбора, используемый для выбора канала, в который распределяется значимый пакет (канал распределения) в соответствии с определенной скоростью передачи данных потока с удаленными NP по каналу ch#n (ниже также называется просто скоростью передачи данных по каналу ch#n), и предоставляет сгенерированный сигнал в модуль 82 распределения пакета.

Другими словами, в этом примере, скорости передачи данных каналов ch#1 и ch#2 обозначаются, как r1 и r2, соответственно.

Схема 91 защелки фиксирует суммарное значение, передаваемое в селектор 94 в момент времени, в синхронизации с пакетами входного потока, на основе предположения, что исходное значение равно нулю, и представляет значение sum в арифметические модули 92 и 93, и в схему 95 сравнения в модуле 83 выбора канала.

Арифметический модуль 92 добавляет значение sum из схемы 91 защелки к скорости r1 передачи данных по каналу ch#1, и предоставляет полученное в результате суммарное значение, как новый кандидат значений sum=sum+r1 в селектор 94.

Арифметический модуль 93 добавляет значение sum из схемы 91 защелки к скорости r2 передачи данных по каналу ch#2, и предоставляет полученное в результате добавленное значение, как новый кандидат значения sum=sum+r2 в селектор 94.

Кроме добавленных значений, получаемых из арифметических модулей 92 и 93, как описано выше, сигнал выбора sel подают из схемы 95 сравнения в селектор 94.

В этом примере сигнал sel выбора принимает значение ноль или единица. Сигнал sel выбора, имеющий значение ноль, обозначает, что канал ch#2 выбирают, как канал распределения. Сигнал sel выбора, имеющий значение один, обозначает, что канал ch#1 выбран, как канал распределения.

Селектор 94 выбирает добавленное значение из арифметического модуля 92 или добавленное значение из арифметического модуля 93, в соответствии с сигналом sel выбора из схемы 95 сравнения, и предоставляет выбранное значение в схему 91 защелки.

Схема 95 сравнения сравнивает значение sum из схемы 91 защелки с суммарным значением r1+r2 скоростей передачи данных каналов ch#1 и ch#2. Затем схема 95 сравнения выводит сигнал sel выбора, имеющий значение один, когда значение sum больше чем или равно суммарному значению r1+r2. Схема 95 сравнения выводит сигнал sel выбора, имеющий значение ноль, когда значение sum меньше, чем суммарное значение r1+r2.

Сигнал sel выбора, выводимый из схемы 95 сравнения, предоставляют в модуль 82 распределения пакета и в селектор 94.

В разделителе 21, имеющем конфигурацию, описанную выше, модуль 83 выбора канала генерирует сигнал выбора, используемый для выбора канала, который распределяет значимый пакет (канал распределения) в соответствии со скоростями r1 и r2 передачи данных каналов ch#1 и ch#2 таким образом, что отношения NP, вставленные в каналы ch#1 и ch#2, являются идентичными отношениям обратных величин скоростей r1 и r2 передачи данных по каналам ch#1 и ch#2. Затем модуль 83 выбора канала предоставляет сгенерированный сигнал в модуль 82 распределения пакета.

Другими словами, модуль 83 выбора канала генерирует сигнал sel выбора таким образом, что канал ch#1 выбирают, как канал распределения каждый (r1+r2)/r1 пакет, и канал ch#2 выбирают, как канал распределения каждый (r1+r2)/r2 пакет.

Модуль 82 распределения пакета выбирает один из каналов ch#1 и ch#2, как канал распределения, в соответствии с сигналом выбора sel из модуля 83 выбора канала. Модуль 82 распределения пакетов распределяет (выводит) значимый пакет, сохраненный в буфере 81, в выбранный канал распределения и распределяет (выводит) NP в другой канал.

На фиг. 12 показана пояснительная схема операции разделителя 21, представленного на фиг. 11, когда скорости r1 и r2 передачи данных равны единице и двум, соответственно.

Когда скорости r1 и r2 передачи данных равны единице и двум, соответственно, значения sum изменяется, как представлено на фиг. 12. Когда значение sum больше чем или равно r1+r2=3, сигнал sel выбора равен единице, и канал ch#1 выбирают, как канал распределения.

Когда значение sum меньше чем r1+r2=3, сигнал sel выбора равен нулю, и канал ch#2 выбирают, как канал распределения.

На фиг. 12 отношения NP, вставленных в каналы ch#1 и ch#2 (отношения коэффициентов того, что каналы ch#1 и ch#2 не будут выбраны, как канал распределения), идентичны отношению 1/r1 : 1/r2 = 1:1/2 = 2:1 для обратных величин скоростей r1 и r2 передачи данных каналов ch#1 и ch#2.

На фиг. 12 сигнал sel выбора генерируют таким образом, что канал ch#1 выбирают, как канал распределения каждые (r1+r2)/r1 = три пакета (пакет в трех пакетах). Канал ch#2 выбирают, как канал распределения каждые (r1+r2)/r2=1,5 пакета, а именно, каждый второй пакет или два пакета.

На фиг. 13 показана блок-схема второй примерной конфигурации разделителя 21, который разделяет входной поток на разделенные потоки в соответствии со способом вставки NP, описанным выше.

Другими словами, на фиг. 13 иллюстрируется пример конфигурации разделителя 21, когда разделитель 21 разделяет входной поток на разделенные потоки из трех каналов ch#1 - ch#3.

Следует отметить, что компоненты на фиг. 13, соответствующие показанным на фиг. 11, представлены с теми же номерами ссылочных позиций. Их описание будет, соответственно, исключено ниже.

Аналогично разделителю 21 на фиг. 11, разделитель 21 на фиг. 13 включает в себя буфер 81 и модуль 82 распределения пакета.

Однако, в отличие от разделителя 21 на фиг. 11, разделитель 21 на фиг. 13 включает в себя модуль 111 выбора канала вместо модуля 83 выбора канала.

Аналогично модулю 83 выбора канала на фиг. 11, модуль 111 выбора канала генерирует сигнал sel выбора, используемый для выбора канала, в который распределяют значимый пакет, в соответствии со скоростями передачи данных каналов от ch#1 до ch#3, и предоставляет сгенерированный сигнал в модуль 82 распределения пакета.

Однако модуль 111 выбора канала предоставляет флаг выбора flagn, который обозначает, был ли канал ch#n (n=1, 2 или 3 на фиг. 13) выбран, как канал распределения, как сигнал sel выбора в модуль 82 распределения пакета.

Флаг flagn выбора принимает значение ноль или единица. Флаг flagn выбора, имеющий значение единица, обозначает, что канал ch#n (может быть) выбран, как канал распределения. Флаг flagn выбора, имеющий значение ноль, обозначает, что канал ch#n не выбран, как канал распределения.

В этом примере, модуль 82 распределения пакета на фиг. 13, который принимает флаг flagn выбора, описанный выше, как сигнал выбора sel, выбирает канал ch#n из каналов от ch#1 до ch#3, как канал распределения, когда флаг flagn выбора, предоставляемый как сигнал sel выбора, равен единице, и предоставляет значимый пакет в канал ch#n, который представляет собой канал распределения.

Модуль 82 распределения пакета также распределяет NP во все каналы, которые не были выбраны, как канал распределения среди каналов от ch#1 до ch#3.

Модуль 83 выбора канала включает в себя счетчики от 1211 до 1213 и модули от 1221 до 1223 вывода выбранного флага для каналов от ch#1 до ch#3, и модуль 123 управления выбором.

В этом примере скорости передачи данных в каналах ch#1, ch#2 и ch#3 обозначены, как r1, r2 и r3, соответственно.

Счетчик 1211 подсчитывает величину sum1 подсчета в момент времени синхронизации с пакетом во входном потоке, и предоставляет величину sum1 подсчета в модуль 1221 вывода выбранного флага.

Другими словами, счетчик 1211 обновляет значение sum1 подсчета в соответствии с выражением sum1=sum1-r2-r3, когда значение sum1 больше или равно значению r1+r2+r3, и предоставляет обновленное значение в модуль 1221 вывода выбранного флага.

В качестве альтернативы, счетчик 1211 обновляет величину sum1 подсчета, в соответствии с выражением sum1=sum1+r1, когда значение sum1 меньше, чем значение r1+r2+r3, и предоставляет обновленное значение в модуль 1221 вывода выбранного флага.

Счетчик 1212 подсчитывает значение sum2 подсчета в момент времени синхронизации с пакетом во входном потоке, и предоставляет значение sum2 подсчета в модуль 1222 вывода выбранного флага.

Другими словами, счетчик 1212 обновляет величину sum2 подсчета в соответствии с выражением sum2=sum2-r1-r3, когда значение sum2 больше или равно значению r1+r2+r3, и предоставляет обновленное значение в модуль 1222 вывода выбранного флага.

В качестве альтернативы, счетчик 1212 обновляет значение sum2 подсчета, в соответствии с выражением sum2=sum2+r2, когда значение sum2 меньше, чем значение r1+r2+r3, и предоставляет обновленное значение в модуль 1222 вывода выбранного флага.

Счетчик 1213 подсчитывает значение sum3 подсчета в момент времени синхронизации с пакетом во входном потоке, и предоставляет значение sum3 подсчета в модуль 1223 вывода выбранного флага.

Другими словами, счетчик 1213 обновляет значение sum3 подсчета в соответствии с выражением sum3=sum3-r1-r2, когда значение sum3 больше, чем или равно значению r1+r2+r3, и предоставляет обновленное значение в модуль 1223 вывода выбранного флага.

В качестве альтернативы, счетчик 1213 обновляет значение sum3 подсчета, в соответствии с выражением sum3=sum3+r3, когда значение sum3 меньше, чем значение r1+r2+r3, и предоставляет обновленное значение в модуль 1223 вывода выбранного флага.

Модуль 122n вывода выбранного флага выводит флаг flagn выбора, имеющий значение ноль, как принятое по умолчанию значение, в модуль 123 управления выбором.

Когда значение sumn подсчета, предоставляемое из счетчика 121n, больше или равно значению r1+r2+r3, модуль 122n вывода выбранного флага выводит флаг flagn выбора, имеющий значение единица, в модуль 123 управления выбором.

Модуль 123 управления выбором выбирает один из флагов flagn выбора, имеющий значение единица, среди флагов от flag1 до flag3 выбора из модуля от 1221 до 1223 вывода выбранного флага в качестве сигнала sel выбора и предоставляет выбранный флаг в модуль 82 распределения пакета.

Модуль Т23 управления выбором управляет модулем 122n вывода выбранного флага для сброса значения флагов flagn выбора, выбранных как сигнал sel выбора, в ноль.

В этом примере, флаг flag1 выбора выбран, как сигнал sel выбора, когда флаг flag1 выбора равен единице, на основе предположения того, что модуль 123 управления выбором выбирает один из флагов выбора flag1, flag2 и flag3 в качестве сигнала sel выбора, например, в порядке возрастания в качестве порядка приоритета.

Когда флаг flag1 выбора равен нулю, и флаг flag2 выбора равен единице, флаг flag2 выбора выбирают как сигнал sel выбора.

Когда оба флага flag1 и flag2 равны нулю, и флаг flag3 выбора равен единице, флаг flag3 выбора выбирают, как сигнал sel выбора.

В разделителе 21, имеющем конфигурацию, описанную выше, модуль 111 выбора канала генерирует сигнал sel выбора, используемый для выбора канала, который распределяет значимый пакет, в соответствии со скоростями r1 - r3 передачи данных каналов от ch#1 по ch#3 таким образом, что отношения NP, вставленных в каналы от ch#1 до ch#3, являются идентичными отношениям обратных величин скорости от r1 до r3 передачи данных, по каналам от ch#1 до ch#3. Затем модуль 83 выбора канала предоставляет сгенерированный сигнал в модуль 82 распределения пакета.

Другими словами, модуль 111 выбора канала генерирует сигнал sel выбора таким образом, что канал ch#1 выбирают, как канал распределения, каждые (r1+r2+r3)/r1 пакеты, канал ch#2 выбирают, как канал распределения каждые (r1+r2+r3)/r2 пакеты, и канал ch#3 выбирают, как канал распределения каждые (r1+r2+r3)/r3 пакеты.

Модуль 82 распределения пакета выбирает каналы ch#n из каналов от ch#1 до ch#3, как канал распределения, в соответствии сигналом sel выбора, из модуля 111 выбора канала. Модуль 82 распределения пакета распределяет (выводит) значимый пакет, сохраненный в буфере 81, в выбранный канал распределения, и распределяет (выводит) NP в другие два канала.

Конфигурация, представленная на фиг. 13, может использоваться для разделителя 21, который разделяет входной поток на разделенные потоки по двум каналам, или разделяет входной поток на разделенные потоки по четырем или больше каналам.

Обработка, когда входной поток включает в себя NP

На фиг. 14 показана пояснительная схема примерного способа, когда устройство 11 передачи обрабатывает входной поток, включающий в себя NP.

Другими словами, на фиг. 14 иллюстрируются примерные входные потоки, разделенные потоки и потоки с удаленными NP.

Следует отметить, что количество N каналов равно двум, и иллюстрация ISCR не представлена на фиг. 14.

В позиции А на фиг. 14 показан примерный входной поток, включающий в себя NP.

Следует отметить, что NP, включенный во входной поток, обозначен как NP' на фиг. 14, чтобы различать NP от NP, вставленных в разделенные потоки в разделителе 21.

В позиции В на фиг. 14 показан пример потоков, разделенных на два канала от ch#1 до ch#2, которые разделитель 21 генерирует из входного потока в позиции А на фиг. 14.

Разделенные потоки включают в себя NP, вставленные в разделитель 21, и NP' (первоначально), включенные во входной поток.

В позиции С на фиг. 14 показан пример потока с удаленными NP по двум каналам ch#1 и ch#2, предоставляемым из потоков, разделенных по двум каналам от ch#1 и ch#2, в позиции В на фиг. 14, в модуле 32n удаления NP.

Модуль 32n удаления NP генерирует потоки с удаленными NP путем удаления NP из (синхронизированного потока, который модуль 31n синхронизации генерирует из) разделенных потоков, как описано выше.

Как представлено в позиции В на фиг. 14, разделенные потоки иногда включают в себя NP, вставленные, когда разделитель 21 генерирует разделенные потоки, и NP, первоначально включенные во входной поток в данном примере.

Когда разделенные потоки включают в себя NP и NP' и модуль 32n удаления NP удаляет NP', в дополнение к NP, модуль 63n вставки NP в устройстве 12 приема должен вставлять также NP' в дополнение к NP, когда модуль 63n вставки NP генерирует поток со вставленными NP.

Когда модуль 63n вставки NP последовательно вставляет множество NP (NP'), буфер 64n должен иметь большой объем буфера, поскольку пакеты не считывают из буфера 64n, как описано со ссылкой на фиг. 8.

Учитывая представленное выше, модуль 32n удаления NP в устройстве 11 передачи удаляет только NP, вставленные, когда разделитель 21 генерирует разделенные потоки, и может удерживать NP', первоначально включенные во входной поток, без удаления NP'.

Сохранение NP', первоначально включенных во входной поток, в том виде, как они есть, без удаления NP', как описано выше, позволяет исключить требование слишком большого объема буфера 64n в устройстве 12 приема.

В потоках с удаленными NP в позиции С на фиг. 14, удаляют только NP, вставленные в разделитель 21, и включенные в разделенные потоки в позиции В на фиг. 14n и NP, первоначально включенные во входной поток, не удаляют, и их оставляют в том виде, как они есть.

На фиг. 15 показана пояснительная схема примерного способа для различения NP, вставленных разделителем 21, от NP', первоначально включенных во входной поток.

Необходимо различать NP, вставленные разделителем 21, от NP', первоначально включенных во входной поток, для того, чтобы обеспечить для модуля 32n удаления NP в устройстве 11 передачи возможность удалять только NP, вставленными в разделителе 21 из (синхронизированного потока, полученного из) разделенных потоков, и сохранения NP', первоначально включенных во входной поток, в том виде, как они есть, без удаления NP.

В качестве способа для различения NP, вставленных в разделитель 21, от NP', первоначально включенных во входной поток, используется способ, в соответствии с которым информация идентификации NULL, которая обозначает, что пакет TS представляет собой пакет с NP, вставленными в разделителе 21, или NP', первоначально включенными во входной поток, включена в пакет TS, который представляет собой NP или NP'.

На фиг. 15 иллюстрируется формат пакета TS.

Заголовок TS пакета TS включает в себя программный PID таким образом, что по программному PID можно различать, является ли пакет TS пакетом NP (NP').

Информация идентификации NULL может, например, представлять собой такую информацию, что единица установлена в старшем значащем бите фиксированного слова 0x47 синхронизации, включенного в заголовок TS (0х обозначает, что последующие значения отображаются в шестнадцатеричной системе счисления), и слово синхронизации представляет собой 0хС7.

В качестве альтернативы, информация идентификации NULL может представлять, например, что часть или вся полезная нагрузка пакета TS (NP или NP') имеет конкретные значения, обозначающие, что пакет TS содержит NP или NP'. Например, строка битов, в которой старший значащий бит равен единице, и другие биты равны нулю, может использоваться, как конкретные значения.

Следует отметить, что информация идентификации NULL может быт такой, что информация идентификации NULL, обозначающая, что пакет TS представляет собой NP, включена только в NP, что информация идентификации NULL, обозначающая, что пакет TS представляет собой NP', включена только в NP', или что информация идентификации NULL, обозначающая, что пакет TS представляет собой NP, включена в NP, и информация идентификации NULL, обозначающая, что пакет TS представляет собой NP', включена в NP'.

Однако, когда информация идентификации NULL, обозначающая, что пакет TS представляет собой NP', включена в NP', необходимо вернуть NP' в состояние перед тем, как информация идентификации NULL была включена в NP', для обработки, которую модуль 32n удаления NP выполняет после этого.

Таким образом, информация идентификации NULL, предпочтительно, представляет, что информация идентификации, обозначающая, что пакет TS содержит NP, включена только в NP.

NP, включающие в себя информацию идентификации NULL, обозначающую, что пакет TS представляет собой NP, не влияет на обработку, которую модуль 32n удаления NP выполняют в последующем, поскольку модуль 32n удаления NP удаляет информацию идентификации NULL (при этом нет необходимости возвращать NP, включающие в себя информацию идентификации NULL, обозначающую, что пакет TS состоит из NP, в состоянии перед тем, как информация идентификации NULL была включена в NP).

Идентификатор размера, обозначающий размер DNP

На фиг. 16 показана пояснительная схема идентификатора размера, обозначающего размер DNP.

Когда модуль 32n удаления NP изменяет поток синхронизации на поток с удаленными NP путем удаления NP из синхронизированного потока, модуль 32n удаления NP добавляет однобайтовый DNP, обозначающий количество NP, удаленных между пакетом и следующим пакетом, к верхней части каждого пакета в потоке с удаленными NP.

Однобайтный DNP может обозначать число от нуля и до 255, как количество NP, удаленных между пакетом и следующим пакетом.

В частности, когда количество N каналов, на которое разделитель 21 разделяет входной поток на разделенные потоки, равно значимому количеству, тогда количество NP, последовательно вставленных в разделенный поток, проявляет тенденцию быть большим числом.

Однако, когда DNP равен одному байту, DNP может обозначать номер только в пределах до 255. Таким образом, модуль 32n удаления NP может удалять только вплоть до 255 NP, если больше, чем 255 NP последовательно включены в синхронизированный поток.

Учитывая представленное выше, можно использовать DNP, имеющий размер больше, чем один байт, например, DNP размером два байта.

Двухбайтный DNP может обозначать число (от нуля) до 65535.

Это позволяет модулю 32n удаления NP удалять вплоть до 65535 последовательных NP.

В частности, DNP добавляют к верхней части каждого пакета в потоке с удаленным NP. Таким образом, когда размер DNP составляет два байта, количество служебных сигналов в потоке с удаленными NP удваивается по сравнению с количеством служебных сигналов, когда размер DNP равен составляет один байт.

Когда количество N каналов, на которое разделитель 21 разделяет входной поток разделенных потоков, является небольшим количеством, количество NP, последовательно вставленных в разделенный поток, проявляет тенденцию быть небольшим числом. Таким образом, модуль 32n удаления NP иногда удаляет NP такое количество раз, которое равно числу, обозначенному только однобайтным DNP, даже если используется двухбайтный DNP (NP, превышающие количество, обозначенное однобайтным DNP, иногда не удаляют).

Учитывая представленное выше, размер DNP может быть выбран из одного байта и двух байтов в системе передачи, представленной фиг. 1. Модуль 33n FEC может генерировать поток, включающий в себя сигналы, которые представляют собой идентификатор размера, обозначающий размер DNP, и поток с удаленными NP.

Модуль 33n FEC генерирует поток фрейма ВВ, путем добавления заголовка ВВ и необходимых сигналов в полосе к одному или больше пакетам в потоке с удаленными NP по каналу ch#n, предоставляемому из модуля 32n удаления NP, как описано выше.

Идентификатор размера может быть включен, например, в заголовок ВВ фрейма ВВ.

На фиг. 16 иллюстрируется формат фрейма ВВ.

Например, поле, в котором фиксированные значения установлены в заголовке ВВ фрейма ВВ, может использоваться в качестве идентификатора размера.

Другими словами, поле, в котором фиксированные значения установлены в заголовок ВВ, представляют собой, например, двухбайтное UPL или однобайтное SYNC. Один или больше битов UPL или SYNC фиксированных значений могут использоваться в качестве идентификатора размера.

Когда один байт или два байта избирательно используются, как размер DNP, как описано выше, один бит из UPL или SYNC с фиксированными значениями используются в качестве идентификатора размера. Например, когда размер DNP составляет один байт, значение одного бита UPL или SYNC фиксированного значения используется в качестве идентификатора размера без каких-либо изменений. Когда размер DNP составляет один байт, значение бита UPL или SYNC с фиксированными значениями, используемыми, как идентификатор размера, может представлять собой значение, полученное путем инвертирования исходных значений.

Следует отметить, что размер DNP может составлять не только один байт и два байта, но также и три или больше байтов.

Когда модуль 33n FEC в устройстве 11 передачи генерирует поток фрейма ВВ, включающий в себя идентификатор размера, как описано выше, модуль 63n вставки NP в устройстве 12 приема распознает размер DNP, включенный в принимаемый поток после FEC, а именно, поток с удаленными NP, в формате фрейма ВВ, в соответствии с идентификатором размера, и вставляет такое количество NP, которое равно числу, обозначенному DNP, имеющим размер.

Передача BUFS и BUFSTAT

На фиг. 17 иллюстрируется формат ISSY.

ISSY включает в себя ISCR, BUFS и BUFSTAT.

ISCR представляет собой информацию времени, обозначающую время, когда пакет передают, как описано выше, и представляет собой информацию из двух или трех байтов.

BUFS представляет собой (фактически) двухбайтовую информацию, обозначающую емкость буфера (требуемую величину буфера) для буфера 64n, которая требуется для сохранения принимаемого потока после FEC, когда модуль 63n вставки NP восстанавливает синхронизированный поток, как поток со вставленными NP, вставляя NP в принимаемый поток после FEC.

Пятый и шестой биты сверху строки битов, которая представляет собой BUFS размером два байта (первый байт и второй байт), называется BUFS_UNIT. BUFS_UNIT обозначает единицу емкости буфера, обозначенного BUFS. Десять битов от седьмого бита по последний 16-ый бит обозначают значение емкости буфера.

Например, область сохранения, которая работает, как буфер 64n, имеющий емкость буфера, обозначенную BUFS, обеспечивается в модуле 63n вставки NP устройства 12 приема. Принимаемый поток после FEC записывают в буфер 64n, в то время как синхронизированный поток восстанавливают, как поток со вставленными NP.

BUFSTAT представляет собой (фактически) двухбайтную информацию, обозначающую время начала считывания, когда пакет считывают из буфера 64n, в то время как модуль 63„ вставки NP восстанавливает синхронизированный поток, как поток со вставленными NP, путем считывания пакетов (для принимаемого потока после FEC), сохраненного в буфере 64n.

Следует отметить, что пятый и шестой биты сверху строки битов, которая представляет собой BUFSTAT из двух байтов (первый байт и второй байт), называется BUFSTAT_UNIT. BUFSTAT_UNIT обозначает модуль времени начала считывания, обозначенного BUFSTAT. Десять битов от седьмого бита по последний 16-ый бит обозначают значение времени начала считывания. 10 битов BUFSTAT обозначают время начала считывания с остаточным количеством данных в буфере 64n, когда пакеты считывают из буфера 64n.

Модуль 63n вставки NP в устройстве 12 приема начинает считывать пакеты из буфера 64n в момент времени (время), обозначенный BUFSTAT, когда модуль 63n вставки NP восстанавливает синхронизированный поток, как поток со вставленными NP.

ISCR в ISSY, описанном выше, добавляют к каждому пакету разделенных потоков в модуле 31n синхронизации устройства 11 передачи таким образом, что модуль 52 слияния в устройстве 12 приема реконструирует входной поток.

Таким образом, когда только ISSY может быть добавлен к каждому пакету разделенных потоков, и ISCR добавляют к каждому пакету, может быть невозможно добавлять BUFS и BUFSTAT к каждому пакету.

Таким образом, устройство 11 передачи должно передавать сигналы, то есть, BUFS и BUFSTAT, в способе, отличном от способа для передачи ISCR.

Например, аналогично идентификатору размера, BUFS и BUFSTAT могут быть включены в заголовок ВВ фрейма ВВ, в котором поток генерируется модулем 33n FEC.

На фиг. 18 показана схема для формата заголовка ВВ.

Например, UPL или SYNC, которые представляют собой поле, в котором фиксированное значение установлено в заголовке ВВ, могут использоваться в качестве BUFS и BUFSTAT, аналогично идентификатору размера.

В этом примере, когда все идентификаторы размера BUFS и BUFSTAT, включены в заголовок ВВ, например, BUFS и BUFSTAT могут быть включены в UPL, и идентификатор размера может быть включен в SYNC.

Следует отметить, что, например, однобитный идентификатор размера может быть включен в однобайтный SYNC в заголовке ВВ каждого фрейма ВВ.

Каждый из BUFS и BUFSTAT имеет два байта. Таким образом, BUFS и BUFSTAT могут быть периодически (регулярно), например, поочередно включены в двухбайтный UPL в заголовке ВВ каждого фрейма ВВ.

Другой способ передачи идентификатора размера, BUFS и BUFSTAT

На фиг. 19 показана пояснительная схема другого способа для передачи идентификатор размера, BUFS и BUFSTAT.

Другими словами, на фиг. 19 показана схема формата фрейма ВВ.

Как описано выше, сигналы в полосе могут быть добавлены к фрейму ВВ.

Существуют два типа сигналов в полосе, сигналы типа А в полосе и сигналы типа B в полосе, в DVB-T2, вместо этих типов сигналов в полосе, могут использоваться новые типы сигналов в системе передачи на фиг. 1.

Как показано на фиг. 19, новые сигналы в полосе включает в себя однобитный идентификатор размера, двухбайтный BUFSTAT_UNIT, 10-битный BUFSTAT (а именно, значение времени начала передачи), двухбитный BUFS_UNIT и 10-битный BUFS (а именно, значение емкости буфера).

Новые сигналы в полосе добавляют к фрейму ВВ, когда модуль 33n FEC в устройстве 11 передачи генерирует фрейм ВВ.

TS используется, как входной поток в настоящем варианте осуществления. Следует отметить, однако, что поток, сформированный множеством пакетов, может использоваться в качестве входного потока, вместо TS.

Описание компьютера, в котором используется настоящее изобретение

Последовательность обработки, описанная выше, может быть выполнена в аппаратных средствах или в программных средствах. Когда последовательность обработки выполняется с использованием программного обеспечения, программу такого программного обеспечения устанавливают, например, в компьютере общего назначения.

На фиг. 20 иллюстрируется пример конфигурации, в соответствии с вариантом осуществления компьютера, на котором установлена программа для выполнения последовательности обработки.

Программа может заранее быть сохранена на жестком диске 205 или ROM 203, которое представляет собой носитель записи, встроенный в компьютер.

В качестве альтернативы, программа может быть сохранена (записана) на съемный носитель 111 записи. Съемный носитель 111 записи может быть предусмотрен, как, так называемое, пакетное программное обеспечение. Съемный носитель 111 записи, например, гибкий диск, постоянное запоминающее устройство на компакт-дисках (CD-ROM), магнитооптический (МО) диск, цифровой универсальный диск (DVD), магнитный диск или полупроводниковое запоминающее устройство.

Следует отметить, что программа может быть загружена в компьютер через сеть передачи данных или сеть широковещательной передачи, и может быть установлена на встроенный жесткий диск 205 вместо установки на компьютер со съемного носителя 111 записи. Другими словами, программа может быть передана, например, из сайта загрузки через искусственный спутник земли для цифровой спутниковой широковещательной передачи в компьютер при беспроводной передаче данных, или через сеть, такую как локальная вычислительная сеть (LAN) или Интернет, в компьютер при проводной передаче данных.

Компьютер включает в себя центральное процессорное устройство (CPU) 202. Интерфейс 110 ввода и вывода соединен с CPU 202 через шину 201.