Уровень техники

Область техники, к которой относится изобретение

[0001] Настоящее изобретение относится к полупроводниковому устройству и к подложке головки выброса жидкости.

Описание предшествующего уровня техники

[0002] Выложенный японский патент № 10-209292 раскрывает схему защиты для защиты элемента от ESD (электростатического разряда: ESD) в полупроводниковом устройстве. Схема защиты в выложенном японском патенте № 10-209292 включает в себя транзистор M2, который соединяет линию напряжения и линию заземления. Если в линии напряжения создается перенапряжение, транзистор M2 включается, и ток протекает из линии напряжения в линию заземления, разряжая перенапряжение в линии напряжения. Выложенный японский патент № 10-209292 раскрывает то, что в результате внутренняя цепь защищена от ESD.

Сущность изобретения

[0003] В схеме защиты выложенного японского патента № 10-209292 флуктуации напряжения в линии напряжения передаются на затвор транзистора M1 через паразитную емкость затвор-сток транзистора M1. Флуктуации напряжения на затворе транзистора M1 включают транзистор M1, и на затвор транзистора M2 подается напряжение для включения этого транзистора M2.

[0004] Однако, как описано в выложенном японском патенте № 10-209292, емкостная связь для передачи флуктуаций напряжения на затвор транзистора M1 может быть недостаточной, если в качестве емкостного элемента в схеме защиты используется только паразитная емкость затвор-сток MOS (МОП-структуры). Емкость затвор-исток транзистора M1 не может заряжаться, и в силу этого может быть невозможным обеспечивать достаточное напряжение Vgs затвор-исток для включения транзистора M1. В результат может ухудшаться функция схемы защиты.

[0005] Выложенный японский патент № 10-209292 раскрывает дополнительное использование емкостного элемента. Однако, он не раскрывает конкретную структуру емкостного элемента. Чтобы использовать его для вывода высокого напряжения, требуется высокое напряжение пробоя емкостного элемента. Например, в качестве емкостного элемента в схеме защиты может использоваться емкость оксидной пленки, полученная при утолщении оксидной пленки затвора, либо емкость p-n-перехода, использующая p-n-переход. Однако, для того, чтобы образовать емкость оксидной пленки, требуется процесс образования толстой оксидной пленки, что увеличивает число этапов в процессе. Емкость p-n-перехода является недостаточной по эффективности использования площади, что увеличивает затраты.

[0006] Как описано выше, в раскрытой в выложенном японском патенте № 10-209292 технологии затруднительно, в частности, надлежащим образом защищать вывод, к которому приложено высокое напряжение.

[0007] Настоящее изобретение предоставляет технологию, преимущественную для соответствующей защиты внутренней цепи от ESD в полупроводниковом устройстве.

[0008] Согласно некоторым вариантам осуществления, предусмотрено полупроводниковое устройство, содержащее: первый транзистор, который включает в себя первый первичный вывод, второй первичный вывод и первый управляющий вывод; второй транзистор, который включает в себя третий первичный вывод, четвертый первичный вывод и второй управляющий вывод; и первый резистивный элемент, при этом первый первичный вывод и третий первичный вывод подключены к (соединены с) первой линии напряжения, второй первичный вывод и один вывод первого резистивного элемента подключены ко второй линии напряжения, первый управляющий вывод, второй управляющий вывод, четвертый первичный вывод и другой вывод первого резистивного элемента соединены друг с другом с образованием одного узла, при этом изменение потенциала в третьем первичном выводе передается на первый управляющий вывод через емкостную связь между третьим первичным выводом и упомянутым одним узлом, и передаваемое изменение потенциала включает первый транзистор.

[0009] Согласно некоторым другим вариантам осуществления, предусмотрена подложка головки выброса жидкости, содержащая: полупроводниковое устройство; нагревательный элемент, выполненный с возможностью нагревать жидкость; и пятый транзистор, выполненный с возможностью возбуждать нагревательный элемент, при этом полупроводниковое устройство содержит: первый транзистор, который включает в себя первый первичный вывод, второй первичный вывод и первый управляющий вывод; второй транзистор, который включает в себя третий первичный вывод, четвертый первичный вывод и второй управляющий вывод; и первый резистивный элемент, при этом первый первичный вывод и третий первичный вывод подключены к первой линии напряжения, второй первичный вывод и один вывод первого резистивного элемента подключены ко второй линии напряжения, при этом первый управляющий вывод, второй управляющий вывод, четвертый первичный вывод и другой вывод первого резистивного элемента соединены друг с другом с образованием одного узла, при этом изменение потенциала в третьем первичном выводе передается на первый управляющий вывод через емкостную связь между третьим первичным выводом и упомянутым одним узлом, и передаваемое изменение потенциала включает первый транзистор.

[0010] Согласно некоторым другим вариантам осуществления, предусмотрена подложка головки выброса жидкости, содержащая: полупроводниковое устройство; нагревательный элемент, выполненный с возможностью нагревать жидкость; и пятый транзистор, выполненный с возможностью возбуждать нагревательный элемент, при этом полупроводниковое устройство содержит: первый транзистор, который включает в себя первый первичный вывод, второй первичный вывод и первый управляющий вывод; второй транзистор, который включает в себя третий первичный вывод, четвертый первичный вывод и второй управляющий вывод; первый резистивный элемент; емкостный элемент, который включает в себя первый вывод и второй вывод; третий транзистор, который включает в себя пятый первичный вывод, соединенный со вторым выводом, шестой первичный вывод и третий управляющий вывод; и блок возбуждения, образованный по меньшей мере одним транзистором, который включает в себя четвертый транзистор, и выполненный с возможностью вызывать пробой изоляции емкостного элемента при подаче управляющего сигнала на третий управляющий вывод, при этом первый первичный вывод, третий первичный вывод и первый вывод подключены к первой линии напряжения, второй первичный вывод, один вывод первого резистивного элемента и шестой первичный вывод подключены ко второй линии напряжения, при этом первый управляющий вывод, второй управляющий вывод, четвертый первичный вывод и другой вывод первого резистивного элемента соединены друг с другом с образованием одного узла, при этом изменение потенциала в третьем первичном выводе передается на первый управляющий вывод через емкостную связь между третьим первичным выводом и упомянутым одним узлом, и передаваемое изменение потенциала включает первый транзистор.

[0011] Дополнительные признаки настоящего изобретения станут очевидными из нижеприведенного описания примерных вариантов осуществления (со ссылкой на прилагаемые чертежи).

Краткое описание чертежей

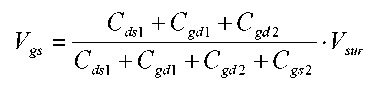

[0012] Фиг. 1 является принципиальной схемой, показывающей компоновку схемы полупроводникового устройства согласно варианту осуществления настоящего изобретения;

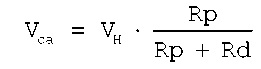

[0013] Фиг. 2 является видом, показывающим структуру в разрезе полупроводникового устройства на фиг. 1;

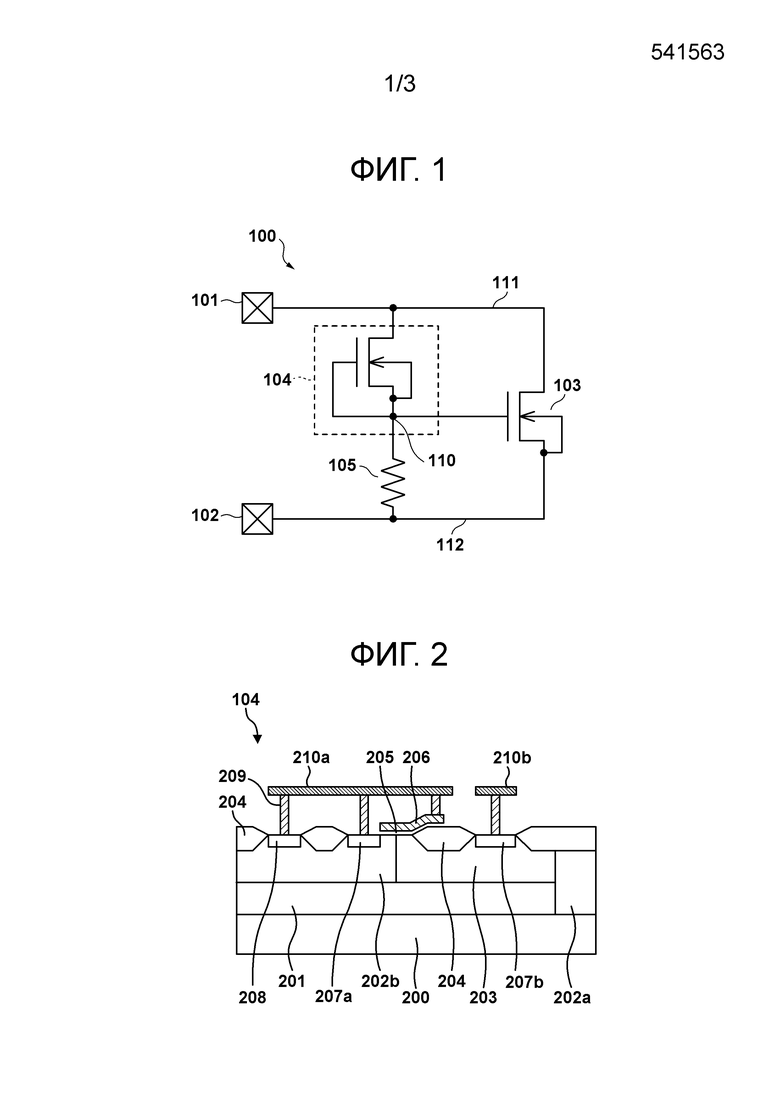

[0014] Фиг. 3 является принципиальной схемой, показывающей компоновку схемы полупроводникового устройства согласно варианту осуществления настоящего изобретения;

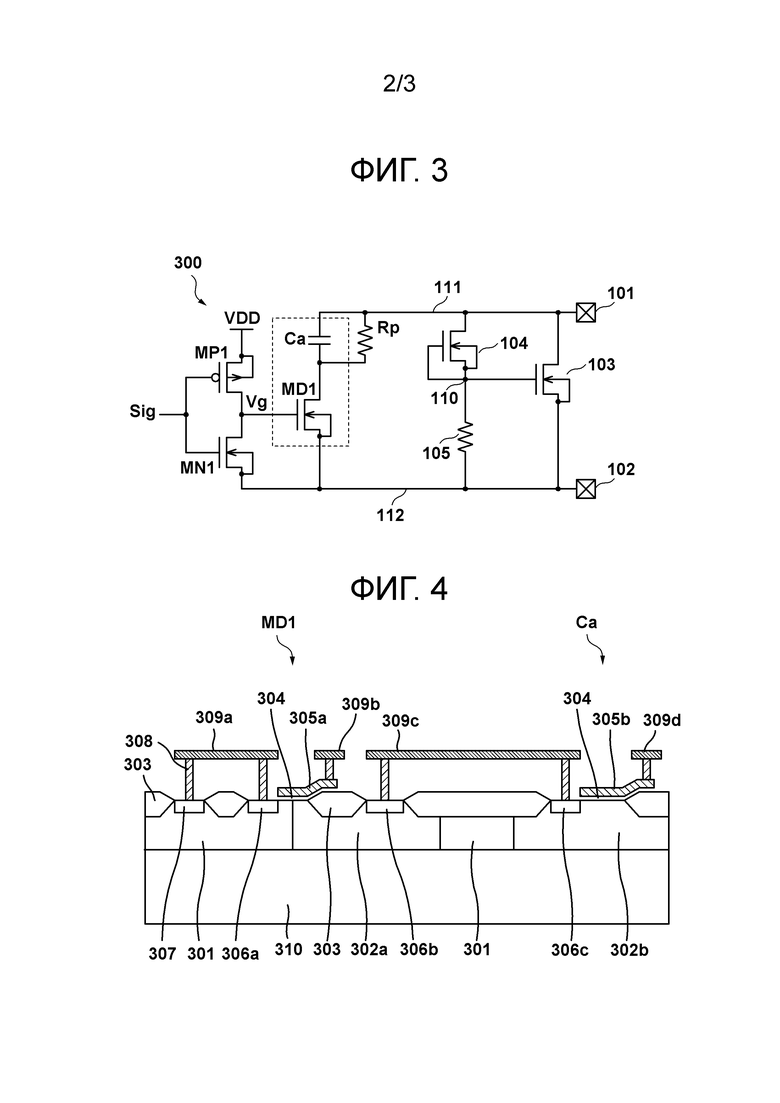

[0015] Фиг. 4 является видом, показывающим структуру в разрезе полупроводникового устройства на фиг. 3;

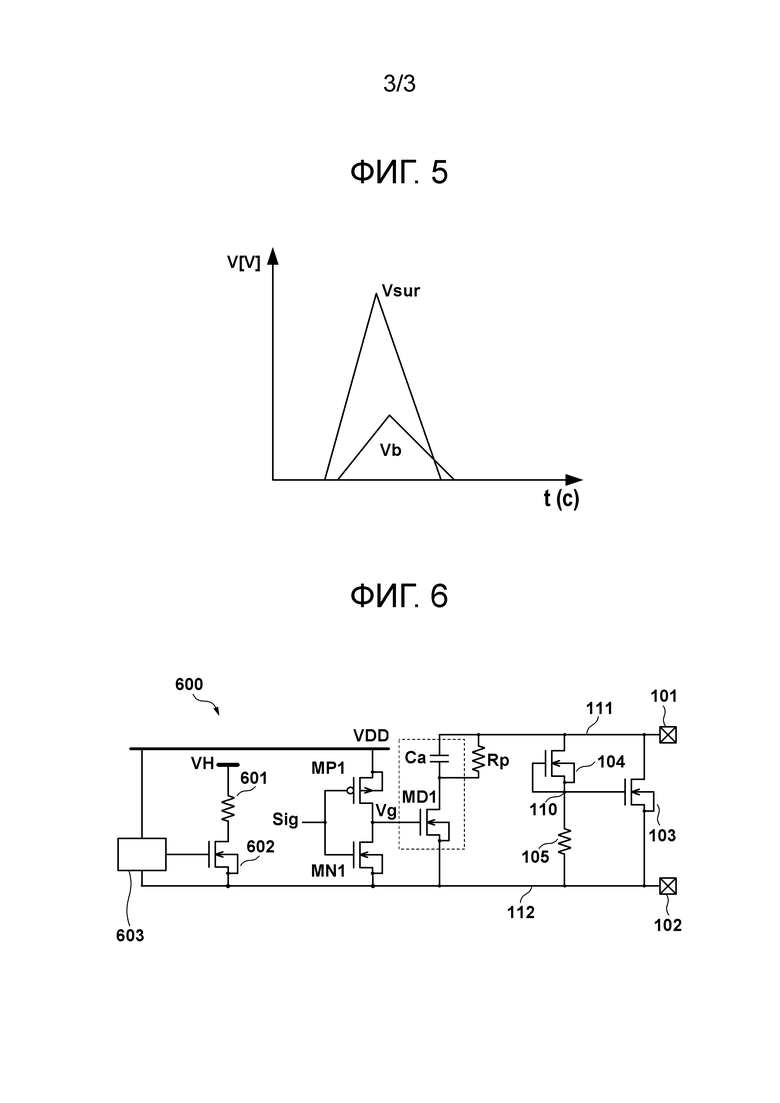

[0016] Фиг. 5 является графиком, показывающим формы сигналов напряжений, приложенных к двум выводам элемента проводящего мостика на фиг. 3; и

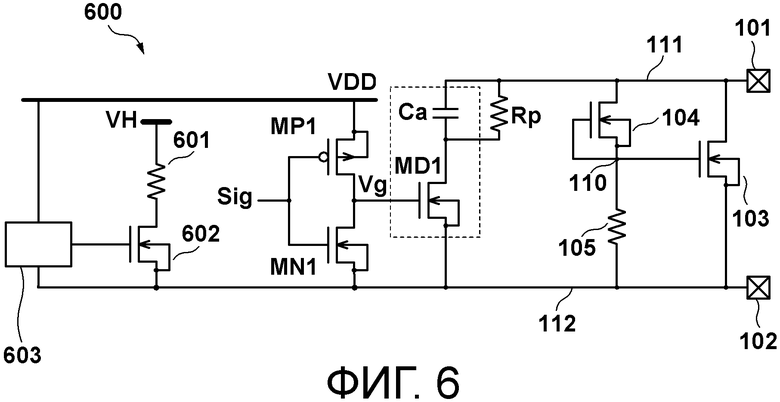

[0017] Фиг. 6 является принципиальной схемой, показывающей компоновку схемы подложки головки выброса жидкости согласно варианту осуществления настоящего изобретения.

Подробное описание вариантов осуществления

[0018] Ниже будут описаны практические варианты осуществления полупроводникового устройства по настоящему изобретению со ссылкой на прилагаемые чертежи. Следует отметить, что в нижеприведенном описании и на чертежах общие ссылочные позиции обозначают общие компоновки на множестве чертежей. Следовательно, общие компоновки будут описаны при взаимной ссылке на множество чертежей, и описания компоновок, обозначаемых общими ссылочными позициями, опускаются при необходимости.

[0019] Со ссылкой на фиг. 1 и 2 будет описана структура полупроводникового устройства согласно варианту осуществления настоящего изобретения. Фиг. 1 является принципиальной схемой, показывающей компоновку схемы полупроводникового устройства 100 согласно первому варианту осуществления настоящего изобретения. Полупроводниковое устройство 100 образует схему защиты для защиты внутренней цепи от электростатического разряда (ESD). Полупроводниковое устройство 100 включает в себя транзистор 103, транзистор 104 и резистивный элемент 105. Один первичный вывод (сток) транзистора 103 и один первичный вывод (сток) транзистора 104 подключены к линии 111 напряжения. Другой первичный вывод (исток) транзистора 103 и один вывод резистивного элемента 105 подключены к линии 112 напряжения. Управляющий вывод (затвор) транзистора 103, управляющий вывод (затвор) и другой первичный вывод (исток) транзистора 104 и другой вывод резистивного элемента 105 соединены друг с другом с образованием одного узла 110. Из вывода 101 на линию 111 напряжения подается высокое напряжение VH, а из вывода 102 на линию 112 напряжения подается потенциал земли. Для транзистора 103 и транзистора 104 используются транзисторы на основе DMOS (МОП-структура с двойной диффузией), каждый из которых служит в качестве выдерживающего высокое напряжение элемента, имеющего более высокое напряжение пробоя, чем обычный транзистор.

[0020] Фиг. 2 показывает структуру в разрезе транзистора 104, обведенного пунктирной линией на фиг. 1. Углубленный слой 201, служащий в качестве полупроводниковой области n-типа (электронный полупроводник), и область 202a кармана, служащая в качестве полупроводниковой области p-типа (дырочный полупроводник), расположены на полупроводниковой области 200 p-типа. Полупроводниковая область 200, например, может представлять собой полупроводниковую подложку p-типа из кремния или подобного, либо область кармана p-типа, образованную на подложке. В этом варианте осуществления для полупроводниковой области 200 используется полупроводниковая подложка p-типа из кремния. Область 202b кармана, служащая в качестве полупроводниковой области p-типа, и область 203 кармана, служащая в качестве полупроводниковой области n-типа, расположены на углубленном слое 201. Над областью 202b кармана и областью 203 кармана через изолирующую пленку 205 затвора расположен электрод 206 затвора. Электрод 206 затвора включает в себя участки, расположенные в области 202b кармана, области 203 кармана и изолирующей поле пленке 204, соответственно. Соответственно, реальная толщина изолирующей пленки затвора на участке, контактирующем с областью 203 кармана на изолирующей пленке 205 затвора и изолирующей поле пленке 204, превышает толщину изолирующей пленки затвора на участке, контактирующем с областями 202b и 203 кармана только на изолирующей пленке 205 затвора. Изолирующая пленка 205 затвора может использовать, например, оксид кремния, нитрид кремния, оксинитрид кремния или подобное. Электрод 206 затвора может быть образован с использованием, например, поликристаллического кремния. Диффузионные области 207a и 207b представляют собой высококонцентрированные диффузионные области n-типа. Диффузионная область 208 представляет собой высококонцентрированную диффузионную область p-типа. Диффузионные области 207a, 207b и 208 образуют соответствующие электроды (выводы) истока, стока и нижнего затвора, соответственно, как будет описано далее. Электрод 206 затвора и диффузионные области 207a, 207b и 208 электрически подключаются к межсоединениям (электропроводке) 210a и 210b, соответственно, через контактные участки 209. Для контактных участков 209 и межсоединений 210a и 210b используют, например, металл или подобное. Однако, их способы изготовления и структуры не ограничены при условии, что они электрически соединяются с соответствующими электродами. Изолирующие поле пленки 204, каждая из которых имеет структуру на основе LOCOS (локального оксидирования кремния), расположены между соответствующими электродами и между элементами, такими как транзисторы или подобное. Каждая изолирующая поле пленка 204 может иметь структуру на основе STI (узкощелевой изоляции). Типы проводимости вышеописанных полупроводников, включающие в себя типы проводимости полупроводников, которые описываются далее, могут быть противоположными относительно друг друга.

[0021] Теперь будет описана компоновка транзистора 104. Электрод 206 затвора расположен над областью 202b кармана и областью 203 кармана, соседних друг к другу, через изолирующую пленку 205 затвора. Область, в которой область 202b кармана и электрод 206 затвора перекрываются, становится областью канала. В этом варианте осуществления транзистор 104 представляет собой транзистор на основе LDMOS (МОП-структура с поперечной диффузией), который представляет собой поперечную DMOS с областью канала, образованной вдоль поверхности полупроводниковой подложки, как показано на фиг. 2. Диффузионная область 207a образует электрод истока (область истока), а диффузионная область 208 образует электрод нижнего затвора. Как показано на фиг. 1 и 2, электрод истока и электрод 206 затвора транзистора 104 замкнуты накоротко. Область 203 кармана функционирует в качестве области ослабления (релаксации) электрического поля в области стока и простирается под электродом 206 затвора. Диффузионная область 207b, образованная в области 203 кармана, образует электрод стока (область стока). Область 203 кармана n-типа имеет более низкую концентрацию примесей, чем диффузионная область 207b, имеющая тот же самый n-тип проводимости. Изолирующая поле пленка 204 расположена в области 203 кармана. Сторона стока электрода 206 затвора имеет структуру, которая простирается на изолирующей поле пленке 204, т.е. так называемую смещенную LOCOS-структуру. Это позволяет обеспечивать напряжение пробоя затвор-сток, даже если транзистор 104 находится в отключенном состоянии, т.е. в состоянии, в котором электрод затвора и электрод истока замкнуты накоротко, и напряжение электрода стока повышается до высокого напряжения VH. Транзистор 103 также может иметь ту же самую компоновку, как транзистор 104. Однако, он отличается по компоновке межсоединений 210a и 210b, а электрод 206 затвора и электрод истока не замкнуты накоротко. Изолирующая пленка 205 затвора и изолирующие поле пленки 204 могут быть образованы одинаковым материалом. Изолирующая пленка 205 затвора и изолирующие поле пленки 204 могут быть образованы в различных процессах. Однако, их структуры включают в себя изолирующие пленки, образованные одинаковым материалом и имеющие участки, отличающиеся по толщине.

[0022] Теперь будут описаны паразитные емкости, которые существуют в транзисторе 104. Паразитные емкости Cds1 p-n-перехода существуют между областью 202b кармана и областью 203 кармана и между областью 202b кармана и углубленным слоем 201. Между областью 203 кармана и электродом 206 затвора существует паразитная емкость Cgd1. Между областью 202b кармана и электродом 206 затвора существует паразитная емкость Cgs1.

[0023] Теперь будет описана работа полупроводникового устройства 100, показанного на фиг. 1. Будет рассмотрено состояние до того, как прикладывается высокое перенапряжение, при ESD, из вывода 101 на линию 111 напряжения с высокой скоростью. Паразитные емкости Cgd1 и Cds1 транзистора 104 не передают низкочастотный сигнал, и в силу этого потенциал затвора транзистора 103 становится потенциалом земли 0 В. Следовательно, транзистор 103 выключается, и никакого тока не протекает между истоком и стоком транзистора 103. Теперь будет рассмотрен случай, в котором прикладывается высокое перенапряжение, при ESD, из вывода 101 на линию 111 напряжения с высокой скоростью. Паразитные емкости Cgd1 и Cds1 транзистора 104 существуют последовательно с паразитной емкостью Cgs2, которая существует между электродом истока и электродом затвора транзистора 103, и эти емкости осуществляют емкостную связь и работают в качестве емкостей связи. Паразитная емкость Cgd2, которая существует между электродом затвора и электродом стока транзистора 103, также существует параллельно паразитным емкостям Cgd1 и Cds1 транзистора 104, и в силу этого эти емкости осуществляют емкостную связь и работают в качестве емкостей связи. Следовательно, паразитные емкости Cgd1, Cds1 и Cgd2 заряжают паразитную емкость Cgs2 затвор-исток транзистора 103 и включают транзистор 103. Таким образом, когда к стоку транзистора 104 прикладывается перенапряжение, изменение потенциала на стоке транзистора 104 передается на электрод затвора транзистора 103 с помощью емкостной связи между узлом 110 и стоком транзистора 104. В результате транзистор 103 включается, и ток перегрузки протекает через вывод 102 через линию 112 напряжения, предотвращая протекание тока перегрузки через внутреннюю цепь. Каждая из паразитных емкостей Cgd1, Cgs1 и Cds1 имеет зависимость от напряжения. Следовательно, если прикладываемое перенапряжение Vsur является высоким, обедненный (запирающий) слой каждой паразитной емкости Cds1 становится толстым, и паразитная емкость Cgd1 теряет свой эффект. Однако, когда перенапряжение повышается, зависимость от напряжения каждой паразитной емкости Cds1 является слабой. Следовательно, обедненный слой каждой паразитной емкости Cds1 является тонким, и паразитная емкость Cgd1 имеет свой эффект. Следует отметить, что значение напряжения Vgs затвор-исток транзистора 103 может быть задано как:

...(1)

...(1)

Можно увеличивать напряжение Vgs затвор-исток транзистора 103 при выполнении паразитных емкостей Cgd1 и Cds1 транзистора 104 большими, чем по уравнению (1). Появляется возможность более надежно включать транзистор 103 и в достаточной степени пропускать ток перегрузки при увеличении напряжения Vgs затвор-исток транзистора 103. Время, в течение которого транзистор 103 включен, определяется временной константой τ=(Cgd1+Cgd2+Cds1)×R с помощью паразитной емкости Cgd2 транзистора 103, паразитных емкостей Cgd1 и Cds1 транзистора 104 и резистивного значения резистивного элемента 105. Следовательно, сначала соответствующие значения паразитных емкостей Cgd1, Cgs1, Cgd2 и Cgs2 определяются таким образом, чтобы ток перегрузки мог протекать в достаточной степени. Более конкретно, соответствующие значения паразитных емкостей Cgd1, Cgs1, Cgd2 и Cgs2 могут определяться при определении длин затвора и ширин затвора транзисторов 103 и 104 надлежащим образом. Затем время, в течение которого транзистор 103 включен, регулируется выбором резистивного значения резистивного элемента 105 надлежащим образом.

[0024] Как описано выше, можно включать транзистор 103 в достаточной степени при реализации емкости схемы защиты для защиты внутренней цепи от ESD с использованием DMOS-транзистора, который соединяет электрод затвора и электрод истока в полупроводниковом устройстве 100. Необходимая для полупроводникового устройства 100 емкость реализуется с помощью паразитной емкости, исключая необходимость добавлять емкостный элемент или подобное. Высокое напряжение пробоя требуется для емкостного элемента, используемого для схемы защиты, к которой прикладывается высокое напряжение, подобное ESD. Например, в качестве емкостного элемента схемы защиты может использоваться MOS-емкость, емкость p-n-перехода, использующая p-n-переход, или подобное. Если в качестве емкостного элемента используется MOS-емкость, должна быть образована изолирующая пленка, более толстая, чем другие транзисторы, включенные во внутреннюю цепь или подобное, чтобы задавать напряжение пробоя выше, чем у других транзисторов. Это требует, например, дополнительного этапа образования толстой изолирующей пленки в дополнение к этапу образования изолирующей пленки затвора транзистора, приводя к вероятности увеличения числа этапов в процессе изготовления. Емкость p-n-перехода является ничтожной по эффективности использования площади, затрудняя уменьшение размера полупроводникового устройства. Напротив, полупроводниковое устройство 100, описанное в этом варианте осуществления, функционирует в качестве емкости за счет совершенствования соединения транзистора 103. Следовательно, можно выполнять емкостный элемент с большим емкостным значением без добавления емкостного элемента. В результате может подавляться увеличение числа этапов в процессе изготовления, и также может дополнительно улучшаться эффективность использования площади.

[0025] Структура полупроводникового устройства согласно варианту осуществления настоящего изобретения будет описана со ссылкой на фиг. 3 и 4. Фиг. 3 является принципиальной схемой, показывающей компоновку схемы полупроводникового устройства 300 согласно второму варианту осуществления настоящего изобретения. Полупроводниковое устройство 300 включает в себя емкостный элемент Ca, который образует элемент проводящего мостика, и транзисторы 103 и 104 и резистивный элемент 105, каждый из которых имеет ту же самую компоновку, как вышеописанное полупроводниковое устройство 100, в качестве схемы защиты, которая защищает элемент проводящего мостика. Полупроводниковое устройство 300 также включает в себя транзистор MD1, транзистор MP1, транзистор MN1 и резистивный элемент Rp. Фиг. 3 показывает состояние до того, как информация записывается в элемент проводящего мостика, другими словами, до того, как емкостный элемент Ca разрушается.

[0026] Транзистор MP1 представляет собой MOS-транзистор p-типа, а транзистор MN1 представляет собой MOS-транзистор n-типа. Транзисторы MP1 и MN1 используют обычные MOS-транзисторы и имеют более низкое напряжение пробоя, чем DMOS-транзисторы, используемые для транзисторов 103 и 104. Другими словами, транзисторы 103 и 104 имеют более высокое напряжение пробоя, чем транзисторы MP1 и MN1. Транзистор MD1 представляет собой DMOS-транзистор, аналогично транзисторам 103 и 104, и имеет более высокое напряжение пробоя, чем транзисторы MP1 и MN1, подробности которых будут описаны далее. Нижний затвор и один первичный вывод (исток) транзистора MP1 подключены к напряжению VDD источника питания логики. Нижний затвор и один первичный вывод (исток) транзистора MN1 подключены к линии 112 напряжения. Напряжение VDD источника питания логики имеет более низкий потенциал, чем высокое напряжение VH, подаваемое на вывод 101. Линия 112 напряжения подключена к выводу 102 и потенциалу земли, как описано выше. В управляющий электрод (затвор) транзистора MP1 и управляющий электрод (затвор) транзистора MN1 вводится управляющий сигнал Sig. Другой первичный вывод (сток) транзистора MP1 и другой первичный вывод (сток) транзистора MN1 соединены друг с другом и образуют инверторную схему, служащую в качестве блока возбуждения, с помощью транзистора MP1 и транзистора MN1. Управляющий сигнал Vg, служащий в качестве выходного сигнала инверторной схемы (блока возбуждения), вводится в управляющий электрод (затвор) транзистора MD1, который управляет записью в элементе проводящего мостика. Нижний затвор и один первичный электрод (исток) транзистора MD1 подключены к линии 112 напряжения. Другой первичный вывод (сток) транзистора MD1 соединен с одним выводом емкостного элемента Ca, который образует элемент проводящего мостика. Другой вывод емкостного элемента Ca подключен к линии 111 напряжения. Высокое напряжение VH, прикладываемое, когда информация записывается в элемент проводящего мостика, подается из вывода 101 на линию 111 напряжения. Один вывод резистивного элемента Rp соединен со стоком транзистора MD1 и одним выводом емкостного элемента Ca с образованием одного узла. Другой вывод резистивного элемента Rp подключен к линии 111 напряжения.

[0027] Далее, фиг. 4 показывает структуру в разрезе емкостного элемента Ca и транзистора MD1, обведенную пунктирной линией, показанной на фиг. 3. Область 301 кармана, служащая в качестве полупроводниковой области p-типа, и области 302a и 302b кармана, каждая из которых служит в качестве полупроводниковой области n-типа, расположены на полупроводниковой области 310 p-типа. В этом варианте осуществления, аналогично полупроводниковой области 200 по вышеописанному первому варианту осуществления, для полупроводниковой области 310 используется полупроводниковая подложка p-типа из кремния. Область 301 кармана имеет общую концентрацию примесей с областью кармана p-типа транзистора MN1, который образует логическую схему блока возбуждения. Каждая из областей 302a и 302b кармана имеет общую концентрацию примесей с областью кармана n-типа транзистора MP1, который образует логическую схему блока возбуждения. Следует отметить, что концентрации примесей областей 302a и 302b кармана должны задаваться относительно концентрации примесей полупроводниковой области 310 таким образом, что напряжение пробоя между полупроводниковой областью 310 и областями 302a и 302b кармана становится выше высокого напряжения VH. Изолирующая поле пленка 303 имеет LOCOS-структуру. Изолирующая пленка 304 затвора транзистора MD1 использует, например, оксид кремния и образуется одновременно с этапом образования изолирующих пленок затворов транзисторов MP1 и MN1, каждый из которых образует логическую схему блока возбуждения. Емкостный элемент Ca, который образует элемент проводящего мостика, имеет MOS-структуру, а изолирующая пленка 304 затвора, которая образует этот емкостный элемент Ca, также образуется одновременно с изолирующими пленками затворов транзисторов MD1, MP1 и MN1. Электрод 305a затвора представляет собой электрод затвора транзистора MD1, а электрод 305b затвора представляет собой электрод, который образует другой вывод емкостного элемента Ca, служащего в качестве элемента проводящего мостика. Электроды 305a и 305b затвора образуются с использованием, например, поликристаллического кремния. Диффузионные области 306a-306c представляют собой высококонцентрированные диффузионные области n-типа. Диффузионная область 307 представляет собой высококонцентрированную диффузионную область p-типа. Электроды 305a и 305b затвора и диффузионные области 306a-306c и 307 могут быть образованы на том же самом этапе, как этап образования электродов затвора транзисторов MP1 и MN1, каждый из которых образует логическую схему блока возбуждения, и этап образования соответствующих диффузионных областей. Электроды 305a и 305b затвора и диффузионные области 306a-306c и 307 образуют свои соответствующие электроды (выводы), как будет описано далее, и электрически подключаются к межсоединениям 309a-309d через контактные участки 308. Для контактных частей 308 и межсоединений 309a-309d используется, например, металл или подобное. Однако, их способы изготовления и структуры не ограничены при условии, что они электрически подключаются к соответствующим электродам.

[0028] Теперь будет описана компоновка транзистора MD1. Электрод 305a затвора расположен над областью 301 кармана и областью 302a кармана, смежными друг другу, через изолирующую пленку 304 затвора. Область, в которой область 301 кармана и электрод 305a затвора перекрываются, становится областью канала. В этом варианте осуществления, аналогично транзисторам 103 и 104, транзистор MD1 представляет собой LDMOS-транзистор, т.е. поперечную DMOS-структуру с областью канала, образованной вдоль поверхности полупроводниковой подложки. Высококонцентрированная диффузионная область 306a n-типа образует электрод истока (область истока), а диффузионная область 307 образует электрод нижнего затвора. Область 302a кармана функционирует в качестве области ослабления электрического поля в области стока и простирается под электродом 305a затвора. Область 302a кармана n-типа имеет более низкую концентрацию примесей, чем диффузионная область 306b, имеющая тот же самый n-тип проводимости. Диффузионная область 306b, образованная в области 302a кармана, образует электрод стока (область стока). Изолирующая поле пленка 303 расположена на области 302a кармана. Сторона стока электрода 305a затвора имеет структуру, которая простирается на изолирующей поле пленке 303, т.е. так называемую смещенную LOCOS-структуру. Это позволяет обеспечивать напряжение пробоя затвор-сток, даже если транзистор MD1 находится в отключенном состоянии, т.е. в состоянии, в котором потенциал электрода 305a затвора является потенциалом земли, и напряжение электрода стока повышается до высокого напряжения VH. Как описано выше, транзистор MD1 имеет ту же самую компоновку, как транзисторы 103 и 104.

[0029] Теперь будет описан емкостный элемент Ca, который образует элемент проводящего мостика. Емкостный элемент Ca имеет MOS-структуру, в которой изолирующая пленка 304 затвора, расположенная на области 302b кармана n-типа, расположена между электродом 305b затвора и нижним электродом, образованным диффузионной областью 306c n-типа. В показанной на фиг. 4 компоновке диффузионная область 306c образуется только в части начала контактного участка 308 для соединения с межсоединением 309c. Однако, диффузионная область 306c может быть образована во всей области, которая перекрывает электрод 305b затвора через изолирующую пленку 304 затвора. Дополнительно, в показанной на фиг. 4 компоновке диффузионная область 306c соединена со стоком транзистора MD1. Однако, настоящее изобретение не ограничено этим. Например, электрод 305b затвора соединен со стоком транзистора MD1, и высокое напряжение VH может подаваться на диффузионную область 306c через межсоединение 309d (линию 111 напряжения). Кроме того, в показанной на фиг. 4 компоновке электроды емкостного элемента Ca образуются с помощью области 302b кармана n-типа и электрода 305b затвора. Однако, также возможна компоновка, в которой используется область кармана p-типа.

[0030] Теперь будет описано состояние соединения каждого электрода. Межсоединение 309a соединено с электродом нижнего затвора и электродом истока транзистора MD1 через контактные участки 308, и подается потенциал земли. Межсоединение 309b соединено с электродом 305a затвора транзистора MD1 через контактный участок 308 и принимает управляющий сигнал Vg, служащий в качестве выходного сигнала инверторной схемы блока возбуждения, показанного на фиг. 3. Межсоединение 309c соединено, через контактные участки 308, с электродом стока транзистора MD1 и диффузионной областью 306c, служащей в качестве нижнего электрода элемента проводящего мостика. Межсоединение 309d соединено с электродом 305b затвора емкостного элемента Ca через контактный участок 308, и во время записи подается высокое напряжение VH.

[0031] Как описано выше, изолирующие пленки затворов транзисторов MP1 и MN1, изолирующая пленка 304 затвора емкостного элемента Ca и изолирующая пленка 304 затвора транзистора MD1 могут быть образованы на одном и том же этапе. При образовании изолирующих пленок затворов на одном и том же этапе, емкостный элемент Ca и транзисторы MD1, MP1 и MN1 могут быть образованы без необходимости множества толщин изолирующей пленки затвора, и число этапов в процессе изготовления не увеличивается. Что касается транзисторов 103 и 104, изолирующая пленка 205 затвора может быть образована одновременно с образованием изолирующих пленок затворов емкостного элемента Ca и транзисторов MD1, MP1 и MN1. Следовательно, поскольку соответствующие толщины изолирующей пленки затвора емкостного элемента Ca и транзисторов 103, 104, MD1, MP1 и MN1 являются одинаковыми, число этапов не должно увеличиваться в процессе изготовления. В емкостном элементе Ca и транзисторах 103, 104, MD1, MP1 и MN1 области кармана и диффузионные области, имеющие одинаковую концентрацию примесей, могут быть образованы на одном и том же этапе, таком как ионная имплантация. Как описано выше, в этом варианте осуществления транзисторы, имеющие различные напряжения пробоя между транзисторами MP1 и MN1, и транзисторы 103, 104 и MD1 могут быть образованы при подавлении увеличения числа этапов в процессе изготовления.

[0032] Теперь будет описана работа, когда в элемент проводящего мостика записывается информация. Когда информация записывается в элемент проводящего мостика, во-первых, управляющий сигнал Vg подается из инверторной схемы блока возбуждения с помощью ввода сигнала низкого уровня в управляющий сигнал Sig, включающий транзистор MD1. Следовательно, ток протекает через резистивный элемент Rp и транзистор MD1. Следует отметить, что если сопротивление Rd представляет собой сопротивление во включенном состоянии транзистора MD1, значение прикладываемого к двум контактным выводам емкостного элемента Ca напряжения Vca может быть задано как:

...(2)

...(2)

Информация записывается в элемент проводящего мостика, когда напряжение Vca становится равным или превышающим напряжение, которое вызывает пробой изоляции у изолирующей пленки 304 затвора емкостного элемента Ca. Способ считывания информации, записанной в элемент проводящего мостика, включает в себя, например, способ измерения изменения импеданса элемента проводящего мостика или подобное.

[0033] Теперь со ссылкой на фиг. 5 будет описана работа, когда к полупроводниковому устройству 300 прикладывается перенапряжение. Во-первых, будет рассмотрен случай, в котором полупроводниковое устройство 300 по фиг. 3 не включает в себя схему защиты, имеющую ту же самую компоновку, как полупроводниковое устройство 100, показанное на фиг. 1. Когда прикладывается высокое перенапряжение, при ESD, из вывода 101 на линию 111 напряжения с высокой скоростью, к одному выводу емкостного элемента Ca с высокой скоростью прикладывается высокое перенапряжение Vsur. Если напряжение Vb представляет собой напряжение на другом выводе емкостного элемента Ca, напряжение Vb вводит большую задержку, чем перенапряжение Vsur, создавая напряжение. Напряжение Vb вводит задержку, поскольку емкостью, которая паразитирует на резистивном элементе Rp, формируется фильтр. Эта емкость может представлять собой паразитную емкость, созданную не только резистивным элементом Rp, но также межсоединениями, транзистором MD1 или подобным. Если напряжение Vb вводит большую задержку, чем перенапряжение Vsur, задавая разность потенциалов между двумя выводами емкостного элемента Ca, равную или выше напряжения, которое разрушает емкостный элемент Ca, изолирующая пленка 304 затвора емкостного элемента Ca подвергается пробою изоляции. Таким образом, информация может быть записана в элемент проводящего мостика с помощью ESD.

[0034] Между тем, если прикладывается высокое перенапряжение Vsur, при ESD, к линии 111 напряжения полупроводникового устройства 300, показанного на фиг. 3, с высокой скоростью, паразитные емкости Cgd1 и Cds1 транзистора 104 и паразитная емкость Cgd2 транзистора 103 осуществляют емкостную связь и работают в качестве емкостей связи. Следовательно, паразитная емкость Cgs2 затвор-исток транзистора 103 заряжается, включая транзистор 103. В результате через линию 112 напряжения транзистора 103 протекает ток перегрузки, предотвращая протекание тока перегрузки через внутреннюю цепь. Это позволяет предотвращать запись информации в емкостный элемент Ca, который образует элемент проводящего мостика.

[0035] Емкостный элемент Ca, который образует элемент проводящего мостика, используется при приложении высокого напряжения VH и вызывании пробоя изоляции изолирующих пленок 304 затворов. Следовательно, он образуется с помощью выдерживающего низкое напряжение элемента. Если используется схема защиты, использующая транзистор с тем же самым напряжением пробоя, как у транзисторов MP1 и MN1, схема защиты разрушается при приложении перенапряжения. Следовательно, схема защиты не работает, и, помимо этого, разрушается емкостный элемент Ca. Таким образом, выдерживающая низкое напряжение схема защиты не имеет эффекта. Следовательно, как описано в этом варианте осуществления, требуется выдерживающая высокое напряжение схема защиты, использующая DMOS-транзисторы, аналогичные транзисторам 103 и 104. Емкостный элемент Ca используется при приложении высокого напряжения VH и вызывании пробоя, и в силу этого схема защиты не должна работать для постоянного напряжения, а должна работать только для сигнала переменного тока. Соответственно, схема защиты элемента проводящего мостика имеет высокое напряжение пробоя, и требуется схема, которая работает для высокоскоростного перенапряжения. Образованная полупроводниковым устройством 100 схема защиты, показанная на фиг. 1 и встроенная в полупроводниковое устройство 300, имеет высокое напряжение пробоя и работает только для высокоскоростного перенапряжения, имеющего эффект в качестве схемы защиты элемента проводящего мостика.

[0036] Как описано выше, при использовании полупроводникового устройства 300, описанного в этом варианте осуществления, можно предотвращать ошибочную запись, производимую ESD в емкостный элемент Ca, который образует элемент проводящего мостика.

[0037] Со ссылкой на фиг. 6 будет описана структура подложки головки выброса жидкости согласно варианту осуществления настоящего изобретения. Фиг. 6 является принципиальной схемой, показывающей компоновку схемы подложки 600 головки выброса жидкости согласно третьему варианту осуществления настоящего изобретения. Подложка 600 головки выброса жидкости включает в себя нагревательный элемент 601, транзистор 602, схему 603 управления и ту же самую компоновку схемы, как у полупроводникового устройства 300 по вышеописанному второму варианту осуществления. Нагревательный элемент 601 предоставляет энергию при нагреве жидкости, служащей в качестве печатающего материала, и выбрасывает жидкость из сопла. Нагревательный элемент 601 может предоставлять собой теплообразующий элемент, который предоставляет энергию жидкости при нагреве. Дополнительно, вместо нагревательного элемента 601 может использоваться пьезоэлектрический элемент, который предоставляет энергию жидкости, служащей в качестве печатающего материала, при деформации. На фиг. 6, нагревательный элемент 601 проиллюстрирован как резистивный элемент, который предоставляет тепловую энергию жидкости. Транзистор 602 выполнен с возможностью возбуждать нагревательный элемент 601. Схема 603 управления управляет выбросом жидкости за счет управления транзистором 602. Один вывод нагревательного элемента 601 подключен к высокому напряжению VH, такому как линия 111 напряжения, а другой вывод соединен с первичным выводом (стоком) транзистора 602. Другой первичный вывод (исток) транзистора 602 подключен к линии 112 напряжения, и подается потенциал земли. Управляющий вывод (затвор) транзистора 602 соединен со схемой 603 управления. Схема 603 управления подключена к напряжению VDD источника питания логики. Другие элементы, которые образуют схему, могут быть теми же самыми, как в вышеописанном втором варианте осуществления.

[0038] Транзистор 602 подключен к высокому напряжению VH, аналогично транзисторам 103, 104 и MD1, и в силу этого используется DMOS-транзистор, имеющий более высокое напряжение пробоя, чем транзисторы MP1 и MN1. Аналогично транзисторам 103, 104 и MD1, транзистор 602 может представлять собой LDMOS-транзистор. Дополнительно, аналогично транзисторам 103, 104 и MD1, транзистор 602 может иметь смещенную LOCOS-структуру.

[0039] Между тем, включенная в схему 603 управления схема подключена к общему напряжению VDD источника питания логики с помощью транзисторов MP1 и MN1, и в силу этого может использовать обычный транзистор. Следовательно, каждый из транзисторов 103, 104, MD1 и 602 может иметь более высокое напряжение пробоя, чем включенный в схему 603 управления транзистор.

[0040] Как описано выше, исток и нижний затвор транзистора MP1 и схема 603 управления подключены к общему напряжению VDD источника питания логики. Соответственно, все изолирующие пленки затворов транзисторов MP1 и MN1 и транзистора, который образует схему 603 управления, могут быть образованы на одном и том же этапе. Дополнительно, все транзисторы 103 и 104, которые образуют схему защиты, транзистор MD1, который управляет записью в элементе проводящего мостика, и транзистор 602, выполненный с возможностью возбуждать нагревательный элемент 601, могут использовать LDMOS-транзисторы. В этом случае изолирующие пленки затворов транзисторов 103, 104, MD1 и 602 и емкостного элемента Ca могут быть образованы на том же самом этапе, как изолирующие пленки затворов транзисторов MP1 и MN1, как описано выше. Таким образом, изолирующие пленки затворов транзисторов 103, 104, MD1, 602, MP1 и MN1 и емкостный элемент Ca могут иметь одинаковую толщину. Как описано выше, в транзисторах 103, 104, MD1 и 602, транзисторах MP1 и MN1 и емкостном элементе Ca могут использоваться области кармана и диффузионные области, каждая из которых имеет общую концентрацию примесей. Появляется возможность, при использовании описанной в этом варианте осуществления компоновки, устанавливать элемент проводящего мостика и схему защиты элемента проводящего мостика на подложке головки выброса жидкости при подавлении увеличения числа этапов в процессе изготовления.

[0041] Выше примерно проиллюстрированы три варианта осуществления согласно настоящему изобретению. Однако, настоящее изобретение не ограничено этими вариантами осуществления. Вышеописанные варианты осуществления могут надлежащим образом модифицироваться и комбинироваться без отступления от объема настоящего изобретения.

[0042] Хотя настоящее изобретение описано со ссылкой на примерные варианты осуществления, следует понимать, что это изобретение не ограничено раскрытыми примерными вариантами осуществления. Объем прилагаемой формулы изобретения должен соответствовать самой широкой интерпретации с тем, чтобы заключать в себе все такие модификации и эквивалентные структуры, и функции.

Предоставлено полупроводниковое устройство. Устройство содержит: первый транзистор, который включает в себя первый первичный вывод, второй первичный вывод и первый управляющий вывод; второй транзистор, который включает в себя третий первичный вывод, четвертый первичный вывод и второй управляющий вывод; и резистивный элемент. Первый и третий первичный выводы подключены к первой линии напряжения. Второй первичный вывод и один вывод резистивного элемента подключены ко второй линии напряжения. Первый и второй управляющие выводы, четвертый первичный вывод и другой вывод резистивного элемента соединены в узел. Изменение потенциала в третьем первичном выводе передается на первый управляющий вывод за счет емкостной связи между третьим первичным выводом и упомянутым узлом, включая первый транзистор. 3 н. и 24 з.п. ф-лы, 6 ил.

1. Полупроводниковое устройство, содержащее:

первый транзистор, который включает в себя первый первичный вывод, второй первичный вывод и первый управляющий вывод;

второй транзистор, который включает в себя третий первичный вывод, четвертый первичный вывод и второй управляющий вывод; и

первый резистивный элемент,

при этом первый первичный вывод и третий первичный вывод подключены к первой линии напряжения,

второй первичный вывод и один вывод первого резистивного элемента подключены ко второй линии напряжения,

первый управляющий вывод, второй управляющий вывод, четвертый первичный вывод и другой вывод первого резистивного элемента соединены друг с другом с образованием одного узла,

изменение потенциала в третьем первичном выводе передается на первый управляющий вывод через емкостную связь между третьим первичным выводом и упомянутым одним узлом,

передаваемое изменение потенциала на первом управляющем выводе включает первый транзистор,

при этом полупроводниковое устройство дополнительно содержит:

емкостный элемент, который включает в себя подключенный к первой линии напряжения первый вывод и второй вывод;

третий транзистор, который включает в себя соединенный со вторым выводом пятый первичный вывод, подключенный ко второй линии напряжения шестой первичный вывод и третий управляющий вывод; и

блок возбуждения, образованный по меньшей мере одним транзистором, который включает в себя четвертый транзистор, и выполненный с возможностью вызывать пробой изоляции емкостного элемента при подаче управляющего сигнала на третий управляющий вывод, и

при этом третий транзистор имеет более высокое напряжение пробоя, чем четвертый транзистор.

2. Устройство по п. 1, в котором каждый из первого транзистора и второго транзистора является DMOS-транзистором (на основе МОП-структуры с двойной диффузией).

3. Устройство по п. 2, в котором каждый из первого транзистора и второго транзистора является LDMOS-транзистором (на основе МОП-структуры с поперечной диффузией).

4. Устройство по п. 1, в котором каждый из первого транзистора и второго транзистора имеет смещенную LOCOS-структуру (с локальным оксидированием кремния).

5. Устройство по п. 1, в котором каждый из первого транзистора и второго транзистора включает в себя

первую полупроводниковую область первого типа проводимости, расположенную в полупроводниковой подложке,

вторую полупроводниковую область второго типа проводимости, расположенную смежно с первой полупроводниковой областью в полупроводниковой подложке,

область истока второго типа проводимости, расположенную в первой полупроводниковой области,

область стока второго типа проводимости, расположенную во второй полупроводниковой области,

электрод затвора, который включает в себя расположенный над первой полупроводниковой областью первый участок и расположенные над второй полупроводниковой областью второй участок и третий участок, и

изолирующую пленку, которая включает в себя расположенный между первым участком и первой полупроводниковой областью четвертый участок, имеющий первую толщину, расположенный между вторым участком и второй полупроводниковой областью пятый участок, имеющий первую толщину, и расположенный между третьим участком и второй полупроводниковой областью шестой участок, имеющий вторую толщину, превышающую первую толщину.

6. Устройство по п. 1, в котором первый транзистор и второй транзистор имеют более высокое напряжение пробоя, чем четвертый транзистор.

7. Устройство по п. 1, в котором третий транзистор является DMOS-транзистором.

8. Устройство по п. 7, в котором третий транзистор является LDMOS-транзистором.

9. Устройство по п. 1, в котором третий транзистор имеет смещенную LOCOS-структуру.

10. Устройство по п. 1, в котором емкостный элемент имеет MOS-структуру, а

изолирующая пленка затвора первого транзистора, изолирующая пленка затвора второго транзистора, изолирующая пленка затвора третьего транзистора, изолирующая пленка затвора четвертого транзистора и изолирующая пленка, которая образует емкостный элемент, равны друг другу по толщине.

11. Устройство по п. 1, дополнительно содержащее подключенный между первой линией напряжения и вторым выводом второй резистивный элемент.

12. Устройство по п. 1, дополнительно содержащее соединенную с четвертым транзистором линию напряжения источника питания логики,

при этом потенциал линии напряжения источника питания логики находится между потенциалом первой линии напряжения и потенциалом второй линии напряжения.

13. Устройство по п. 1, в котором второй транзистор включает в себя емкость p-n-перехода, которая имеет зависимость от напряжения.

14. Устройство по п. 5, в котором первая полупроводниковая область и вторая полупроводниковая область составляют емкость p-n-перехода, которая имеет зависимость от напряжения.

15. Устройство по п. 5, дополнительно содержащее электропроводку, причем электропроводка соединяет область истока, электрод затвора и первую полупроводниковую область друг с другом.

16. Устройство по п. 1, в котором

при приложении перенапряжения к первой линии напряжения возрастает напряжение между первым выводом и вторым выводом емкостного элемента и первый транзистор включается до возникновения пробоя изоляции емкостного элемента.

17. Подложка головки выброса жидкости, содержащая:

полупроводниковое устройство по п. 1;

нагревательный элемент, выполненный с возможностью нагревать жидкость; и

пятый транзистор, выполненный с возможностью возбуждать нагревательный элемент.

18. Подложка головки выброса жидкости, содержащая:

полупроводниковое устройство;

нагревательный элемент, выполненный с возможностью нагревать жидкость; и

пятый транзистор, выполненный с возможностью возбуждать нагревательный элемент,

при этом полупроводниковое устройство содержит:

первый транзистор, который включает в себя первый первичный вывод, второй первичный вывод и первый управляющий вывод;

второй транзистор, который включает в себя третий первичный вывод, четвертый первичный вывод и второй управляющий вывод;

первый резистивный элемент;

емкостный элемент, который включает в себя первый вывод и второй вывод;

третий транзистор, который включает в себя соединенный со вторым выводом пятый первичный вывод, шестой первичный вывод и третий управляющий вывод; и

блок возбуждения, образованный по меньшей мере одним транзистором, который включает в себя четвертый транзистор, и выполненный с возможностью вызывать пробой изоляции емкостного элемента при подаче управляющего сигнала на третий управляющий вывод,

при этом первый первичный вывод, третий первичный вывод и первый вывод подключены к первой линии напряжения,

второй первичный вывод, один вывод первого резистивного элемента и шестой первичный вывод подключены ко второй линии напряжения,

первый управляющий вывод, второй управляющий вывод, четвертый первичный вывод и другой вывод первого резистивного элемента соединены друг с другом с образованием одного узла,

изменение потенциала в третьем первичном выводе передается на первый управляющий вывод через емкостную связь между третьим первичным выводом и упомянутым одним узлом,

передаваемое изменение потенциала включает первый транзистор, и

при этом пятый транзистор имеет более высокое напряжение пробоя, чем четвертый транзистор.

19. Подложка по п. 18, в которой четвертый транзистор и пятый транзистор равны друг другу по толщине изолирующей пленки затвора.

20. Подложка по п. 18, в которой пятый транзистор является DMOS-транзистором.

21. Подложка по п. 20, в которой пятый транзистор является LDMOS-транзистором.

22. Подложка по п. 18, в которой пятый транзистор имеет смещенную LOCOS-структуру.

23. Подложка по п. 18, в которой каждый из первого транзистора и второго транзистора включает в себя

первую полупроводниковую область первого типа проводимости, расположенную в полупроводниковой подложке,

вторую полупроводниковую область второго типа проводимости, расположенную смежно с первой полупроводниковой областью в полупроводниковой подложке,

область истока второго типа проводимости, расположенную в первой полупроводниковой области,

область стока второго типа проводимости, расположенную во второй полупроводниковой области,

электрод затвора, который включает в себя расположенный над первой полупроводниковой областью первый участок и расположенные над второй полупроводниковой областью второй участок и третий участок, и

изолирующую пленку, которая включает в себя расположенный между первым участком и первой полупроводниковой областью четвертый участок, имеющий первую толщину, расположенный между вторым участком и второй полупроводниковой областью пятый участок, имеющий первую толщину, и расположенный между третьим участком и второй полупроводниковой областью шестой участок, имеющий вторую толщину, превышающую первую толщину.

24. Подложка по п. 18, дополнительно содержащая соединенную с четвертым транзистором линию напряжения источника питания логики,

при этом потенциал линии напряжения источника питания логики находится между потенциалом первой линии напряжения и потенциалом второй линии напряжения.

25. Подложка по п. 18, в которой второй транзистор включает в себя емкость p-n-перехода, которая имеет зависимость от напряжения.

26. Подложка по п. 23, в которой первая полупроводниковая область и вторая полупроводниковая область составляют емкость p-n-перехода, которая имеет зависимость от напряжения.

27. Подложка по п. 23, дополнительно содержащая электропроводку, причем электропроводка соединяет область истока, электрод затвора и первую полупроводниковую область друг с другом.

| US 7910950 B1, 22.03.2011 | |||

| US 20140078223 A1, 20.03.2014 | |||

| WO 2008155729 A1, 24.12.2008 | |||

| US 20100232081 A1, 16.09.2010. |

Авторы

Даты

2019-02-12—Публикация

2017-04-06—Подача