Область техники

Изобретение относится к электронной и оптоэлектронной технике и может быть использовано для изготовления монолитных интегральных схем, работающих в сантиметровом и миллиметровом диапазоне длин волн, а также для изготовления вертикально-излучающих лазеров ближнего инфракрасного диапазона.

Уровень техники

Для формирования электродов на поверхности заглубленных слоев полупроводниковых гетероструктур необходимо проведение процессов локального прецизионного травления. Для обеспечения процессов локального прецизионного травления используются так называемые «стоп-слои», которые представляют собой эпитаксиальные слои с отличающимся от нижележащих и вышележащих слоев химическим составом, скорость травления которых выбранным травящем раствором значительно меньше скорости травления вышележащих слоев. Существенным аспектом при формировании гетероструктур со стоп-слоями является способ формирования стоп-слоев, который должен обеспечить изготовление атомарно гладких и однородных по химическому составу стоп-слоев, имеющих одинаковую толщину по всей поверхности создаваемой полупроводниковой пластины, обеспечивающих нанометровую точность глубины травления. Высочайшая точность глубины травления в настоящее время один из ключевых параметров технологии изготовления затвора транзисторов для современных монолитных интегральных микросхем.

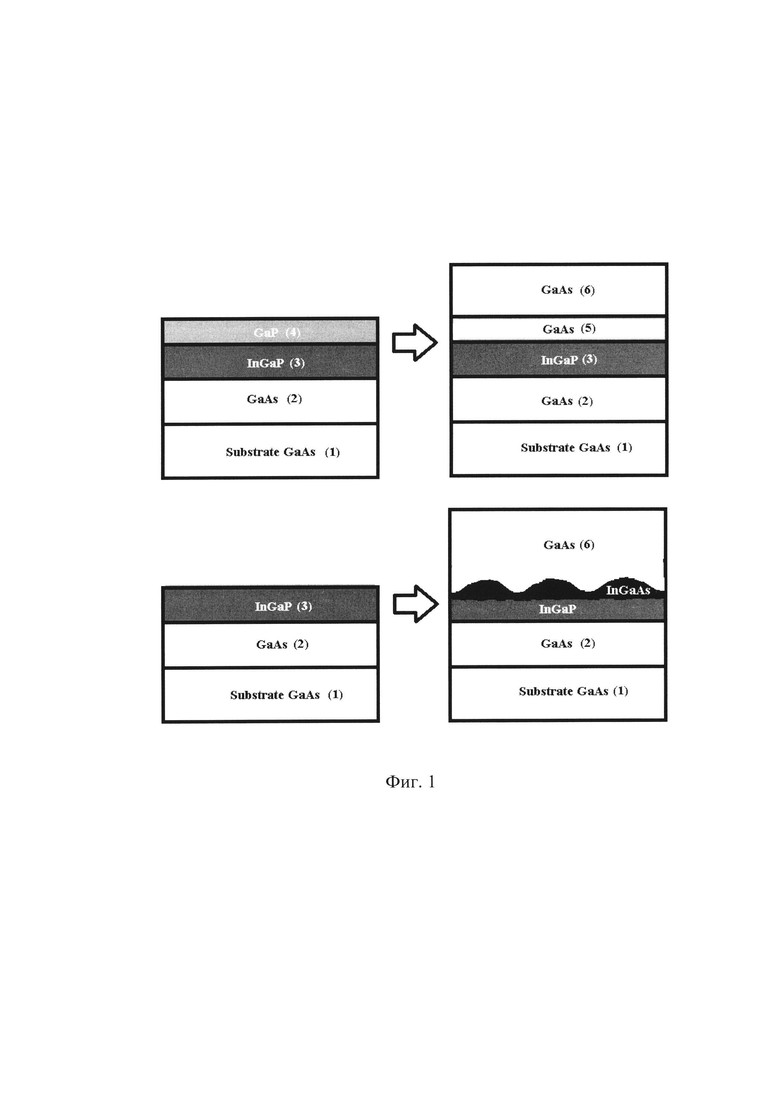

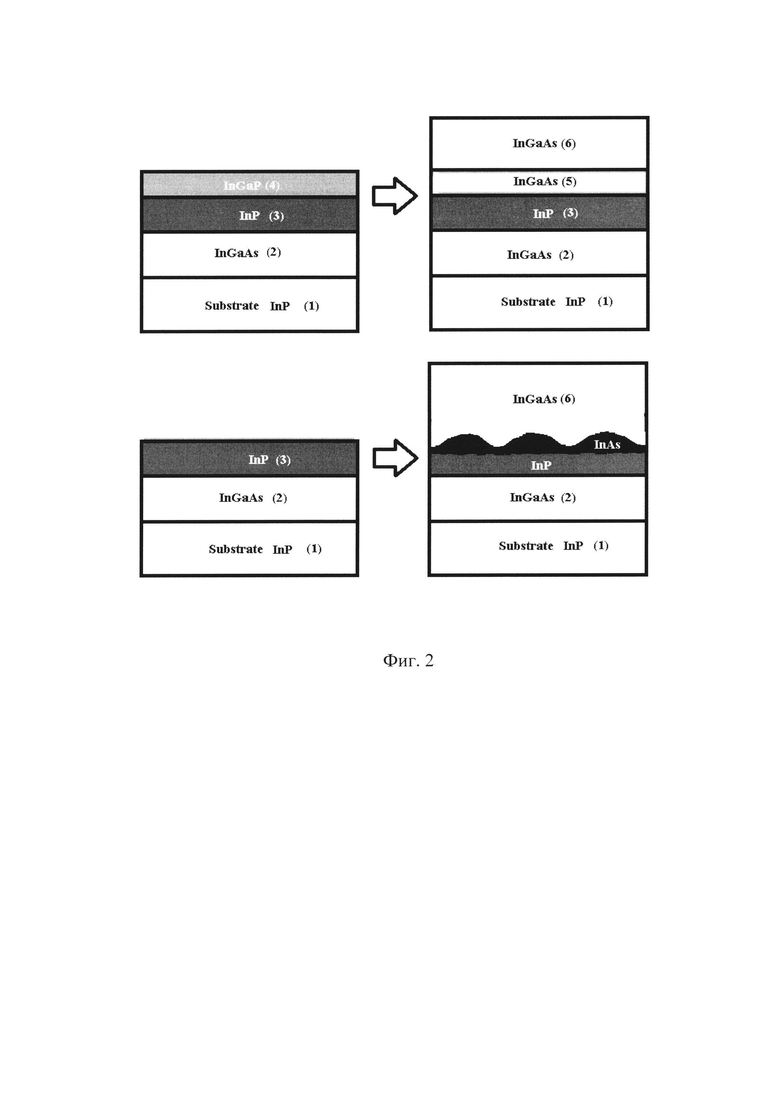

В транзисторных и оптоэлектронных гетероструктурах на подложке GaAs используют фосфорсодержащие стоп-слои из AlGaP [1], InAlP [1], InGaP [2,3,4,5]. Наличие фосфора в стоп-слое позволяет применять селективное жидкостное травление для формирования на поверхности гетероструктуры профиля прецизионной глубины для создания электродов на поверхности заглубленных слоев гетероструктур. Выполнение стоп-слоя InyGa1-yP описано в [6]. Указано, что формирование стоп-слоя InyGa1-yP толщиной как менее 2 нм, так и более 4 нм недопустимо, в первом случае из-за его функциональной неэффективности, во втором - из-за увеличения плотности дефектов в полупроводниковой гетероструктуре и увеличения толщины области под электродом затвора полевого транзистора, что, соответственно, приводит к снижению выхода годных и выходной мощности. При отсутствии источника фосфора в эпитаксиальной установке используются стоп-слои из AlAs [7,8,9,10] либо стоп-слои из AlxGa1-xAs с х≥0.3 [11,12,13,14,15]. При выращивании на подложках InP арсенидных гетероструктур в качестве стоп-слоев используют InP [16]. При условии, что основная гетероструктура представляет собой набор мышьяксодержащих слоев, стоп-слои на основе фосфорсодержащих соединений наиболее предпочтительны, так как гарантированно обеспечивают высокую селективность травления за счет замены элемента пятой группы (мышьяка) на фосфор. Стоп-слои на основе фосфорсодержащих соединений не подвержены окислению при химической обработке гетероструктур и не создают дополнительных существенных и нежелательных скачков потенциала на гетерограницах. Химический состав стоп-слоев выбирается так, чтобы параметр кристаллической решетки стоп-слоев совпадал с параметров кристаллической решетки подложки. Например, In0.51Ga0.49P для подложки GaAs. Основной проблемой при реализации стоп-слоев на основе фосфорсодержащих соединений в составе гетероструктур, состоящих из слоев арсенидов, является нарушение планарности верхних гетерограниц стоп-слоев и формирование на поверхности трехмерного рельефа из островков, обогащенных арсенидом индия. Такое явление объясняется частичным замещением фосфора, который испаряется из стоп-слоя, на мышьяк во время замены внешнего потока элемента пятой группы с фосфора на мышьяк для выращивания покрывающего слоя из арсенида галлия, индия, алюминия. В результате химический состав верней части стоп-слоя изменяется, превращаясь из фосфида в арсенид, и на поверхности полупроводниковой пластины непреднамеренно образуется слой арсенида с большей постоянной решетки, чем у материала подложки, поскольку химический состав слоя заранее выбирается так, чтобы полное согласование кристаллических решеток возникало, когда стоп-слой состоит только из фосфида. Затем при достижении критической толщины верхней модифицированной части стоп-слоя, 1.0-1.5 нм, происходит деформация поверхности под действием возникших упругих напряжений и на поверхности возникает трехмерный рельеф, состоящий из островков, обогащенных арсенидом индия. Схематически такая нежелательная трансформация показана на фиг. 1 и фиг. 2 в нижней части рисунков. Дополнительно, во время эпитаксии на больших пластинах (диаметром 76 мм и более) возможный градиент температуры поверхности подложки может усугублять описанный выше процесс в отдельных областях пластины. В результате выход годных приборов с эпитаксиальной пластины может быть существенно уменьшен.

Раскрытие изобретения

Задачей предлагаемого изобретения является контролируемое формирования атомарно гладких (планарных) и однородных по химическому составу стоп-слоев из фосфорсодержащих полупроводниковых соединений и твердых растворов, обеспечивающих прецизионный контроль глубины травления при формировании электродов на поверхности заглубленных слоев арсенидных гетероструктур, сформированных на поверхности подложек GaAs и InP, и повышение выхода годных приборов с эпитаксиальной пластины.

Техническим результатом, позволяющим выполнить поставленную задачу формирования атомарно гладких (планарных) и однородных по химическому составу стоп-слоев, является создание полупроводниковой модифицированной гетероструктуры со стоп-слоем InGaP (3), в состав которой вводится дополнительный защитный слой GaP (4) (см. фиг. 1), в случае эпитаксии на подложке GaAs (1) с буферным слоем GaAs (2), и модифицированной полупроводниковой гетероструктуры со стоп-слоем InP (3) (см. фиг. 2), в состав которой входит вводится дополнительный защитный слой InGaP (4), в случае эпитаксии на подложке InP (1). Под стоп-слоем подразумевается полупроводниковый слой в составе гетероструктуры, скорость травления которого, выбранным травящем раствором, значительно меньше скорости травления вышележащих слоев, отличающихся от стоп-слоя химическим составом. Перед заращиванием покрывающими слоями, состоящими из арсенидов (например, GaAs (6) (см. фиг. 1) или InGaAs (6) (см. фиг. 2)), защитный слой GaP (4), в случае эпитаксии на подложке GaAs, конвертируется в слой GaAs (5), а защитный слой InGaP (4), в случае эпитаксии на подложке InP, конвертируется в слой InGaAs (5). Такая конвертация происходит во время остановки эпитаксии для замены внешнего потока элемента пятой группы с фосфора на мышьяк для выращивания покрывающего слоя из арсенида галлия, арсенида индия, арсенида алюминия. В результате такой конвертации образуются слои с такой же постоянной кристаллической решетки, что и у материала подложки, поэтому никаких дополнительных упругих напряжений не возникает и поверхность не деформируется. Таким образом, формируются гетероструктуры с атомарно гладкими и однородными по всей площади пластины фосфорсодержащими стоп-слоями.

Краткое описание чертежей

На фиг. 1, в верхней части, изображена схема модифицированной полупроводниковой гетероструктуры со стоп-слоем InGaP (3), в состав которой входит дополнительный защитный слой GaP(4), на подложке GaAs (1) с буферным слоем из GaAs (2) до и после заращивания покрывающим слоем GaAs (6), относящейся к настоящему изобретению. После заращивания покрывающим слоем GaAs (6), защитный слой GaP(4) превращается в потоке As в слой GaAs (5).

Для сравнения, в нижней части, показано изображение традиционной гетероструктуры со стоп-слоем InGaP (3), при реализации которой защитный слой GaP (4) не использовался, до и после заращивания покрывающим слоем GaAs (6).

На фиг. 2, в верхней части, изображена схема модифицированной полупроводниковой гетероструктуры с стоп-слоем InP (3), в состав которой входит дополнительный защитный слой InGaP(4), на подложке InP (1) с буферным слоем из InGaAs (2) до и после заращивания покрывающим слоем InGaAs (6), относящейся к настоящему изобретению. После заращивания покрывающим слоем InGaAs (6), защитный слой InGaP (4) в потоке As превращается в слой InGaAs (5).

Для сравнения, в нижней части, показано изображение традиционной гетероструктуры со стоп-слоем InP (3), при реализации которой защитный слой InGaP (4) не использовался, до и после заращивания покрывающим слоем InGaAs (6).

Осуществление изобретения

Выращивание модифицированных полупроводниковых гетероструктур со стоп-слоями InGaP и InP на подложках GaAs и InP осуществляется методом молекулярно-пучковой эпитаксии.

В случае выращивания модифицированной полупроводниковой гетероструктуры со стоп-слоем InGaP, в состав которой входит защитный слой GaP, на подложке GaAs осуществляется последовательное выращивание слоев InGaP и GaP. При этом толщина защитного слоя GaP должна быть не менее 0.6 нм для обеспечения надежности защиты слоя InGaP от взаимодействия с потоком As и не более 1.3 нм для обеспечения полной конвертации слоя GaP в слой GaAs в потоке As. После выращивания слоя GaP поток фосфора закрывается, а поток мышьяка открывается, и поверхность выдерживается в потоке мышьяка 3-10 мин при температуре 450-550°С. Затем осуществляется заращивание покрывающим слоем GaAs.

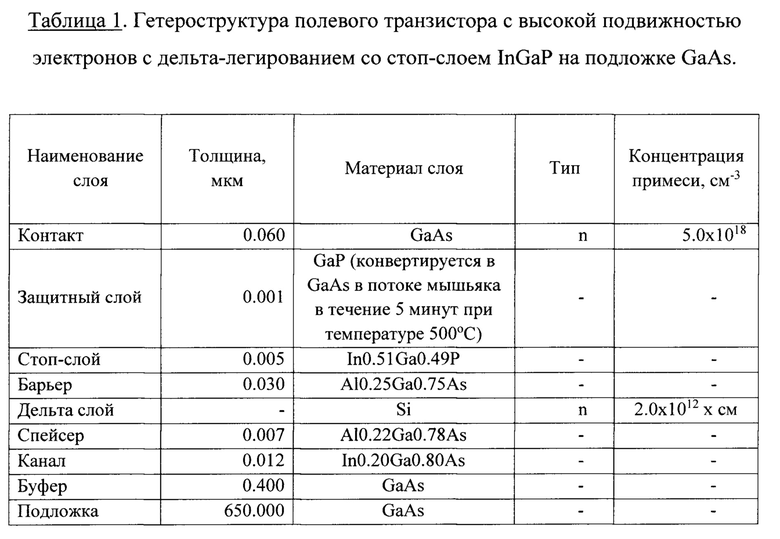

В течение 3-10 мин, при указанных температурах, происходит полная замена фосфора на мышьяк. Время также зависит и от выбранного потока мышьяка. При скорости выращивания GaAs равной 0.8 мкм/час и потоке мышьяка, который обеспечивает соотношение потоков элементов пятой и третьей групп равное 4, полная замена происходит в течение 5-6 минут. Приведенный диапазон температур обеспечивает хорошо контролируемое время протекание реакции и формирование атомарно плоской поверхности кристалла. Повышенные температуры ускоряют реакции и могут приводить к формированию шероховатой поверхности кристалла. Пример изготовления гетеростуктуры полевого транзистора с высокой подвижностью электронов приведен в нижеследующей таблице.

В случае выращивания модифицированной полупроводниковой гетероструктуры со стоп-слоем InP, в состав которой входит защитный слой InGaP, на подложке InP осуществляется последовательное выращивание слоев InP и InGaP. При этом толщина защитного слоя InGaP должна быть не менее 0.6 нм для обеспечения надежности защиты слоя InP от взаимодействия с потоком As и не более 1.3 нм для обеспечения полной конвертации слоя InGaP в слой InGaAs в потоке As. После выращивания слоя InGaP, поток фосфора закрывается, а поток мышьяка открывается, и поверхность выдерживается в потоке мышьяка 3-10 мин при температуре 450-510°С. Затем осуществляется заращивание покрывающим слоем InGaAs.

Процесс осуществляется при пониженных температурах, чтобы избежать разложения слоев, содержащих индий.

Источники информации

[1] Patent US 7538365 В2. Field effect transistor and phosphorus etch stop layer / Matthew Francis O'Keefe, Michael Charles Clausen, Richard Alun Davies, Robert Grey; Filtronic PLC. - Appl. No. 11/153785; filling date 15.06.2005; publication date 26.05.2009.

[2] Patent US 20020176464 A1. InGaP etch stop / Oleg Smolski; Jeff Bullington. - Appl. No. 10/104,574; filling date 22.03.2001; publication date 28.11.2002.

[3] Patent US 8288260 B1. Field effect transistor with dual etch-stop layers for improved power, performance and reproducibility/Allen W. Hanson; M/A-COM Technology Solutions Holdings, Inc. - Appl. N13/173015; filling date 30.06.2011; publication date 16.10.2012.

[4] Patent US 6307221 B1. InxGa1-xP etch stop layer for double recess pseudomorphic high electron mobility transistor structures / David Danzilio; The Whitaker Corporation. - Appl. No. 09/195478; filling date 18.11.1998; publication date 23.18.2001.

[5] Патент 2463685 РФ. Интегральный полевой транзистор с размерным квантованием энергии / Воробьев А.А., Галдецкий А.В., Лапин В.Г.; заявитель и патентообладатель Федеральное государственное унитарное предприятие «Научно-производственное предприятие «Исток» (ФГУП НГШ «Исток»). -№2011123071/28; заявл. 07.06.11; опубл. 10.10.12, Бюл. №28.

[6] Патент 2563544 РФ. Полупроводниковая гетероструктура/ Бажинов А.Н., Обручников А.Е., Духновский М.П., Яцюк Ю.А., Пехов Ю.П.; заявитель и патентообладатель Акционерное общество "Научно-производственное предприятие "Исток" имени А.И. Шокина" (АО "НПП "Исток" им. Шокина").

[7] Patent US 5175740. Semiconductor laser and method of fabricating same / Boris S. Elman, Wayne F. Sharfin; GTE Laboratories Inc. - Appl. N734827; filling date 24.07.1991; publication date 19.12.1992.

[8] Patent US 8610173 B2. Enhancement/depletion PHEMT device / Alessandro Chini, Claudio Lanzieri; Selex Sistemi Integrati S.p.A. - Appl. N13/561860; filling date 30.07.2012; publication date 17.12.2013.

[9] Patent US 2010/0218819 A1. Semiconductor optoelectronic devices and methods for making semiconductor optoelectronic devices / Corrie Farmer, Colin Stanley; The University Court of the University of Glasgow. - Appl. N12/681390; filling date 06.10.2008; publication date 02.09.2010.

[10] Patent US 7678629 B1. Method for fabricating a recessed ohmic contact for a PHEMT structure / Jerod F. Mason, Dylan C. Bartle; Skyworks Solutions, Inc. - Appl. N11/827001; filling date 09.07.2007; publication date 16.03.2010.

[11] Патент 2582440 РФ. Полупроводниковая транзисторная наногетероструктура на подложке gaas с модифицированным стоп-слоем AlxGal-xAs / Хабибуллин Р.А., Пушкарев С.С, Клочков А.Н., Галиев Г.Б., Пономарев Д.С, Климов Е.А.; заявитель и патентообладатель Федеральное государственное бюджетное учреждение науки Институт сверхвысокочастотной полупроводниковой электроники Российской академии наук (ИСВЧПЭ РАН). - №2015104011; заявл. 06.02.15; зарегистр. 01.04.16.

[12] Patent US 6110393. Epoxy bond and stop etch fabrication method / Jerry A. Simmons, Mark V. Weckwerth, Wes E. Baca; Sandia Corporation. - Appl. N09/066091; filling date 23.04.1998; publication date 29.08.2000.

[13] Patent US 5420066. Method for producing semiconductor laser device using etch stop layer / Akibiro Shima, Takeshi Miura, Tomoko Kadowaki, Norio Hayafuji; Mitsubishi Denki Kabushiki Kaisha. - Appl. N267211; filling date 06.07.1994; publication date 30.05.1995.

[14] Patent US 5357535. Semiconductor laser including an aluminium-rich AlGaAs etch stopping layer / Akibiro Shima, Takeshi Miura, Tomoko Kadowaki, Norio Hayafuji; Mitsubishi Denki Kabushiki Kaisha. - Appl. N1547; filling date 06.01.1993; publication date 18.10.1994.

[15] J.K. Abrokwah et al. High-performance self-aligned p+/n GaAs epitaxial JFET's incorporating AlGaAs etch-stop layer // IEEE Transactions on Electron Devices. - 1990. - Vol. 37, N6. - P. 1529.

[16] Patent US 4,873,558. Group III-V compound field effect transistor with diffusion barrier / Arsam Antreasyan, Fanwood; Paul A. Garbinski, New Providence; Vincent D. Mattera, Jr., Flemington; Henryk Temkin, Berkeley Heights.- Appl. No. 159,156; filling date Feb. 23, 1988; Date of Patent: Oct. 10, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВАЯ ТРАНЗИСТОРНАЯ НАНОГЕТЕРОСТРУКТУРА НА ПОДЛОЖКЕ GaAs С МОДИФИЦИРОВАННЫМ СТОП-СЛОЕМ AlGaAs | 2015 |

|

RU2582440C1 |

| Наноразмерная структура с профилем легирования в виде нанонитей из атомов олова | 2016 |

|

RU2650576C2 |

| Мезаструктурный фотодиод на основе гетероэпитаксиальной структуры InGaAs/AlInAs/InP | 2016 |

|

RU2627146C1 |

| ЛАВИННЫЙ ФОТОДИОД И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2021 |

|

RU2769749C1 |

| Материал на основе InGaAs на подложках InP для фотопроводящих антенн | 2016 |

|

RU2657306C2 |

| МАТЕРИАЛ ДЛЯ ФОТОПРОВОДЯЩИХ АНТЕНН | 2015 |

|

RU2610222C1 |

| СВЕТОДИОД БЕЛОГО СВЕЧЕНИЯ И СВЕТОДИОДНАЯ ГЕТЕРОСТРУКТУРА НА ОСНОВЕ ПОЛУПРОВОДНИКОВЫХ ТВЕРДЫХ РАСТВОРОВ GaPAsN НА ПОДЛОЖКАХ GaP И Si | 2013 |

|

RU2548610C2 |

| Способ изготовления гетероструктуры полупроводникового лазера ближнего инфракрасного диапазона с безалюминиевой активной областью | 2023 |

|

RU2836258C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ФОТОЭЛЕКТРИЧЕСКОГО ПРЕОБРАЗОВАТЕЛЯ ЛАЗЕРНОГО ИЗЛУЧЕНИЯ | 2022 |

|

RU2791961C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЕТОИЗЛУЧАЮЩЕЙ СТРУКТУРЫ И СВЕТОИЗЛУЧАЮЩАЯ СТРУКТУРА | 2004 |

|

RU2257640C1 |

Изобретение относится к электронной и оптоэлектронной технике и может быть использовано для изготовления монолитных интегральных схем, работающих в сантиметровом и миллиметровом диапазонах длин волн, а также для изготовления вертикально-излучающих лазеров ближнего инфракрасного диапазона. Согласно изобретению описан способ изготовления полупроводниковых гетероструктур с атомарно гладкими стоп-слоями InGaP и InP на подложках GaAs и InP и предложены конструкции полупроводниковых гетероструктур, обеспечивающие формирование атомарно гладких стоп-слоев. Изобретение обеспечивает устойчивое формирование атомарно гладких фосфорсодержащих стоп-слоев InGaP и InP в слоях твердых растворов, состоящих из арсенидов индия и галлия, не оказывает негативного влияния на параметры изготавливаемых приборов. Для устойчивого формирования атомарно гладкого стоп-слоя InGaP в гетероструктурах на подложках GaAs выращивают буферный слой GaAs, затем последовательно слой InGaP и защитный слой GaP толщиной 0,6-1,3 нм и лишь затем выращивается покрывающий слой арсенида. Для устойчивого формирования атомарно гладкого стоп-слоя InP в гетероструктурах на подложках InP выращивают буферный слой InGaAs, затем слой InP и защитный слой InGaP толщиной 0,6-1,3 нм и лишь затем выращивается покрывающий слой арсенида. Формирование стоп-слоев описанным способом обеспечивает формирование атомарно гладких фосфорсодержащих стоп-слоев InGaP и InP в слоях твердых растворов, состоящих из арсенидов индия и галлия, и точный контроль глубины травления по всей площади эпитаксиальной пластины при изготовлении приборов электронной и оптоэлектронной техники. 2 з.п. ф-лы, 2 ил., 1 табл.

1. Способ изготовления полупроводниковых гетероструктур с атомарно гладкими стоп-слоями, включающий:

- изготовление полупроводниковых гетероструктур на подложках GaAs или InP,

- выращивание на подложке GaAs буферного слоя GaAs или на подложке InP буферного слоя InGaAs,

- выращивание на буферном слое подложки GaAs последовательно слоя InGaP и защитного слоя GaP в потоке фосфора или на буферном слое подложки InP последовательно слоя InP и защитного слоя InGaP в потоке фосфора,

- замену потока фосфора на поток мышьяка и выдерживание поверхности при температуре 450-510°С до полной конвертации защитного слоя GaP в слой GaAs в гетероструктуре на буферном слое подложки GaAs или до полной конвертации защитного слоя InGaP в слой InGaAs в гетероструктуре на буферном слое подложки InP,

- выращивание покрывающего слоя GaAs гетероструктуры на буферном слое подложки GaAs или покрывающего слоя InGaAs гетероструктуры на буферном слое подложки InP.

2. Способ по п. 1, характеризующийся тем, что время выдержки в потоке фосфора составляет 3-10 мин.

3. Способ по п. 1, характеризующийся тем, что толщина слоя GaP или InGaP составляет 0,6-1,3 нм.

| ПОЛУПРОВОДНИКОВАЯ ТРАНЗИСТОРНАЯ НАНОГЕТЕРОСТРУКТУРА НА ПОДЛОЖКЕ GaAs С МОДИФИЦИРОВАННЫМ СТОП-СЛОЕМ AlGaAs | 2015 |

|

RU2582440C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ФОТОПРИЕМНОГО ЭЛЕМЕНТА НА ОСНОВЕ МНОГОСЛОЙНЫХ ГЕТЕРОСТРУКТУР GA AS/AL GA AS | 1994 |

|

RU2065644C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОЙ ГЕТЕРОСТРУКТУРЫ | 2014 |

|

RU2570099C1 |

| МОЩНЫЙ ПОЛЕВОЙ ТРАНЗИСТОР СВЧ | 2011 |

|

RU2463685C1 |

| Гетероэпитаксиальная структура для полевых транзисторов | 2017 |

|

RU2649098C1 |

| ПОЛУПРОВОДНИКОВАЯ ГЕТЕРОСТРУКТУРА | 2014 |

|

RU2563544C1 |

| US 7538365 B2, 26.05.2009. | |||

Авторы

Даты

2019-06-06—Публикация

2018-05-30—Подача