Изобретение относится к области вычислительной техники и может быть использовано для создания системных интерфейсов программируемого логического контроллера (ПЛК).

Известен «Программируемый логический контроллер для территориально-распределенной системы управления» [РФ №171436 U1, G05B 19/042, 31.05.2017], построенный по магистрально-модульной архитектуре и состоящий из одного или нескольких помещенных в дополнительную защитную оболочку каркасов, содержащих, по крайней мере, один модуль центрального процессора, а так же модули ввода и вывода аналоговых и дискретных сигналов, связные модули с поддержкой внешних интерфейсов RS-485 или RS-232, оборудованных опторазвязкой, все модули имеют собственные встроенные гальванически развязанные источники вторичного электропитания; межмодульная магистраль в каркасе организована помощью пассивной объединительной панели, которая содержит дублированные шины CAN, подключение модулей к которым оборудованы опторазвязкой, шины разводки входного питания 27 В и дополнительны сигналов, кроме того в каждый разъем панель подается индивидуальный код, используемый для идентификации в шине CAN устанавливаемого в этот разъем модуля, отличающийся тем, что каждый каркас содержит модуль управления электропитанием, который контролирует значения входного напряжения питания каркаса, нагрузку по току на внутренних линиях электропитания шины и температуру каркаса, выполняет выдачу в модуль центрального процессора предупредительных сообщений при повышении входного напряжения, увеличении тока нагрузки или температуры, а так же аварийное отключение каркаса от входного источника электропитания; выполняет индикацию наличия внешнего питающего напряжения 27 В и внутреннего напряжения на линиях объединительной платы, а так же индикацию аварийного состояния по входному питанию.

Недостатком этого контроллера является использование сложного оборудования, так как он используется в автоматизированных системах управления территориально-распределенными взрывоопасными производственными объектами, работающими в тяжелых климатических условиях, и может быть использовано для построения систем управления объектами наземной инфраструктуры ракетно-космических комплексов, а также химических и нефтегазовых установок.

Наиболее близким к заявляемому является «Устройство переключения интерфейсов» [РФ №2421794 C1, G06F 13/40, 20.06.2011], содержащее интерфейсные микросхемы с входом управления включением, соединенные с интерфейсами ЭВМ и аппаратуры передачи данных (АПД), управляющий вход интерфейсной микросхемы, соединенной с интерфейсом АПД, соединен постоянно с разрешающим потенциалом, в его состав включен микроконтроллер, входы микроконтроллера соединены с интерфейсными входами интерфейсных микросхем, соединенных с интерфейсами ЭВМ, выходы микроконтроллера соединены с управляющими входами этих микросхем, микроконтроллер управляется программой, анализирующей уровни сигналов на входах микроконтроллера и устанавливающей разрешающий уровень на входах управления интерфейсных микросхем, соединенных с интерфейсами ЭВМ, TTL выходы интерфейсных микросхем, соединенных с интерфейсами ЭВМ, соединены друг с другом и входами интерфейсной микросхемы, соединенной с интерфейсом АПД, TTL входы интерфейсных микросхем, соединенных с интерфейсами ЭВМ, соединены друг с другом и выходами интерфейсной микросхемы, соединенной с интерфейсом АПД.

Недостатком устройства является отсутствие возможности объединения в единую систему модулей ввода-вывода для подключения датчиков и исполнительных механизмов и процессорных модулей для исполнения алгоритмов контроля и управления.

Техническим результатом является расширение функциональных возможностей за счет реализации объединения в единую систему модулей ввода-вывода для подключения датчиков и исполнительных механизмов и процессорных модулей для исполнения алгоритмов контроля и управления.

Технический результат достигается тем, что в «Системный интерфейс программируемого логического контроллера», содержащий микроконтроллер, дополнительно введены второй микроконтроллер, два разъема для установки двух «Модулей питания», два разъема для установки двух «Модулей процессорных» и десять разъемов для установки функциональных модулей ПЛК, вторые двухсторонние входы выходы которых объединены и соединены с вторым двухсторонним входом выходом первого микроконтроллера, второй вход которого соединен с вторым выходом второго разъема для установки двух «Модулей питания», первый выход которого соединен с первым входом второго микроконтроллера, второй вход которого соединен с вторым выходом первого разъема для установки двух «Модулей питания», первый выход которого соединен с первым входом первого микроконтроллера, первый двухсторонний вход выход которого соединен с первым двухсторонним входом выходом второго микроконтроллера, третий двухсторонний вход выход которого соединен с объединенными четвертыми двухсторонними входами выходами с первого по десятый разъемов для установки функциональных модулей ПЛК, второй двухсторонний вход выход второго микроконтроллера соединен с вторым двухсторонним входом выходом второго разъема для установки двух «Модулей процессорных», четвертый двухсторонний вход выход которого соединен с четвертым двухсторонним входом выходом первого разъема для установки двух «Модулей процессорных», второй двухсторонний вход выход которого соединен с третьим двухсторонним входом выходом первого микроконтроллера, первые двухсторонние входы выходы первого и второго разъемов для установки двух «Модулей процессорных» объединены и соединены с объединенными первыми двухсторонними входами выходами с первого по десятый разъемов для установки функциональных модулей ПЛК, третьи двухсторонние входы выходы первого и второго разъемов для установки двух «Модулей процессорных» объединены и соединены с объединенными третьими двухсторонними входами выходами с первого по десятый разъемов для установки функциональных модулей ПЛК.

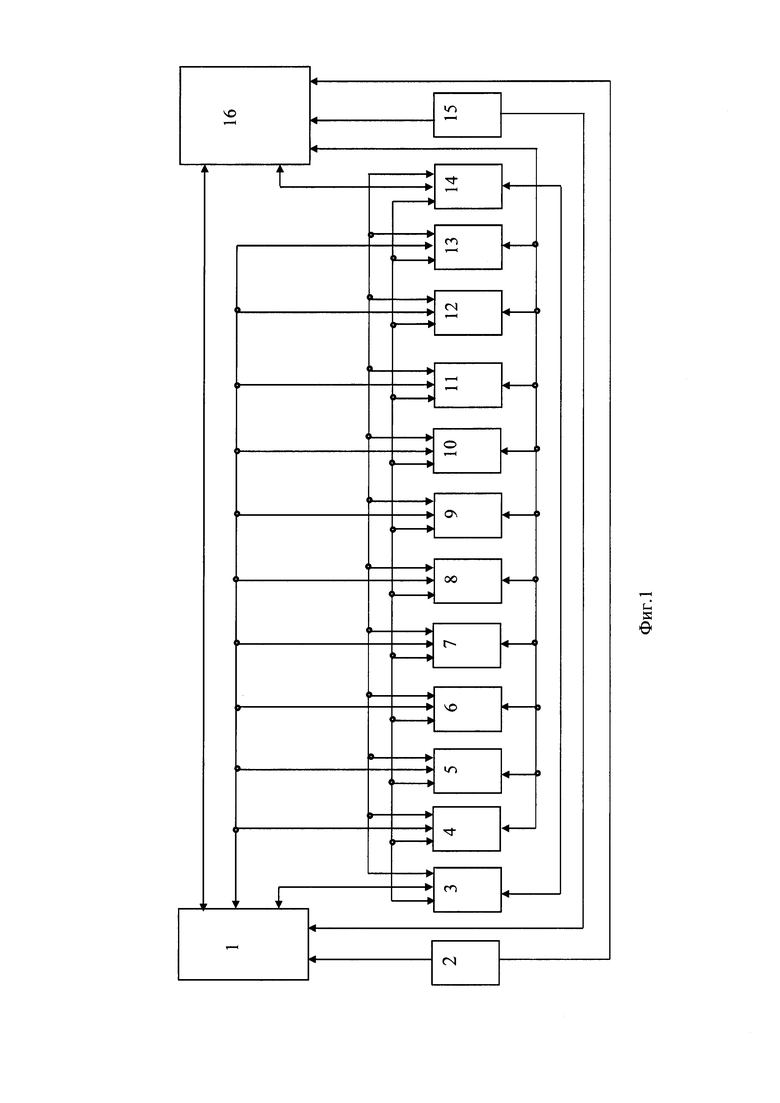

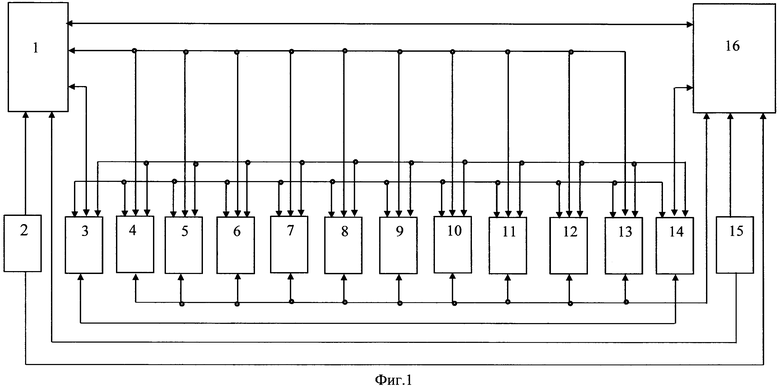

На фиг. 1 представлена блок-схема системного интерфейса программируемого логического контроллера.

Системный интерфейс программируемого логического контроллера (ПЛК) (фиг. 1) содержит два микроконтроллера 1 и 16, реализующие алгоритм работы интерфейса, два разъема 2 и 15 для установки двух «Модулей питания», два разъема 3 и 14 для установки двух «Модулей процессорных» и десять разъемов 4…13 для установки функциональных модулей ПЛК, вторые двухсторонние входы выходы которых объединены и соединены с вторым двухсторонним входом выходом первого микроконтроллера 1, второй вход которого соединен с вторым выходом второго разъема 15 для установки двух «Модулей питания», первый выход которого соединен с первым входом второго микроконтроллера 16, второй вход которого соединен с вторым выходом первого разъема 2 для установки двух «Модулей питания», первый выход которого соединен с первым входом первого микроконтроллера 1, первый двухсторонний вход выход которого соединен с первым двухсторонним входом выходом второго микроконтроллера 16, третий двухсторонний вход выход которого соединен с объединенными четвертыми двухсторонними входами выходами с первого 4 по десятый 13 разъемов для установки функциональных модулей ПЛК, второй двухсторонний вход выход второго микроконтроллера 16 соединен с вторым двухсторонним входом выходом второго разъема 14 для установки двух «Модулей процессорных», четвертый двухсторонний вход выход которого соединен с четвертым двухсторонним входом выходом первого разъема 3 для установки двух «Модулей процессорных», второй двухсторонний вход выход которого соединен с третьим двухсторонним входом выходом первого микроконтроллера 1, первые двухсторонние входы выходы первого 3 и второго 14 разъемов для установки двух «Модулей процессорных» объединены и соединены с объединенными первыми двухсторонними входами выходами с первого 4 по десятый 13 разъемов для установки функциональных модулей ПЛК, третьи двухсторонние входы выходы первого 3 и второго 14 разъемов для установки двух «Модулей процессорных» объединены и соединены с объединенными третьими двухсторонними входами выходами с первого 4 по десятый 13 разъемов для установки функциональных модулей ПЛК.

Системный интерфейс программируемого логического контроллера (ELPLC-BUS) выполняет функцию объединения в единую систему модулей ввода-вывода, для подключения датчиков и исполнительных механизмов, и процессорных модулей для исполнения алгоритмов контроля и управления.

Системный интерфейс ELPLC-BUS реализован в виде активной объединительной панели («бэкплейн») А, представляющей собой печатную плату с электронными компонентами и соединительными разъемами для установки модулей.

Микроконтроллеры 1 и 16 обеспечивают формирование сигналов выборки отдельных функциональных модулей в циклах конфигурации интерфейса, сбор запросов прерываний от функциональных модулей и трансляцию их «Модулям процессорным», синхронизацию работы функциональных модулей и модулей процессорных, сбор информации о состоянии модулей питания и объединительной панели и передачу ее модулям процессорным через соответствующие разъемы.

Каждый микроконтроллер 1 и 16 через соответствующие разъемы осуществляет контроль выходного напряжения каждого «Модуля питания» и величину потребляемого тока от каждого «Модуля питания». Тем самым обеспечивается диагностика работоспособности каждого из «Модулей питания».

Микроконтроллер 1 соединен с «Модулем процессорным», установленным в разъем 3, с помощью интерфейса SPI и двух дискретных сигналов INT и CLK. Микроконтроллер 16, соответственно, соединен с «Модулем процессорным», установленным в разъем 14. По интерфейсу SPI «Модули процессорные» передают микроконтроллерам 1 и 16 команды управления объединительной панелью (подтверждение прерывания, выбор конкретного функционального модуля и т.д. в соответствии с перечнем команд шины) и получают от них информацию о состоянии объединительной панели и функциональных модулей (номер модуля, вызвавшего прерывание, величину напряжения и отдаваемого тока для «Модулей питания» и т.д. в соответствии с перечнем команд интерфейса). С помощью сигнала INT микроконтроллер через соответствующий разъем передает «Модулю процессорному» информацию о наличии запросов прерываний от функциональных модулей. Сигнал CLK используется для синхронизации работы «Модуля процессорного» с функциональными модулями.

Модули процессорные посредством разъемов 3 и 14 для установки «Модулей процессорных» соединены друг с другом скоростным интерфейсом RS-485, использующимся для синхронизации управляющих алгоритмов и данных, реализуемых и хранимых каждым модулем процессорным в режиме дублирования.

Каждый модуль процессорный соединен со всеми функциональными модулями двумя независимыми интерфейсами RS-485. Таким образом, функциональные модули должны обеспечивать возможность обмена информацией по двум каналам RS-485. Это обеспечивает возможность работы объединительной панели в следующих режимах: простой (один процессор + один канал связи), дублирование интерфейса (один процессор + два канала связи), дублирование процессорного модуля (два процессора + один канал связи с каждым процессором).

Системный интерфейс ELPLC-BUS поддерживает дублирование компонентов системы: процессорных модулей и модулей источников питания. Активная объединительная панель является также резервированной за счет дублирования микроконтроллеров (1 и 16). Системный интерфейс поддерживает режим горячей замены для всех извлекаемых компонентов в разъемах 2-15. Горячей замене могут быть подвергнуты источники питания, процессорные модули, модули ввода-вывода. Системный интерфейс обеспечивает бесперебойную работу системы при изъятии или отказе дублированных компонентов: процессорных модулей, модулей источников питания, микроконтроллеров. Модули ввода-вывода в разъемах 4-13 могут быть дублированы функционально, на уровне системы.

Таким образом, системный интерфейс программируемого логического контроллера обеспечивает расширение функциональных возможностей за счет реализации объединения в единую систему модулей ввода-вывода для подключения датчиков и исполнительных механизмов и процессорных модулей для исполнения алгоритмов контроля и управления.

Изобретение относится к области вычислительной техники. Технический результат заключается в расширении функциональных возможностей. Системный интерфейс программируемого логического контроллера содержит: микроконтроллер; второй микроконтроллер; два разъема для установки двух «Модулей питания»; два разъема для установки двух «Модулей процессорных»; десять разъемов для установки функциональных модулей ПЛК. 1 ил.

Системный интерфейс программируемого логического контроллера, содержащий микроконтроллер, отличающийся тем, что в него дополнительно введены второй микроконтроллер, два разъема для установки двух «Модулей питания», два разъема для установки двух «Модулей процессорных» и десять разъемов для установки функциональных модулей ПЛК, вторые двухсторонние входы/выходы которых объединены и соединены с вторым двухсторонним входом/выходом первого микроконтроллера, второй вход которого соединен с вторым выходом второго разъема для установки двух «Модулей питания», первый выход которого соединен с первым входом второго микроконтроллера, второй вход которого соединен с вторым выходом первого разъема для установки двух «Модулей питания», первый выход которого соединен с первым входом первого микроконтроллера, первый двухсторонний вход/выход которого соединен с первым двухсторонним входом/выходом второго микроконтроллера, третий двухсторонний вход/выход которого соединен с объединенными четвертыми двухсторонними входами/выходами с первого по десятый разъемов для установки функциональных модулей ПЛК, второй двухсторонний вход/выход второго микроконтроллера соединен с вторым двухсторонним входом/выходом второго разъема для установки двух «Модулей процессорных», четвертый двухсторонний вход/выход которого соединен с четвертым двухсторонним входом/выходом первого разъема для установки двух «Модулей процессорных», второй двухсторонний вход/выход которого соединен с третьим двухсторонним входом/выходом первого микроконтроллера, первые двухсторонние входы/выходы первого и второго разъемов для установки двух «Модулей процессорных» объединены и соединены с объединенными первыми двухсторонними входами/выходами с первого по десятый разъемов для установки функциональных модулей ПЛК, третьи двухсторонние входы выходы первого и второго разъемов для установки двух «Модулей процессорных» объединены и соединены с объединенными третьими двухсторонними входами/выходами с первого по десятый разъемов для установки функциональных модулей ПЛК.

| УСТРОЙСТВО ПЕРЕКЛЮЧЕНИЯ ИНТЕРФЕЙСОВ | 2010 |

|

RU2421794C1 |

| СПОСОБ ПОДАВЛЕНИЯ ИМПУЛЬСОВ ОБРАТНОЙ | 0 |

|

SU171436A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| УСТРОЙСТВА, СИСТЕМЫ И СПОСОБЫ КОНФИГУРИРОВАНИЯ ПРОГРАММИРУЕМОГО ЛОГИЧЕСКОГО КОНТРОЛЛЕРА | 2007 |

|

RU2417391C2 |

Авторы

Даты

2019-12-16—Публикация

2018-11-19—Подача