Изобретение относится к вычислительной технике.

Из уровня техники известна материнская плата, содержащая вычислительный модуль, в состав которого входят центральный процессор, соединенный с запоминающим устройством и северным мостом, который соединен с южным мостом (см. патент США № 7082039 на изобретение, опубл. 25.07.2006).

Недостатком известной платы является то, что в ней для осуществления вычислений применяется только один центральный процессор, что существенно ограничивает скорость и производительность. При увеличении количества процессоров системная плата подвергается перегреву и выходит из строя. Кроме того, в системной плате отсутствует возможность удаленного управления и мониторинга.

Из уровня техники известна системная плата, содержащая вычислительный модуль, в состав которого входят центральный процессор, соединенный с оперативным запоминающим устройством и основным контроллером системной логики, который соединен с центральным графическим процессором, вспомогательным набором микросхем и коммутатором Infiniband, отличающаяся тем, что в состав вычислительного модуля включены дополнительный центральный процессор, соединенный с центральным процессором, дополнительным оперативным запоминающим устройством и дополнительным контроллером системной логики, который соединен с другими центральным графическим процессором и коммутатором Infiniband, а также коммутатором Ethernet, а основной и дополнительный контроллеры системной логики соединены друг с другом, при этом центральные процессоры и центральные графические процессоры расположены на поверхности платы таким образом, что прямая, проведенная через центр одного из ЦП и одного из центральных графических процессоров, параллельна прямой, проведенной через центры других ЦП и центрального графического процессора, и обе эти прямые параллельны продольной оси системной платы (см. патент РФ № 122506 на полезную модель, опубл. 27.11.2012).

Недостатком известной платы является низкая производительность, отсутствует возможность установки дополнительных карт расширения, ограниченный объем памяти, отсутствует возможность установки контроллера для удаленного управления.

Задачей заявленного изобретения является создание универсальной в использовании системной платы вычислительного модуля с упрощенным конструктивом, обладающей длительным жизненным циклом.

Техническими результатами заявленного изобретения являются:

- повышение скорости, пропускной способности и производительности вычислительного модуля сервера;

- повышение вычислительной плотности сервера;

- снижение стоимости вычислительного модуля сервера;

- обеспечение возможности удаленного управления и контроля за компонентами вычислительного модуля;

- обеспечение отказоустойчивости работы вычислительного модуля;

- обеспечение возможности реализации вычислительными модулями сервера гибкой конфигурации производительности и расширяемости;

- обеспечение возможности использования в серверах различных форм-факторов. Технические результаты заявленного изобретения достигаются тем, что плата системная

вычислительного модуля (см. фиг. 1 и 2) представляет собой печатную плату, включающую:

- два центральных процессора Ampere Altra Мах (ЦПУ 1, ЦПУ 0);

- основную микросхему памяти SPI Flash (3а);

- резервную микросхема памяти SPI Flash (3б);

- основную микросхему памяти EEPROM (4а) с интерфейсом I2C, содержащую UEFI BIOS;

- резервную микросхему памяти EEPROM (4б) с интерфейсом I2C, содержащую UEFI BIOS;

- разъем (27) для возможности установки карт расширения стандарта ОСР;

- разъем (5) для возможности соединения с бэкплейном сервера форм-фактора 1/2U;

- шестнадцать слотов (6-9, 11-14, 17-24) для возможности установки модулей оперативной памяти, при этом каждый процессор ЦПУ 0 и ЦПУ 1 подключен к соответствующим восьми слотам оперативной памяти и использует восемь каналов памяти;

- четыре разъема (10, 15, 26, 28) для возможности установки адаптеров (райзеров) PCIe х16 и проприетарных плат, при этом каждый процессор ЦПУ 0 и ЦПУ 1 подключен к соответствующим двум разъемам (26,28) и (10,15);

- два разъема (16, 31) для возможности установки внутренних накопителей М.2, при этом каждый процессор ЦПУ 0 и ЦПУ 1 подключен к соответствующему разъему (31) и (16);

- коммутатор (25);

- разъемы (29,30) для возможности подключения дискового бэкплейна для обеспечения подключения до восьми накопителей SSD NVMe с поддержкой их горячей замены;

- разъем (32) для возможности подключения контроллера мониторинга и управления (ВМС);

- штырьковый разъем (33) для возможности установки джамперов;

- ПЛИС-контроллер (35), осуществляющий подачу стартовых импульсов напряжения для инициализации процессоров ЦПУ 0 и ЦПУ 1;

- модуль (36) регулирования напряжения питания (VRM) процессоров ЦПУ 0 и ЦПУ 1;

- преобразователь (37) интерфейса RGMII/SGMII;

- коннектор USB (38);

- разъем (39) для возможности установки карты ввода-вывода;

- первый разъем (40) для возможности подключения к мидплейну шасси;

- второй разъем (41) для подключения к мидплейну шассси; при этом:

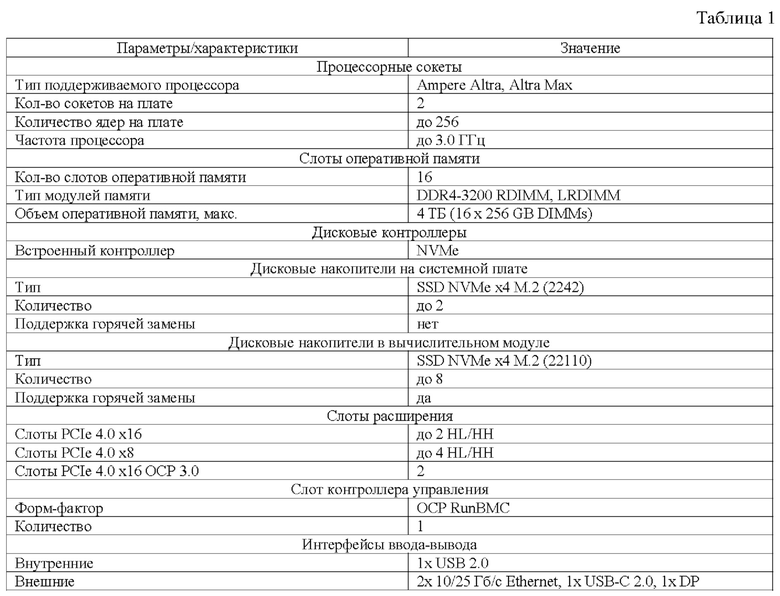

- процессоры ЦПУ 0 и ЦПУ 1 соединены между собой по интерфейсам CCIX, GPIO, I2C, 2xUART и SMBus;

- процессор ЦПУ 0 соединен по интерфейсу PCIe х16 с разъемом (27) для возможности установки карт расширения стандарта ОСР;

- процессор ЦПУ 1 соединен по интерфейсу PCIe х16 с разъемом (5) для возможности соединения с бэкплейном сервера форм-фактора 1/2U;

- процессор ЦПУ 0 соединен по интерфейсам PCIe х16 с разъемами (29,30) для возможности подключения дискового бэкплейна;

- каждый процессор ЦПУ 0 и ЦПУ 1 соединен по интерфейсам I2C, UART с разъемом (32) для подключения контроллера мониторинга и управления (ВМС);

- процессор ЦПУ 0 соединен по интерфейсам с разъемом (32) для подключения контроллера мониторинга и управления (ВМС) через коммутатор (25), выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейсы USB и I2C;

- процессор ЦПУ 0 соединен по интерфейсу с коннектором USB (38) через коммутатор (25), выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейс USB;

- процессор ЦПУ 0 соединен по интерфейсам с разъемом (39) для возможности установки карты ввода-вывода через коммутатор (25), выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейсы USB и SGMII;

- процессор ЦПУ 0 соединен по интерфейсам GPIO и PCIe xl с ПЛИС-контроллером (35);

- разъем (32) для подключения контроллера мониторинга и управления (ВМС) соединен по интерфейсам RMII и DP с разъемом (39) для возможности установки карты ввода-вывода;

- разъем (32) для подключения контроллера мониторинга и управления (ВМС) соединен по интерфейсу GPIO с ПЛИС-контроллером (35);

- разъем (32) для подключения контроллера мониторинга и управления (ВМС) соединен по интерфейсам 4х GPIO с ПЛИС-контроллером (35) через штырьковый разъем (33) для возможности установки джамперов;

- разъем (32) для подключения контроллера мониторинга и управления (ВМС) соединен по интерфейсам 3х GPIO с ПЛИС-контроллером (35) и с разъемом (39) для возможности установки карты ввода-вывода;

- процессор ЦПУ 1 соединен по интерфейсу GPIO с ПЛИС-контроллером (35);

- модуль (36) регулирования напряжения питания (VRM) соединен с ПЛИС-контроллером (35);

- первый и второй разъемы (40) для возможности подключения к мидплейну шасси соединены по линиям питания с модулем (36) регулирования напряжения питания (VRM);

- основная и резервная микросхемы памяти SPI Flash (3а, 3б) соединены по интерфейсу I2C с каждым из процессоров ЦПУ 0 и ЦПУ 1;

- основная и резервная микросхемы памяти EEPROM (4а, 46) с интерфейсом I2C, содержащие UEFI BIOS, соединены по интерфейсу SPI с процессором ЦПУ 0, как с ведущим процессором;

- процессор ЦПУ 0 соединен по интерфейсу с первым и вторым разъемами (40) для возможности подключения к мидплейну шасси через коммутатор (25), выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейс SGMII;

- разъем (32) для подключения контроллера мониторинга и управления (ВМС) соединен по интерфейсу с первым и вторым разъемами (40, 41) для возможности подключения к мидплейну шасси через преобразователь (37) интерфейса RGMII/SGMII;

- первый и второй разъемы (40, 41) для возможности подключения к мидплейну шасси соединены по интерфейсу 1x I2C с разъемом (32) для подключения контроллера мониторинга и управления (ВМС) и с ПЛИС-контроллером (35);

- первый и второй разъемы (40) для возможности подключения к мидплейну шасси соединены по интерфейсам 2х GPIO с ПЛИС-контроллером (35);

- первый и второй разъемы (40, 41) для возможности подключения к мидплейну шасси соединены по интерфейсам GPIO с разъемом (32) для подключения контроллера мониторинга и управления (ВМС) и ПЛИС-контроллером (35).

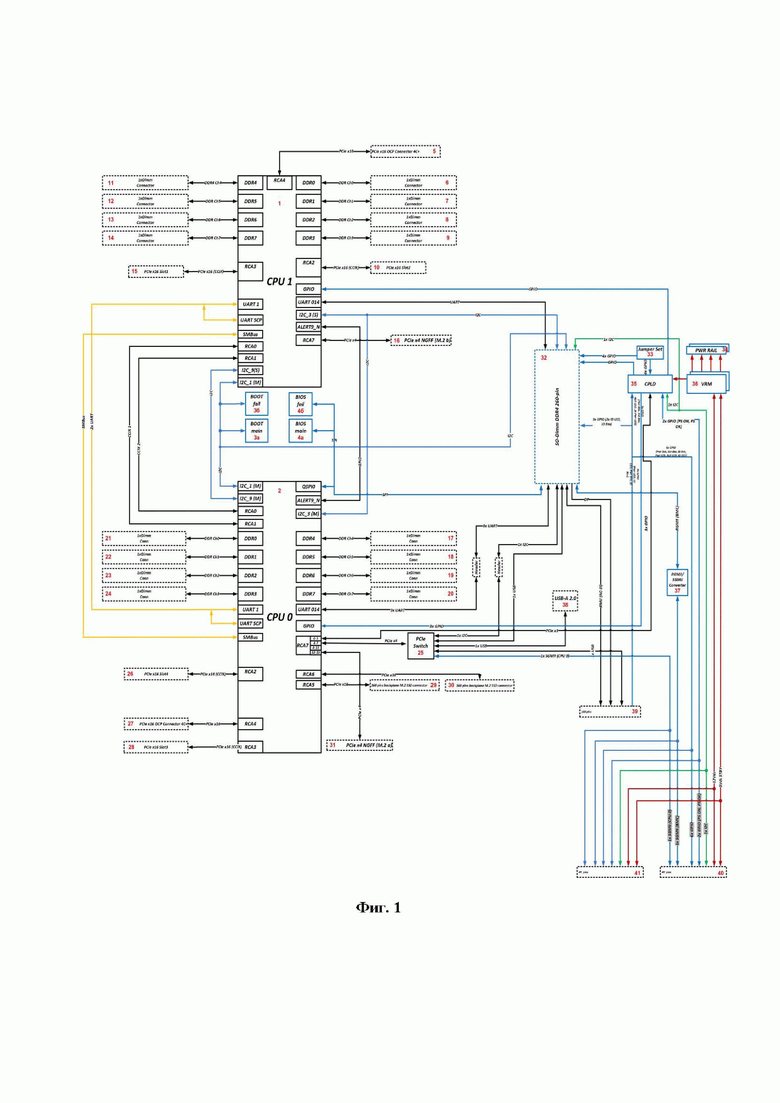

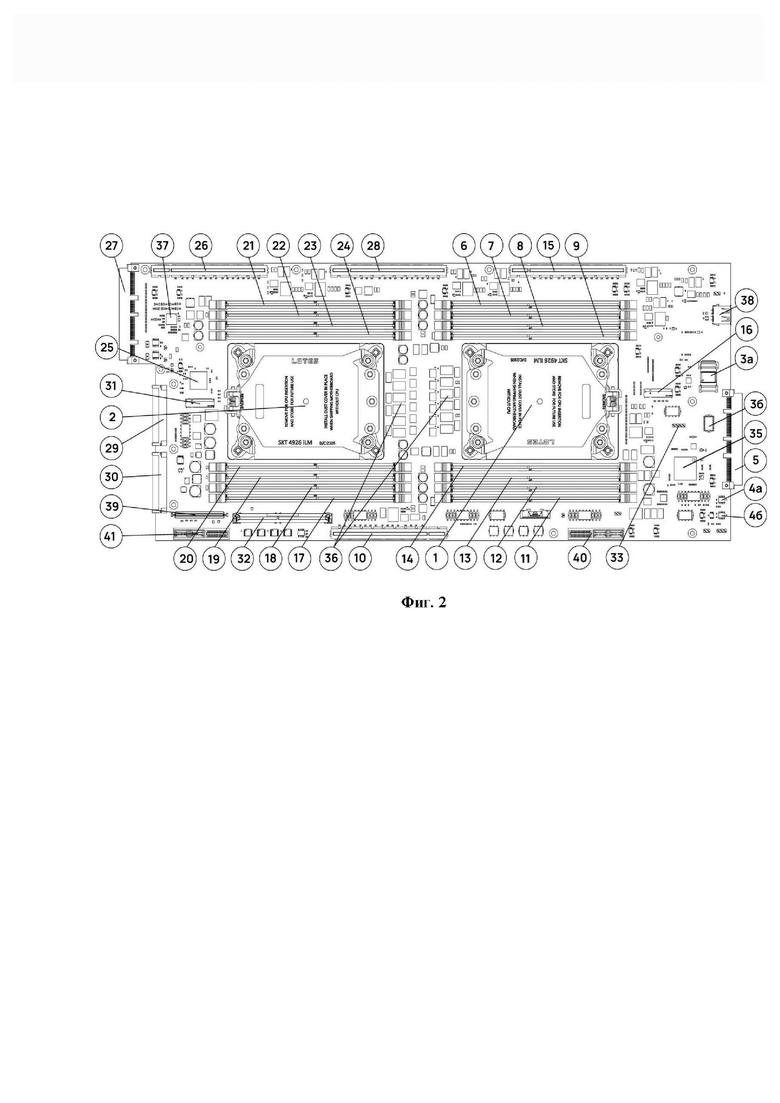

Признаки и сущность заявленного изобретения поясняются в последующем детальном описании, иллюстрируемом чертежами (см. фигуры 1 - 2).

На фиг. 1 представлен пример реализации заявленной системной платы вычислительного модуля.

На фиг. 2 представлено изображение системной платы вычислительного модуля сервера (вид сверху, пример реализации).

На фигурах 1 и 2 под одинаковыми позициями обозначено следующее:

1,2- первый и второй центральные процессоры Ampere Altra Мах (ЦПУ 1, ЦПУ 0);

3а - основная микросхема памяти SPI Flash;

3б - резервная микросхема памяти SPI Flash;

4а - основная микросхема памяти EEPROM с интерфейсом I2C, содержащая UEFI BIOS;

4б - резервная микросхема памяти EEPROM с интерфейсом I2C, содержащая UEFI BIOS;

5 - разъем для соединения с бэкплейном сервера форм-фактора 1/2U;

6-9, 11-14 - слоты для установки модулей оперативной памяти для процессора ЦПУ 1;

10, 15, 26, 28 - разъемы для установки адаптеров (райзеров) PCIe х16 и проприетарных плат;

16, 31 - разъемы для установки внутренних накопителей М.2;

17 - 24 - слоты для установки модулей оперативной памяти для процессора ЦПУ 0;

25 - коммутатор PCIe;

27 - разъем для установки карт расширения стандарта ОСР;

29, 30 - разъемы для подключения дискового бэкплейна с возможностью подключения до 8 накопителей SSD NVMe с поддержкой их горячей замены;

32 - разъем для возможности подключения контроллера мониторинга и управления (ВМС);

33 - штырьковый разъем для установки джамперов;

34 - линии питания, идущие от модуля VRM к процессорам ЦПУ 1 и ЦПУ 0;

35 - ПЛИС-контроллер, осуществляющий подачу стартовых импульсов напряжения для запуска процессоров ЦПУ 0 и ЦПУ 1;

36 - модуль регулирования напряжения питания (VRM) для процессоров ЦПУ 0 и ЦПУ 1;

37 - преобразователь интерфейса RGMII/SGMII;

38 - коннектор USB;

39 - разъем для установки карты (адаптера) ввода-вывода;

40 первый разъем для подключения к мидплейну шасси;

41 - второй разъем для подключения к мидплейну шассси.

Процессоры ЦПУ (1,2) системной платы сконфигурированы с возможностью:

- получения данных из модулей оперативной памяти (6-9, 11 -14, 17-24);

- приема запросов и информации от внешних устройств;

- обработки поступающей информации;

- выполнения логических и арифметических операций с полученной информацией;

- временного хранения результатов выполненных операций, переданных сигналов и других данных;

- передачи итогов обработки информации внешним устройствам;

- формирования управляющих сигналов, необходимых для работы внутренних узлов, компонентов и внешних устройств;

- определения приоритета выполнения задач, управления потоками данных и разделения вычислительных ресурсов между программами и процессами.

Коммутатор (25) предназначен для преобразования интерфейса PCIe х4 от процессора ЦПУ 0 в интерфейсы USB, I2C, SGMII.

Джамперы, устанавливаемые в разъем 33, предназначены для задания режимов работы системной платы:

- одиночный режим (при использовании одной системной платы в 2-х процессорной конфигурации);

- режим ведущей платы или ведомой платы (при объединении двух системных плат в единый 4-х процессорный конструктив).

На системной плате имеется два разъема (29,30) для возможности подключения дискового бэкплейна, что дает возможность подключать до восьми накопителей SSD NVMe с поддержкой их горячей замены.

Модуль VRM (36) представляет собой импульсный преобразователь, который предназначен для регулировки напряжения питания до необходимого уровня, подаваемого на процессоры ЦПУ 0 и ЦПУ 1 и другие компоненты платы, например, на видеокарту, от блока питания. Также модуль (36) обеспечивает стабильное и точное выходное напряжение.

ПЛИС контроллер (35) выполнен с возможностью:

- подачи стартовых импульсов питания с заданной частотой и уровнем напряжения для инициализации процессоров ЦПУ 0 и ЦПУ 1;

обеспечения корректной последовательности подачи/отключения питания на процессоры (1,2) системной платы путем управления соответствующими микросхемами системы питания и системы тактовой синхронизации системной платы (подача/отключение питания производится синхронно для обоих процессоров);

- обеспечения выполнения команд от внешних источников на включение, сброс процессоров (1,2) и периферийных интерфейсов PCIe и USB;

- обеспечения взаимодействия с внешним ПО по шине I2C;

- распознавания режима работы материнской платы вычислительного модуля сервера.

Системная плата сконфигурирована с возможностью объединения со второй типовой системной платой в единый четырехпроцессорный конструктив с помощью четырех универсальных слотов (10, 15, 26, 28).

Четырехпроцессорная конфигурация позволяет увеличить общую производительность вычислительного модуля сервера в 2 раза, что открывает новые преимущества:

- возможность выполнения задач, которые невозможно выполнить на 2-х процессорной конфигурации, задач, которые требуют повышенной процессорной производительности вычислительного узла и объема оперативной памяти;

- сокращение интерфейсов ввода-вывода в 2 раза и упрощение топологии подключения к корпоративным сетям и сетям хранения данных за счет укрупнения вычислительного узла;

- возможность сокращения размера коммутационной сети более, чем в 2 раза, в некоторых конфигурациях в 3, 4 и более раз (при использовании в высокопроизводительных вычислительных кластерах).

Системная плата сконфигурирована с возможностью установки контроллера удаленного управления и мониторинга за счет наличия стандартного слота ОСР RunBMC v1.4.1 (32), что позволяет администратору удаленно производить необходимое управление и мониторинг компонентов вычислительного модуля сервера.

Использование современной многоядерной процессорной архитектуры ARM64 позволяет:

- снизить энергопотребление вычислительных модулей сервера, создаваемых на базе системной платы;

- снизить стоимость вычислительных модулей сервера, создаваемых на базе системной платы;

- увеличить производительность вычислительных модулей сервера, создаваемых на базе системной платы;

- увеличить плотность вычислений вычислительных модулей сервера, создаваемых на базе системной платы;

- обеспечить возможность реализации 4-х процессорного вычислительного модуля с использованием 2 типовых системных плат и процессоров Ampere Altra Мах, что в разы дешевле аналогичных решений на платформе х86 благодаря прогрессивной архитектуре ARM64.

Разъемы 10, 15, 26, 28 предназначены для установки адаптеров (райзеров) PCIe х16 и проприетарных плат, например, объединительных плат для соединения двух системных плат в единый 4-х процессорный конструктив или плат для объединения процессоров ЦПУ 0 и ЦПУ 1, обеспечивая дополнительную соединительную линию ССГХ (PCIe х16) для увеличения пропускной способности и скорости обмена информацией между процессорами ЦПУ 0 и ЦПУ 1.

Основная микросхема памяти SPI Flash (3а) предназначена для загрузки стартовой программы сервисного процессора SCP, установленного внутри ЦПУ 0 и ЦПУ 1, осуществляющего запуск процессоров ЦПУ 0 и ЦПУ 1 перед загрузкой UEFI BIOS.

Резервная микросхема памяти SPI Flash (36) предназначена для загрузки стартовой программы сервисного процессора SCP, установленного внутри ЦПУ 0 и ЦПУ 1, осуществляющего запуск процессоров ЦПУ 0 и ЦПУ 1 перед загрузкой UEFI BIOS.

За счет дублирования микросхем памяти SPI Flash (3а, 3б) обеспечивается отказоустойчивость работы вычислительного модуля. В случае отказа микросхемы памяти SPI Flash, с которой происходит загрузка программы в сервисный процессор, разрушения программного кода, или наличие в нем ошибки, загрузка программы производится с резервной микросхемы памяти SPI Flash.

Основная микросхема памяти EEPROM (4а) с интерфейсом I2C содержит UEFI BIOS и предназначена для загрузки BIOS для ЦПУ 0 и ЦПУ 1.

Резервная микросхема памяти EEPROM (46) с интерфейсом I2C содержит UEFI BIOS и предназначена для загрузки BIOS для ЦПУ 0 и ЦПУ 1.

За счет дублируемых микросхем памяти (4а и 4б) с интерфейсом I2C, содержащих прошивку UEFI BIOS для процессоров ЦПУ 0 и ЦПУ 1, обеспечивается отказоустойчивость работы вычислительного модуля. В случае отказа микросхемы памяти EEPROM, с которой происходит загрузка UEFI BIOS, а также разрушения программного кода, или наличие в нем ошибки, происходит загрузка программы с резервной микросхемы памяти.

Заявленная системная плата предназначена для обеспечения коммуникации и передачи данных между всеми компонентами вычислительного модуля сервера, обеспечивает питание и интеграцию всех компонентов вычислительного модуля сервера, т.е. обеспечивает физическое и логическое соединение между процессорами, оперативной памятью, жесткими дисками, контроллером управления, сетевыми портами, дополнительными контроллерами, размещенными на системной плате, а также с дополнительными картами расширения, устанавливаемыми в слоты расширения, и другими устройствами.

При подаче питания на системную плату (при включении вычислительного модуля), ПЛИС контроллер (35) подает запускающие импульсы питания на процессоры ЦПУ О И ЦПУ 1 Ampere Altra Мах, которые в свою очередь загружаются и запускают работу UEFI BIOS (унифицированного интерфейса расширяемой прошивки, ПО низкого уровня, запускающегося при старте сервера перед тем, как загрузится операционная система). С помощью UEFI BIOS осуществляется проверка установленных компонентов, их инициализация и запуск операционной системы. Далее операционная система с помощью процессоров (1,2) управляет всеми компонентами вычислительного модуля сервера.

С помощью контроллера удаленного управления и мониторинга можно включить/выключить вычислительный модуль сервера, а также осуществлять мониторинг и управление всеми компонентами системной платы удаленно по стандартным интерфейсам подключения (Ethernet).

Возможны следующие режимы работы системной платы вычислительного модуля сервера:

- базовый двухпроцессорный режим (только для двухпроцессорного исполнения);

- четырехпроцессорный режим, ведущая плата (только для четырехпроцессорного исполнения);

- четырехпроцессорный режим, ведомая плата (только для четырехпроцессорного исполнения).

Заявленная системная плата в отличии от известных из уровня техники системных плат универсальна в применении. Плата может использоваться в:

- модульном сервере (блейд) в форм-факторе с минимальным размером и максимальной плотностью размещения вычислительных ресурсов;

- высокоплотном сервере в форм-факторе 2U;

- в GPU сервере в форм-факторе 2U;

- в классическом сервере в форм-факторах 1U и 2U

- в системе хранения данных (СХД) в качестве контроллера (в перспективе).

Универсальность использования достигается за счет наличия на системной плате разъема (5) стандарта ОСР, с помощью которого она соединяется с бэкплейном в сервере или СХД. За счет наличия на системной плате разъема (5) для соединения с бэкплейном сервера форм-фактора Ш или форм-фактора 2U не требуется использования каких-либо дополнительных кабельных соединений или плат для соединений с сервером, что облегчает процесс подключения системной платы к серверам и, тем самым, расширяет область ее применения.

Заявленная системная плата имеет упрощенный конструктив, в частности:

- отсутствует ретаймер;

- снижено количество слоев платы до 16 - 18 (в известных платах - 20 и более);

- снижено количество радиаторов и тепловых зон.

Это достигается за счет изменения дизайна, расположения компонентов на плате и проводки интерфейсных линий.

Заявленная системная плата обладает увеличенной производительностью за счет:

- наличия двух мощных центральных процессоров (1, 2) типа Ampere Altra Max;

- увеличения в 2 раза числа линий, соединяющих центральные процессоры (с 1 до 2), проложенных внутри платы;

- увеличения количества слотов и объема модулей памяти (6 - 9, 11 - 14, 17 - 24) для ЦПУ О и ЦПУ 1 до 16;

- увеличения мощности процессора почти в 2 раза (с 120 Вт до 220 Вт).

Системная плата обеспечивает:

- поддержку не менее 5 слотов расширения PCIe х16 Gen4;

- поддержку не менее двух сетевых портов 10/25 Гб/с Ethernet с помощью адаптера ввода-вывода, устанавливаемого в разъем (39) системной платы.

Использование стандарта ОСР RunBMC v1.4.1 (позиция 32) в качестве форм-фактора модуля управления ВМС позволило реализовать возможность установки другого модуля управления, а съемный характер модуля управления позволяет реализовать работоспособность платы системной вычислительного модуля без установленного контроллера ВМС.

На системной плате расположены 2 разъема для установки накопителей SSD NVME М.2 key М (16,31) и 2 разъема с интерфейсом PCIe х16 Gen4 ОСР NIC 3.0 (5,27).

Разъем (40) предназначен для подключения к мидплейну шасси (используется во всех моделях, кроме конфигурации второй платы в четырехпроцессорной конфигурации);

Разъем (41) предназначен для подключения к мидплейну шассси (используется при развороте второй платы в четырехпроцессорной конфигурации).

Вычислительный модуль, построенный на базе системной платы, реализует наиболее производительную и гибкую встроенную конфигурацию сетевых подключений Ethernet (общая производительность 50Гб/с).

Системная плата позволяет создавать полноценные серверы с высокой плотностью размещения вычислительных ресурсов 0,6U, по техническим характеристикам сравнимые с традиционными серверами для установки в стойку в форм-факторе 1U.

В заявленной системной плате в отличии от известных из уровня техники системных плати используются как стандартные (5, 10, 15, 16, 26, 27, 28, 31 32), так и проприетарные (29, 30, 39, 40) слоты расширения.

Увеличение жизненного цикла вычислительного модуля достигается за счет модульной идеологии построения системной платы, она выполнена с упрощенным функционалом, а дополнительные функции вынесены в отдельные модули.

Повышение вычислительной плотности сервера достигается за счет установки 10 двухсокетных вычислительных модулей в конструктив 6U. То есть 0,6U на двухсокетный сервер.

Снижение стоимости вычислений достигается за счет использования современной процессорной архитектуры ARM64, которая предлагает сравнимую производительность с архитектурой х86 за меньшую стоимость и при меньшем потреблении энергии.

Обеспечение возможности реализации вычислительными модулями сервера гибкой конфигурации производительности и расширяемости достигается за счет построения на базе одной системной платы 4-х (а далее более) различных моделей вычислительных модулей, которые покрывают до 95% потребностей заказчиков.

За счет использования центральных процессоров (1,2) Ampere Altra Max реализуется:

- поддержка 8-ми каналов оперативной памяти;

- размещение на плате 16 слотов оперативной памяти;

- поддержка максимального объема памяти в 2 ТБ (на процессор);

- поддержка 128 PCIe 4.0 линий на процессор;

- поддержка коррекции ошибок оперативной памяти ЕСС и АЕСС;

- поддержка памяти типа DDR4 с частотой 3200 МГц.

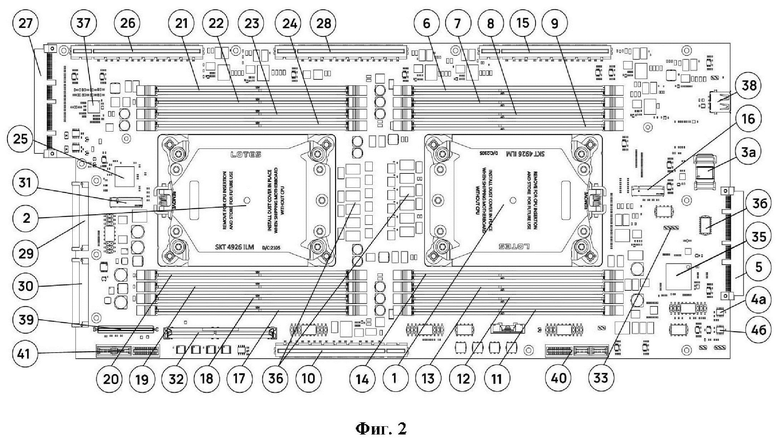

Технические характеристики и параметры заявленной системной платы представлены в таблице 1.

В качестве оперативной памяти используют модули оперативной памяти типа DDR4 с максимальным объемом 256 МБ на модуль (4 Тб на системную плату).

В качестве интерфейсов приема/передачи данных используются:

- интерфейс PCIe х16 GEN4, до 2 шт.;

- интерфейс PCIe х8 GEN4, до 2 шт.;

- интерфейс PCIe х4 GEN4, до 2 шт.;

- интерфейс ОСР PCIe х16 GEN4, до 2 шт.;

- интерфейс USB-A 2.0, 2 шт.;

- интерфейс DP (Display port);

- интерфейс для подключения адаптера к корпусной платформе системы электропитания, 1 шт (6xGPIO, 1xPS ON, 1xI2C, 1x GPIO, lxSGMII CPUO, lxSGMII BMC, 2x3,3B standby);

- интерфейс для возможности подключения контроллера удаленного управления и мониторинга (ВМС) системы управления и мониторинга, 1 шт. (стандарт интерфейса Open Compute Project RunBMC BMC daughter board I/O specification Rev 1.4.1);

- интерфейс для подключения адаптера ввода/вывода, 1 шт. (GPIO, lxDisplayPort, PCIe х4);

- интерфейс для подключения системы хранения данных, 1 шт.

Системная плата вычислительного модуля сервера, в варианте реализации, имеет ширину 223 мм, высоту 27 мм, глубину 446 мм, массу 1 кг.

Условия эксплуатации системной платы:

- рабочая температура от 0 до +55°С;

- влажность при температуре плюс 25°С - 90%.

| название | год | авторы | номер документа |

|---|---|---|---|

| Плата системная вычислительного модуля | 2024 |

|

RU2822305C1 |

| Компьютерная система с удаленным управлением сервером и устройством создания доверенной среды и способ реализации удаленного управления | 2016 |

|

RU2633098C1 |

| СИСТЕМНАЯ ВЫЧИСЛИТЕЛЬНАЯ ПЛАТА | 2024 |

|

RU2828793C1 |

| Устройство мониторинга и контроля обращений к BIOS со стороны ЦП | 2021 |

|

RU2762519C1 |

| Платформа для построения систем управления, передачи и обработки данных в вычислительных сетях | 2021 |

|

RU2771431C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ АТАК ДЛЯ СЕТЕВЫХ СИСТЕМ | 2013 |

|

RU2552135C2 |

| Малогабаритный высокопроизводительный вычислительный модуль на базе многопроцессорной Системы-на-Кристалле | 2021 |

|

RU2778213C1 |

| СЕТЕВОЙ АДАПТЕР | 2014 |

|

RU2574834C1 |

| СЕРВЕР | 2022 |

|

RU2804258C1 |

| Способ и устройство доверенной загрузки компьютера с контролем периферийных интерфейсов | 2020 |

|

RU2748575C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении производительности, отказоустойчивости и вычислительной плотности сервера. Технический результат достигается за счет того, что плата системная вычислительного модуля включает: два центральных процессора Ampere Altra Max, дублируемые микросхемы памяти SPI Flash и микросхемы памяти EEPROM, разъем для установки карт расширения стандарта ОСР, разъем для соединения с бэкплейном сервера форм-фактора 1/2U, шестнадцать слотов для установки модулей оперативной памяти, четыре разъема для установки адаптеров PCIe х16 и проприетарных плат, два разъема для установки внутренних накопителей М.2, коммутатор, разъемы для подключения дискового бэкплейна, разъем для подключения контроллера мониторинга и управления, разъем для установки джамперов, ПЛИС-контроллер, модуль регулирования напряжения питания процессоров, преобразователь интерфейса RGMII/SGMII, коннектор USB, разъем для установки карты ввода-вывода, два разъема для подключения к мидплейну шасси. 1 з.п. ф-лы, 2 ил., 1 табл.

1. Плата системная вычислительного модуля, представляющая собой печатную плату, включающую:

- два центральных процессора Ampere Altra Max (ЦПУ 1, ЦПУ 0);

- основную микросхему памяти SPI Flash;

- резервную микросхему памяти SPI Flash;

- основную микросхему памяти EEPROM с интерфейсом I2C, содержащую UEFI BIOS;

- резервную микросхему памяти EEPROM с интерфейсом I2C, содержащую UEFI BIOS;

- разъем для возможности установки карт расширения стандарта OCP;

- разъем для возможности соединения с бэкплейном сервера форм-фактора 1/2U;

- шестнадцать слотов для возможности установки модулей оперативной памяти, при этом каждый процессор ЦПУ 0 и ЦПУ 1 подключен к соответствующим восьми слотам оперативной памяти и использует восемь каналов памяти;

- четыре разъема для возможности установки адаптеров (райзеров) PCIe x16 и проприетарных плат, при этом каждый процессор ЦПУ 0 и ЦПУ 1 подключен к соответствующим двум разъемам;

- два разъема для возможности установки внутренних накопителей M.2, при этом каждый процессор ЦПУ 0 и ЦПУ 1 подключен к соответствующему разъему;

- коммутатор;

- разъемы для возможности подключения дискового бэкплейна для обеспечения подключения до восьми накопителей SSD NVMe с поддержкой их горячей замены;

- разъем для возможности подключения контроллера мониторинга и управления (BMC);

- штырьковый разъем для возможности установки джамперов;

- ПЛИС-контроллер, осуществляющий подачу стартовых импульсов напряжения для инициализации процессоров ЦПУ 0 и ЦПУ 1;

- модуль регулирования напряжения питания (VRM) процессоров ЦПУ 0 и ЦПУ 1;

- преобразователь интерфейса RGMII/SGMII;

- коннектор USB;

- разъем для возможности установки карты ввода-вывода;

- первый разъем для возможности подключения к мидплейну шасси;

- второй разъем для подключения к мидплейну шассси;

при этом:

- процессоры ЦПУ 0 и ЦПУ 1 соединены между собой по интерфейсам CCIX, GPIO, I2C, 2xUART и SMBus;

- процессор ЦПУ 0 соединен по интерфейсу PCIе х16 с разъемом для возможности установки карт расширения стандарта OCP;

- процессор ЦПУ 1 соединен по интерфейсу PCIе х16 с разъемом для возможности соединения с бэкплейном сервера форм-фактора 1/2U;

- процессор ЦПУ 0 соединен по интерфейсам PCIе х16 с разъемами для возможности подключения дискового бэкплейна;

- каждый процессор ЦПУ 0 и ЦПУ 1 соединен по интерфейсам I2C, UART с разъемом для подключения контроллера мониторинга и управления (BMC);

- процессор ЦПУ 0 соединен по интерфейсам с разъемом для подключения контроллера мониторинга и управления (BMC) через коммутатор, выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейсы USB и I2C;

- процессор ЦПУ 0 соединен по интерфейсу с коннектором USB через коммутатор, выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейс USB;

- процессор ЦПУ 0 соединен по интерфейсам с разъемом для возможности установки карты ввода-вывода через коммутатор, выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейсы USB и SGMII;

- процессор ЦПУ 0 соединен по интерфейсам GPIO и PCIe x1 с ПЛИС-контроллером;

- разъем для подключения контроллера мониторинга и управления (BMC) соединен по интерфейсам RMII и DP с разъемом для возможности установки карты ввода-вывода;

- разъем для подключения контроллера мониторинга и управления (BMC) соединен по интерфейсу GPIO с ПЛИС-контроллером;

- разъем для подключения контроллера мониторинга и управления (BMC) соединен по интерфейсам 4х GPIO с ПЛИС-контроллером через штырьковый разъем для возможности установки джамперов;

- разъем для подключения контроллера мониторинга и управления (BMC) соединен по интерфейсам 3х GPIO с ПЛИС-контроллером и с разъемом для возможности установки карты ввода-вывода;

- процессор ЦПУ 1 соединен по интерфейсу GPIO с ПЛИС-контроллером;

- модуль регулирования напряжения питания (VRM) соединен с ПЛИС-контроллером;

- первый и второй разъемы для возможности подключения к мидплейну шасси соединены по линиям питания с модулем регулирования напряжения питания (VRM);

- основная и резервная микросхемы памяти SPI Flash соединены по интерфейсу I2C c каждым из процессоров ЦПУ 0 и ЦПУ 1;

- основная и резервная микросхемы памяти EEPROM с интерфейсом I2C, содержащие UEFI BIOS, соединены по интерфейсу SPI с процессором ЦПУ 0, как с ведущим процессором;

- процессор ЦПУ 0 соединен по интерфейсу с первым и вторым разъемами для возможности подключения к мидплейну шасси через коммутатор, выполненный с возможностью преобразования интерфейса PCIe х4 в интерфейс SGMII;

- разъем для подключения контроллера мониторинга и управления (BMC) соединен по интерфейсу с первым и вторым разъемами для возможности подключения к мидплейну шасси через преобразователь интерфейса RGMII/SGMII;

- первый и второй разъемы для возможности подключения к мидплейну шасси соединены по интерфейсу 1х I2C с разъемом для подключения контроллера мониторинга и управления (BMC) и с ПЛИС-контроллером;

- первый и второй разъемы для возможности подключения к мидплейну шасси соединены по интерфейсам 2х GPIO с ПЛИС-контроллером;

- первый и второй разъемы для возможности подключения к мидплейну шасси соединены по интерфейсам GPIO с разъемом для подключения контроллера мониторинга и управления (BMC) и ПЛИС-контроллером.

2. Плата по п. 1, отличающаяся тем, что выполнена с возможностью объединения с аналогичной второй платой системной с помощью проприетарных плат с интерфейсом CCIX с образованием 4-процессорного конструктива.

| Плата системная вычислительного модуля | 2024 |

|

RU2822305C1 |

| US 20190095774 A1, 28.03.2019 | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ УЛАВЛИВАНИЯ И СБРОСА ПОЧАТКОВ НА УТОЧНО-МОТАЛЬНОМ ПОЧАТОЧНОМАВТОМАТЕ | 0 |

|

SU208501A1 |

| Дозатор жидкости | 1959 |

|

SU131516A1 |

| Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой | 2016 |

|

RU2635896C1 |

Авторы

Даты

2025-05-19—Публикация

2024-11-08—Подача