Известно устройство широкополосного измерителя частоты СВЧ сигналов [1]. Широкополосный измеритель частоты СВЧ сигналов состоит из входного широкополосного усилителя, набора линий задержки, фазовых корреляторов, аналого-цифровых преобразователей, вычислительного устройства и устройства управления.

Недостатком данного устройства является громоздкость, вызванная необходимостью применения нескольких линий задержки, минимальное и максимальное время задержки которых для достижения заданной точности и диапазона рабочих частот должны отличаться в несколько раз. Другим недостатком указанного устройства является узкий диапазон рабочих частот, который ограничивается сложностью проектирования и изготовления широкополосной линии задержки с большим временем задержки. Еще одним недостатком указанного устройства является невысокая чувствительность устройства, ограничиваемая погонными потерями в длинных линиях задержки.

Наиболее близким по технической сущности и достигаемому техническому результату к заявляемому изобретению является устройство широкополосного измерителя частоты СВЧ сигналов [2]. Широкополосный измеритель частоты СВЧ сигналов состоит из входного широкополосного усилителя-ограничителя, входного полосового СВЧ фильтра, набора линий задержки, фазовых корреляторов, вычислительного устройства.

Недостатком данного устройства является громоздкость, вызванная необходимостью применения нескольких линий задержки, минимальное и максимальное время задержки которых, для достижения заданной точности и диапазона рабочих частот должны отличаться в несколько раз. Другим недостатком указанного устройства является узкий диапазон рабочих частот, который ограничивается сложностью проектирования и изготовления широкополосной линии задержки с большим временем задержки. Еще одним недостатком указанного устройства является невысокая чувствительность устройства, ограничиваемая погонными потерями в длинных линиях задержки.

Техническим результатом изобретения является уменьшение габаритных размеров и массы, повышение чувствительности устройства при сохранении точности измерения частоты.

Целью изобретения является снижение громоздкости устройства за счет замены длинных линий задержки на короткие с предварительным преобразованием частоты входного сигнала путем деления и/или умножения.

Заявленный результат достигается тем, что в устройство, состоящее из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также N линий задержки, N фазовых корреляторов, выходы которых подключены к вычислительному устройству, дополнительно введены N умножителей частоты, коэффициенты умножения которых выбраны из ряда 1,2,3…A полностью или с пропусками, при этом входы умножителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы умножителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов.

Заявленный результат достигается также устройстве, состоящем из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также M линий задержки, M фазовых корреляторов, выходы которых подключены к вычислительному устройству, в которое дополнительно введены M делителей частоты, коэффициенты деления которых выбраны из ряда 1,2,3…B полностью или с пропусками, при этом входы делителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы делителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов.

Указанный технический результат достигается также в устройстве, состоящем из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также N+M линий задержки, N+M фазовых корреляторов, выходы которых подключены к вычислительному устройству, в которое дополнительно введены N умножителей частоты, коэффициенты умножения которых выбраны из ряда 1,2,3…C полностью или с пропусками, M делителей частоты, коэффициенты деления которых выбраны из ряда 1,2,3…D полностью или с пропусками, при этом входы умножителей частоты и делителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы умножителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, первые выходы делителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов.

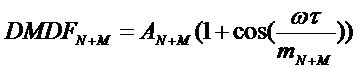

Сущность изобретения поясняется чертежами на фигурах 1,2,3. На фиг.1 представлена структурная схема широкополосного измерителя частоты СВЧ сигналов с умножителями частоты. Широкополосный измеритель частоты СВЧ сигналов содержит: входной широкополосный усилитель-ограничитель 1, полосно-пропускающий СВЧ фильтр 2, делитель 3 СВЧ мощности, умножители частоты 4.1…4.N, линии задержки 5.1…5.N, фазовые корреляторы 6.1…6.N, вычислительное устройство 7.

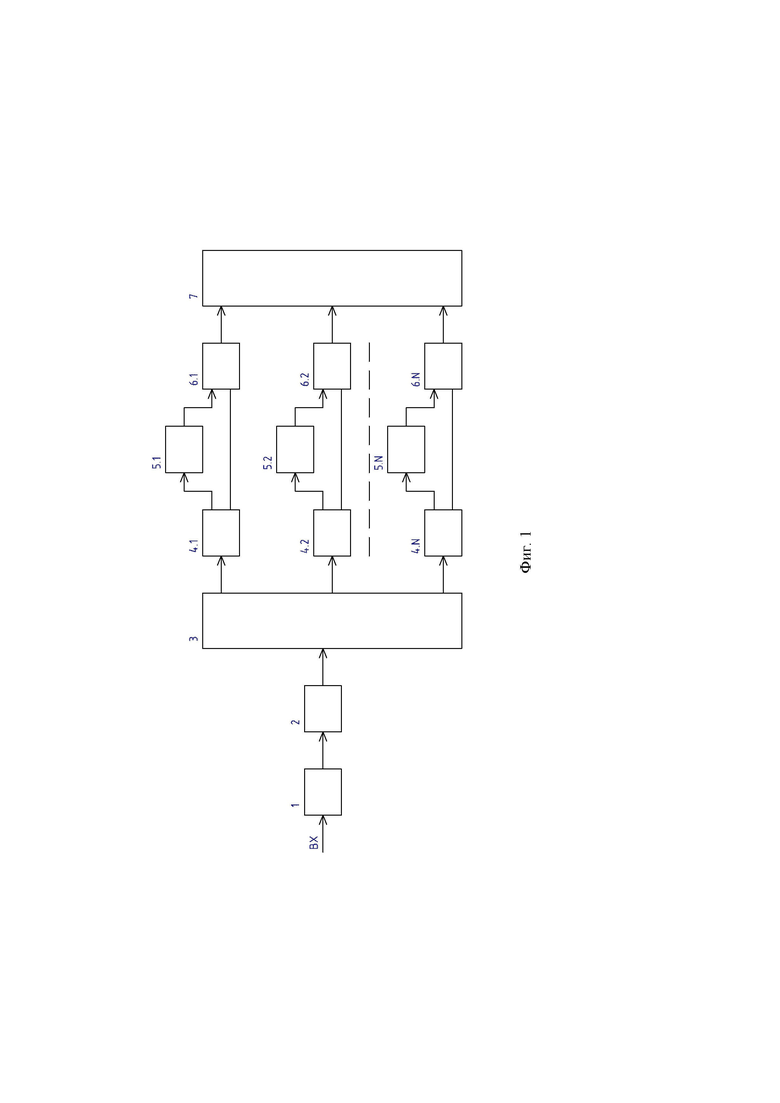

На фиг.2 представлена структурная схема широкополосного измерителя частоты СВЧ сигналов с делителями частоты. Широкополосный измеритель частоты СВЧ сигналов содержит: входной широкополосный усилитель-ограничитель 8, полосно-пропускающий СВЧ фильтр 9, делитель 10 СВЧ мощности, делители частоты 11.1…11.M, линии задержки 12.1…12.M, фазовые корреляторы 13.1…13.M, вычислительное устройство 14.

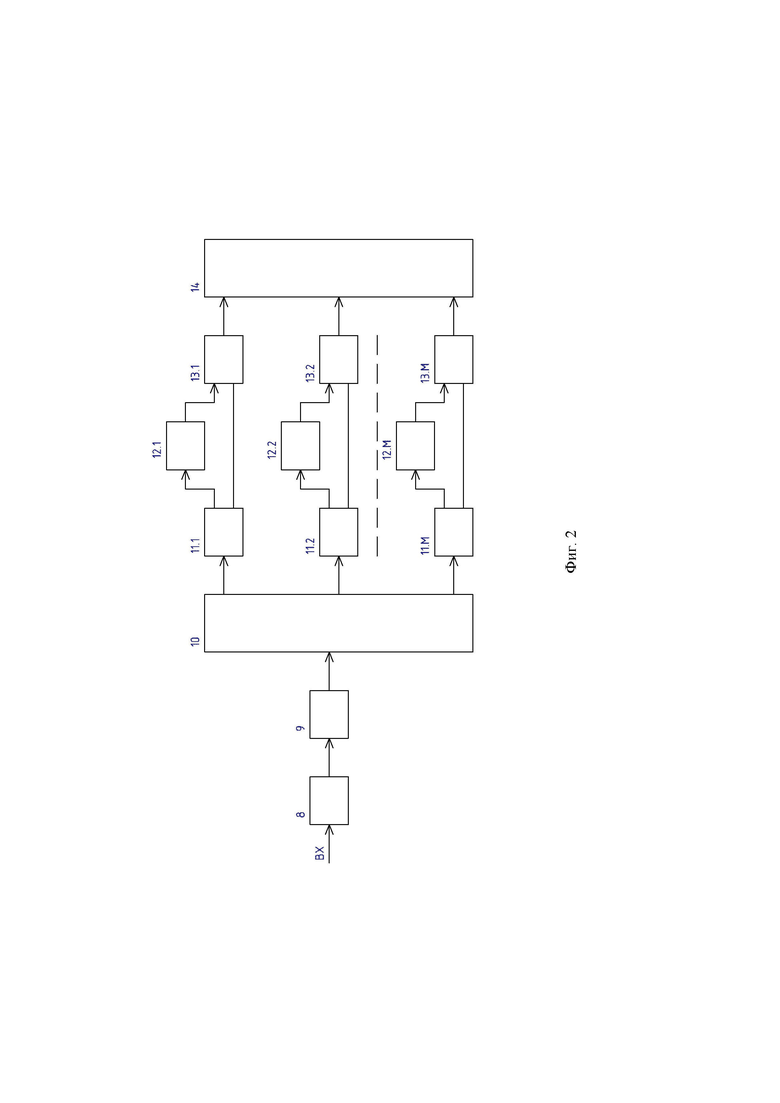

На фиг.3 представлена структурная схема широкополосного измерителя частоты СВЧ сигналов с умножителями и делителями частоты. Широкополосный измеритель частоты СВЧ сигналов содержит: входной широкополосный усилитель-ограничитель 15, полосно-пропускающий СВЧ фильтр 16, делитель 17 СВЧ мощности, умножители частоты 18.1…18.N, делители частоты 19.1…19.N, линии задержки 20.1…20.N+M, фазовые корреляторы 21.1…21.N+M, вычислительное устройство 22.

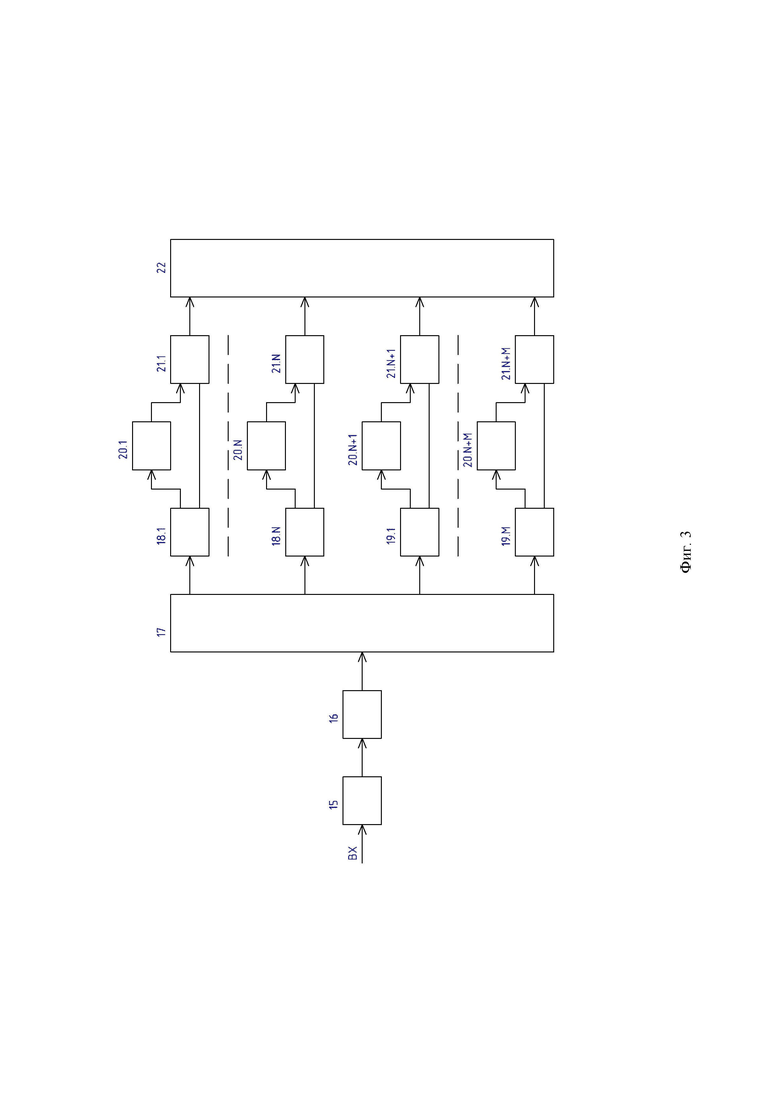

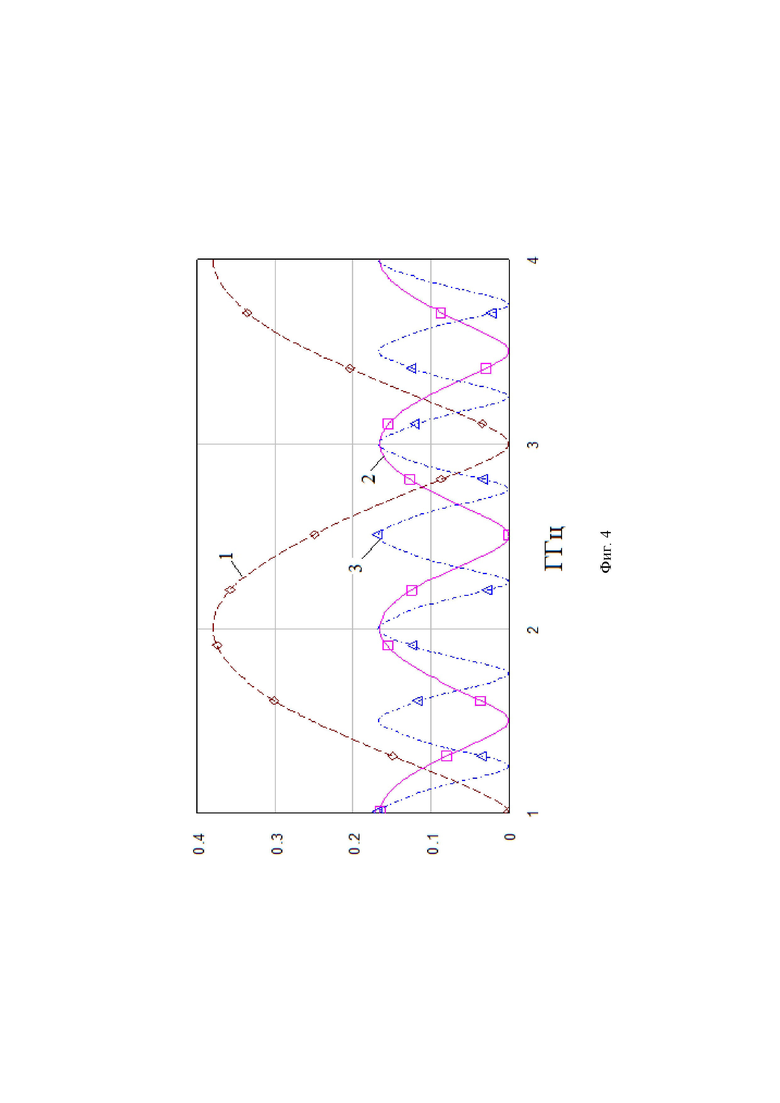

На фиг.4 представлена дискриминационная характеристика фазовых корреляторов.

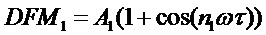

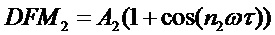

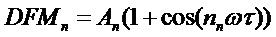

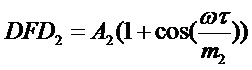

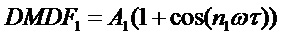

Для удобства рассмотрим работу широкополосного измерителя частоты, функциональная схема которого представлена на фигуре 1. Широкополосный измеритель частоты СВЧ сигналов работает следующим образом. Входной СВЧ сигнал с частотой ω0 поступает через усилитель-ограничитель 1 на полосно-пропускающий фильтр 2, ограничивающий входную полосу частот. Далее сигнал поступает на синфазный делитель 3 СВЧ мощности, где происходит деление мощности входного сигнала на N равных частей. Умножители частоты 4.1…4.N осуществляют функцию умножения частоты и могут быть выполнены на основе диода или транзистора, работающего в нелинейном режиме, или в виде специализированной микросхемы. Коэффициенты умножения умножителей частоты 4.1…4.N выбраны из ряда 1,2,3…A полностью или с пропусками, где А - конечное число, предельный коэффициент умножения, выбираемый из условия физической реализуемости или заданной точности измерения частоты. При коэффициенте умножения частоты одного из умножителей равном 1 преобразования частоты не происходит, и входной сигнал через делитель мощности поступает на фазовый коррелятор. Число умножителей 4.1…4.N, линий задержки 5.1…5.N, фазовых корреляторов 6.1…6.N определяется рабочей полосой устройства и требуемой точностью измерения частоты. Предположим, что коэффициент умножения умножителя частоты 4.1 равен n1, умножителя частоты 4.2 равен n2, умножителя частоты 4.3 равен n3, и так далее до nN, причем nN>…>n3>n2>n1. При этом на выходах умножителей 4.1,4.2,…,4.N частоты получим сигналы с частотами n1ω0, n2ω0, n3ω0,…, nNω0 соответственно. Также предположим, что линии задержки 5.1,5.2,…,5.N идентичны и имеют равное время задержки равное τ. Тогда фазовые набеги, приобретаемые сигналами на выходах линий задержки 5.1,5.2,…,5.N, составят: θ1=n1ω0τ, θ2=n2ω0τ,…, θn=nnω0τ. В тоже время, фазовые набеги, приобретаемые сигналами на выходах линий задержки в устройстве-прототипе, можно описать выражениями: ∆1=ω0τ1, ∆2=ω0τ2,…, ∆n=ω0τn. Принимая во внимание, что τ1=s1τ, τ2=s2τ,…,τn=snτ, где sn>…>s2>s1 – некоторые числа, приходим к идентичности выражений для фазового набега сигналов на выходе линий задержки в устройстве-прототипе и предлагаемом устройстве. При этом прохождение сигнала с частотой nω0 через линию задержки τ в предлагаемом устройстве эквивалентно прохождению сигнала с частотой ω0 через линию задержки nτ в устройстве-прототипе, что позволяет применить в предлагаемом устройстве более короткую и компактную линию задержки. Задержанные в линиях задержки 5.1,5.2,…,5.N и незадержанные сигналы подаются соответственно на фазовые корреляторы 6.1,6.2,…,6.N. Фазовые корреляторы 6.1,6.2,…,6.N формируют следующие дискриминационные характеристики, вид которых показан на фигуре 4 (DFM1 – 1, DFM2 – 2,…, DFMn – 3 и так далее):

где A1, A2,…, An – коэффициенты пропорциональности;

n1,n2,…,nn – коэффициенты умножения частоты;

τ – время задержки линии задержки;

ω – круговая частота.

Коррелятор 6.1, стоящий в одном канале с умножителем частоты 4.1 имеет в рабочем диапазоне частот однозначную, но относительно пологую дискриминационную характеристику, по этой причине коррелятор 6.1 служит для грубой оценки частоты входного сигнала. В тоже время фазовые корреляторы 6.2,…,6.N имеют неоднозначные корреляционные функции, крутизна которых выше по сравнению с крутизной корреляционной характеристики коррелятора 6.1. Корреляторы 6.2,6.3,…6.N служат для повышения точности измерения частоты входного сигнала. Вычислительное устройство 7 предназначено определения частоты входного сигнала по напряжениям от фазовых корреляторов 6.1,6.2,…,6.N.

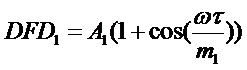

Широкополосный измеритель частоты также может быть реализован с применением делителей частоты. Широкополосный измеритель частоты СВЧ сигналов работает следующим образом. Входной СВЧ сигнал с частотой ω0 поступает через усилитель-ограничитель 8 на полосно-пропускающий фильтр 9, ограничивающий входную полосу частот. Далее сигнал поступает на синфазный делитель 10 СВЧ мощности, где происходит деление мощности входного сигнала на M равных частей. Делители частоты 11.1…11.M осуществляют функцию деления частоты и могут быть выполнены на основе нелинейных элементов или специализированных микросхем делителей частоты. Коэффициенты деления делителей 11.1…11.M частоты выбраны из ряда 1,2,3…B полностью или с пропусками, где B - конечное число, предельный коэффициент деления, выбираемый из условия заданного диапазона рабочих частот. При коэффициенте деления частоты одного из делителей равном 1 преобразования частоты не происходит и входной сигнал через делитель мощности поступает на соответствующий фазовый коррелятор. Число делителей 11.1…11.M частоты, линий задержки 12.1…12.M, фазовых корреляторов 13.1…13.M определяется рабочей полосой устройства и требуемой точностью измерения частоты. Предположим, что коэффициент деления делителя 11.1 частоты равен m1, делителя 11.2 частоты равен m2, делителя 11.3 частоты равен m3, и так далее до mM, причем mM>…>m3>m2>m1. При этом на выходах делителей 11.1,11.2,…,11.M частоты получим сигналы с частотами ω0/m1, ω0/m2,…, ω0/mm. Также предположим, что линии задержки 12.1,12.2,…,12.M идентичны и имеют равное время задержки равное τ. Тогда фазовые набеги, приобретаемые сигналами на выходах линий задержки 12.1,12.2,…,12.M, составят: θ1=ω0τ/m1, θ2= ω0τ/m2,…, θm= ω0τ/mm. В тоже время, фазовые набеги, приобретаемые сигналами на выходах линий задержки в устройстве-прототипе можно описать выражениями: ∆1=ω0τ1, ∆2=ω0τ2,…, ∆m=ω0τm. Принимая во внимание, что τ1=τ/m1, τ2=τ/m2,…, τm=τ/mm, приходим к идентичности выражений для фазового набега сигналов на выходе линий задержки в предлагаемом устройстве и устройстве-прототипе. Время задержки линий задержки 12.1,12.2,…,12.M-1 и коэффициенты деления делителей 11.1,11.2,…,11.M-1 частоты выбраны так, чтобы корреляционные характеристики фазовых корреляторов 13.1,13.2,…,13.M-1 имели крутизну, обеспечивающую заданную точность измерения частоты. Время задержки линии задержки 12.M может быть выбрано идентичным линиям задержки 12.1,12.2,…,12.M-1, а однозначность корреляционной характеристики фазового коррелятора 13.M будет обеспечена выбором коэффициента деления частоты делителя 11.M частоты. Это позволяет унифицировать применяемые линии задержки. Задержанные в линиях задержки 12.1,12.2,…,12.M и незадержанные сигналы подаются на соответствующие фазовые корреляторы 13.1,13.2,…,13.M. Фазовые корреляторы 13.1,13.2,…,13.M формируют следующие дискриминационные характеристики, вид которых показан на фигуре 4 (DFD1 – 3, DFD2 – 2, DFDM - 1):

где A1, A2,.., AM – коэффициенты пропорциональности;

m1,m2,..,mM – коэффициенты деления частоты;

τ – время задержки линии задержки;

ω – круговая частота.

Коррелятор 13.M, стоящий в одном канале с делителем 11.M частоты имеет в рабочем диапазоне частот однозначную, но относительно пологую дискриминационную характеристику, по этой причине коррелятор 13.M служит для грубой оценки частоты входного сигнала. В тоже время фазовые корреляторы 13.1,13.2,…,13.M-1 имеют неоднозначные корреляционные функции, крутизна которых выше по сравнению с крутизной дискриминационной характеристики коррелятора 13.M. Корреляторы 13.1,13.2,…,13.M-1 служат для повышения точности измерения частоты входного сигнала. Вычислительное устройство 14 предназначено для определения частоты входного сигнала по напряжениям от фазовых корреляторов 13.1,13.2,…,13.M.

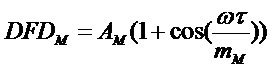

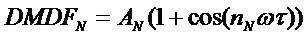

Широкополосный измеритель частоты также может быть реализован с применением делителей частоты и умножителей частоты. Входной СВЧ сигнал с частотой ω0 поступает через усилитель-ограничитель 15 на полосно-пропускающий фильтр 16, ограничивающий входную полосу частот. Далее сигнал поступает на синфазный делитель 17 СВЧ мощности, где происходит деление мощности входного сигнала на N+M равных частей. Умножители частоты 18.1…18.N осуществляют функцию умножения и могут быть выполнены на основе диода или транзистора, работающего в нелинейном режиме, или в виде специализированной микросхемы. Делители частоты 19.1…19.M осуществляют функцию деления частоты и могут быть выполнены на основе нелинейных элементов или специализированных микросхем. Коэффициенты умножения умножителей частоты 18.1…18.N выбраны из ряда 1,2,3…C полностью или с пропусками, где C - конечное число, предельный коэффициент умножения, выбираемый из условия физической реализуемости или заданной точности измерения частоты. Коэффициенты деления делителей частоты 19.1…19.M выбраны из ряда 1,2,3…D полностью или с пропусками, где D - конечное число, предельный коэффициент деления, выбираемый из условия заданного диапазона рабочих частот. При коэффициенте умножения частоты одного из умножителей или коэффициенте деления одного из делителей частоты равном 1 преобразования частоты не происходит, и входной сигнал через делитель мощности поступает на соответствующий фазовый коррелятор. Число умножителей 18.1…18.N частоты, делителей 19.1…19.M частоты, линий задержки 20.1…20.N+M, фазовых корреляторов 21.1…21.N+M определяется рабочей полосой устройства и требуемой точностью измерения частоты. Предположим, что коэффициент умножения умножителя частоты 18.1 равен n1, умножителя 18.2 частоты равен n2, и так далее до nN, причем nN>…>n3>n2>n1. Также предположим, что коэффициент деления делителя 19.1 частоты равен m1, делителя 19.2 частоты равен m2, и так далее до mM, причем mM>…>m3>m2>m1. При этом на выходах умножителей 18.1,18.2,…,18.N частоты получим сигналы с частотами n1ω0, n2ω0,…, nNω0 а на выходах делителей 19.1,19.2,…,19.M частоты получим сигналы с частотами ω0/m1, ω0/m2,…,ω0/mM. Также предположим, что линии задержки 20.1,20.2,…,20.N+M идентичны и имеют одинаковое время задержки равное τ. Тогда фазовые набеги, приобретаемые сигналами на выходах линий задержки 20.1,20.2,…,20.N+M, составят: θ1=n1ω0τ, θ2=n2ω0τ,…, θN=nNω0τ, θN+1=ω0τ/m1,…, θM=ω0τ/mM. В тоже время, фазовые набеги, приобретаемые сигналами на выходах линий задержки в устройстве-прототипе, можно описать выражениями: ∆1=ω0τ1, ∆2=ω0τ2,…, ∆N=ω0τN,…, ∆N+1=ω0/τN+1,…, ∆M=ω0/τM. Принимая во внимание, что τ1=n1τ, τ2=n2τ,…, τN=nNτ, τN+1=τ/mN+1,…,τM=τ/mM, приходим к идентичности выражений для фазового набега сигналов на выходе линий задержки в предлагаемом устройстве и устройстве-прототипе. При этом прохождение сигнала с частотой nω0 через линию задержки τ в предлагаемом устройстве эквивалентно прохождению сигнала с частотой ω0 через линию задержки nτ в устройстве-прототипе, что позволяет применить в предлагаемом устройстве более короткую и компактную линию задержки. Время задержки линий задержки 20.1,20.2,…,20.N+M-1, коэффициенты умножения умножителей 18.1,18.2,…,18.N частоты, коэффициенты деления делителей 19.1,19.2,…,19.M-1 частоты выбраны так, чтобы корреляционные характеристики фазовых корреляторов 21.1,21.2,…,21.N+M-1 имели крутизну, обеспечивающую заданную точность измерения частоты. Время задержки линии задержки 20.N+M может быть выбрано идентичным линиям задержки 20.1,20.2,…,20.N+M-1, а однозначность корреляционной характеристики фазового коррелятора 21.N+M будет обеспечена выбором коэффициента деления частоты делителя 19.M частоты. Задержанные в линиях задержки 20.1,20.2,…,20.N+M и незадержанные сигналы подаются соответственно на фазовые корреляторы 21.1,21.2,…,21.N+M. Фазовые корреляторы 21.1,21.2,…,21.N+M формируют следующие дискриминационные характеристики, вид которых показан на фигуре 4 (DMDF1 – 2, DMDFN – 3, DMDFN+M - 1):

...

где A1,.., AN, AN+M – коэффициенты пропорциональности;

n1,…,nN – коэффициенты умножения частоты;

m1,…,mM – коэффициенты деления частоты;

τ – время задержки линии задержки;

ω – круговая частота.

Коррелятор 21.N+M, имеет в рабочем диапазоне частот однозначную (кривая 1), но относительно пологую дискриминационную характеристику, по этой причине коррелятор 21.N+M служит для грубой оценки частоты входного сигнала. В тоже время фазовые корреляторы 21.1,21.2,…,21.N+M-1 имеют неоднозначные корреляционные функции (кривые 2 и 3 соответственно), крутизна которых выше по сравнению с крутизной дискриминационной характеристики коррелятора 21.N+M. Корреляторы 21.1, 21.2,…,21.N+M-1 служат для повышения точности измерения частоты входного сигнала. Вычислительное устройство 22 предназначено определения частоты входного сигнала по напряжениям от фазовых корреляторов 21.1,21.2,…,21.N+M.

Из описанных принципов работы понятно, что число каналов, включающих в себя делитель или умножитель частоты, линию задержки, фазовый коррелятор, может быть изменено для достижения заданного рабочего диапазона частот и точности измерения частоты.

Список использованных источников

1. Schmidt, R.O. Simultaneous signals IFM receiver using plural delay line correlators. Патент США на изобретение №5440228

2. Tsui, J.B.Y., Hedge, J.N. Instantaneous frequency measurement (IFM) receiver with two signals capability. Патент США на изобретение №5291125

Изобретение относится к измерительной технике и может быть использовано для оперативного измерения частоты непрерывных СВЧ сигналов в широком диапазоне частот. Сущность заявленного решения заключается в том, что широкополосный измеритель частоты СВЧ сигналов на линиях задержки с предварительным преобразованием частоты выполнены в нескольких вариантах. В первом случае в это устройство, состоящее из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также N линий задержки, N фазовых корреляторов, выходы которых подключены к вычислительному устройству, дополнительно введены N умножителей частоты, коэффициенты умножения которых выбраны из ряда 1,2,3…A полностью или с пропусками, при этом входы умножителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы умножителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов. Во втором случае в устройство, состоящее из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также M линий задержки, M фазовых корреляторов, выходы которых подключены к вычислительному устройству, дополнительно введены M делителей частоты, коэффициенты деления которых выбраны из ряда 1,2,3…B полностью или с пропусками, при этом входы делителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы делителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов. В третьем случае в устройство, состоящее из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также N+M линий задержки, N+M фазовых корреляторов, выходы которых подключены к вычислительному устройству, дополнительно введены N умножителей частоты, коэффициенты умножения которых выбраны из ряда 1,2,3…C полностью или с пропусками, M делителей частоты, коэффициенты деления которых выбраны из ряда 1,2,3…D полностью или с пропусками, при этом входы умножителей частоты и делителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы умножителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, первые выходы делителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов. Техническим результатом изобретения является уменьшение габаритных размеров и массы, повышение чувствительности устройства при сохранении точности измерения частоты за счет замены длинных линий задержки на короткие с предварительным преобразованием частоты входного сигнала путем деления и/или умножения. 3 н.п. ф-лы, 4 ил.

1. Широкополосный измеритель частоты СВЧ сигналов на линиях задержки с предварительным преобразованием частоты, состоящий из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также N линий задержки, N фазовых корреляторов, выходы которых подключены к вычислительному устройству, отличающийся тем, что в него дополнительно введены N умножителей частоты, коэффициенты умножения которых выбраны из ряда 1, 2, 3…A полностью или с пропусками, при этом входы умножителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы умножителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов.

2. Широкополосный измеритель частоты СВЧ сигналов на линиях задержки с предварительным преобразованием частоты, состоящий из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также M линий задержки, M фазовых корреляторов, выходы которых подключены к вычислительному устройству, отличающийся тем, что в него дополнительно введены M делителей частоты, коэффициенты деления которых выбраны из ряда 1, 2, 3…B полностью или с пропусками, при этом входы делителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы делителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов.

3. Широкополосный измеритель частоты СВЧ сигналов на линиях задержки с предварительным преобразованием частоты, состоящий из последовательно включенных входного усилителя-ограничителя, полосно-пропускающего СВЧ фильтра, синфазного делителя СВЧ мощности, а также N+M линий задержки, N+M фазовых корреляторов, выходы которых подключены к вычислительному устройству, отличающийся тем, что в него дополнительно введены N умножителей частоты, коэффициенты умножения которых выбраны из ряда 1, 2, 3…C полностью или с пропусками, M делителей частоты, коэффициенты деления которых выбраны из ряда 1, 2, 3…D полностью или с пропусками, при этом входы умножителей частоты и делителей частоты подключены к соответствующим выходам синфазного делителя СВЧ мощности, первые выходы умножителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, первые выходы делителей частоты подключены к входам соответствующих линий задержки, а вторые выходы к одному из входов соответствующих фазовых корреляторов, выходы линий задержки подключены к другому входу соответствующих фазовых корреляторов.

| US 20040008020 A1, 15.01.2004 | |||

| ШИРОКОПОЛОСНЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТЫ СВЧ СИГНАЛОВ С ПРЕДВАРИТЕЛЬНЫМ УМНОЖЕНИЕМ ЧАСТОТЫ | |||

| Ж., Издательство "Научтехлитиздат" | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Анализатор спектра | 1988 |

|

SU1567992A1 |

| US 9664715 В2, 30.05.2017 | |||

| JP 10319058 А, 04.12.1998 | |||

| US 5913158 А1, 15.06.1999. | |||

Авторы

Даты

2020-01-14—Публикация

2019-04-03—Подача