1

(21)4384161/24-21

(22)25.02.88

(46) 30.05.90. Бюл. № 20

(71)Институт технической кибернетики АН БССР

(72)В.И.Петько, В.Е.Куконин и П.М.Чеголин

(53) 621.317(088.8)

(56)Авторское свидетельство СССР 1095357, кл, Н 03 Н 17/04, 1984.

Спектральный анализатор 2030 фирмы Брюль и Кьер. Каталог фирмы Брюль и Кьер, 1980. (54) АНАЛИЗАТОР СПЕКТРА

(57)Изобретение относится к вычислительной технике и предназначено для получения спектра мощности или амплитудного спектра аналогового сигнала. Цель изобретения - повышение точности спектрального анализа - достигается в результате скачкообразного сканирования спектра цифровым полосовым фильтром. Анализатор содержит вход 1, аналоговые фильтры 2, 13 нижних частот, генератор 3 тактовой частоты, блок 4 синхронизации, аналого- цифровой преобразователь 5, промежуточный запоминающий блок 6, запоминающий блок 7 с перезаписью, генератор 8 качающейся частоты, генератор 9 линейно нарастающего ступенчатого напряжения, цифровой полосовой фильтр 10, блок II постоянной памяти, циф- роаналоговый преобразователь 12, коммутаторы 14, 17, блок 15 коррекции, блок 16 выделения частотных полос, квадратор 18, выход 19. Введение цифрового полосового фильтра 10, блока 11 постоянной памяти позволяет повысить точность анализа. 5 ил. I

5

(Л

Изобретение относится к вычислительной технике и предназначено для получения спектра мощности или амплитудного спектра аналогового сигнала.

Целью изобретения является повышение точности спектрального анализа за счет скачкообразного сканирования спектра цифровым полосовым фильтром.

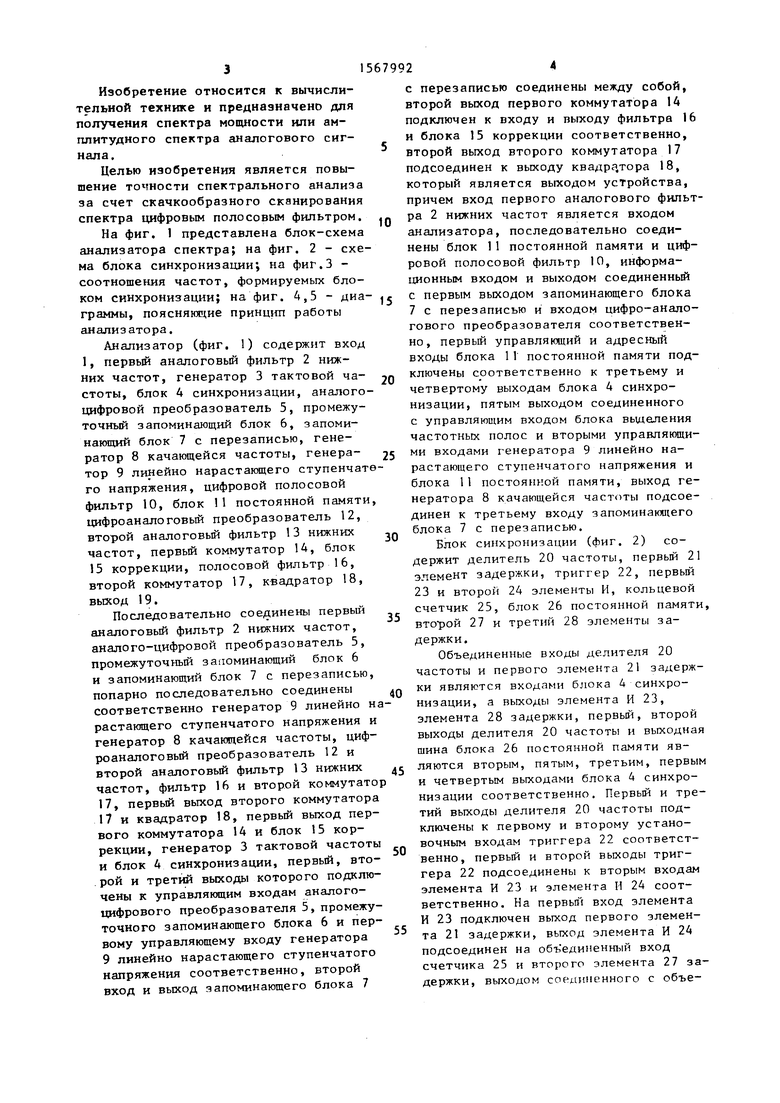

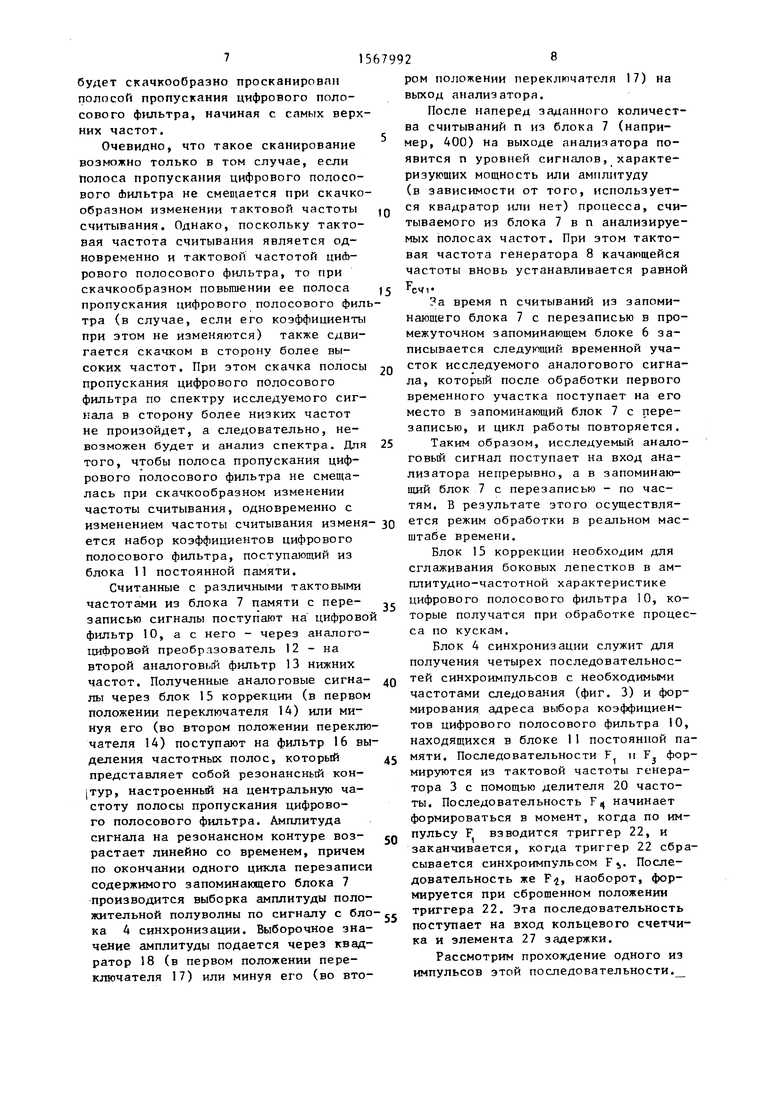

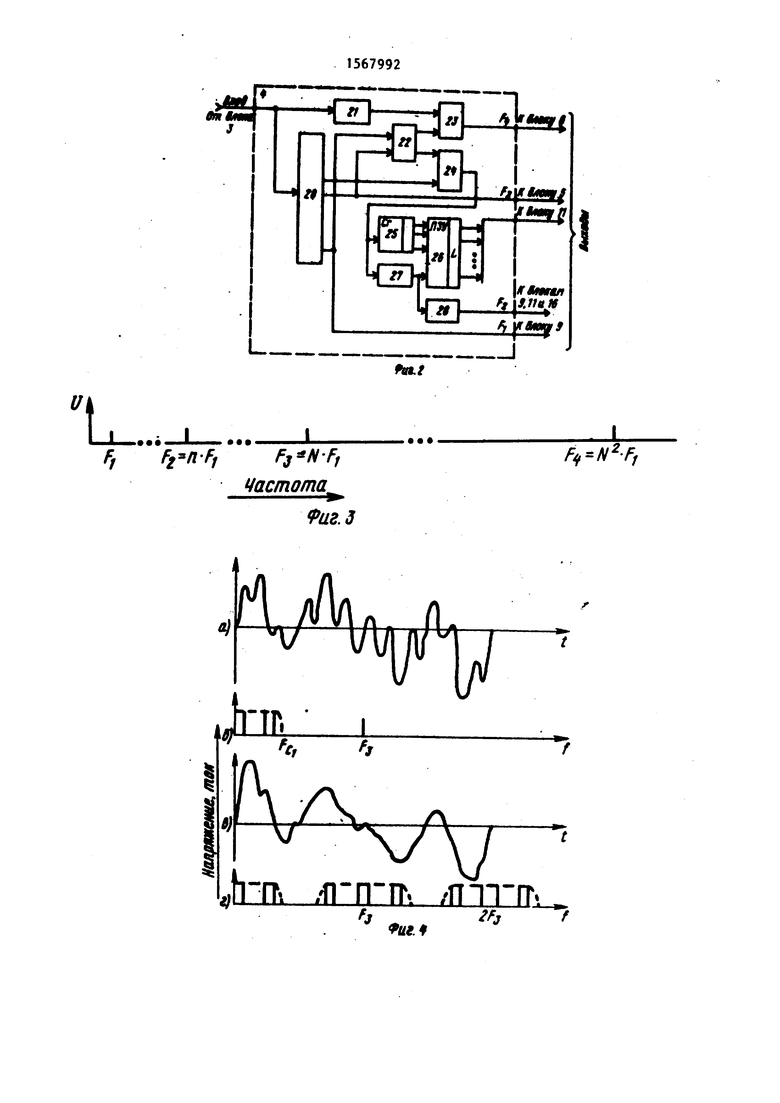

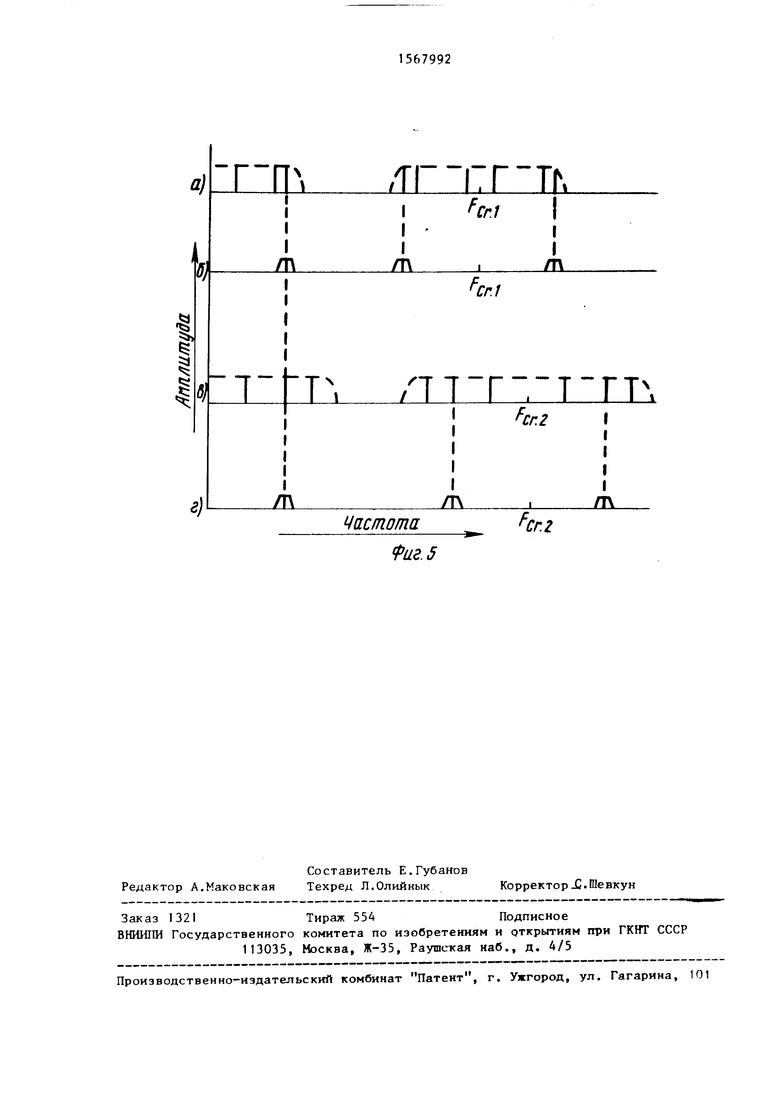

На фиг. 1 представлена блок-схема анализатора спектра; на фиг. 2 - схема блока синхронизации; на фиг.З - соотношения частот, формируемых бло

с перезаписью соединены между собой, второй выход первого коммутатора 14 подключен к входу и выходу фильтра 16 и блока 15 коррекции соответственно, второй выход второго коммутатора 17 подсоединен к выходу квадра/гора 18, который является выходом устройства, причем вход первого аналогового фильтра 2 нижних частот является входом анализатора, последовательно соединены блок 11 постоянной памяти и цифровой полосовой фильтр 10, информационным входом и выходом соединенный

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1988 |

|

SU1619190A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ВИДОВ МАНИПУЛЯЦИИ ЦИФРОВЫХ СИГНАЛОВ | 2005 |

|

RU2309414C2 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЭЛЕКТРОННЫХ СИГНАЛОВ ЦВЕТНОГО ИЗОБРАЖЕНИЯ ОБЪЕКТОВ (ВАРИАНТЫ) | 2003 |

|

RU2258319C2 |

| Устройство для воспроизведения магнитной записи с коррекцией временных искажений | 1985 |

|

SU1278938A1 |

| Способ автоматического анализа спектра сигналов с временной компрессией и устройство для его осуществления | 1987 |

|

SU1619189A1 |

| Аналого-цифровой дисперсионный анализатор спектра | 1980 |

|

SU892337A1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| Цифровой генератор случайных процессов | 1978 |

|

SU750466A1 |

Изобретение относится к вычислительной технике и предназначено для получения спектра мощности или амплитудного спектра аналогового сигнала. Цель изобретения - повышение точности спектрального анализа - достигается в результате скачкообразного сканирования спектра цифровым полосовым фильтром. Анализатор содержит вход 1, аналоговые фильтры 2, 13 нижних частот, генратор 3 тактовой частоты, блок 4 синхронизации, аналого-цифровой преобразователь 5, промежуточный запоминающий блок 6, запоминающий блок 7 с перезаписью, генератор 8 качающейся частоты, генератор 9 линейно нарастающего ступенчатого напряжения, цифровой полосовой фильтр 10, блок 11 постоянной памяти, цифроаналоговый преобразователь 12, коммутаторы 14, 17, блок 15 коррекции, блок 16 выделения частотных полос, квадратор 18, выход 19. Введение цифрового полосового фильтра 10, блока 11 постоянной памяти позволяет повысить точность анализа. 5 ил.

ком синхронизации; на фиг. 4,5 - диа- j. с первым выходом запоминающего блока

20

25

30

35

граммы, поясняющие принцип работы анализатора.

Анализатор (фиг. 1) содержит вход 1, первый аналоговый фильтр 2 нижних частот, генератор 3 тактовой частоты, блок 4 синхронизации, аналого- цифровой преобразователь 5, промежуточный запоминающий блок 6, запоминающий блок 7 с перезаписью, генератор 8 качающейся частоты, генератор 9 линейно нарастающего ступенчате- го напряжения, цифровой полосовой фильтр 10, блок 11 постоянной памяти, цифреаналоговый преобразователь 12, второй аналоговый фильтр 13 нижних частот, первый коммутатор 14, блок 15 коррекции, полосовой фильтр 16, второй коммутатор 17, квадратор 18, выход 19.

Последовательно соединены первый аналоговый фильтр 2 нижних частот, аналого-цифровой преобразователь 5, промежуточный запоминающий блок 6 и запоминающий блок 7 с перезаписью, попарно последовательно соединены соответственно генератор 9 линейно нарастающего ступенчатого напряжения и генератор 8 качающейся частоты, циф- роаналоговый преобразователь 12 и второй аналоговый фильтр 13 нижних д частот, фильтр 16 и второй коммутатор 17, первый выход второго коммутатора 17 и квадратор 18, первый выход первого коммутатора 14 и блок 15 коррекции, генератор 3 тактовой частоты и блок 4 синхронизации, первый, второй и третий выходы которого подключены к управляющим входам аналого- цифрового преобразователя 5, промежуточного запоминающего блока 6 и первому управляющему входу генератора 9 линейно нарастающего ступенчатого напряжения соответственно, второй вход и выход запоминающего блока 7

40

50

55

7 с перезаписью и входом цифро-аналогового преобразователя соответственно, первый управляющий и адресный входы блока 11 постоянной памяти подключены соответственно к третьему и четвертому выходам блока 4 синхронизации, пятым выходом соединенного с управляющим входом блока выделения частотных полос и вторыми управляющими входами генератора 9 линейно нарастающего ступенчатого напряжения и блока 11 постоянной памяти, выход генератора 8 качающейся частоты подсоединен к третьему входу запоминающего блока 7 с перезаписью.

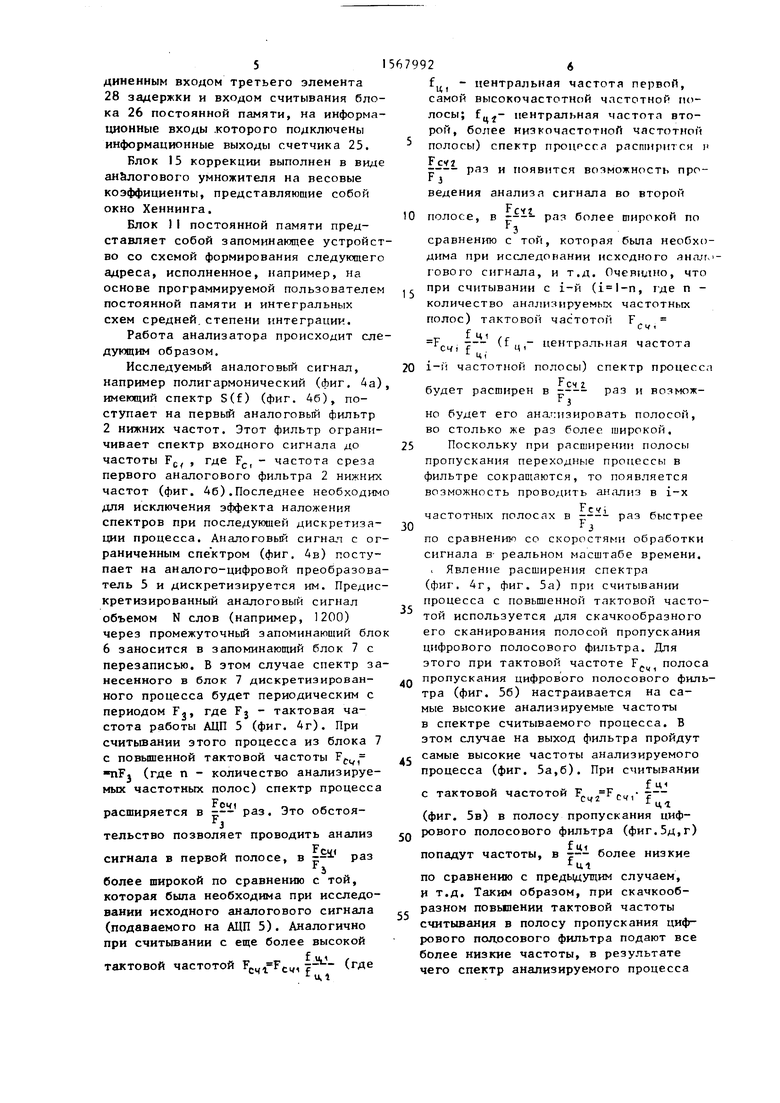

Блок синхронизации (фиг. 2) содержит делитель 20 частоты, первый 2 элемент задержки, триггер 22, первый 23 и второй 24 элементы И, кольцевой счетчик 25, блок 26 постоянной памят 27 и третий 28 элементы задержки.

Объединенные входы делителя 20 частоты и первого элемента 21 задерж ки являются входами блока 4 синхронизации, а выходы элемента И 23, элемента 28 задержки, первый, второй выходы делителя 20 частоты и выходна шина блока 26 постоянной памяти являются вторым, пятым, третьим, первы и четвертым выходами блока 4 синхронизации соответственно. Первый и тре тий выходы делителя 20 частоты подключены к первому и второму установочным входам триггера 22 соответственно, первый и второй выходы триггера 22 подсоединены к вторым входам элемента И 23 и элемента II 24 соответственно. На первый вход элемента И 23 подключен выход первого элемента 21 задержки, выход элемента И 24 подсоединен на объединенный вход счетчика 25 и второго элемента 27 за держки, выходом соединенного с объе. с первым выходом запоминающего блока

0

5

30

35

д

40

50

55

7 с перезаписью и входом цифро-аналогового преобразователя соответственно, первый управляющий и адресный входы блока 11 постоянной памяти подключены соответственно к третьему и четвертому выходам блока 4 синхронизации, пятым выходом соединенного с управляющим входом блока выделения частотных полос и вторыми управляющими входами генератора 9 линейно нарастающего ступенчатого напряжения и блока 11 постоянной памяти, выход генератора 8 качающейся частоты подсоединен к третьему входу запоминающего блока 7 с перезаписью.

Блок синхронизации (фиг. 2) содержит делитель 20 частоты, первый 21 элемент задержки, триггер 22, первый 23 и второй 24 элементы И, кольцевой счетчик 25, блок 26 постоянной памяти, 27 и третий 28 элементы задержки.

Объединенные входы делителя 20 частоты и первого элемента 21 задержки являются входами блока 4 синхронизации, а выходы элемента И 23, элемента 28 задержки, первый, второй выходы делителя 20 частоты и выходная шина блока 26 постоянной памяти являются вторым, пятым, третьим, первым и четвертым выходами блока 4 синхронизации соответственно. Первый и третий выходы делителя 20 частоты подключены к первому и второму установочным входам триггера 22 соответственно, первый и второй выходы триггера 22 подсоединены к вторым входам элемента И 23 и элемента II 24 соответственно. На первый вход элемента И 23 подключен выход первого элемента 21 задержки, выход элемента И 24 подсоединен на объединенный вход счетчика 25 и второго элемента 27 задержки, выходом соединенного с объе

5

диненным входом третьего элемента 28 задержки и входом считывания блока 26 постоянной памяти, на информационные входы .которого подключены информационные выходы счетчика 25.

Блок 15 коррекции выполнен в виде аналогового умножителя на весовые коэффициенты, представляющие собой окно Хеннинга.

Блок 1I постоянной памяти представляет собой запоминающее устройство со схемой формирования следующего адреса, исполненное, например, на основе программируемой пользователем постоянной памяти и интегральных схем средней, степени интеграции.

Работа анализатора происходит следующим образом.

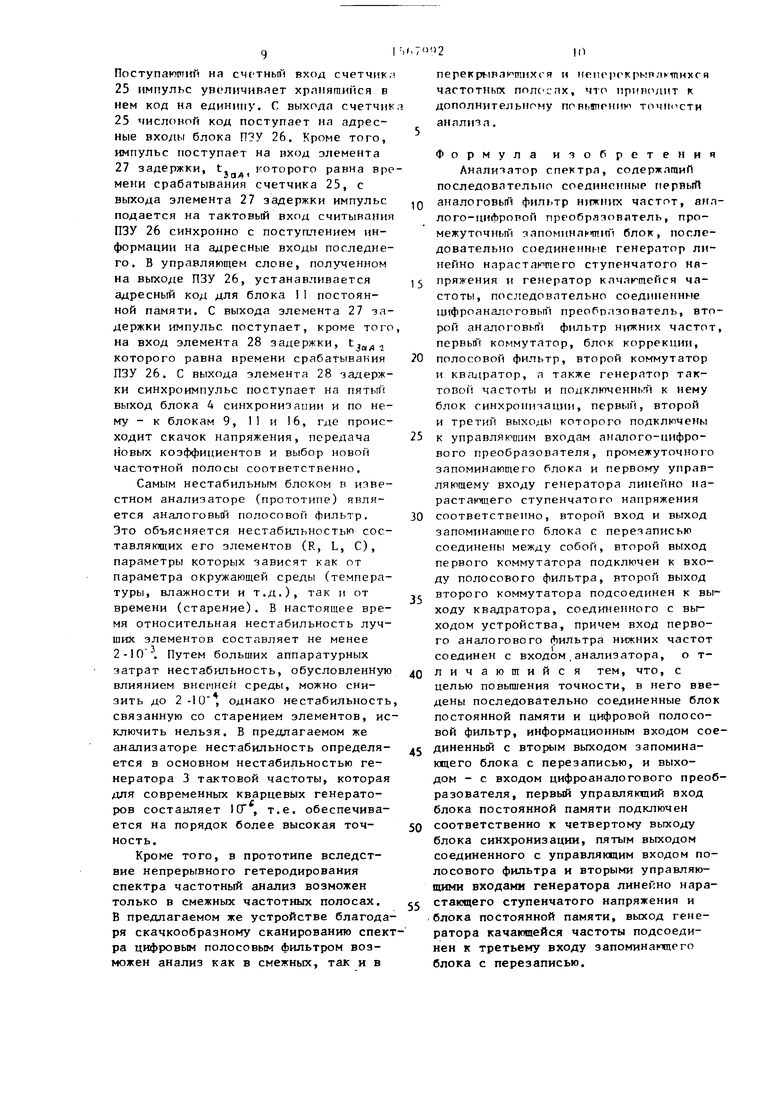

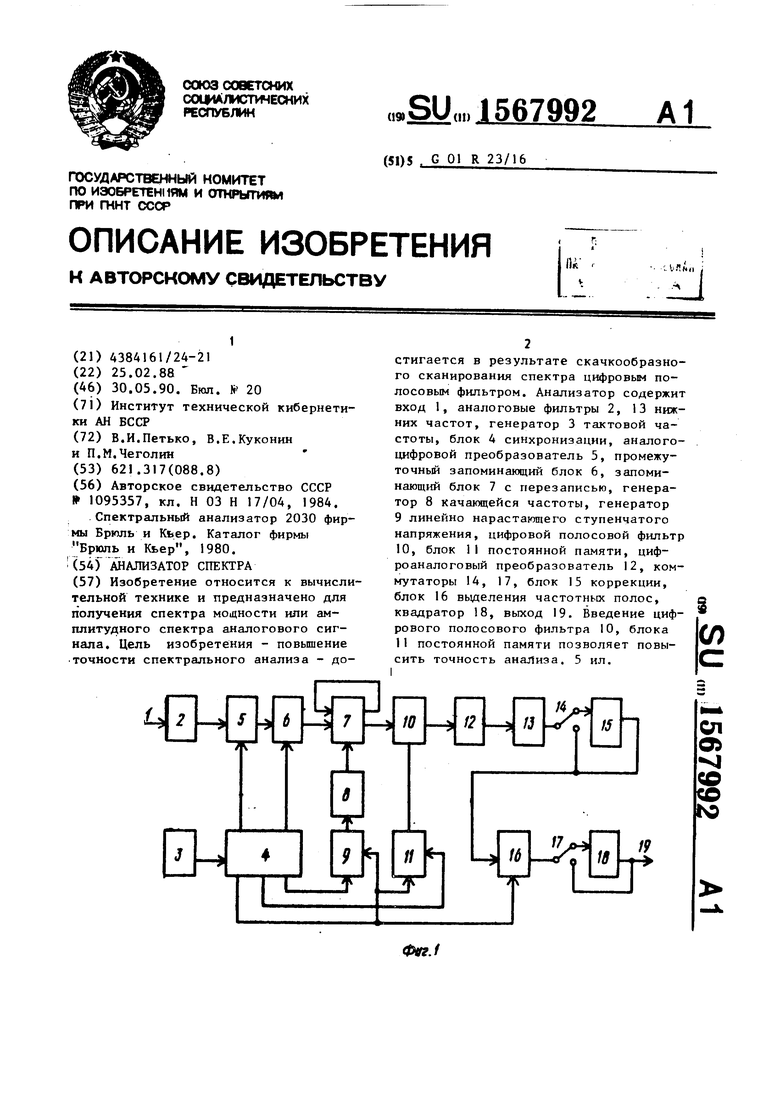

Исследуемый аналоговый сигнал, например полигармонический (фиг. 4а) имеющий спектр S(f) (фиг. 46), поступает на первый аналоговый фильтр 2 нижних частот. Этот фильтр ограничивает спектр входного сигнала до частоты FCf , где FC| - частота среза первого аналогового фильтра 2 нижних частот (фиг. 4б).Последнее необходим для исключения эффекта наложения спектров при последующей дискретизации процесса. Аналоговый сигнал с ограниченным спектром (фиг. 4в) поступает на аналого-цифровой преобразователь 5 и дискретизируется им. Предис кретизированный аналоговый сигнал объемом N слов (например, 1200) через промежуточный запоминающий бло 6 заносится в запоминающий блок 7 с перезаписью. В этом случае спектр занесенного в блок 7 дискретизирован- ного процесса будет периодическим с

F3 тактовая чапериодом F3, где

стота работы АЦП 5 (фиг. 4г). При считывании этого процесса из блока 7 с повышенной тактовой частоты FCw «nFi (где п - количество анализируемых частотных полос) спектр процесса

Fowl расширяется в -- раз,

3 тельство позволяет проводить анализ

Это обстоясигнала в

первой полосе, в раз попадут частоты, в

более широкой по сравнению с той, которая была необходима при исследовании исходного аналогового сигнала (подаваемого на АЦП 5). Аналогично при считывании с еще более высокой

тактовой частотой FC4/l-Fc ё (гДе

1 u, t

f

- центральная частота первой, самой высокочастотной частотной полосы; нейтральная частота второй, более низкочастотной частотной полосы) спектр процесса расширится i Fey 2

ГГ раз

и появится возможность проведения анализа сигнала во второй

Гсчг. F,

полосе, в

раз более широкой по

5

0

5

0

F,

сравнению с той, которая была необходима при исследовании исходного аналогового сигнала, и т.д. Очевидно, что при считывании с i-й (, где п - количество анализируемых частотных полос) тактовой частотой F,

--4-1 (f С L Щ 1 Ui

сч. частота

сч, f центральная

iй частотной полосы) спектр процесса

Гсч 2 будет расширен в раз и возможг з

но будет его анализировать полосой, во столько же раз более широкой.

Поскольку при расширении полосы пропускания переходные процессы в фильтре сокращаются, то появляется возможность проводить анализ в 1-х

---L раз быстрее

частотных полосах в

5

0

5

0

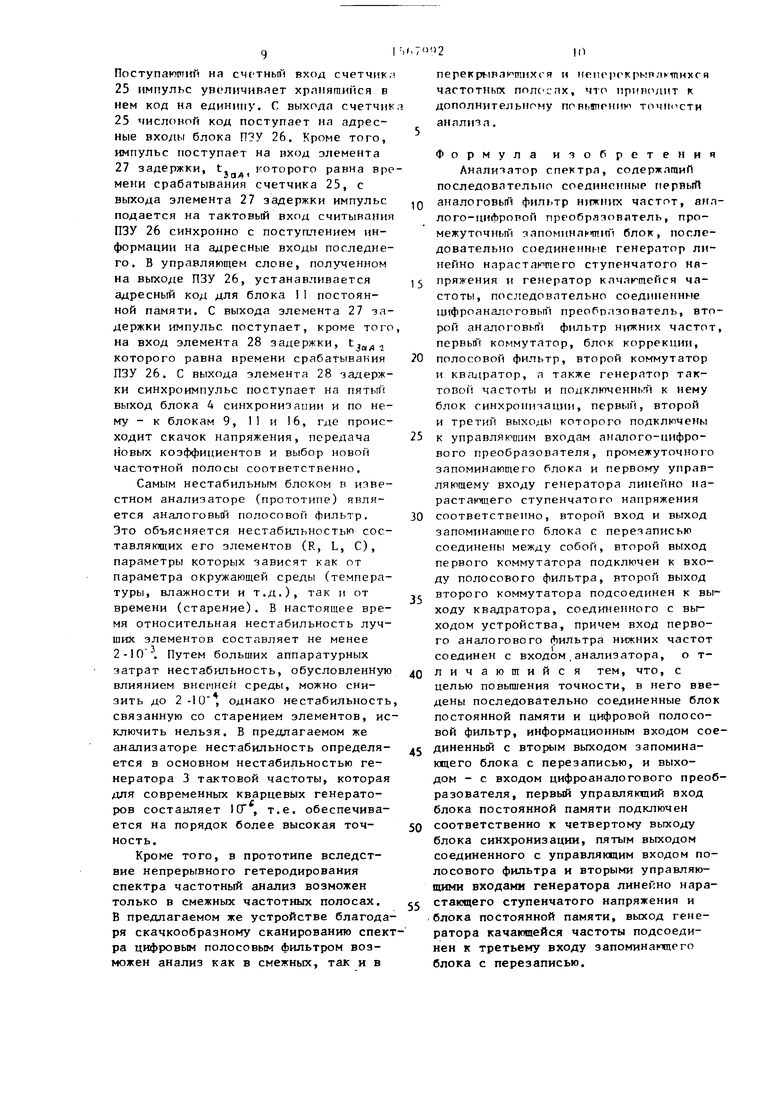

по сравнению со скоростями обработки сигнала в- реальном масштабе времени. с Явление расширения спектра (фиг. 4г, фиг. 5а) при считывании процесса с повышенной тактовой частотой используется для скачкообразного его сканирования полосой пропускания цифрового полосового фильтра. Для этого при тактовой частоте Ff4i полоса пропускания цифрового полосового фильтра (фиг. 56) настраивается на самые высокие анализируемые частоты в спектре считываемого процесса. В этом случае на выход фильтра пройдут самые высокие частоты анализируемого процесса (фиг. 5а,б). При считывании

,J

ц

(фиг. 5в) в полосу пропускания цифрового полосового фильтра (фиг.5д,г)

с тактовой

частотой FC42 FC41попадут частоты, в

| более

f U1

низкие

по сравнению с предыдущим случаем, И т.д. Таким образом, при скачкообразном повышении тактовой частоты считывания в полосу пропускания цифрового полосового фильтра подают все более низкие частоты, в результате чего спектр анализируемого процесса

11

будет скачкообразно просканирован полосой пропускания цифрового полосового фильтра, начиная с самых верхних частот.

Очевидно, что такое сканирование возможно только в том случае, если полоса пропускания цифрового полосового Лильтра не смещается при скачкообразном изменении тактовой частоты считывания. Однако, поскольку тактовая частота считывания является одновременно и тактовой частотой рового полосового фильтра, то при скачкообразном повышении ее полоса пропускания цифрового полосового филтра (в случае, если его коэффициенты при этом не изменяются) также сдвигается скачком в сторону более высоких частот. При этом скачка полосы пропускания цифрового полосового фильтра по спектру исследуемого сигнала в сторону более низких частот не произойдет, а следовательно, невозможен будет и анализ спектра. Для того, чтобы полоса пропускания цифрового полосового фильтра не смещалась при скачкообразном изменении частоты считывания, одновременно с изменением частоты считывания изменя ется набор коэффициентов цифрового полосового фильтра, поступающий из блока 11 постоянной памяти.

Считанные с различными тактовыми частотами из блока 7 памяти с перезаписью сигналы поступают на цифрово фильтр 10, а с него - через аналого- цифровой преобразователь 12 - на второй аналоговьй фильтр 13 нижних частот. Полученные аналоговые сигналы через блок 15 коррекции (в первом положении переключателя 14) или минуя его (во втором положении переключателя 14) поступают на фильтр 16 выделения частотных полос, который представляет собой резонансный кон- |тур, настроенный на центральную частоту полосы пропускания цифрового полосового фильтра. Амплитуда сигнала на резонансном контуре возрастает линейно со временем, причем по окончании одного цикла перезаписи содержимого запоминающего блока 7 производится выборка амплитуды положительной полуволны по сигналу с блока 4 синхронизации. Выборочное значение амплитуды подается через квадратор 18 (в первом положении переключателя 17) или минуя его (во вто

0

5

0

25

7992

30

д5

35

40

50

55

8

ром положении переключателя 17) на выход анализатора.

После наперед заданного количества считываний п из блока 7 (например, 400) на выходе анализатора появится п уровнен сигналов, характеризующих мощность или амплитуду (в зависимости от того, используется квадратор или нет) процесса, считываемого из блока 7 в п анализируемых полосах частот. При этом тактовая частота генератора 8 качающейся частоты вновь устанавливается равной

СЧ1«

а время п считываний из запоминающего блока 7 с перезаписью в промежуточном запоминающем блоке 6 записывается следующий временной участок исследуемого аналогового сигнала, который после обработки первого временного участка поступает на его место в запоминающий блок 7 с перезаписью, и цикл работы повторяется.

Таким образом, исследуемый аналоговый сигнал поступает на вход анализатора непрерывно, а в запоминающий блок 7 с перезаписью - по частям. В результате этого осуществляется режим обработки в реальном масштабе времени.

Блок 15 коррекции необходим для сглаживания боковых лепестков в амплитудно-частотной характеристике цифрового полосового фильтра 10, которые получатся при обработке процесса по кускам.

Блок 4 синхронизации служит для получения четырех последовательностей синхроимпульсов с необходимыми частотами следования (фиг. 3) и формирования адреса выбора коэффициентов цифрового полосового фильтра 10, находящихся в блоке 11 постоянной памяти. Последовательности F и F, формируются из тактовой частоты генератора 3 с помощью делителя 20 частоты. Последовательность F начинает формироваться в момент, когда по импульсу F взводится триггер 22, и заканчивается, когда триггер 22 сбрасывается синхроимпульсом F«,. Последовательность же FЈ, наоборот, формируется при сброшенном положении триггера 22. Эта последовательность поступает на вход кольцевого счетчика и элемента 27 задержки.

Рассмотрим прохождение одного из импульсов этой последовательности

Поступающий на счгтный вход счетчикл 25 импульс увеличивает хранящийся в нем код на единицу. С выхода счетчик 25 числовой код поступает на адресные входы блока ПЗУ 26. Кроме того, импульс поступает на вход элемента 27 задержки, tj которого равна времени срабатывания счетчика 25, с выхода элемента 27 задержки импульс подается на тактовый вход считывания ПЗУ 26 синхронно с поступлением информации на адресные входы последнего. В управляющем слове, полученном на выходе ПЗУ 26, устанавливается адресный код для блока 11 постоянной памяти. С выхода элемента 27 задержки импульс поступает, кроме того на вход элемента 28 задержки, tjaA г которого равна времени срабатывания ПЗУ 26. С выхода элемента 28 задержки синхроимпульс поступает на пятый выход блока 4 синхронизации и по нему - к блокам 9, 11 и 16, где происходит скачок напряжения, передача новых коэффициентов и выбор новой частотной полосы соответственно.

Самым нестабильным блоком в известном анализаторе (прототипе) является аналоговый полосовой фильтр. Это объясняется нестабильностью составляющих его элементов (R, L, С), параметры которых зависят как от параметра окружающей среды (температуры, влажности и т.д.), так и от времени (старение). В настоящее время относительная нестабильность лучших элементов составляет не менее 2-10 . Путем больших аппаратурных затрат нестабильность, обусловленную влиянием внесшей среды, можно снизить до 2-10 однако нестабильность связанную со старением элементов, исключить нельзя. В предлагаемом же анализаторе нестабильность определя- ется в основном нестабильностью генератора 3 тактовой частоты, которая для современных кварцевых генераторов составляет 1СГ , т.е. обеспечивается на порядок более высокая точ- ность.

Кроме того, в прототипе вследствие непрерывного гетеродирования спектра частотный анализ возможен только в смежных частотных полосах. В предлагаемом же устройстве благодаря скачкообразному сканированию спектра цифровым полосовым фильтром возможен анализ как в смежных, так и в

5

5

« 0 5

0 о

5

перекрывавшихся и непгргкрыплмпихгя частотных полосах, что приводит к дополнительному повышению точности анализа.

Формула изобретения

Анализатор спектра, содержащий последовательно соединенные первый аналоговый фильтр нижних частот, анл- лого-цнфровой преобразователь, промежуточный запоминаний блок, последовательно соединенные генератор линейно нарастающего ступенчатого напряжения и генератор качающейся частоты, последовательно соединенные цнфроаналоговый преобразователь, второй аналоговый фильтр нижних частот, первый коммутатор, блок коррекции, полосовой фильтр, второй коммутатор и квадратор, а также генератор тактовой частоты и подключенный к нему блок синхронизации, первый, второй и третий выходы которого подключены к управляющим входам аналого-цифрового преобразователя, промежуточного запоминающего блока и первому управляющему входу генератора линейно нарастающего ступенчатого напряжения соответственно, второй вход и выход запоминающего блока с перезаписью соединены между собой, второй выход первого коммутатора подключен к входу полосового фильтра, второй выход второго коммутатора подсоединен к выходу квадратора, соединенного с выходом устройства, причем вход первого аналогового фильтра нижних частот

i соединен с входом анализатора, о т-

личаюптийся тем, что, с целью повышения точности, в него введены последовательно соединенные блок постоянной памяти и цифровой полосовой фильтр, информационным входом соединенный с вторым выходом запоминающего блока с перезаписью, и выходом - с входом цифроаналогового преобразователя, первый управляющий вход блока постоянной памяти подключен соответственно к четвертому выходу блока синхронизации, пятым выходом соединенного с управляющим входом полосового фильтра и вторыми управляющими входами генератора линейно нарастающего ступенчатого напряжения и блока постоянной памяти, выход генератора качающейся частоты подсоединен к третьему входу запоминающего блока с перезаписью.

Частота

Фаг.З

trrk ггп жтггг

.«

F N2-Ff

fjtfj

J мл

Частота

сг.г

Фиг. 5

Авторы

Даты

1990-05-30—Публикация

1988-02-25—Подача