Изобретение относится к технике связи и может использоваться при проектировании новых и модернизации существующих систем обмена данными с применением блоковых помехоустойчивых кодов.

Заявленное устройство расширяет арсенал применения двоичных избыточных блоковых кодов за счет исправления доли стираний, кратность которых выходит за пределы метрики Хемминга и может быть реализовано на базе использования известных свойств эквивалентных кодов.

Близким по технической сущности к заявленному устройству является способ мягкого декодирования систематических блоковых кодов, в основе которого лежит процедура ранжирования мягких решений символов (МРС) принятой кодовой комбинации, выделения из них наиболее надежных символов по показателям МРС, переход к эквивалентному коду с последующим вычислением вектора ошибок, действовавшего на принятый кодовый вектор в процессе передачи его по каналу связи (см. Р. Морелос-Сарагоса. Искусство помехоустойчивого кодирования. Методы, алгоритмы, применение. М., Техносфера, 2005, С. 213, …, 216).

Недостатком указанного способа является необходимость вычисления определителя и обратной матрицы для переставленной в соответствии с показателями МРС столбцов порождающей матрицы основного кода в процедуре вычисления порождающей матрицы эквивалентного кода.

Кроме того, известен способ мягкого декодирования блоковых кодов (см. патент RU 2580797), в котором процедура вычисления определителя матрицы эквивалентного кода заменяется анализом структуры определенных бит комбинаций выделенного кластера. Эти биты должны образовывать двоичное поле Галуа заданной степени расширения.

Недостатком способа является замена регулярного алгоритма вычисления определителя матрицы переставленного кода на выделение комбинаций поля Галуа и оценку их соответствия заданным степеням примитивного элемента, что не является простой и однозначной задачей.

Известен способ мягкого декодирования систематических кодов (см. патент RU 2444127), в котором с целью снижения вычислительных затрат в алгоритме поиска обратной матрицы, вычисление матрицы эквивалентного кода при приведении ее к систематическому виду используют прием кластеризации множества разрешенных кодовых векторов, что позволяет обрабатывать определители матриц размерности не (k×k), а размерности (k-ƒ)×(k-ƒ), где ƒ - число бит, отводимых на нумерацию (в двоичной

системе) формируемых в коде кластеров. Указанная процедура обеспечивает незначительное снижение вычислительных затрат поскольку в значительной степени зависит от выбранного параметра ƒ, где 1≤ƒ<k.

Все указанные способы обладают одним общим недостатком, который заключается в том, что ряд кодовых комбинаций в процессе обработки данных могут повторяться не только в текущем сеансе, но и по итогам предыдущих сеансов связи. Однако ни один из указанных способов не учитывает этого и не хранит в своей памяти образец матрицы эквивалентного кода комбинации когда-либо переданной в системе обмена данными.

Повторение вычислительного процесса в подобных ситуациях является фактором, снижающим производительность декодера, в то время как проблема с памятью в таких устройствах представляется давно и успешно решенной задачей.

Известно также устройство - декодер с упорядоченной статистикой символов (см. патент RU 2490804), в котором частично решается задача запоминания тех комбинаций номеров переставленных столбцов порождающей матрицы основного кода, определитель которых указывает на вырожденность переставленных матриц и невозможность реализовать декодирование с использованием эквивалентного кода. Следовательно, для невырожденных матриц процедура поиска переставленных порождающих матриц и приведение их к систематической форме для получения эквивалентного кода выполняется в декодере даже в том случае, если образец переставленного вектора уже обрабатывался декодером.

Известно также устройство - декодер с повышенной корректирующей способностью (см. патент RU 2438252), которое практически реализует способ, описанный в работе Р. Морелос-Сарагосы с незначительным уточнением процедуры получения МРС. В таком декодере, по сути, сохраняются все недостатки, характерные для решений по патентам 2444127, 2490804 и 2580797.

Близким по технической сущности к заявленному декодеру является устройство по патенту №2644507, в котором осуществляется поиск порождающих матриц эквивалентных кодов с запоминанием полученных решений и использованием этих решений в случаях повторения перестановок принятых кодовых векторов. Кроме того, при отсутствии оперативной работы декодер способен генерировать перестановки символов для вычисления параметров эквивалентных кодов.

Недостатком указанного устройства является необходимость выделения довольно значительного объема памяти декодера для хранения всех порождающих матриц эквивалентных кодов.

Технический результат при осуществлении предлагаемого изобретения заключается в повышении производительности декодера и значительном снижении требований к объему памяти декодера.

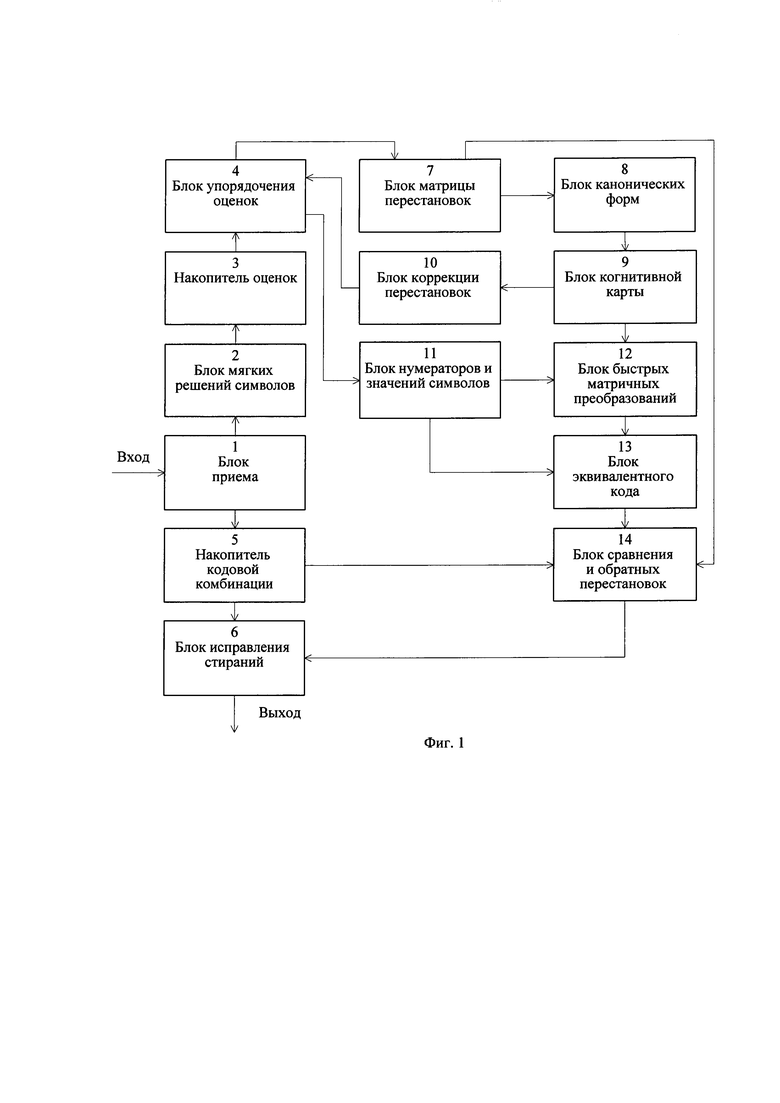

Технический результат достигается за счет того, что в предлагаемом перестановочном декодере с системой быстрых матричных преобразований, содержащем блок приема, первый выход которого через включенные последовательно блок мягких решений символов и накопитель оценок подключен к одному входу блока упорядочения оценок, при этом второй выход блока приема подключен к входу накопителя кодовой комбинации, первый выход которого подключен ко второму входу блока сравнения и обратных перестановок, тогда как первый вход этого блока подключен к выходу блока эквивалентного кода, а выход блока сравнения и обратных преобразований подключен ко второму входу блока исправления стираний, при этом первый вход данного блока подключен ко второму выходу накопителя кодовой комбинации, дополнительно введены блок матрицы перестановок, блок канонических форм, блок когнитивной карты, блок коррекции перестановок, блок нумераторов и значений символов, а также блок быстрых матричных преобразований, при этом второй выход блока матрицы перестановок через блок канонических форм подключен к входу блока когнитивной карты, первый выход которого через блок коррекции перестановок подключен к другому входу блока упорядочения оценок, первый выход которого соединен с входом блока матрицы перестановок, а первый выход этого блока подключен к третьему входу блока сравнения и обратных перестановок, при этом второй выход блока когнитивной карты подключен к одному входу блока быстрых матричных преобразований, выход которого подключен к первому входу блока эквивалентного кода, тогда как второй вход этого блока соединен со вторым выходом блока нумераторов и значений символов, а вход этого блока подключен ко второму выходу блока упорядочения оценок, при этом первый выход блока нумераторов и значений символов подключен к другому входу блока быстрых матричных преобразований.

Структурная схема перестановочного декодера с системой быстрых матричных преобразований представлена на фигуре 1, где:

1 - блок приема;

2 - блок мягких решений символов (МРС);

3 - накопитель оценок;

4 - блок упорядочения оценок;

5 - накопитель кодовой комбинации;

6 - блок исправления стираний;

7 - блок матрицы перестановок;

8 - блок канонических форм;

9 - блок когнитивной карты;

10 - блок коррекции перестановок;

11 - блок нумераторов и значений символов;

12 - блок быстрых матричных преобразований (БМП);

13 - блок эквивалентного кода;

14 - блок сравнения и обратных перестановок.

Перестановочный декодер с системой быстрых матричных преобразований содержит блок приема 1, первый выход которого через последовательно включенные блок мягких решений символов 2 и накопитель оценок 3 подключен к одному входу блока упорядочения оценок 4, при этом первый выход блока упорядочения оценок 4 соединен с входом блока матрицы перестановок 7, второй выход которого через блок канонических форм 8 подключен к входу блока когнитивной карты 9, тогда как первый выход блока когнитивной карты 9 через блок коррекции перестановок 10 соединен с другим входом блока упорядочения оценок 4, второй выход которого подключен к входу блока нумераторов и значений символов 11, тогда как первый выход блока нумераторов и значений символов 11 соединен с другим входом блока быстрых матричных преобразований 12, при этом один вход блока быстрых матричных преобразований 12 подключен ко второму выходу блока когнитивной карты 9, а выход блока быстрых матричных преобразований 12 соединен с первым входом блока эквивалентного кода 13, второй вход которого подключен ко второму выходу блока нумераторов и значений символов 11, тогда как выход блока эквивалентного кода 13 соединен с первым входом блока сравнения и обратных перестановок 14, при этом к третьему входу блока сравнения и обратных перестановок 14 подключен первый выход блока матрицы перестановок 7, а ко второму входу блока сравнения и обратных перестановок 14 подключен первый выход накопителя кодовой комбинации 5, вход которого соединен со вторым выходом блока приема 1, при этом второй выход накопителя кодовой комбинации 5 подключен к первому входу блока исправления стираний 6, второй вход которого соединен с выходом блока сравнения и обратных перестановок 14.

Работу перестановочного декодера с системой быстрых матричных преобразований рассмотрим на примере кода Хэмминга (7, 4, 3) с порождающей матрицей G вида:

При этом алгоритм работы декодера справедлив для любого систематического двоичного блокового кода.

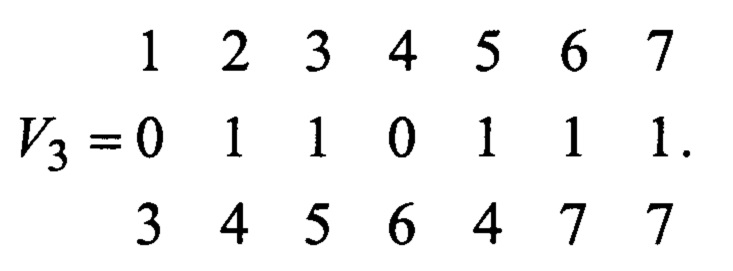

Пусть источник информации передает информационный вектор Vинф = 1010, тогда в канал связи передатчик отправит вектор Vкан = Vинф × G = 1010011. Пусть вектор ошибок Ve имеет вид Ve = 110010С. В блоке приема 1 происходит фиксация вектора приема Vпр, который поступает в блок МРС 2 и накопитель кодовой комбинации 5. В блоке МРС 2 вырабатываются мягкие решения для каждого бита этого вектора. Далее в накопителе оценок 3 фиксируется последовательность целочисленных МРС V3 вида:

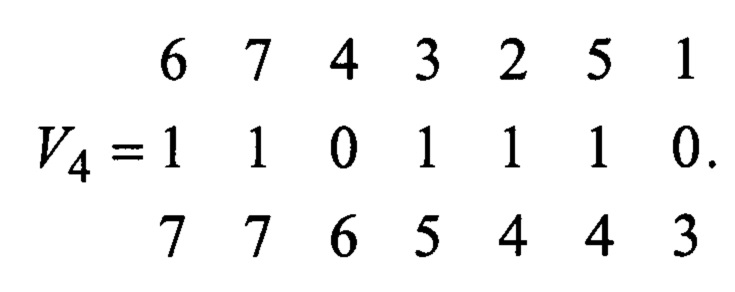

В блоке упорядочения оценок 4 последовательность V3 принимает вид V4:

Упорядоченные нумераторы символов из последовательности V4 передаются одновременно в блок матриц перестановок 7 и в блок нумераторов и значений символов 11, при этом в блок 11 вместе с нумераторами передаются значения их двоичных символов. В результате в блоке 7 формируется последовательность V7 = 6 7 4 3 2 5 1и матрица перестановок Р7, которая передается в блок сравнения и обратных перестановок 14. Матрица P7 в соответствии с упорядочением оценок V7 принимает вид:

Одновременно с этим, последовательность V7 поступает в блок канонических форм 8, где группа нумераторов, относящихся к первым четырем разрядам (6743) приводится к строго возрастающей последовательности (3467), что является канонической формой нумераторов V8 = 3 4 6 7 для данного примера.

Последовательность V8 направляется в блок когнитивной карты 9, которая имеет структуру, показанную в таблице 1.

В этой карте каждая клетка содержит две строки. В первой строке указывается каноническая нумерация информационных разрядов и соответствующий ей номер проверочной матрицы. Вид этих матриц представлен ниже, и их содержание имеется в памяти блока 9.

Нижняя строка каждой клетки указывает на нумерацию строк (первые четыре цифры) и нумерацию столбцов (группа из трех цифр).

В нижней части таблицы указаны сочетания нумераторов, которые не обеспечивают получение эквивалентного кода. Подобная ситуация будет описана отдельно.

Таким образом, блок когнитивной карты 9, получив последовательность V8 = 3 4 6 7 отыскивает в когнитивной карте аналогичную последовательность нумераторов, которая указывает, что данной перестановке соответствует проверочная матрица Н3. Структура этой матрицы направляется в блок БМП 12 и сопровождается нумерацией строк и столбцов из нижней строки. Матрица H3 имеет вид:

В блоке БМП 12 на основании данных блока нумераторов и значений символов 11 осуществляется перестановка строк и столбцов матрицы H3, как показано ниже:

Последовательность H12 направляется в блок эквивалентного кода 13, где формируется вектор эквивалентного кода, соответствующий заданной перестановке надежных символов. Для этого из блока нумераторов и значений символов 11 извлекаются первые k символов последовательности V4, то есть (1101), которые будут представлять информационные разряды эквивалентного кода. Для получения проверочных разрядов необходимо последовательность из k бит умножить на последовательность H12.

Таким образом, вектор эквивалентного кода в блоке 13 принимает вид V13 = l 1 0 1 0 0 1. Этот вектор передается в блок сравнения и обратных перестановок 14, где умножается на матрицу  , которая является транспонированной матрицей перестановок P7 из блока 7. Тогда вектор принимает вид

, которая является транспонированной матрицей перестановок P7 из блока 7. Тогда вектор принимает вид

Сравнивая V14 с Vпр, который поступает из накопителя кодовой комбинации 5 получаем вектор ошибок Ve. Это сравнение осуществляется в блоке 14, при этом Vпр в битовом представлении хранится в накопителе кодовой комбинации 5.

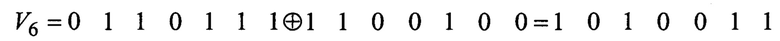

Полученный в блоке сравнения и обратных перестановок 14 Ve поступает в блок исправления стираний 6. В блоке исправления стираний 6 осуществляется исправление ошибочных символов путем сложения по модулю 2 битового представления Vпр из накопителя кодовой комбинации 5 и Ve из блока сравнения и обратных перестановок 14:

Таким образом, V6=Vкан ошибки, возникшие в канале связи, были исправлены.

Недостатком перестановочного декодирования двоичных кодов является относительно высокая вероятность появления таких перестановок символов кодовых комбинаций, которые приводят к линейной зависимости проверочных соотношений. Это означает, что эквивалентный код при таких перестановках получить нельзя. Для сохранения возможности восстановления указанной доли комбинаций в декодер введен блок коррекции перестановок 10. Если в блоке когнитивной карты 9 возникает ситуация, когда нумераторы перестановок в канонической форме конфигурируются в формате, представленном в нижней строке когнитивной карты (см. таблицу 1), то блок 10 обеспечивает коррекцию перестановки за счет замены нумератора на позиции k на нумератор с номером k+1. Этот шаг алгоритма работы декодера немедленно требует коррекции последовательности V4 в блоке упорядочения оценок 4 с последующей коррекцией матрицы перестановок в блоке 7. В последующем работа декодера не отличается от его работы по основному алгоритму, описанному выше.

Например, если перестановка в канонической форме приняла вид (1367), то по команде из блока когнитивной карты 9 в блоке коррекции перестановок 10 эта перестановка переводится в любую (в зависимости от нумератора на позиции k+1) из перестановок 1362; 1364 или 1365. Далее разрешенная перестановка поступает в блок упорядочения оценок 4, где в соответствии с ней формируется новая последовательность V4. Дальнейшая обработка данных в блоках 7, 8, 9, 11, 12, 13, 14, 5, 6 проводится согласно описанию, приведенному выше.

Таким образом, для кода Хэмминга (7, 4, 3) вместо 5040 порождающих матриц эквивалентного кода когнитивная карта содержит всего четыре типа формирующих матриц Н, которые за счет элементарных перестановок обращаются в полное множество требуемых для данного кода последовательностей, обеспечивающих получение эквивалентных кодов.

Сравнительные характеристики требуемых объемов памяти когнитивной карты декодера для различных двоичных блоковых кодов приведены в таблице 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор комбинаций двоичного эквивалентного кода | 2019 |

|

RU2743854C1 |

| Перестановочный декодер с альтернативными решениями | 2024 |

|

RU2826701C1 |

| Способ перестановочного декодирования блоковых кодов на базе упорядоченной когнитивной карты | 2018 |

|

RU2697732C1 |

| ПЕРЕСТАНОВОЧНЫЙ ДЕКОДЕР С ПАМЯТЬЮ | 2017 |

|

RU2672300C2 |

| ПЕРЕСТАНОВОЧНЫЙ ДЕКОДЕР С ОБРАТНОЙ СВЯЗЬЮ | 2018 |

|

RU2704722C2 |

| Перестановочный декодер с режимом обучения | 2017 |

|

RU2644507C1 |

| ДЕКОДЕР С УПОРЯДОЧЕННОЙ СТАТИСТИКОЙ СИМВОЛОВ | 2012 |

|

RU2490804C1 |

| СПОСОБ МЯГКОГО КОГНИТИВНОГО ДЕКОДИРОВАНИЯ СИСТЕМАТИЧЕСКИХ БЛОКОВЫХ КОДОВ | 2016 |

|

RU2646372C1 |

| ДЕКОДЕР С ПОВЫШЕННОЙ КОРРЕКТИРУЮЩЕЙ СПОСОБНОСТЬЮ | 2010 |

|

RU2438252C1 |

| ДЕКОДЕР С ОБРАБОТКОЙ СПИСКА БАЗОВОГО КЛАСТЕРА | 2015 |

|

RU2605365C1 |

Изобретение относится к области техники связи и может использоваться при проектировании новых и модернизации существующих систем обмена данными с применением блоковых помехоустойчивых кодов. Техническим результатом является повышение производительности декодера и значительное снижение требований к объему памяти декодера. Технический результат заявляемого технического решения достигается тем, что в перестановочный декодер введены блок матрицы перестановок, блок канонических форм, блок когнитивной карты, блок коррекции перестановок, блок нумераторов и значений символов, а также блок быстрых матричных преобразований. 1 ил., 2 табл.

Перестановочный декодер с системой быстрых матричных преобразований, содержащий блок приема, первый выход которого через включенные последовательно блок мягких решений символов и накопитель оценок подключен к одному входу блока упорядочения оценок, при этом второй выход блока приема подключен к входу накопителя кодовой комбинации, первый выход которого подключен ко второму входу блока сравнения и обратных перестановок, тогда как первый вход этого блока подключен к выходу блока эквивалентного кода, а выход блока сравнения и обратных преобразований подключен ко второму входу блока исправления стираний, при этом первый вход данного блока подключен ко второму выходу накопителя кодовой комбинации, отличающийся тем, что дополнительно введены блок матрицы перестановок, блок канонических форм, блок когнитивной карты, блок коррекции перестановок, блок нумераторов и значений символов, а также блок быстрых матричных преобразований, при этом второй выход блока матрицы перестановок через блок канонических форм подключен к входу блока когнитивной карты, первый выход которого через блок коррекции перестановок подключен к другому входу блока упорядочения оценок, первый выход которого соединен с входом блока матрицы перестановок, а первый выход этого блока подключен к третьему входу блока сравнения и обратных перестановок, при этом второй выход блока когнитивной карты подключен к одному входу блока быстрых матричных преобразований, выход которого подключен к первому входу блока эквивалентного кода, тогда как второй вход этого блока соединен со вторым выходом блока нумераторов и значений символов, а вход этого блока подключен ко второму выходу блока упорядочения оценок, при этом первый выход блока нумераторов и значений символов подключен к другому входу блока быстрых матричных преобразований.

| Перестановочный декодер с режимом обучения | 2017 |

|

RU2644507C1 |

| RU 2018101641 A, 16.07.2019 | |||

| DILIP V.S.: "High-speed Architectures for ReedSolomon decoders", IEEE Trans | |||

| VLSI systems, 2001 | |||

| vol | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Уровень с пузырьком | 1922 |

|

SU388A1 |

| ШАМИН А.А | |||

| "Повышение энергетической эффективности элементов сенсорных сетей методом перестановочного декодирования", Вестник НГИЭИ, 10 (77), 2017, стр.24-34 | |||

| ПЧЕЛИН Н.А | |||

Авторы

Даты

2020-03-31—Публикация

2019-09-30—Подача