Заявленное устройство относится к электросвязи, а именно к цифровой радиосвязи, и может быть использовано в помехоустойчивых системах передачи информации посредством структурно-скрытых сигналов с двухпозиционной манипуляцией.

Известна система передачи четверично-кодированных последовательностей с улучшенным значением помехоустойчивости по патенту РФ №2188516 от 27.08.2005, состоящая из генератора тактовых импульсов, формирователя D-кодов, формирователя сигналов двукратной частотной манипуляции, селектора сигналов, блока выделения дополнительных последовательностей, двухканального согласованного фильтра, вычитателя и решающего блока.

Недостатком аналога является низкая скрытность структуры формируемого сигнала, и как следствие, к низкому значению помехоустойчивости при воздействии имитационных помех.

Известна система передачи четверично-кодированных радиосигналов с улучшенным значением помехоустойчивости (патент РФ №2258313 от 10.08.2005), состоящая из генератора тактовых импульсов, двух формирователей D-кодов, двух формирователей сигналов двукратной частотной манипуляции, сумматора, модулятора, двух синтезаторов частот, двух генераторов псевдослучайных чисел, демодулятора, селектора сигналов, генератора тактовых импульсов, блока выделения дополнительных последовательностей, блока свертки дополнительных последовательностей, решающего блока.

Недостатком аналога является низкая скрытность структуры формируемого сигнала, что определяет снижение помехоустойчивости при воздействии имитационных помех.

Наиболее близким по технической сущности к заявленному устройству является устройство формирования сигнала с четырехпозиционной манипуляцией (патент РФ №2631149 от 19.09.2017). Данное устройство выбрано в качестве прототипа. Устройство состоит из источника сообщений (1), скремблера (2), дешифратора (3), первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот, первого (8), второго (9), третьего (10), четвертого (11), пятого (12), шестого (13), седьмого (14), восьмого (15) управляемых ключей, первого (16), второго (17), третьего (18), четвертого (19) сумматоров, первого (20), второго (21), третьего (22), четвертого (23) генераторов псевдослучайной последовательности, регистра сдвига (24), схемы «И» (25).

Данное устройство осуществляет формирование четырехпозиционного сигнала методом расширения его спектра за счет применения частотно-временных матриц (ЧВМ) и режима медленной программной перестройки рабочих частот. При этом заполнение ЧВМ осуществляется кодированием элементами информационной битовой последовательности номиналов рабочих частот на временном интервале случайной длительности.

Первый сумматор (16) выполнен четырехвходовым, вход скремблера (2) подключен к выходу источника сообщений (1), а выход подключен к входу дешифратора (3), первый (3.1), второй (3.2), третий (3.3), четвертый (3.4) сигнальные выходы которого подключены к управляющим входам (8.2) первого (8), (9.2) второго (9), (10.2) третьего (10), (11.2) четвертого (11) управляемых ключей соответственно, а к высокочастотным входам (8.1) первого (8), (9.1) второго (9), (10.1) третьего (10), (11.1) четвертого (11) управляемых ключей подключены соответствующие выходы первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот, первый (16.1), второй (16.2), третий (16.3) и четвертый (16.4) входы первого сумматора (16) подключены соответственно к выходам первого (8), второго (9), третьего (10), четвертого (11) управляемых ключей, а выход (16.5) первого сумматора (16) является выходом устройства, выход первого генератора ПСП (20) подключен к входу регистра сдвига (24), к первому входу (12.1) пятого управляемого ключа (12) и к второму входу (17.2) второго сумматора (17), к первому входу (17.1) которого подключен выход второго генератора ПСП (21), а выход второго сумматора (17) подключен к первому входу (13.1) шестого управляемого ключа (13) и к второму входу (18.2) третьего сумматора (18), к первому входу (18.1) которого подключен выход третьего генератора ПСП (22), а выход третьего сумматора (18) подключен к первому входу (14.1) седьмого управляемого ключа (14) и к второму входу (19.2) четвертого сумматора (19), к первому входу (19.1) которого подключен выход четвертого генератора ПСП (23), а выход четвертого сумматора (19) подключен к первому входу (15.1) восьмого управляемого ключа (15), выходы (24.1) и (24.2) регистра сдвига (24) подключены к первому и второму входам схемы «И» (25) соответственно, выход которой подключен к вторым входам (12.2) пятого (12), (13.2) шестого (13), (14.2) седьмого (14), (15.2) восьмого (15) управляемых ключей, выходы которых подключены к входам первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот соответственно. Первый сумматор (16) содержит четыре входа (16.1), (16.2), (16.3), (16.4), к которым подключены соответственно выходы первого (8), второго (9), третьего (10), четвертого (11) управляемых ключей, а выход (16.5) первого сумматора (16) является выходом устройства.

Недостатком прототипа является низкая скрытность структуры формируемого сигнала, что приводит к низкому значению помехоустойчивости при воздействии имитационных помех.

Целью изобретения является разработка устройства формирования сигналов двухпозиционной манипуляции с повышенным значением структурной скрытности и помехоустойчивости в условиях воздействия имитационных помех.

Техническим результатом заявляемого устройства является повышение помехоустойчивости формируемого сигнала на основе его структурной скрытности при воздействии имитационных помех.

Заявляемый технический результат достигается тем, что в известное устройство, которое содержит источник сообщений (1), выход которого подключен к входу скремблера (2), первый (4), второй (5), третий (6), четвертый (7) синтезаторы частот, выходы которых подключены к высокочастотным входам (8.2) первого (8), (9.2) второго (9), (10.2) третьего (10), (11.2) четвертого (11) управляемых ключей соответственно, сигнальные выходы которых подключены к входам (16.1), (16.2), (16.3), (16.4) первого сумматора (16) соответственно, а выход (16.5) первого сумматора (16) является выходом устройства, второй сумматор (17), выход которого подключен к первому входу (13.1) шестого управляемого ключа (13) и к второму входу (18.2) третьего сумматора (18), к первому входу (18.1) которого подключен выход третьего генератора ПСП (22), а выход третьего сумматора (18) подключен к первому входу (14.1) седьмого управляемого ключа (14) и к второму входу (19.2) четвертого сумматора (19), к первому входу (19.1) которого подключен выход четвертого генератора ПСП (23), первый генератор ПСП (20), выход которого подключен к входу регистра сдвига (24), к первому входу (12.1) пятого управляемого ключа (12) и к второму входу (17.2) второго сумматора (17), к первому входу (17.1) которого подключен выход второго генератора ПСП (21), четвертый сумматор (19), выход которого подключен к первому входу (15.1) восьмого управляемого ключа (15), регистр сдвига (24), выходы (24.1) и (24.2) которого подключены к первому и второму входам схемы «И» (25) соответственно, выход которой подключен к вторым входам (12.2) пятого (12), (13.2) шестого (13), (14.2) седьмого (14), (15.2) восьмого (15) управляемых ключей, выходы которых подключены к входам первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот соответственно, отличается тем, что дополнительно введены первая (27), вторая (28), третья (29), четвертая (30) схемы «ИЛИ», первые управляющие входы (27.1) первой (27), (28.1) второй (28), (29.1) третьей (29), (30.1) четвертой (30) схем «ИЛИ» подключены к выходу скремблера (2), блок датчиков случайных чисел (3), выходы (3.1.1), (3.2.1), (3.3.1), (3.4.1) которого подключены к вторым управляющим входам (27.2) первой (27), (28.2) второй (28), (29.2) третьей (29), (30.2) четвертой (30) схем «ИЛИ» соответственно и к управляющим входам (26.1), (26.2), (26.3), (26.4) блока управляемых аттенюаторов (26), к высокочастотным входам (26.5), (26.6), (26.7), (26.8) которого подключены соответствующие выходы первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот, выходы блока управляемых аттенюаторов (26) подключены к высокочастотным входам (8.2) первого (8), (9.2) второго (9), (10.2) третьего (10), (11.2) четвертого (11) управляемых ключей соответственно.

Блок датчиков случайных чисел (3) состоит из первого (3.1), второго (3.2), третьего (3.3), четвертого (3.4) идентичных датчиков случайных чисел, выходы которых являются выходами блока и подключены соответственно к вторым управляющим входам (27.2) первой, (28.2) второй, (29.2) третьей, (30.2) четвертой схем «ИЛИ» соответственно и к управляющим входам (26.1), (26.2), (26.3), (26.4) блока управляемых аттенюаторов (26).

Блок управляемых аттенюаторов (26) состоит из первой (26.1), второй (26.2), третьей (26.3), четвертой (26.4) идентичных схем аттенюаторов, первая схема аттенюатора (26.1) содержит девятый (31), десятый (32), одиннадцатый (33), двенадцатый (34) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, вторая схема аттенюатора (26.2) содержит тринадцатый (35), четырнадцатый (36), пятнадцатый (37), шестнадцатый (38) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, третья схема аттенюатора (26.3) содержит семнадцатый (39), восемнадцатый (40), девятнадцатый (41), двадцатый (42) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, четвертая схема аттенюатора (26.4) содержит двадцать первый (43), двадцать второй (44), двадцать третий (45), двадцать четвертый (46) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, управляемые входы девятого (31), тринадцатого (35), семнадцатого (39), двадцать первого (43) управляемых ключей подключены к входу (26.1) блока управляемых аттенюаторов (26), а высокочастотные входы девятого (31), тринадцатого (35), семнадцатого (39), двадцать первого (43) управляемых ключей подключены к высокочастотному выходу первого (4) синтезатора частот, а выходы девятого (31), тринадцатого (35), семнадцатого (39), двадцать первого (43) управляемых ключей подключены к резистивному сопротивлению R2, управляемые входы десятого (32), четырнадцатого (36), восемнадцатый (40), двадцать второй (44) управляемых ключей подключены к входу (26.2) блока управляемых аттенюаторов (26), а высокочастотные входы десятого (32), четырнадцатого (36), восемнадцатый (40), двадцать второй (44) управляемых ключей подключены к высокочастотному выходу второго (5) синтезатора частот, выходы десятого (32), четырнадцатого (36), восемнадцатый (40), двадцать второй (44) управляемых ключей подключены к резистивному сопротивлению R3, управляемые входы одиннадцатого (33), пятнадцатого (37), девятнадцатого (41), двадцать третьего (45) управляемых ключей подключены к входу (26.3) блока управляемых аттенюаторов (26), а высокочастотные входы одиннадцатого (33), пятнадцатого (37), девятнадцатого (41), двадцать третьего (45) управляемых ключей подключены к высокочастотному выходу третьего (6) синтезатора частот, выходы одиннадцатого (33), пятнадцатого (37), девятнадцатого (41), двадцать третьего (45) управляемых ключей подключены к резистивному сопротивлению R4, управляемые входы двенадцатого (34), шестнадцатого (38), двадцатого (42), двадцать четвертого (46) управляемых ключей подключены к входу (26.4) блока управляемых аттенюаторов (26), а высокочастотные входы двенадцатого (34), шестнадцатого (38), двадцатого (42), двадцать четвертого (46) управляемых ключей подключены к высокочастотному выходу четвертого (7) синтезатора частот, выходы двенадцатого (34), шестнадцатого (38), двадцатого (42), двадцать четвертого (46) управляемых ключей подключены к резистивному сопротивлению R5, вход резистивного сопротивления R1 в первой (26.1), второй (26.2), третьей (26.3), четвертой (26.4) схем аттенюаторов подключен к высокочастотному выходу первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот соответственно, а выход резистивного сопротивления R1 является соответствующим выходом блока управляемых аттенюаторов (26).

Благодаря новой совокупности существенных признаков производится формирование двухпозиционного сигнала с повышенными свойствами структурной скрытности, при этом информационным символам «0» и «1» соответствуют разное количество несущих колебаний и их уровней амплитуд. При таком способе формирования сигнала в радиоканале в фиксированный момент времени передается совокупность рабочих частот, выбранных в соответствии с псевдослучайной комбинацией логических «0» и «1» датчиков случайных чисел, причем уровень амплитуд рабочих частот также формируется случайным образом. Таким образом, существенно повышается структурная скрытность формируемого устройством сигнала.

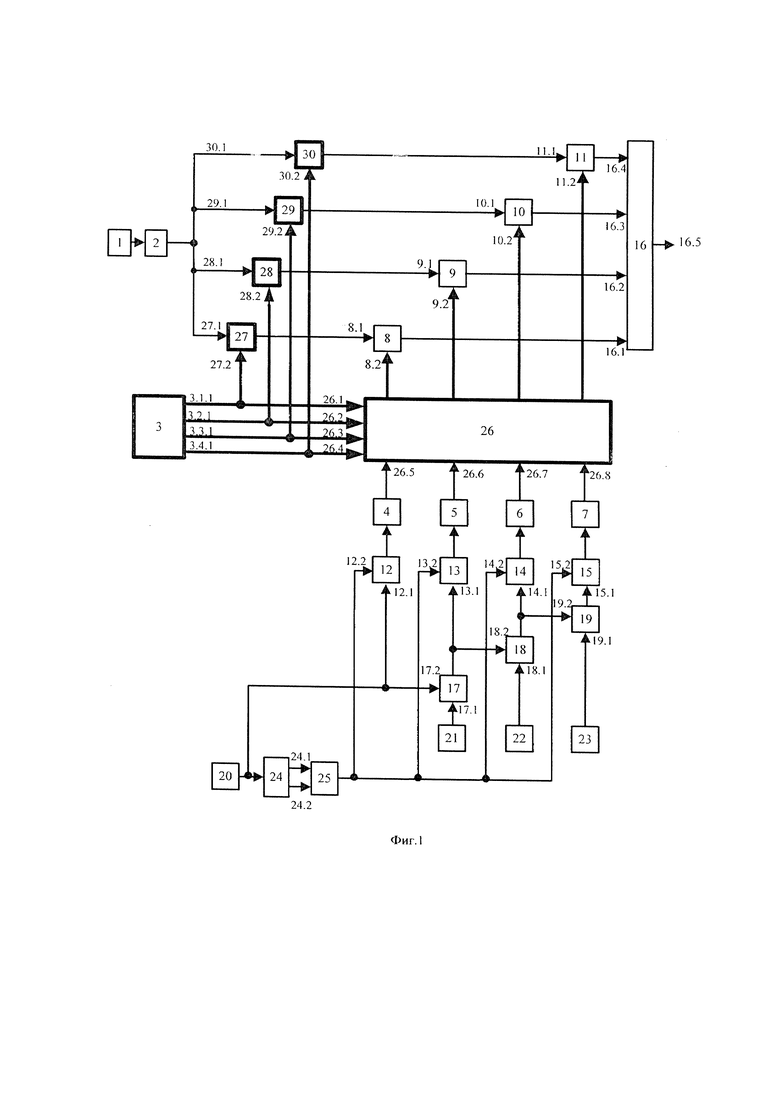

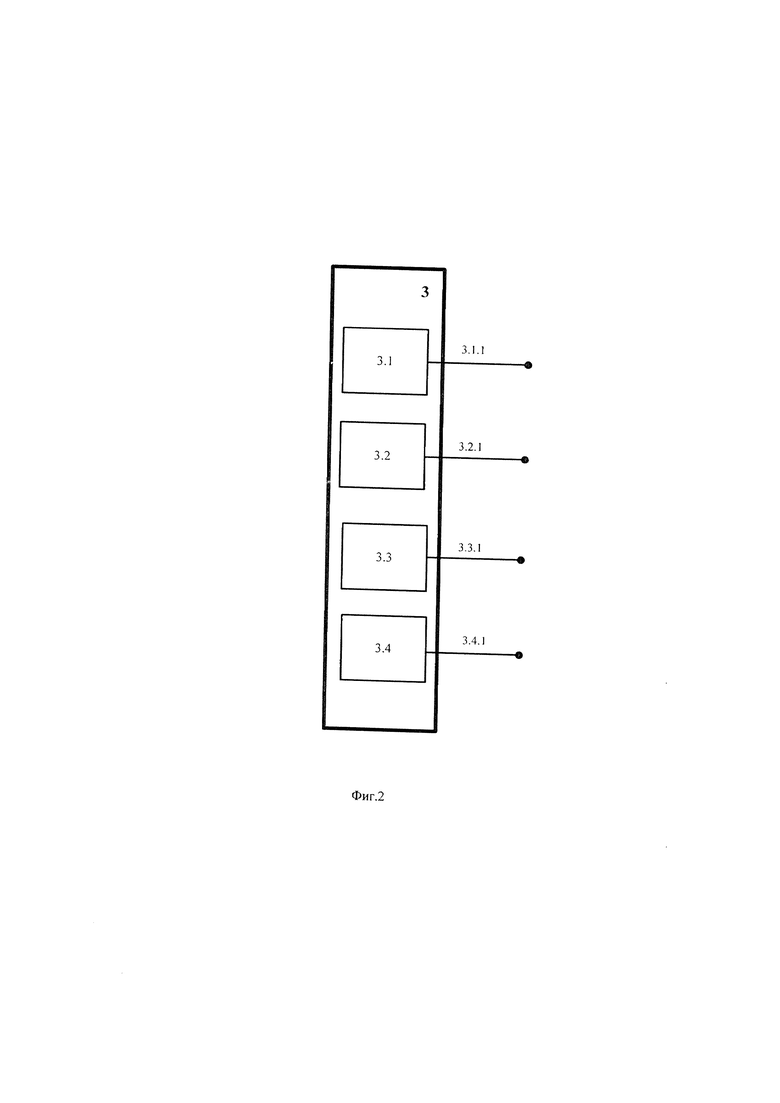

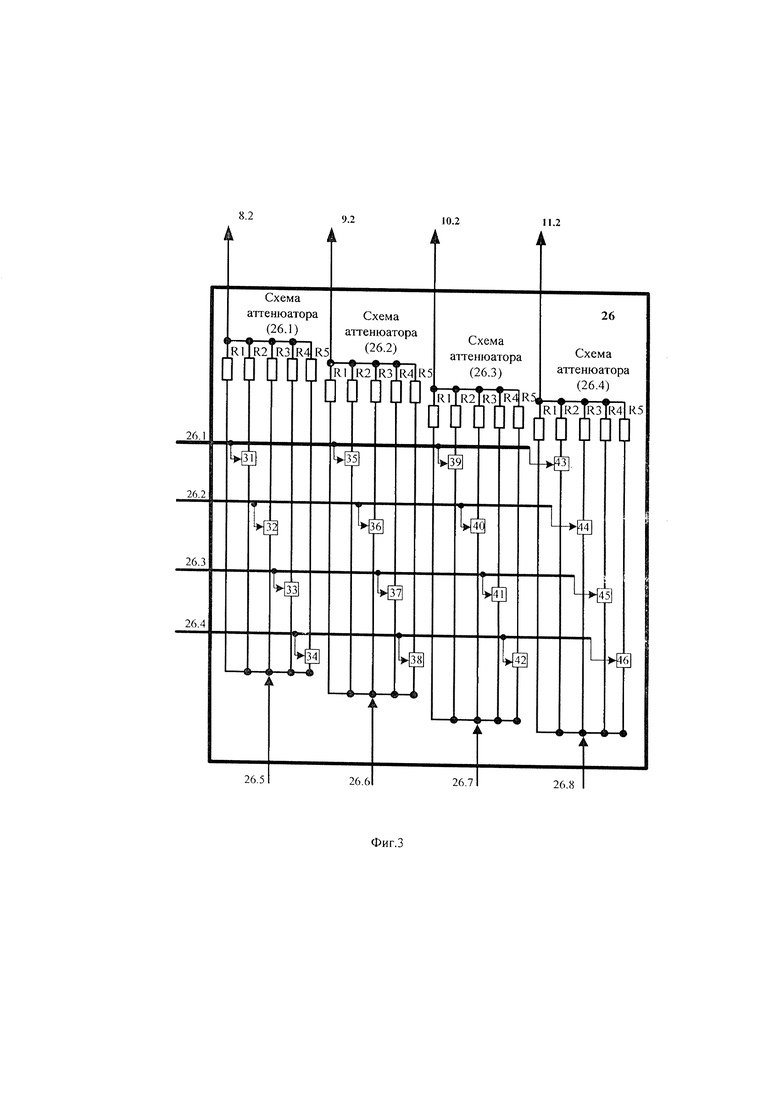

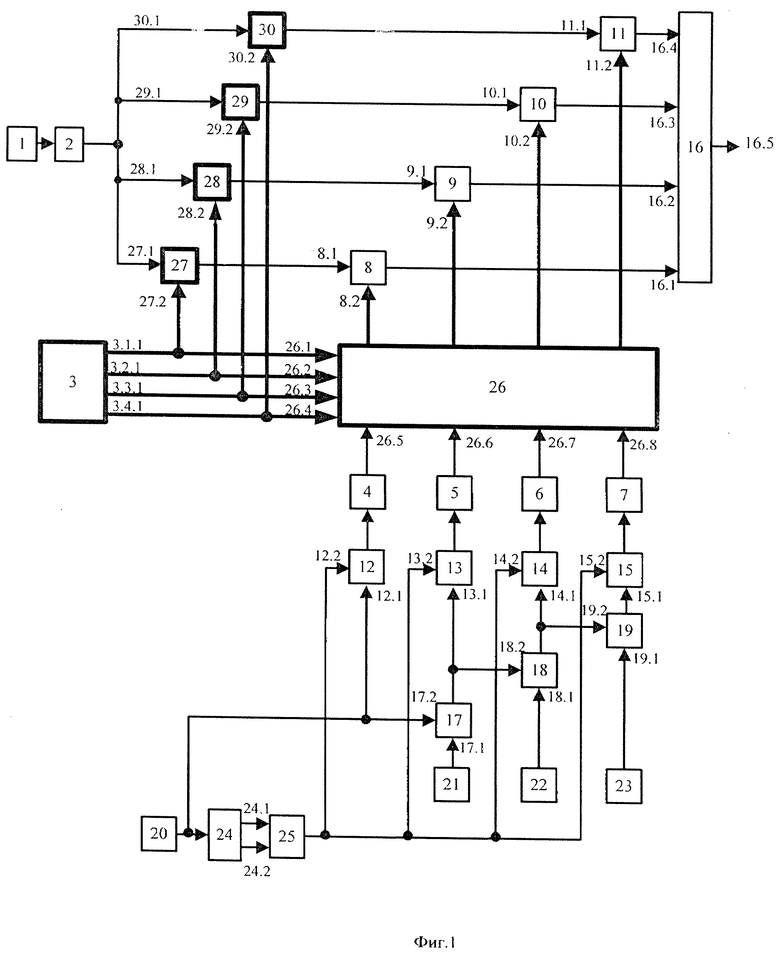

Заявляемое устройство поясняется чертежами, на которых показаны:

фиг. 1 - структурная схема устройства формирования структурно-скрытых сигналов с двухпозиционной манипуляцией;

фиг. 2 - структурная схема датчика случайных чисел;

фиг. 3 - структурная схема блока управляемых аттенюаторов.

Заявленное устройство, показанное на фиг. 1, состоит из источника сообщений (1), скремблера (2), блока датчиков случайных чисел (3), первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот, первого (8), второго (9), третьего (10), четвертого (11), пятого (12), шестого (13), седьмого (14), восьмого (15) управляемых ключей, первого (16), второго (17), третьего (18), четвертого (19) сумматоров, первого (20), второго (21), третьего (22), четвертого (23) генераторов псевдослучайной последовательности (ПСП), регистра сдвига (24), схемы «И» (25), блока управляемых аттенюаторов (26), первой (27), второй (28), третьей (29), четвертой (30) схем «ИЛИ».

Структурная схема блока датчиков случайных чисел (3) показана на фиг. 2, состоящего из состоит из первого (3.1), второго (3.2), третьего (3.3), четвертого (3.4) идентичных датчиков случайных чисел, выходы которых являются выходами блока.

Структурная схема блока управляемых аттенюаторов (26) показана на фиг. 3, состоящего из первой (26.1), второй (26.2), третьей (26.3), четвертой (26.4) схем управляемых аттенюаторов каждая из которых содержит резистивные сопротивления R1, R2, R3, R4, R5 и девятый (31), десятый (32), одиннадцатый (33), двенадцатый (34) управляемые ключи в первой (26.1) схеме аттенюатора, тринадцатый (35), четырнадцатый (36), пятнадцатый (37), шестнадцатый (38) управляемые ключи во второй (26.2) схеме аттенюатора, семнадцатый (39), восемнадцатый (40), девятнадцатый (41), двадцатый (42) управляемые ключи в третьей (26.3) схеме аттенюатора, двадцать первый (43), двадцать второй (44), двадцать третий (45), двадцать четвертый (46) управляемые ключи в четвертой (26.4) схеме аттенюатора.

Выход источника сообщений (1) подключен к входу скремблера (2), выход которого подключен к первым управляющим входам (27.1) первой (27), (28.1) второй (28), (29.1) третьей (29), (30.1) четвертой (30) схем «ИЛИ», к вторым управляющим входам (27.2) первой (27), (28.2) второй (28), (29.2) третьей (29), (30.2) четвертой (30) схем «ИЛИ» подключены соответствующие выходы (3.1.1) первого (3.1), (3.2.1) второго (3.2), (3.3.1) третьего (3.3), (3.4.1) четвертого (3.4) датчиков случайных чисел блока датчиков случайных чисел (3), которые также подключены к управляющим входам (26.1), (26.2), (26.3), (26.4) блока управляемых аттенюаторов (26), сигнальные выходы первой (27), второй (28), третьей (29), четвертой (30) схем «ИЛИ» подключены к управляющим входам (8.1) первого (8), (9.1) второго (9), (10.2) третьего (10), (11.1) четвертого (11) управляемых ключей соответственно, а к высокочастотным входам (8.2) первого, (9.2) второго, (10.2) третьего, (11.2) четвертого управляемых ключей (8-11) соответственно подключены соответствующие выходы блока управляемых аттенюаторов (26), к высокочастотным входам (26.5), (26.6), (26.7), (26.8) которого подключены соответствующие выходы первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот.

Первый сумматор (16) содержит четыре входа (16.1), (16.2), (16.3), (16.4), к которым подключены соответственно выходы первого (8), второго (9), третьего (10), четвертого (11) управляемых ключей, а выход (16.5) первого сумматора (16) является выходом устройства. Выход первого генератора ПСП (20) подключен к входу регистра сдвига (24), к первому входу (12.1) пятого управляемого ключа (12) и к второму входу (17.2) второго сумматора (17), к первому входу (17.1) которого подключен выход второго генератора ПСП (21).

Выход второго сумматора (17) подключен к первому входу (13.1) шестого управляемого ключа (13) и к второму входу (18.2) третьего сумматора (18), к первому входу (18.1) которого подключен выход третьего генератора ПСП (22), а выход третьего сумматора (18) подключен к первому входу (14.1) седьмого управляемого ключа (14) и к второму входу (19.2) четвертого сумматора (19), к первому входу (19.1) которого подключен выход четвертого генератора ПСП (23).

Выход четвертого сумматора (19) подключен к первому входу (15.1) восьмого управляемого ключа (15), выходы (24.1) и (24.2) регистра сдвига (24) подключены к первому и второму входам схемы «И» (25) соответственно, выход которой подключен к вторым входам (12.2) пятого (12), (13.2) шестого (13), (14.2) седьмого (14), (15.2) восьмого (15) управляемых ключей, выходы которых подключены к входам первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот соответственно.

Скремблер (2) предназначен для перемежения битов импульсной битовой последовательности (ИБП) от источника сообщений (1). Схема скремблера известна и может быть реализована, например, на интегральной микросхеме FX118DW.

Блок датчиков случайных чисел (3) предназначен для формирования каждым из четырех датчиков случайных чисел равновероятных логических «0» и «1». Схема датчика случайных чисел известна и приведена, например, в [Патент РФ №2103725 от 27.01.1998 г. Датчик случайных чисел с равномерным распределением. Ермаков В.Ф., Гудзовская В.А.].

Первый (4), второй (5), третий (6), четвертый (7) синтезаторы частот предназначены для формирования колебаний рабочих частот в зависимости от кода псевдослучайной последовательности. Техническая реализация синтезатора частот известна и представлена, например, в [Системы с прыгающей частотой / В кн.: Кларк Дж., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. - М.: Радио и связь, 1987. - С. 352-356].

Блок управляемых аттенюаторов (26) предназначен для формирования уровней колебаний рабочих частот каждой из идентичных схем аттенюатора, входящих в блок, в зависимости от комбинации, поступаемых на их вход равновероятных и независимых двоичных «0» и «1» блока датчиков случайных чисел (3) посредством подключения к резистивному сопротивлению R1 через управляемые датчиками случайных чисел ключи (31-46) параллельно-соединенных резистивных сопротивлений R2, R3, R4, R5 схем аттенюатора соответственно.

Первый (8), второй (9), третий (10), четвертый (11), пятый (12), шестой (13), седьмой (14), восьмой (15), девятый (31), десятый (32), одиннадцатый (33), двенадцатый (34), тринадцатый (35), четырнадцатый (36), пятнадцатый (37), шестнадцатый (38), семнадцатый (39), восемнадцатый (40), девятнадцатый (41), двадцатый (42), двадцать первый (43), двадцать второй (44), двадцать третий (45), двадцать четвертый (46) управляемые ключи предназначены для коммутации выходов блоков, подключенных к их сигнальным (первым) входам в зависимости от уровня напряжения на управляющих (вторых) входах. Реализация управляемых ключей известна и приведена, например, в патенте РФ №2037265 09.06.1995.

Первый (16), второй (17), третий (18), четвертый (19) сумматоры предназначены для объединения сигналов на их входах. Вариант реализации сумматоров известны и приведены, например, в [Схемотехника. 500 устройств на аналоговых микросхемах / М.А. Шустов. - СПб.: Наука и Техника, 2013. - 352 с.].

Первый (20), второй (21), третий (22), четвертый (23) генераторы псевдослучайной последовательности (Генераторы ПСП) предназначены для формирования последовательностей равновероятных номеров частот в диапазоне i=1, …, N. В качестве генератора ПСП можно использовать любой генератор ПСП, производимый промышленностью, например, генератор ПСП, используемый в радиостанциях комплекса Р-168.

Регистр сдвига (24) предназначен для преобразования последовательной комбинации ПСП в параллельную. Регистр сдвига может быть реализован, например, на интегральной микросхеме К155ИР1.

Схема «И» предназначена для формирования управляющего напряжения на выходе методом умножения напряжений на ее входах. Схема «И» может быть выполнена, например, на интегральной микросхеме серии КР 1533.

Схема «ИЛИ» предназначена для формирования управляющего напряжения на выходе методом сложения напряжений на ее входах. Схема «ИЛИ» может быть выполнена, например, на интегральной микросхеме серии КР 1533.

Устройство, представленное на фиг. 1, функционирует следующим образом.

В скремблере (2) осуществляется перемежение импульсной битовой последовательности (ИБП), поступающей от источника сообщений (1). Преобразованная таким образом ИБП поступает на вход (27.1) первой (27), (28.1) второй (28), (29.1) третьей (29), (30.1) четвертой (30) схем «ИЛИ». На выходах (3.1.1-3.4.1) блока датчиков случайных чисел (3) (см. фиг. 2) формируются 16 различных комбинаций логических «0» или «1», синтезированных датчиками случайных чисел (3.1-3.4) блока датчиков случайных чисел (3). С выхода (3.1.1-3.4.1) блока датчиков случайных чисел (3) комбинация логических «0» или «1» поступает на второй вход (27.2) первой, (28.2) второй, (29.2) третьей, (30.2) четвертой схем «ИЛИ» и параллельно на входы (26.1-26.4) блока управляемых аттенюаторов (26) (см. фиг. 3). При поступлении информационного нуля ИБП на вход (27.1) первой, (28.1) второй, (29.1) третьей, (30.1) четвертой схем «ИЛИ», а на второй вход (27.2) первой, (28.2) второй, (29.2) третьей, (30.2) четвертой схем «ИЛИ» комбинации от одной до четырех логических единиц с выходов (3.1.1) первого, (3.2.1) второго, (3.3.1) третьего, (3.4.1) четвертого датчиков случайных чисел блока датчиков случайных чисел (3), на выходе соответствующей из схем «ИЛИ» формируется сигнал логической единицы, которые открывают управляемые ключи (8-11) соответственно и, тем самым, подключая соответствующие выходы блока управляемых аттенюаторов (26) к входам (16.1-16.4) первого сумматора (16). При этом, при поступлении информационного нуля ИБП на вход (27.1) первой, (28.1) второй, (29.1) третьей, (30.1) четвертой схем «ИЛИ» количеству логических «1» на выходах (3.1.1-3.4.1) блока датчиков случайных чисел (3) соответствует количество подключенных выходов блока управляемых аттенюаторов (26). Таким образом, информационному нулю ИБП на выходе (16.5) первого сумматора (16) соответствуют комбинации: от нуля (в пространство сигнал не излучается), одной, двух, трех или четырех, сформированных синтезаторами частот (4-7) высокочастотных гармонических колебаний. Единице ИБП всегда соответствуют сформированные синтезаторами частот (4-7) четыре высокочастотных гармонических колебаний (см. фиг. 3).

Уровень амплитуды высокочастотных гармонических колебаний формируется в блоке управляемых аттенюаторов (26). При этом, поступаемые комбинации от одной до четырех единиц с выходов (3.1.1) первого, (3.2.1) второго, (3.3.1) третьего, или (3.4.1) четвертого датчиков случайных чисел блока (3) соответственно на входы (26.1-26.4) блока управляемых аттенюаторов (26) открывают управляемые ключи (31-34) первой, (35-38) второй, (39-42) третьей, (43-46) четвертой схем аттенюаторов блока управляемых аттенюаторов (26) (см. фиг. 3) и, тем самым, подключают параллельно соединенные резистивные сопротивления R2-R5 к резистивному сопротивлению R1 в соответствующей схеме аттенюаторов, через которые поступает высокочастотное гармоническое колебание с выхода первого синтезатора частот (4) на второй высокочастотный вход (8.2) открытого первого управляемого ключа (8) к входу (16.1), с выхода второго синтезатора частот (5) на второй высокочастотный вход (9.2) второго открытого управляемого ключа (9) к входу (16.2), с выхода третьего синтезатора частот (6) на второй высокочастотный вход (10.2) открытого третьего управляемого ключа (10) к входу (16.3), с выхода четвертого синтезатора частот (7) на второй высокочастотный вход (11.2) открытого четвертого управляемого ключа (11) к входу (16.4) первого сумматора (16). Так, при поступлении с выхода (3.1.1) датчика случайных чисел блока датчиков случайных чисел (3) логической единицы на управляющий вход (26.1), являющимся общим входом для девятого (31), тринадцатого (35), семнадцатого (39), двадцать первого (43) управляемых ключей соответственно первой (26.1), второй (26.2), третьей (26.3), четвертой (26.4) схем аттенюатора, открываются управляемые ключи (31, 35, 39, 43) и, тем самым, подключая резистивное сопротивление R2 к резистивному сопротивлению R1, образующие параллельное соединение (см. фиг. 3). При поступлении с выхода (3.1.1) датчика случайных чисел блока (3) логического нуля на управляющие входы схем аттенюатора (26.1-26.4), управляемые ключи в соответствующих схемах аттенюаторов закрываются, при этом ветвь с сопротивлением R1 не содержит управляемый ключ и, в случае, когда управляемые ключи в схемах аттенюаторов закрыты - высокочастотное гармоническое колебание с соответствующих выходов синтезаторов частот (4-7) подключается через сопротивление R1 к второму высокочастотному входу (8.2-11.2) управляемых ключей (8-11) соответственно (см. фиг. 3).

Таким образом, нулю ИБП соответствует различное количество сформированных синтезаторами частот (4-7) высокочастотных гармонических колебаний (единице ИБП соответствуют четыре высокочастотных гармонических колебаний), с ослаблением от максимального до минимального уровня, соответствующим параллельно-соединенным сопротивлениям R1-R5, которые поступают на выход сумматора (16.5), являющимся выходом устройства.

Синтезаторы частот (4) - (11) перестраиваются при изменении кода ПСП в случайные моменты времени. Изменение номиналов рабочих частот первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот производится соответственно при открытом пятом (12), шестом (13), седьмом (14), восьмом (15) управляемых ключах.

В этом случае на входы первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот подается код ПСП, в соответствии с которым производится смена номиналов рабочих частот. Причем на вход первого синтезатора частоты (4) подается код ПСП через пятый управляемый ключ (12), сформированный генератором ПСП (20). На вход второго синтезатора частоты (5) - код ПСП через шестой управляемый ключ (13), сформированный сложением во втором сумматоре (17) кода ПСП генератора ПСП (20) и (21). На вход третьего синтезатора частоты (6) - код ПСП через седьмой управляемый ключ (14), сформированный сложением в третьем сумматоре (18) суммарного кода ПСП генератора ПСП (20), генератора ПСП (21) и генератора ПСП (22). На вход четвертого синтезатора частоты (7) - код ПСП через восьмой управляемый ключ (15), сформированный сложением в четвертом сумматоре (19) суммарного кода ПСП генератора ПСП (20), генератора ПСП (21), генератора ПСП (22) и генератора ПСП (23). Такой способ формирования ПСП исключает совпадение кодов.

Пятый (12), шестой (13), седьмой (14), восьмой (15) управляемые ключи открываются при поступлении логической единицы с схемы «И» (25) на вторые входы (12.2), (13.2), (14.2), (15.2) данных ключей. Причем логическая единица формируется схемой «И» при поступлении единичного напряжения с первого (24.1) и второго (24.2) выходов регистра сдвига (24).

Таким образом, заявляемое устройство формирует структурно-скрытую двухпозиционную сигнальную конструкцию. При этом производится кодирование ИБП совокупностью рабочих частот: от нуля (сигнал не излучается) до четырех, уровни амплитуд которых также формируются случайным образом.

Применение данных методов внесения избыточности параметров, не несущих информацию, повышает неопределенность у постановщика помех в определении структуры сигнала для формирования оптимальной помехи, что ведет к увеличению временных или ресурсных затрат противоборствующей стороны, и, таким образом, повышает помехоустойчивость формируемого сигнала.

Для количественной оценки полученного выигрыша помехоустойчивости в среде Simulink построена модель сигнала, формируемого разработанным устройством. Анализ результатов имитационного моделирования показал, что временное и спектральное представление сигнала, формируемого разработанным устройством, существенно отличается от известных сигналов, а его помехоустойчивость повышается примерно на 2,3 дБ. Таким образом, разработанное устройство формирует структурно-скрытый сигнал с двухпозиционной манипуляцией с повышенным значением помехоустойчивости при воздействии имитационных помех.

| название | год | авторы | номер документа |

|---|---|---|---|

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2296420C1 |

| Устройство формирования сигналов с четырехпозиционной манипуляцией | 2016 |

|

RU2631149C1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1988 |

|

SU1540013A2 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

| УСТРОЙСТВО МОНИТОРИНГА БЕЗОПАСНОСТИ АВТОМАТИЗИРОВАННЫХ СИСТЕМ | 2004 |

|

RU2270478C1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1984 |

|

SU1211750A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2009 |

|

RU2417537C1 |

| Широкополосное приемопередающее устройство | 2016 |

|

RU2628328C1 |

| РАДИОЛИНИЯ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2004 |

|

RU2273099C1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ ФАЗЫ СИГНАЛА | 2017 |

|

RU2646602C1 |

Заявленное устройство относится к электросвязи. Техническим результатом заявляемого устройства является повышение помехоустойчивости формируемого сигнала на основе его структурной скрытности при воздействии имитационных помех. Для достижения технического результата предлагается устройство, состоящее из источника сообщений (1), скремблера (2), блока датчиков случайных чисел (3), первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот, первого (8), второго (9), третьего (10), четвертого (11), пятого (12), шестого (13), седьмого (14), восьмого (15) управляемых ключей, первого (16), второго (17), третьего (18), четвертого (19) сумматоров, первого (20), второго (21), третьего (22), четвертого (23) генераторов псевдослучайной последовательности, регистра сдвига (24), схемы «И» (25), блока управляемых аттенюаторов (26), первой (27), второй (28), третьей (29), четвертой (30) схем «ИЛИ». 2 з.п. ф-лы, 3 ил.

1. Устройство формирования структурно-скрытых сигналов с двухпозиционной манипуляцией, содержащее источник сообщений (1), выход которого подключен к входу скремблера (2), первый (4), второй (5), третий (6), четвертый (7) синтезаторы частот, выходы которых подключены к высокочастотным входам (8.2) первого (8), (9.2) второго (9), (10.2) третьего (10), (11.2) четвертого (11) управляемых ключей соответственно, сигнальные выходы которых подключены к входам (16.1), (16.2), (16.3), (16.4) первого сумматора (16) соответственно, а выход (16.5) первого сумматора (16) является выходом устройства, второй сумматор (17), выход которого подключен к первому входу (13.1) шестого управляемого ключа (13) и к второму входу (18.2) третьего сумматора (18), к первому входу (18.1) которого подключен выход третьего генератора ПСП (22), а выход третьего сумматора (18) подключен к первому входу (14.1) седьмого управляемого ключа (14) и к второму входу (19.2) четвертого сумматора (19), к первому входу (19.1) которого подключен выход четвертого генератора ПСП (23), первого генератора ПСП (20), выход которого подключен к входу регистра сдвига (24), к первому входу (12.1) пятого управляемого ключа (12) и к второму входу (17.2) второго сумматора (17), к первому входу (17.1) которого подключен выход второго генератора ПСП (21), четвертый сумматор (19), выход которого подключен к первому входу (15.1) восьмого управляемого ключа (15), регистр сдвига (24), выходы (24.1) и (24.2) которого подключены к первому и второму входам схемы «И» (25) соответственно, выход которой подключен к вторым входам (12.2) пятого (12), (13.2) шестого (13), (14.2) седьмого (14), (15.2) восьмого (15) управляемых ключей, выходы которых подключены к входам первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот соответственно, отличающееся тем, что дополнительно введены первая (27), вторая (28), третья (29), четвертая (30) схемы «ИЛИ», первые управляющие входы которых (27.1) первой (27), (28.1) второй (28), (29.1) третьей (29), (30.1) четвертой (30) схем «ИЛИ» соответственно подключены к выходу скремблера (2), блок датчиков случайных чисел (3), выходы (3.1.1), (3.2.1), (3.3.1), (3.4.1) которого подключены к вторым управляющим входам (27.2) первой (27), (28.2) второй (28), (29.2) третьей (29), (30.2) четвертой (30) схем «ИЛИ» соответственно и к управляющим входам (26.1), (26.2), (26.3), (26.4) блока управляемых аттенюаторов (26), к высокочастотным входам (26.5), (26.6), (26.7), (26.8) которого подключены высокочастотные выходы первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот, а выходы блока управляемых аттенюаторов (26) подключены к высокочастотным входам (8.2) первого (8), (9.2) второго (9), (10.2) третьего (10), (11.2) четвертого (11) управляемых ключей.

2. Устройство по п. 1, отличающееся тем, что блок датчиков случайных чисел (3) состоит из первого (3.1), второго (3.2), третьего (3.3), четвертого (3.4) идентичных датчиков случайных чисел, выходы которых являются выходами блока и подключены соответственно к вторым управляющим входам (27.2) первой, (28.2) второй, (29.2) третьей, (30.2) четвертой схем «ИЛИ» соответственно и к управляющим входам (26.1), (26.2), (26.3), (26.4) блока управляемых аттенюаторов (26).

3. Устройство по п. 1, отличающееся тем, что блок управляемых аттенюаторов (26) состоит из первой (26.1), второй (26.2), третьей (26.3), четвертой (26.4) идентичных схем аттенюаторов, первая схема аттенюатора (26.1) содержит девятый (31), десятый (32), одиннадцатый (33), двенадцатый (34) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, вторая схема аттенюатора (26.2) содержит тринадцатый (35), четырнадцатый (36), пятнадцатый (37), шестнадцатый (38) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, третья схема аттенюатора (26.3) содержит семнадцатый (39), восемнадцатый (40), девятнадцатый (41), двадцатый (42) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, четвертая схема аттенюатора (26.4) содержит двадцать первый (43), двадцать второй (44), двадцать третий (45), двадцать четвертый (46) управляемые ключи, резистивные сопротивления R1, R2, R3, R4, R5, управляемые входы девятого (31), тринадцатого (35), семнадцатого (39), двадцать первого (43) управляемых ключей подключены к входу (26.1) блока управляемых аттенюаторов (26), а высокочастотные входы девятого (31), тринадцатого (35), семнадцатого (39), двадцать первого (43) управляемых ключей подключены к высокочастотному выходу первого (4) синтезатора частот, а выходы девятого (31), тринадцатого (35), семнадцатого (39), двадцать первого (43) управляемых ключей подключены к резистивному сопротивлению R2, управляемые входы десятого (32), четырнадцатого (36), восемнадцатого (40), двадцать второго (44) управляемых ключей подключены к входу (26.2) блока управляемых аттенюаторов (26), а высокочастотные входы десятого (32), четырнадцатого (36), восемнадцатого (40), двадцать второго (44) управляемых ключей подключены к высокочастотному выходу второго (5) синтезатора частот, выходы десятого (32), четырнадцатого (36), восемнадцатого (40), двадцать второго (44) управляемых ключей подключены к резистивному сопротивлению R3, управляемые входы одиннадцатого (33), пятнадцатого (37), девятнадцатого (41), двадцать третьего (45) управляемых ключей подключены к входу (26.3) блока управляемых аттенюаторов (26), а высокочастотные входы одиннадцатого (33), пятнадцатого (37), девятнадцатого (41), двадцать третьего (45) управляемых ключей подключены к высокочастотному выходу третьего (6) синтезатора частот, выходы одиннадцатого (33), пятнадцатого (37), девятнадцатого (41), двадцать третьего (45) управляемых ключей подключены к резистивному сопротивлению R4, управляемые входы двенадцатого (34), шестнадцатого (38), двадцатого (42), двадцать четвертого (46) управляемых ключей подключены к входу (26.4) блока управляемых аттенюаторов (26), а высокочастотные входы двенадцатого (34), шестнадцатого (38), двадцатого (42), двадцать четвертого (46) управляемых ключей подключены к высокочастотному выходу четвертого (7) синтезатора частот, выходы двенадцатого (34), шестнадцатого (38), двадцатого (42), двадцать четвертого (46) управляемых ключей подключены к резистивному сопротивлению R5, вход резистивного сопротивления R1 первой (26.1), второй (26.2), третьей (26.3), четвертой (26.4) схем аттенюаторов подключен к высокочастотному выходу первого (4), второго (5), третьего (6), четвертого (7) синтезаторов частот соответственно, а выход резистивного сопротивления R1 является соответствующим выходом блока управляемых аттенюаторов (26).

| Устройство формирования сигналов с четырехпозиционной манипуляцией | 2016 |

|

RU2631149C1 |

| СИСТЕМА ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2001 |

|

RU2188516C1 |

| СИСТЕМА ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2004 |

|

RU2258313C1 |

| Нагнетательный клапан | 1971 |

|

SU527527A2 |

Авторы

Даты

2020-06-04—Публикация

2019-12-26—Подача