Изобретение относится к области радиосвязи и может быть использовано в системах связи с программной перестройкой рабочих частот, функционирующих в условиях воздействия помех, уровень которых периодически изменяется по частотам программной перестройки.

Известны радиолинии, обеспечивающие ведение связи в режиме программной перестройки рабочих частот (ППРЧ) (см., например, патент США №4653068, 11.02.1987 "Frequency Hopping Data Communication System", патент №2157051 от 27.09.2000 "Широкополосное приемопередающее устройство").

Радиолиния по патенту США №4653068 содержит на передающей стороне кодер, модулятор, усилитель мощности, передающую антенну, блок синхронизации, генератор псевдослучайной последовательности, блок управления, синтезатор частот. На приемной стороне - приемную антенну, входной усилитель, смеситель-гетеродин, детектор, решающее устройство, декодер, блок синхронизации, генератор псевдослучайной последовательности, блок управления и блок автоматической регулировки усиления. Недостатком данной радиолинии является относительно низкая помехоустойчивость при наличии в полосе перестройки не пригодных для ведения радиосвязи частот.

Радиолиния по патенту №2157051 содержит на передающей стороне первый и второй фазовые манипуляторы, сумматор, смеситель, частотный синтезатор, два высокочастотных ключа, элемент НЕ, генератор псевдослучайной последовательности, передающую антенну. На приемной стороне - приемную антенну, смеситель, усилитель промежуточной частоты, демодулятор, генератор псевдослучайной последовательности, частотный синтезатор, два высокочастотных ключа, элемент НЕ. Недостатком данной радиолинии является относительно низкая помехоустойчивость при наличии непригодных частот в диапазоне программной перестройки, а также при изменяющемся по частотам программной перестройки уровне помех.

Наиболее близкой по своей технической сущности к заявляемой радиолинии является радиолиния, обеспечивающая программную перестройку рабочих частот, описанная в патенте РФ №2185029, МПК7 Н 04 В 15/00, заявл. 12.02.2001, опубл. 10.07.2002, бюллетень №19.

Ближайший аналог (прототип) содержит на передающей стороне кодер, модулятор, усилитель мощности, передающую антенну, блок синхронизации, генератор псевдослучайной последовательности, преобразователь псевдослучайной последовательности, блок управления, синтезатор частот. На приемной стороне - приемную антенну, входной усилитель, смеситель-гетеродин, детектор, решающее устройство, декодер, блок синхронизации, генератор псевдослучайной последовательности, преобразователь псевдослучайной последовательности, блок управления и блок автоматической регулировки усиления.

На передающей стороне кодер, модулятор, усилитель мощности, передающая антенна соединены последовательно по информационным входам. Выход блока синхронизации подключен к входу генератора псевдослучайной последовательности. Выход блока управления подключен к входу синтезатора частот, выход которого подключен к входу управления модулятора. Выход генератора псевдослучайной последовательности подключен к входу преобразователя псевдослучайной последовательности, выход которого подключен к входу блока управления. Тактовый вход преобразователя псевдослучайной последовательности подключен к выходу блока синхронизации. Вход кодера является входом радиолинии.

На приемной стороне приемная антенна, входной усилитель, смеситель-гетеродин, детектор, решающее устройство, декодер соединены последовательно по информационным входам. Выход блока автоматической регулировки усиления подключен к управляющим входам входного усилителя и блока управления. Управляющий выход детектора подключен к входу блока автоматической регулировки усиления. Выход блока управления подключен к управляющим входам смесителя-гетеродина и решающего устройства, выход которого дополнительно подключен к входу блока синхронизации. Выход блока синхронизации подключен к управляющим входам генератора псевдослучайной последовательности и преобразователя псевдослучайной последовательности. Выход генератора псевдослучайной последовательности подключен к входу преобразователя псевдослучайной последовательности, выход которого подключен к входу блока управления. Выход декодера является выходом радиолинии.

Радиолиния-прототип обеспечивает ведение радиосвязи в режиме неравномерной программной перестройки по выделенным частотам: из диапазона программной перестройки исключаются не пригодные по уровню помех частоты, на частоты с большим отношением средней мощности сигнала к средней мощности помех радиолиния перестраивается чаще. За счет этого помехоустойчивость такой радиолинии с программной перестройкой рабочей частоты выше, чем радиолинии с равномерной программной перестройкой рабочей частоты (см. Одоевский С.М., Ерышев В.Г. "Адаптивно-игровой алгоритм переключения каналов передачи информации." / Сети связи и системы коммутации. Выпуск №11. - СПб: Тема, 2000. С.91-98).

Однако устройство-прототип имеет недостаток: неравномерная перестройка осуществляется по одному алгоритму в расчете на постоянно воздействующие на частотах программной перестройки помехи. Известно, что каналы метровой и декаметровой связи являются каналами с переменными параметрами (см. "Военные системы радиосвязи. Часть I" / В.В.Игнатов, Ю.П.Килимник, И.И.Никольский и др.; Под ред. В.В.Игнатова. - Л.: ВАС, 1989. С.19-26). В условиях воздействия изменяющихся по частотам программной перестройки помех данная радиолиния будет иметь помехоустойчивость, равную или меньшую, чем в случае равномерной программной перестройки, так как не позволяет изменить закон перестройки и может чаще обращаться к тем частотам, на которых уровень значений эффективного напряжения помех превышает допустимый.

Целью изобретения является разработка радиолинии с программной перестройкой рабочей частоты, позволяющей повысить помехоустойчивость в условиях воздействия помех, уровень которых периодически изменяется по частотам программной перестройки.

Указанная цель достигается тем, что в радиолинии с программной перестройкой рабочей частоты, включающей на первом и втором пунктах связи радиопередатчик с антенной и информационный радиоприемник с антенной, дополнительно введены блок коммутации, блок формирования весовых коэффициентов частот и блок анализа частот. Высокочастотный вход блока анализа частот подключен к дополнительной приемной антенне. Группы выходов коэффициентов сравнения передачи и приема блока формирования весовых коэффициентов частот по N выходов в каждой группе, где N>20 - количество выделенных для работы частот радиолинии, подключены соответственно к N входам коэффициентов сравнения передачи радиопередатчика и N входам коэффициентов сравнения информационного радиоприемника. Выходы управления радиопередатчиком и информационным радиоприемником блока формирования весовых коэффициентов частот подключены соответственно к управляющим входам радиопередатчика и информационного радиоприемника. Первый, второй, третий и четвертый управляющие выходы блока формирования весовых коэффициентов частот подключены соответственно к первому, второму, третьему и четвертому управляющим входам блока коммутации, информационные выход и вход которого подключены соответственно к информационному входу радиопередатчика и информационному выходу информационного радиоприемника. Входы "уровень помехи" и "коэффициенты частоты корреспондента" блока формирования весовых коэффициентов частот подключены к выходам соответственно "уровень помехи" блока анализа частот и "коэффициенты частоты корреспондента" блока коммутации. Вход "коэффициенты частоты" блока коммутации подключен к выходу "коэффициенты частоты" блока формирования весовых коэффициентов частот. Выходы управления "адрес", "считывание", "диапазон" блока формирования весовых коэффициентов частот подключены к соответствующим входам управления "адрес", "считывание", "диапазон" блока анализа частот. Вход "информация к корреспонденту" и выход "информация от корреспондента" блока коммутации являются соответственно входом и выходом соответствующего пункта связи.

Блок формирования весовых коэффициентов частот состоит из первого и второго дешифраторов, первой и второй группы регистров памяти по N регистров памяти в каждой группе, корреспондентского запоминающего устройства (КЗУ), запоминающего устройства (ЗУ), преобразователей параллельного кода в последовательный (ППКПс) и последовательного кода в параллельный (ППКПр), промежуточного запоминающего устройства (ПЗУ), микропроцессора (МПУ), обеспечивающего вычисление весовых коэффициентов частот, в зависимости от уровня помех на соответствующих частотах, а также формирование сигналов управления процессами анализа частот, вычисления, записи весовых коэффициентов частот, приема и передачи информации. N выходов первого и второго дешифраторов подключены к управляющим входам соответствующих регистров памяти соответственно первой и второй групп регистров памяти. Шестой и седьмой порты микропроцессора подключены соответственно к входам информации и управления первого дешифратора, десятый и двадцать восьмой порты микропроцессора подключены к информационным входам N регистров памяти соответственно первой и второй групп регистров памяти. Девятый и двадцать девятый порты микропроцессора подключены к входам синхронизации N регистров памяти соответственно первой и второй групп регистров памяти. Пятнадцатый, шестнадцатый, семнадцатый и восемнадцатый порты микропроцессора подключены соответственно к входам "запись/считывание", "разрешение", "адрес", "информация" промежуточного запоминающего устройства, а девятнадцатый, двадцатый, двадцать первый и двадцать второй порты микропроцессора подключены соответственно к входам "запись/считывание", "разрешение", "адрес", "информация" запоминающего устройства. Двадцать второй порт микропроцессора дополнительно подключен к входу преобразователя параллельного кода в последовательный, управляющий вход которого подключен к двадцать третьему порту микропроцессора и управляющему входу преобразователя последовательного кода в параллельный. Двадцать четвертый, двадцать пятый, двадцать шестой и двадцать седьмой порты микропроцессора подключены соответственно к входам "запись/считывание", "разрешение", "адрес", "информация" корреспондентского запоминающего устройства, и двадцать седьмой порт микропроцессора также подключен к выходу преобразователя последовательного кода в параллельный. Первый и тридцать первый порты микропроцессора подключены соответственно к входам информации и управления второго дешифратора. Тридцатый и восьмой порты микропроцессора являются выходом управления соответственно информационным радиоприемником и радиопередатчиком блока формирования весовых коэффициентов частот. N выходов первой и N выходов второй группы регистров памяти являются соответственно выходами коэффициентов сравнения передачи и коэффициентов сравнения приема блока. Одиннадцатый, двенадцатый, тринадцатый, четырнадцатый порты микропроцесора являются соответственно первым, вторым, третьим и четвертым управляющими выходами блока. Выход преобразователя параллельного кода в последовательный и вход преобразователя последовательного кода в параллельный являются соответственно выходом "коэффициенты частоты" и входом "коэффициенты частоты корреспондента" блока формирования весовых коэффициентов частот. Второй, третий и четвертый порты микропроцессора являются соответственно выходами "диапазон", "считывание", "адрес", а пятый порт микропроцессора является входом "уровень помехи" блока формирования весовых коэффициентов частот.

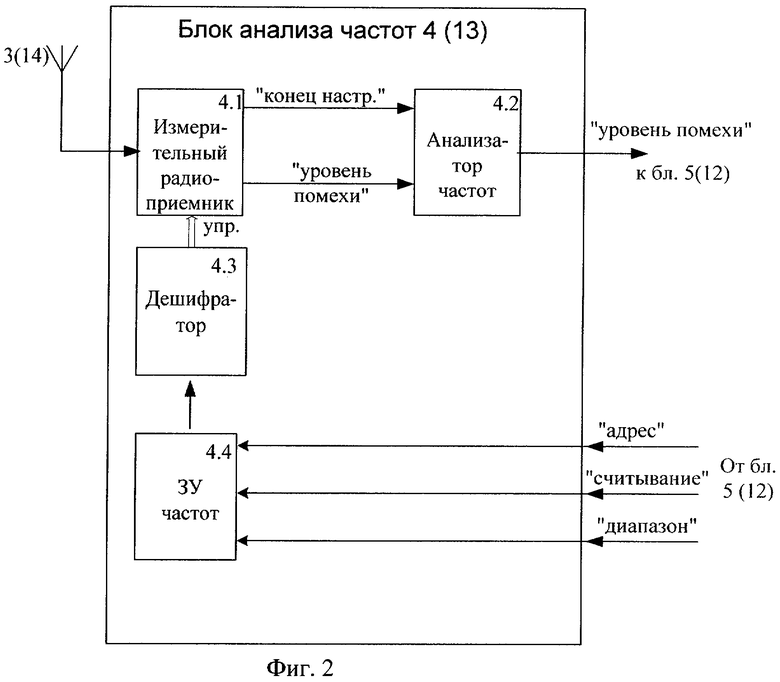

Блок анализа частот состоит из запоминающего устройства частот, дешифратора, анализатора частот, измерительного радиоприемника. Высокочастотный вход измерительного радиоприемника является высокочастотным входом блока. Выходы "конец настройки" и "уровень помехи" измерительного радиоприемника подключены к одноименным входам анализатора частот, выход которого является выходом "уровень помехи" блока. Выход запоминающего устройства подключен к входу дешифратора. Выход дешифратора подключен к входу управления измерительного радиоприемника. Входы "адрес", "считывание" и "диапазон" запоминающего устройства частот являются входами соответственно "адрес", "считывание" и "диапазон" блока анализа частот.

Блок коммутации состоит из первого, второго, третьего, четвертого элементов с тремя состояниями выхода, входы управления которых являются соответственно первым, вторым, третьим, четвертым управляющими входами блока. Информационные входы первого, второго и четвертого элементов с тремя состояниями выхода являются входами соответственно "информация от корреспондента", "информация" и "коэффициенты частоты" блока. Выход первого и четвертого элементов с тремя состояниями выхода объединены и являются информационным выходом блока. Выход второго и третьего элементов с тремя состояниями выхода являются выходами соответственно "информация от корреспондента" и "коэффициенты частоты корреспондента" блока. Информационный вход второго элемента с тремя состояниями выхода подключен к информационному входу третьего элемента с тремя состояниями выхода.

Благодаря новой совокупности признаков заявляемая радиолиния с программной перестройкой рабочей частоты чаще перестраивается на рабочие частоты с большим отношением эффективного значения напряжения сигнала к эффективному значению напряжения помех, а частоты, на которых уровень помех превышает допустимый, исключаются из механизма перестройки. Причем алгоритм неравномерной по частотам перестройки периодически изменяется в зависимости от изменения уровня помех по рабочим частотам. За счет этого помехоустойчивость заявляемой радиолинии с программной перестройкой рабочей частоты в условиях воздействия периодически изменяющегося по частотам уровня помех повышается.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусмотренных существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспобности "изобретательский уровень".

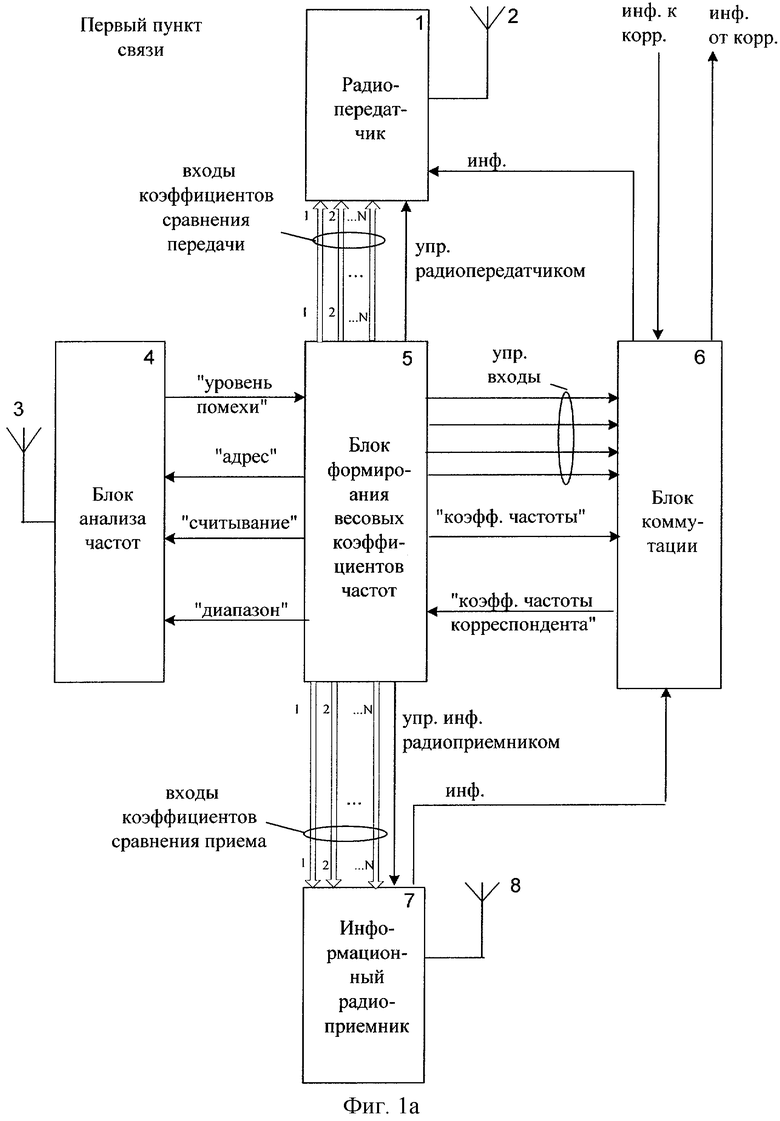

Заявленное устройство поясняется чертежами.

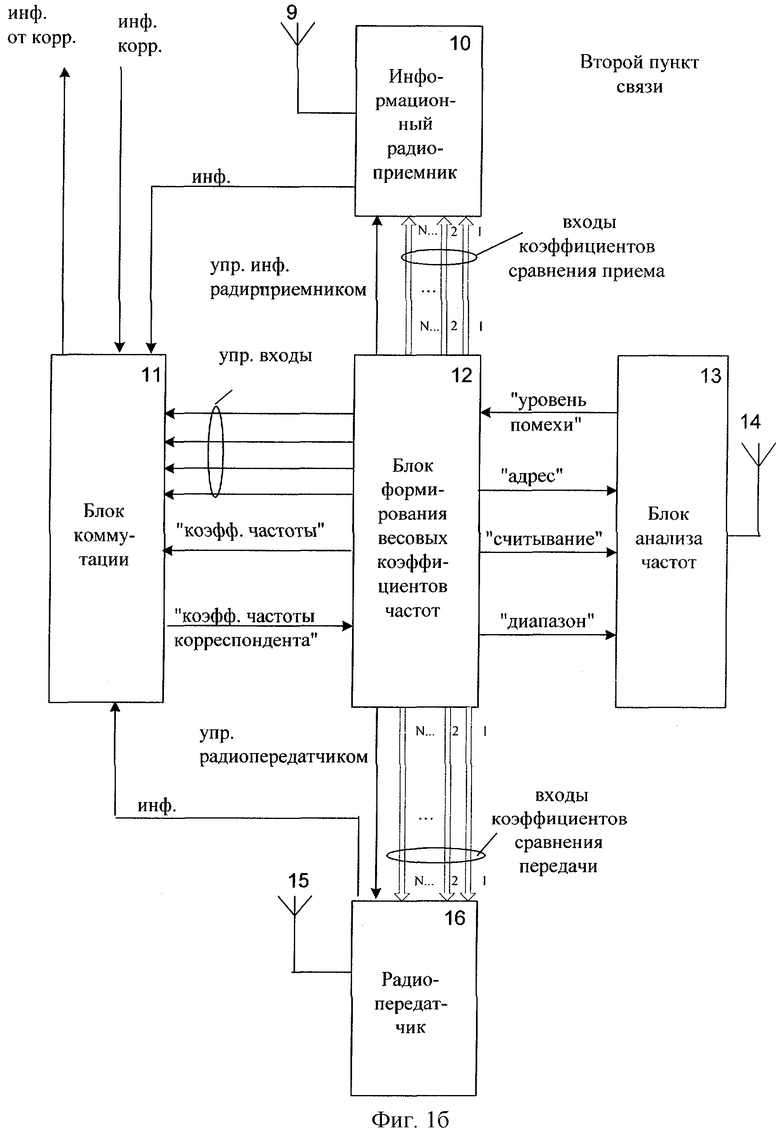

На фиг.1 изображена структурная схема радиолинии с программной перестройкой рабочей частоты;

фиг.2 - структурная схема блока анализа частот;

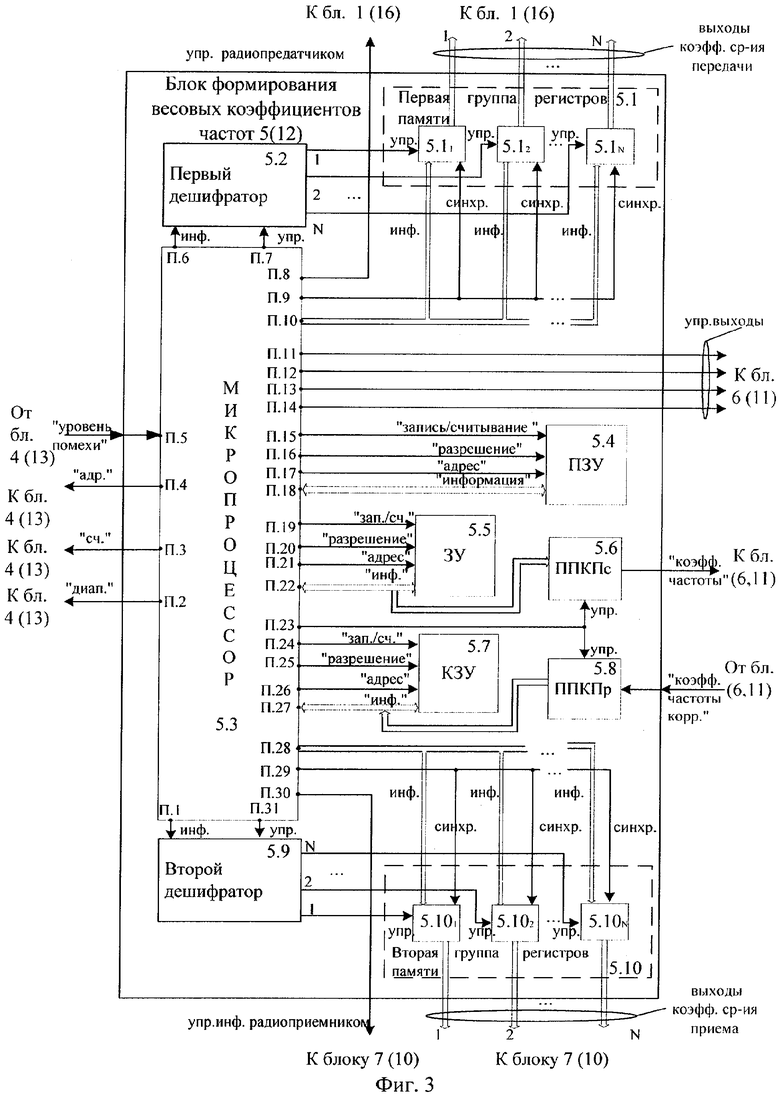

фиг.3 - структурная схема блока формирования весовых коэффициентов частот;

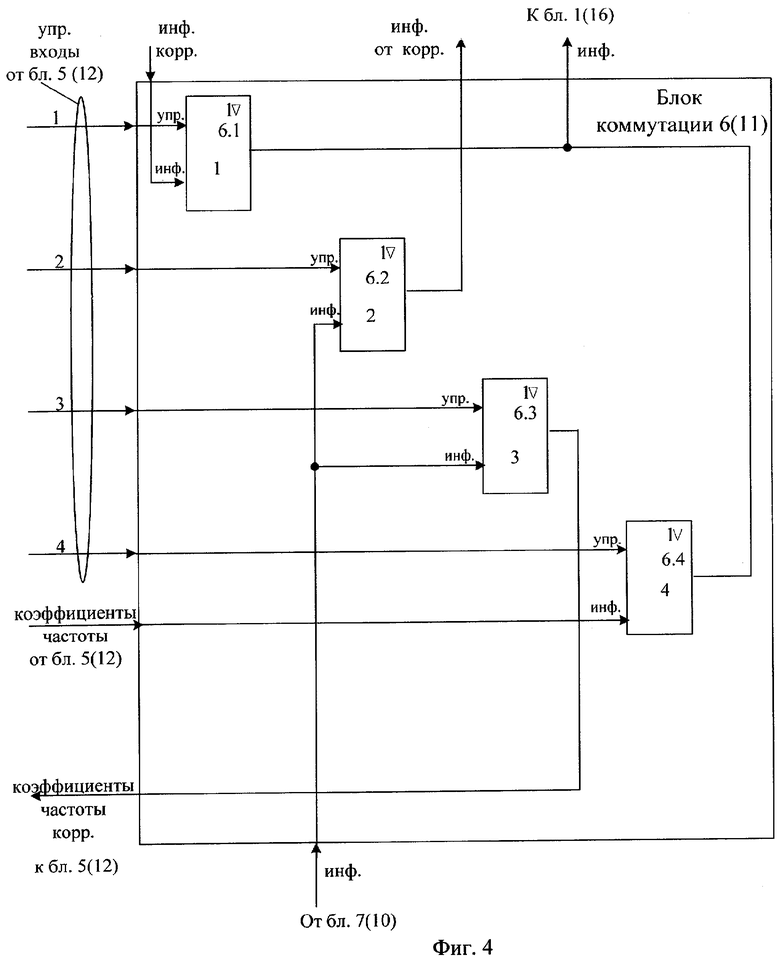

фиг.4 - структурная схема блока коммутации;

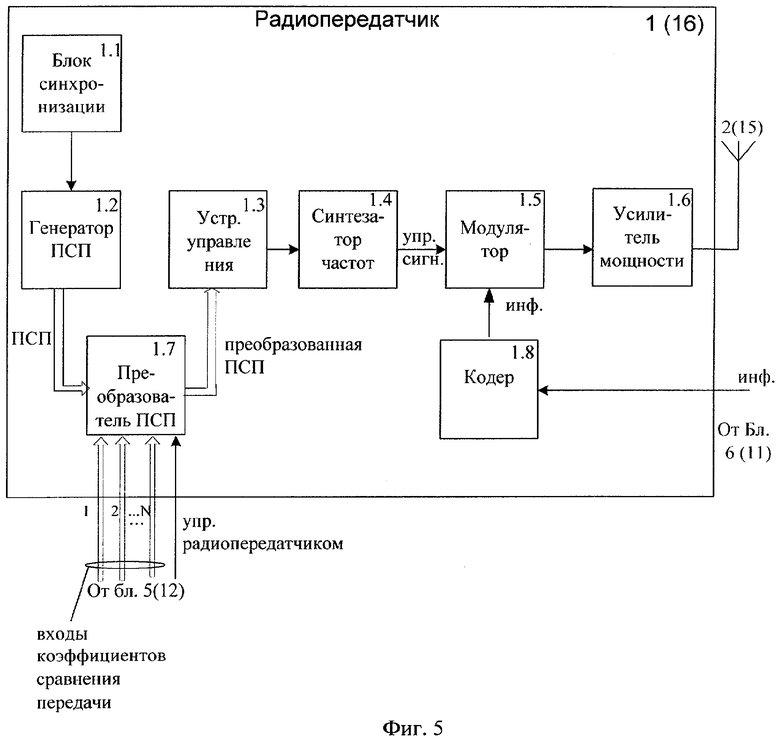

фиг.5 - структурная схема радиопередатчика;

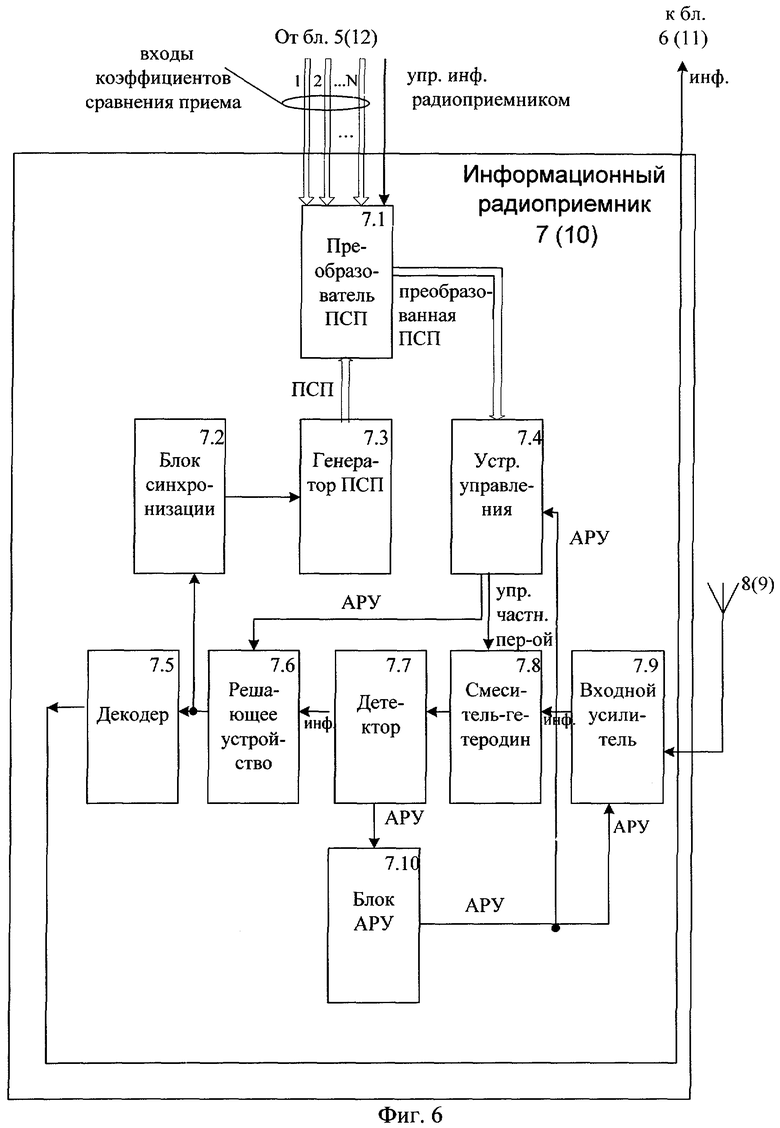

фиг.6 - структурная схема информационного радиоприемника;

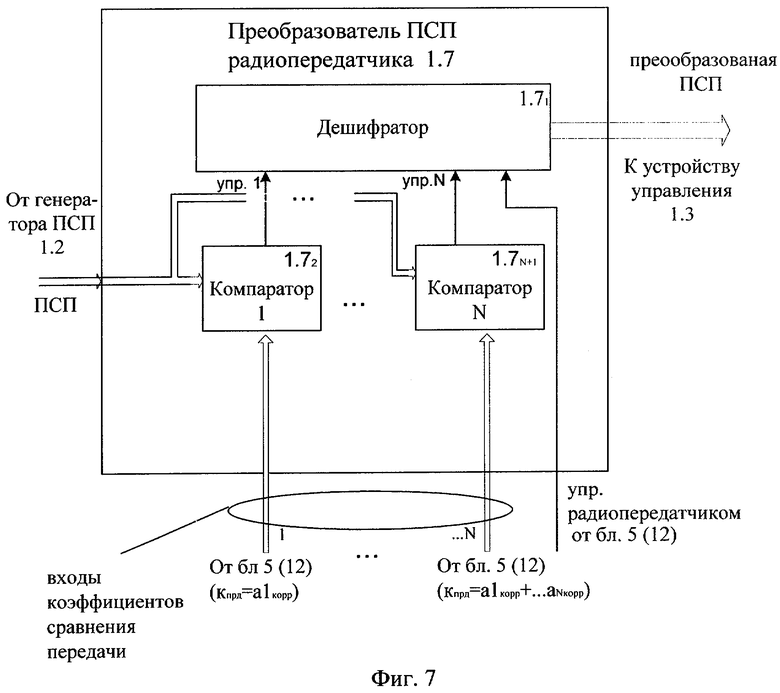

фиг.7 - структурная схема преобразователя псевдослучайной последовательности радиопередатчика;

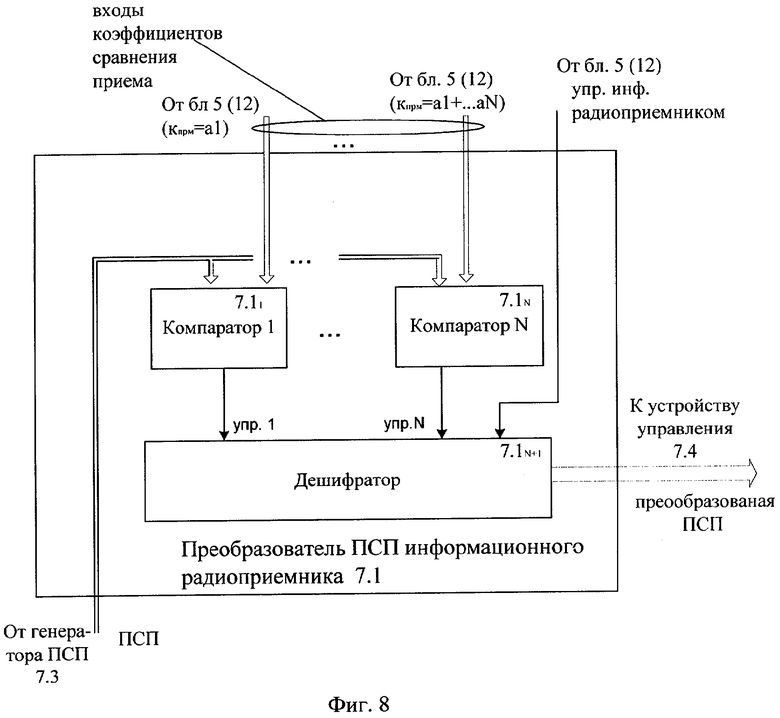

фиг.8 - структурная схема преобразователя псевдослучайной последовательности информационного радиоприемника;

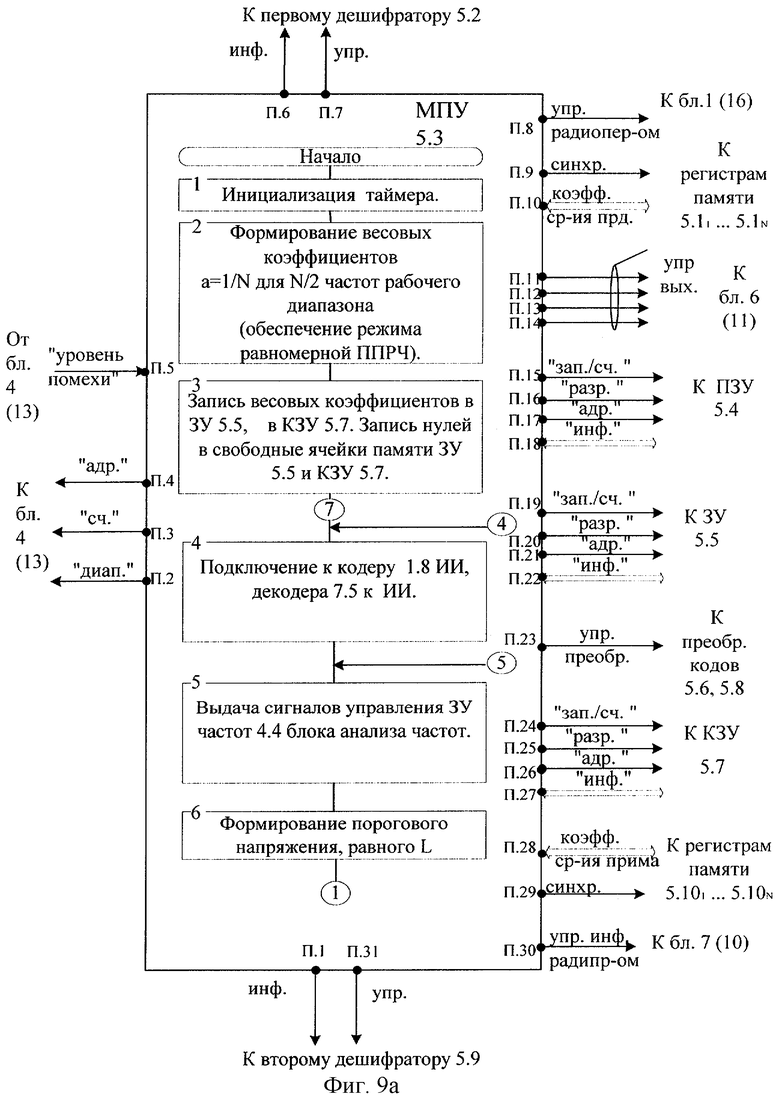

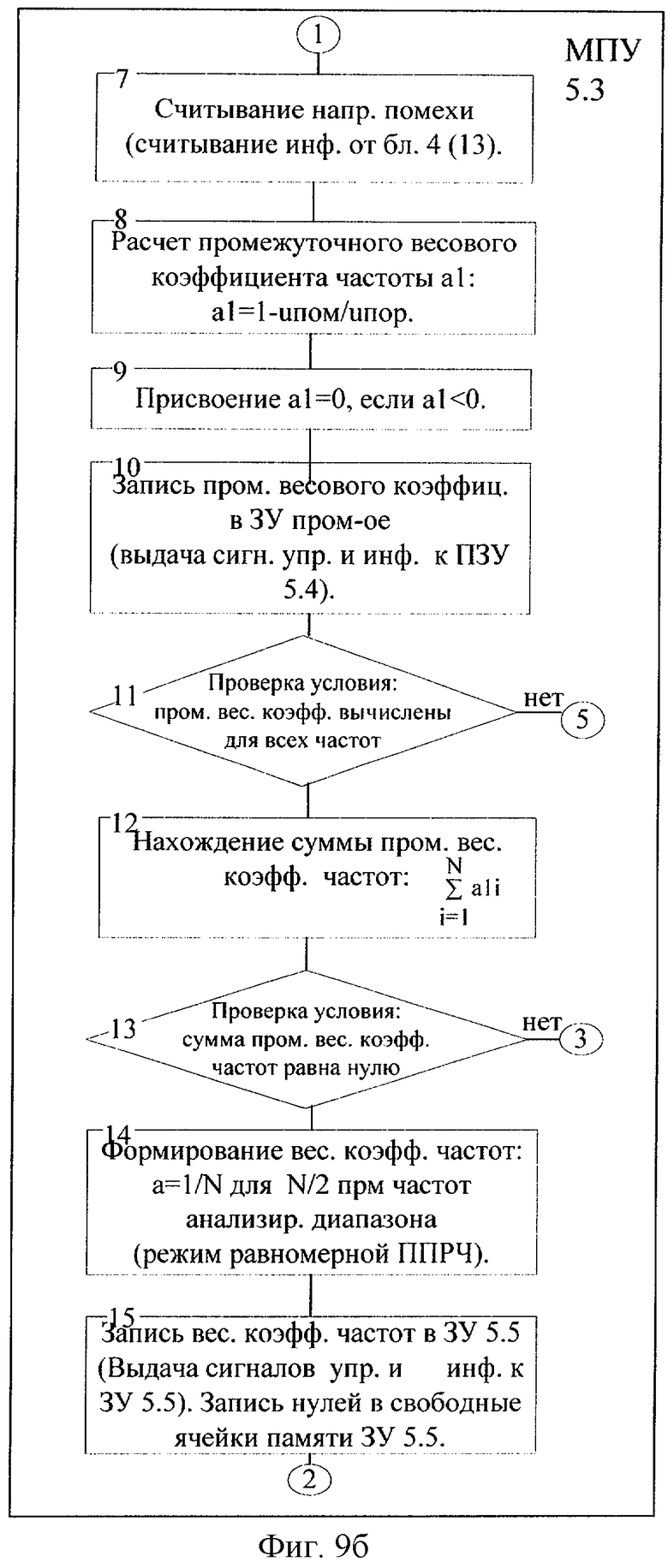

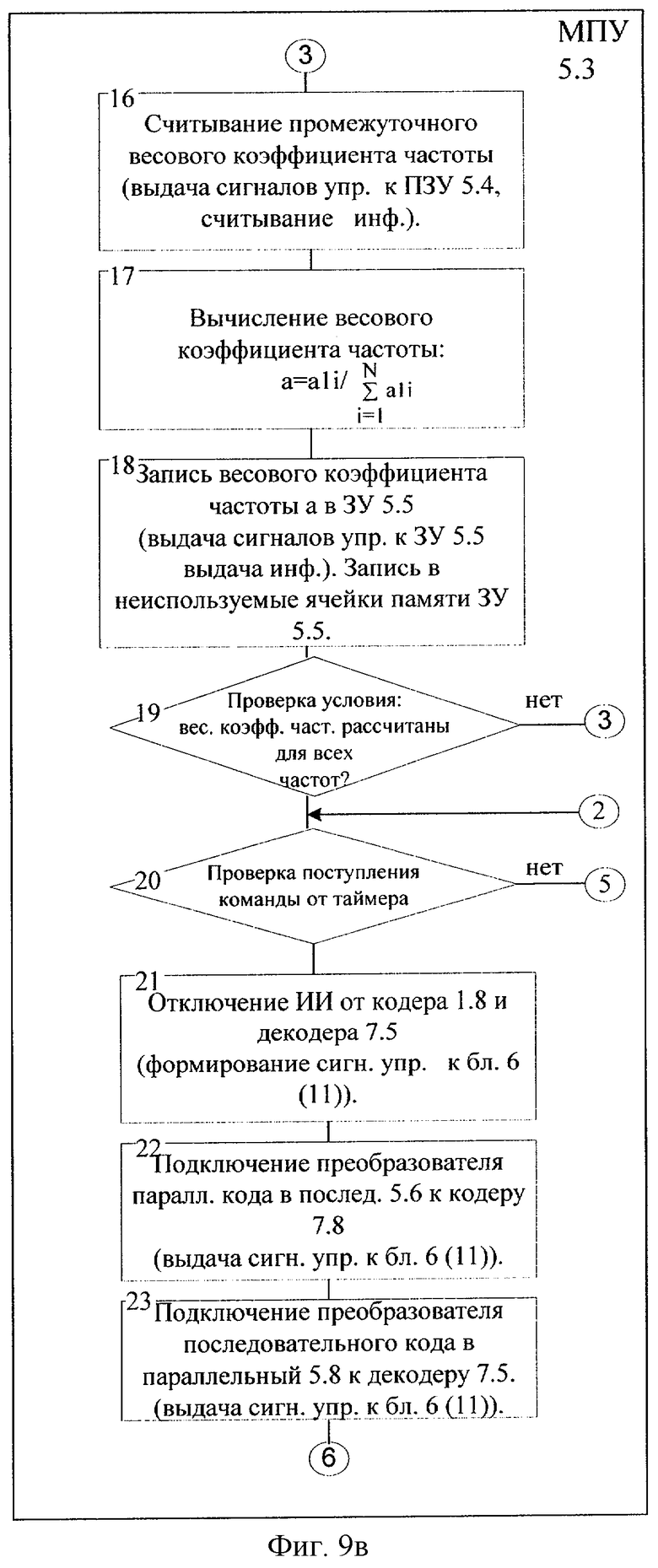

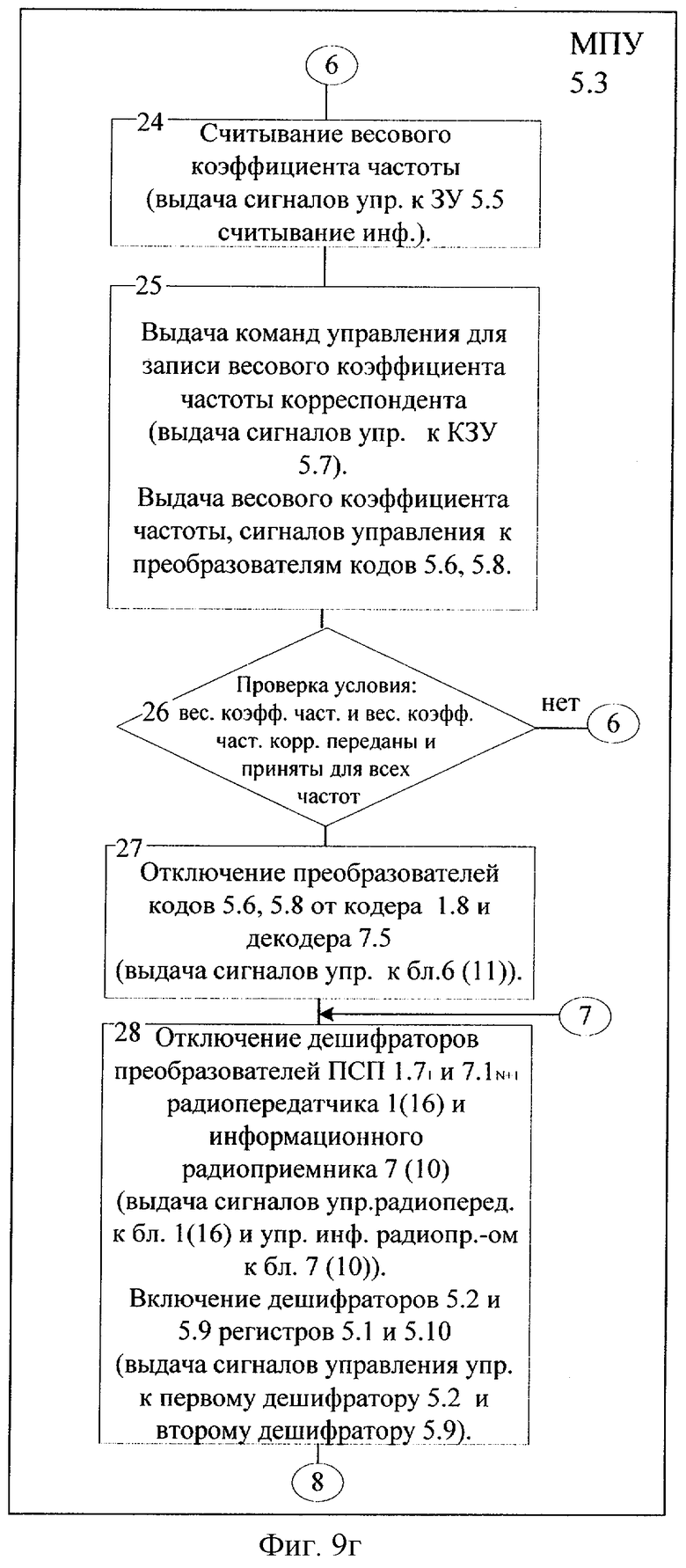

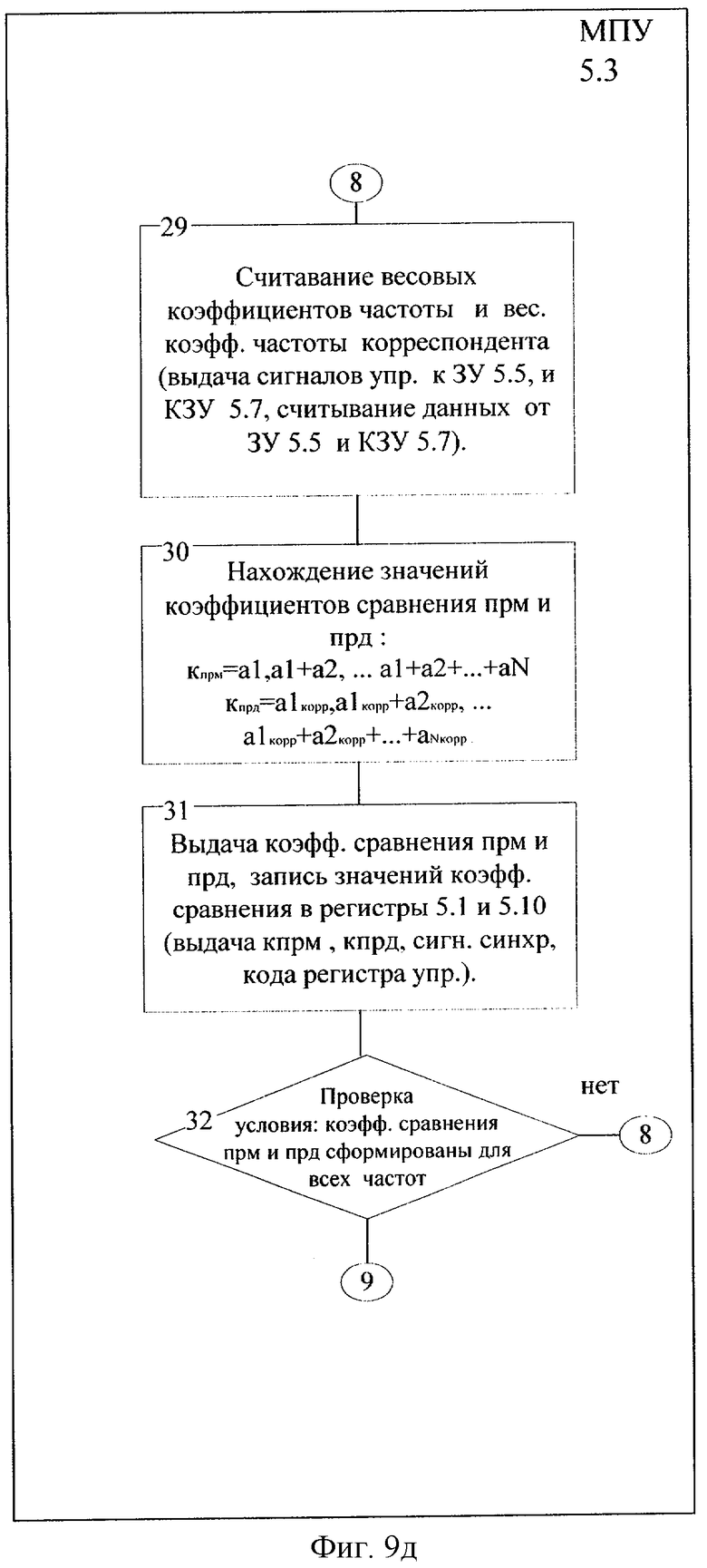

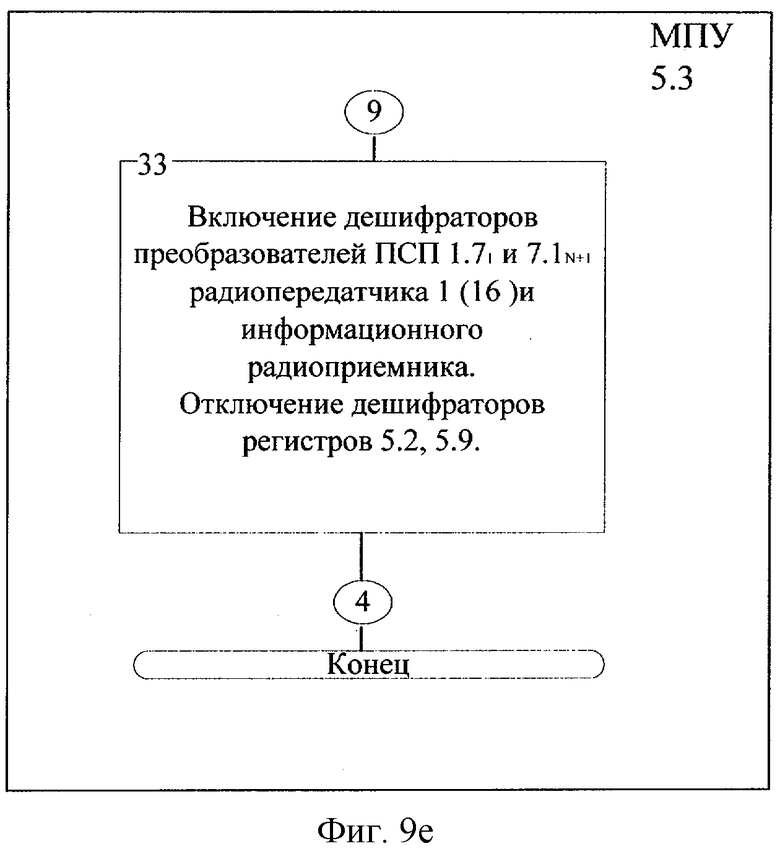

фиг.9 - алгоритм работы микропроцессора.

Заявляемая радиолиния с программной перестройкой рабочей частоты, представленная на фиг.1, содержит на первом и втором пунктах связи радиопередатчик 1 (16) с антенной 2 (15) и информационный радиоприемник 7 (10) с антенной 8 (9), блок коммутации 6 (11), блок формирования весовых коэффициентов частот 5 (12) и блок анализа частот 4 (13). Высокочастотный вход блока анализа частот 4 (13) подключен к дополнительной приемной антенне 3 (14), группы выходов коэффициентов сравнения передачи и приема блока формирования весовых коэффициентов частот 5 (12) по N выходов в каждой группе, где N>20 - количество выделенных для работы частот радиолинии, подключены соответственно к N входам коэффициентов сравнения передачи радиопередатчика 1 (16) и N входам коэффициентов сравнения информационного радиоприемника 7 (10). Выходы управления радиопередатчиком 1 (16) и информационным радиоприемником 7 (10) блока формирования весовых коэффициентов частот 5 (12) подключены соответственно к управляющим входам радиопередатчика 1 (16) и информационного радиоприемника 7 (10). Первый, второй, третий и четвертый управляющие выходы блока формирования весовых коэффициентов частот 5 (12) подключены соответственно к первому, второму, третьему и четвертому управляющим входам блока коммутации 6 (11), информационные выход и вход которого подключены соответственно к информационному входу радиопередатчика 1 (16) и информационному выходу информационного радиоприемника 7 (10). Входы "уровень помехи" и "коэффициенты частоты корреспондента" блока формирования весовых коэффициентов частот 5 (12) подключены к выходам соответственно "уровень помехи" блока анализа частот 4 (13) и "коэффициенты частоты корреспондента" блока коммутации 6 (11). Вход "коэффициенты частоты" блока коммутации 6 (11) подключен к выходу "коэффициенты частоты" блока формирования весовых коэффициентов частот 5 (12). Выходы управления "адрес", "считывание", "диапазон" блока формирования весовых коэффициентов частот 5 (12) подключены к соответствующим входам управления "адрес", "считывание", "диапазон" блока анализа частот 4 (13). Вход "информация к корреспонденту" и выход "информация от корреспондента" блока коммутации 6 (11) являются соответственно входом и выходом соответствующего пункта связи.

Радиопередатчик 1 (16) предназначен для преобразования первичного электрического сигнала в высокочастотный сигнал в режиме неравномерной программной перестройки рабочей частоты с периодически изменяющимся алгоритмом перестройки, усиления этого сигнала. Структурная схема радиопередатчика приведена на фиг.5. Радиопередатчик 1 (16) реализован как передающая часть радиолинии прототипа (см. патент РФ №2185029 от 12.02.01 "Радиолиния с псевдослучайной перестройкой рабочей частоты", с.3-19).

Дополнительно в блок преобразования псевдослучайной последовательности 1.7 радиопередатчика 1 (16) введены связи: коэффициенты сравнения передачи и управление радиопередатчиком от блока формирования весовых коэффициентов частот 5 (12). Кроме того, произведена замена структуры преобразователя псевдослучайной последовательности 1.7.

Преобразователь псевдослучайной последовательности 1.7 (7.1) предназначен для преобразования псевдослучайной последовательности, поступающей с выхода генератора ПСП 1.2 (7.3). Преобразователь псевдослучайной последовательности 1.7 (7.1) радиопередатчика 1 (16) и информационного радиоприемника 7 (10) выполнены по одинаковой схеме, представленной на фиг.7, фиг.8. Преобразователь псевдослучайной последовательности 1.7 (7.1) состоит из дешифратора 1.71 (7.1N+1) и N компараторов 1.72...1.7N+1 (7.1.1...7.1N). N выходов коэффициентов сравнения передачи (приема) блока формирования весовых коэффициентов частот 5 (12) подключены к первыми входами сравнения компараторов 1.72...1.7N+1 (7.1.1...7.1N). Вторые входы сравнения компараторов 1.72...1.7N+1 (7.1.1...7.1N) подключены к выходу генератора псевдослучайной последовательности 1.2 (7.3). Вход управления дешифратором 1.71 (7.1N+1) подключен к выходу управления радиопередатчиком 1 (16) (информационным радиоприемником 7 (10)) блока формирования весовых коэффициентов частот 5 (12). Выходы компараторов 1.72...1.7N+1 (7.1.1...7.1N) подключены к N информационным входам дешифратора 1.71 (7.1N+1). Компараторы 1.72...1.7N+1 (7.1.1...7.1N) предназначены для сравнения коэффициентов передачи каждой частоты программной перестройки со случайным числом генератора псевдослучайной последовательности 1.2 (7.3). Схема компаратора 1.72...1.7N+1 (7.1.1...7.1N) известна (см. Угрюмов Е.П. "Цифровая схемотехника". С-Пб: БХВ-Петербург, 2002. С.65, рис.2.16). Дешифратор 1.71 (7.1N+1) преобразовывает код с выхода компараторов в код соответствующей частоты при равномерной программной перестройке. Схема дешифратора 1.71 (7.1N+1) известна (см. Угрюмов Е.П. "Цифровая схемотехника". СПб: БХВ-Петербург, 2002, стр.47, рис.2). Вход EN1 дешифратора является входом управления радиопередатчиком 1 (16) (информационным радиоприемником 7 (10)).

Антенные устройства 2, 3, 8 (9, 14, 15) предназначены для преобразования высокочастотного радиосигнала в электромагнитные волны при передаче 2 (15) и обратно при приеме 8 (9), анализе частот 3 (14). Варианты реализации антенных устройств 2, 3, 8 (9, 14, 15) известны и приведены в ряде источников (см., например, Дж.Спилкер. "Цифровая связь". М.: Связь, 1979. С.169-172, рис.7.2 и рис.7.4).

Информационный радиоприемник 7 (10) предназначен для преобразования высокочастотного сигнала в режиме неравномерной программной перестройки рабочей частоты с периодически изменяющимся алгоритмом перестройки в первичный электрический сигнал, усиления этого сигнала. Структурная схема информационного радиоприемника приведена на фиг.6. Информационный радиоприемник 7 (10) реализован как приемная часть радиолинии прототипа (см. патент РФ №2185029 от 12.02.01 "Радиолиния с псевдослучайной перестройкой рабочей частоты". С.3-19).

Дополнительно в блок преобразования псевдослучайной последовательности 7.1 информационного радиоприемника 7 (10) введены связи: коэффициенты сравнения приема и управление информационным радиоприемником от блока формирования весовых коэффициентов частот 5 (12). Кроме того, заменена структура преобразователя псевдослучайной последовательности 7.1. Описание преобразователя псевдослучайной последовательности 7.1 приведено выше.

Блок анализа частот 4 (13) предназначен для измерения эффективного напряжения помех на частотах программной перестройки и преобразования его в цифровой код. Структурная схема блока анализа частот 4 (13) приведена на фиг.2. Блок анализа частот 4 (13) состоит из запоминающего устройства частот 4.4, дешифратора 4.3, анализатора частот 4.2, измерительного радиоприемника 4.1. Высокочастотный вход измерительного радиоприемника 4.1 является высокочастотным входом блока. Выходы "конец настройки" и "уровень помехи" измерительного радиоприемника 4.1 подключены к одноименным входам анализатора частот 4.2, выход которого является выходом "уровень помехи" блока 4 (13). Выход запоминающего устройства подключен к входу дешифратора 4.3. Выход дешифратора 4.3 подключен к входу управления измерительного радиоприемника 4.1. Входы "адрес", "считывание" и "диапазон" запоминающего устройства (ЗУ) частот 4.4 являются входами соответственно "адрес", "считывание" и "диапазон" блока анализа частот 4 (13).

Запоминающее устройство частот 4.4 предназначено для хранения номеров частот программной перестройки. Запоминающее устройство реализовано в патенте РФ №2220503 от 27.12.2003 "Устройство автоматического выбора рабочих частот" (см. фиг.6, с.25-26). Вход "диапазон" запоминающего устройства частот соответствует входу "код радионаправления".

Дешифратор 4.3 служит для преобразования номера частоты в код, необходимый для настройки измерительного радиоприемника 4.1 на анализируемую частоту. Схема дешифратора 4.3 известна (см. Гольденберг Л.М. "Импульсные и цифровые устройства". М.: Связь, 1973, с.462-468, рис.10.11).

Измерительный радиоприемник 4.1 предназначен для измерения эффективного напряжения помех на анализируемой частоте и выдачи полученного значения в анализатор частот. В качестве измерительного радиоприемника 4.1 может быть использован любой серийно выпускаемой промышленностью радиоприемник с диапазоном перестройки большим или равным диапазону программной перестройки, например радиоприемник Р-155У, схема которого приведена в "Техническом описании и инструкции по эксплуатации. Радиоприемное устройство Р-155У, ЦЛ 2.003.001, часть 1", 1973 г.

Анализатор частот 4.2 предназначен для преобразования значения эффективного напряжения помех в цифровой код. В качестве анализатора частот 4.2 может быть использован любой серийно реализованный промышленностью анализатор частот, схема которого приведена, например, в техническом описании на аппаратуру Р-016В (Р-016В, ЯР2.068.166, книга №1, 1992, с.43-57, рис.7.21), а также в техническом описании на аппаратуру анализа и выбора частот (аппаратура Р-015, ТШ1.170.005, книга №1, 1975, с.72-83, рис.12).

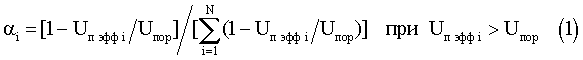

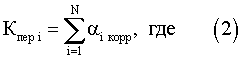

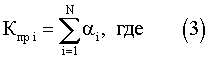

Блок формирования весовых коэффициентов частоты 5 (12) предназначен для

1. Вычисления весовых коэффициентов частот

αi=0 при Uп эфф i≤Uпор, где

αi - весовой коэффициент i-ой частоты; N - количество частот;

Uп эфф i - эффективное напряжение помехи; Uпор - порговое напряжение.

2. Вычисления коэффициентов сравнения приема и передачи

αi корр - весовой коэффициент i-ой частоты корреспондента; Кпер i - коэффициент передачи;

αi - весовой коэффициент i-ой частоты; Кпр i - коэффициент приема.

3. Управления процессами

- приема весовых коэффициентов частоты корреспондента и передачи весовых коэффициентов частоты корреспонденту при истечении заданного (оператором связи) интервала времени;

- вычисления весовых коэффициентов частот программной перестройки и коэффициентов сравнения приема и передачи;

- измерения эффективного значения напряжения помех на частотах программной перестройки;

- приема и передачи информации от корреспондента к корреспонденту;

- коммутации.

Структурная схема блока формирования весовых коэффициентов частот 5 (12) представлена на фиг.3. Блок формирования весовых коэффициентов частот 5 (12) состоит из первого 5.2 и второго 5.9 дешифраторов, первой 5.1 и второй 5.10 группы регистров памяти по N регистров памяти в каждой группе, корреспондентского запоминающего устройства 5.7 (КЗУ), запоминающего устройства 5.5 (ЗУ), преобразователей параллельного кода в последовательный 5.6 (ППКПс) и последовательного кода в параллельный 5.8 (ППКПр), промежуточного запоминающего устройства (ПЗУ), микропроцессора (МПУ) 5.3, обеспечивающего вычисление весовых коэффициентов частот, в зависимости от уровня помех на соответствующих частотах, а также формирование сигналов управления процессами анализа частот, вычисления, записи весовых коэффициентов частот, приема и передачи информации. N выходов первого 5.2 и второго 5.9 дешифраторов подключены к управляющим входам соответствующих регистров памяти соответственно первой 5.1 и второй 5.10 групп регистров памяти. Шестой и седьмой порты микропроцессора 5.3 подключены соответственно к входам информации и управления первого дешифратора 5.2, десятый и двадцать восьмой порты микропроцессора 5.3 подключены к информационным входам N регистров памяти соответственно первой 5.1 и второй 5.10 групп регистров памяти. Девятый и двадцать девятый порты микропроцессора 5.3 подключены к входам синхронизации N регистров памяти соответственно первой 5.1 и второй 5.10 групп регистров памяти. Пятнадцатый, шестнадцатый, семнадцатый и восемнадцатый порты микропроцессора 5.3 подключены соответственно к входам "запись/считывание", "разрешение", "адрес", "информация" промежуточного запоминающего устройства 5.4, а девятнадцатый, двадцатый, двадцать первый и двадцать второй порты микропроцессора 5.3 подключены соответственно к входам "запись/считывание", "разрешение", "адрес", "информация" запоминающего устройства 5.5. Двадцать второй порт микропроцессора 5.3 дополнительно подключен к входу преобразователя параллельного кода в последовательный 5.6, управляющий вход которого подключен к двадцать третьему порту микропроцессора 5.3 и управляющему входу преобразователя последовательного кода в параллельный 5.8. Двадцать четвертый, двадцать пятый, двадцать шестой и двадцать седьмой порты микропроцессора 5.3 подключены соответственно к входам "запись/считывание", "разрешение", "адрес", "информация" корреспондентского запоминающего устройства 5.7, и двадцать седьмой порт микропроцессора 5.3 также подключен к выходу преобразователя последовательного кода в параллельный 5.8. Первый и тридцать первый порты микропроцессора 5.3 подключены соответственно к входам информации и управления второго дешифратора 5.9. Тридцатый и восьмой порты микропроцессора 5.3 являются выходом управления соответственно информационным радиоприемником 7 (10) и радиопередатчиком 1 (16) блока формирования весовых коэффициентов частот 5 (12). N выходов первой 5.1 и N выходов второй 5.10 групп регистров памяти являются соответственно выходами коэффициентов сравнения передачи и коэффициентов сравнения приема блока 5 (12). Одиннадцатый, двенадцатый, тринадцатый, четырнадцатый порты микропроцесора 5.3 являются соответственно первым, вторым, третьим и четвертым управляющими выходами блока 5 (12). Выход преобразователя параллельного кода в последовательный 5.6 и вход преобразователя последовательного кода в параллельный 5.8 являются соответственно выходом "коэффициенты частоты" и входом "коэффициенты частоты корреспондента" блока формирования весовых коэффициентов частот 5 (12). Второй, третий и четвертый порты микропроцессора 5.3 являются соответственно выходами "диапазон", "считывание", "адрес", а пятый порт микропроцессора 5.3 является входом "уровень помехи" блока формирования весовых коэффициентов частот 5 (12).

Первая группа регистров памяти 5.1 предназначена для хранения коэффициентов сравнения передачи, рассчитываемых по формуле 3. Вторая группа регистров памяти 5.10 служит для хранения коэффициентов сравнения приема, рассчитываемых по формуле 2. Регистр памяти 5.11...5.1N, 5.101...5.10N является известным устройством (см. Шило В.Л. "Популярные цифровые микросхемы". М.: Радио и связь, 1987, стр.120-122, рис 1.86). Вход EI регистра памяти 5.11...5.1N, 5.101...5.10N является управляющим входом.

Первый 5.2 и второй 5.9 дешифраторы предназначены для преобразования адресного сигнала микропроцессора 5.3 в код регистра памяти 5.11...5.1N, 5.101...5.10N. Схемы дешифраторов 5.2 и 5.9 описаны в книге Угрюмов Е.П. "Цифровая схемотехника". СПб: БХВ-Петербург, 2002, с.47, рис.2.4.

Промежуточное запоминающее устройство 5.4 предназначено для хранения промежуточного результата вычисления весовых коэффициентов частот. Запоминающее устройство 5.5 служит для хранения весовых коэффициентов частот. Корреспондентское запоминающее устройство 5.7 предназначено для хранения весовых коэффициентов частот корреспондента. Промежуточное 5.4, корреспондентское 5.7 и запоминающее 5.5 устройства имеют структуру 2D и описаны в книге Угрюмов Е.П. "Цифровая схемотехника". СПб: БХВ-Петербург, 2002, с.182-183, рис.4.3.

Преобразователи параллельного кода в последовательный 5.6 и последовательного кода в параллельный 5.8 предназначены для преобразования кодов. Схемы данных преобразователей известны (см., например, Угрюмов Е.П. "Цифровая схемотехника". СПб: БХВ-Петербург, 2002, стр.146-150, рис.3.41, 3.42).

Микропроцессор 5.3 реализует выполнение функций блока анализа частот. Микропроцессор 5.3 работает по алгоритму, приведенному на фиг.9. Микропроцессор 5.3 реализуется на технологии больших интегральных схем (БИС). В качестве микропроцессора 5.3 может быть использован любой промышленно реализованный микропроцессор. Например, серии 8086 и выше. Описание принципов работы микропроцессора 5.3 приведено в книге Угрюмов Е.П. "Цифровая схемотехника". СПб: БХВ-Петербург, 2002, с.249-253.

Блок коммутации 6 (11) предназначен для осуществления подключения/отключения входов

- "коэффициенты частоты" от блока 5 (12) к радиопередатчику 1 (16);

- "информация корреспондентская" к радиопередатчику 1 (16);

- "информация" от измерительного радиоприемника 7 (10) на выход радиолинии,

а также выхода "коэффициенты частоты корреспондента" от блока 5(12) под действием управляющих сигналов от блока формирования весовых коэффициентов частот 5 (12). Структурная схема блока коммутации 6 (11) приведена на фиг.4. Блок коммутации 6 (11) состоит из первого 6.1, второго 6.2, третьего 6.3, четвертого 6.4 элементов с тремя состояниями выхода, входы управления которых являются соответственно первым, вторым, третьим, четвертым управляющими входами блока 6 (11). Информационные входы первого 6.1, второго 6.2 и четвертого 6.4 элементов с тремя состояниями выхода являются входами соответственно "информация от корреспондента", "информация" и "коэффициенты частоты" блока 6 (11). Выход первого 6.1 и четвертого 6.4 элементов с тремя состояниями выхода объединены и являются информационным выходом блока 6 (11). Выход второго 6.2 и третьего 6.3 элементов с тремя состояниями выхода являются выходами соответственно "информация от корреспондента" и "коэффициенты частоты корреспондента" блока 6 (11). Информационный вход второго элемента 6.2 с тремя состояниями выхода подключен к информационному входу третьего 6.3 элемента с тремя состояниями выхода. Элемент с тремя состояниями выхода 6.1...6.4 является коммутационным элементом блока коммутации 6 (11). Элемент с тремя состояниями выхода 6.1...6.4 известен и описан в книге Угрюмов Е. П. "Цифровая схемотехника". СПб: БХВ-Петербург, 2002, с.10-11, рис.1.4.

Заявляемое устройство работает следующим образом.

Первоначально на первом и втором пунктах связи производится инициализация таймера: установка интервала времени, на котором весовые коэффициенты частот не изменяются (интервала квазистационарности одночастотного канала декаметровой связи - 5-7 минут), запуск таймера (см. блок 1 алгоритма работы МПУ 5.3). Таймер реализован программно в блоке формирования весовых коэффициентов частот 5 (12) на основе микропроцессора 5.3. Далее микропроцессор 5.3 осуществляет вычисление весовых коэффициентов частот a=1/N и запись этих коэффициентов в первую половину запоминающих ячеек запоминающего устройства 5.5 путем выдачи разрешающего сигнала на порт 20, адреса - на порт 21, сигнала записи - на порт 19 и коэффициентов частот - на порт 22 и в первую половину ячеек корреспондентского запоминающего устройства 5.7 путем выдачи разрешающего сигнала на порт 25, адреса - на порт 26, сигнала записи - на порт 24 и коэффициентов частот - на порт 27. В свободные ячейки памяти записываются нули. Весовой коэффициент первой частоты программной перестройки записывается в первую ячейку памяти, второй во вторую и т.д. После этого микропроцессор 5.3 осуществляет отключение дешифраторов 1.71 преобразователя псевдослучайной последовательности 1.7 радиопередатчика 1 (16) и дешифратора 7.1N+1 преобразователя псевдослучайной последовательности 7.1 информационного радиоприемника 7 (10) посредством выдачи логического нуля на порты 8 и 30 (выход управление радиопередатчиком 1 (16) и информационным радиоприемником 7 (10) соответственно блока формирования весовых коэффициентов частот 5 (12)) и включение первого 5.2 и второго 5.9 дешифраторов блока формирования весовых коэффициентов частот 5 (12) посредством выдачи сигнала логической единицы на порты 7 и 31. Далее микропроцессор 5.3 осуществляет считывание весовых коэффициентов частот из запоминающего устройства 5.5 и корреспондентского запоминающего устройства 5.7 (операция считывания аналогична операции записи за исключением: вместо сигнала "запись" на запоминающее устройство подается сигнал "чтение" через соответствующий порт микропроцессора, операция записи в запоминающее устройство 5.5 и корреспондентское запоминающее устройство 5.7 описана выше). Далее микропроцессором 5.3 вычисляются коэффициенты сравнения передачи и приема частот программной перестройки по формуле (2) и (3). После каждого вычисления микропроцессор 5.3 осуществляет запись коэффициентов сравнения передачи в первую группу регистров памяти 5.1 путем выдачи кода регистра на первый дешифратор 5.2 через порт 6 и второй дешифратор 5.9 через порт 1, сигналов синхронизации - через порт 9 (первая группа регистров памяти 5.1) и порт 29 (вторая группа регистров памяти 5.9), коэффициентов сравнения передачи через порт 10 и коэффициентов сравнения приема - через порт 28. Далее микропроцессор 5.3 осуществляет отключение первого 5.2 и второго дешифраторов 5.9 путем выдачи сигнала логического нуля на порты 31 и 7 и включает дешифраторы преобразователей псевдослучайной последовательности 1.7 и 7.1 путем выдачи сигнала логической единицы на порты 8 и 30. Затем микропроцессор 5.3 формирует сигнал на подключение входа радиолинии к кодеру 1.8 радиопередатчика 1 (16) и декодера 7.5 к выходу радиолинии путем выдачи сигнала логической единицы на первый и второй входы блока коммутации 6 (11) через порты 11 и 12. Осуществляется процесс передачи (приема) информации к корреспонденту (от корреспондента). Все вышеперечисленные операции кроме инициализации таймера и вычисления весовых коэффициентов частот a=1/N предназначены для подготовки каждого пункта связи к ведению радиосвязи в режиме программной перестройки с учетом вычисленных коэффициентов частот. После выполнения вышеперечисленных операций радиолиния работает в режиме равномерной программной перестройки рабочих частот (все частоты программной перестройки, на которых работает радиолиния в текущий момент времени, используются одинаковое количество раз).

Отличительной особенностью работы заявляемой радиолинии с программной перестройкой рабочей частоты является то, что каждому пункту связи на передачу выделяется два диапазона частот программной перестройки: Δf1, Δf2 - первому пункту связи, Δf3, Δf4 - второму пункту связи. Каждый диапазон содержит N/2 частот. Первоначально первый пункт связи работает на передачу в диапазоне Δf1, а анализ частот осуществляет в диапазоне Δf4, второй пункт связи работает в диапазоне Δf3, анализ частот - Δf2. Весовые коэффициенты частот диапазона передачи первого и второго пунктов связи, на которых работает радиолиния в текущий момент времени, приравниваются к нулю. Каждому диапазону частот на первом и втором пункте связи выделяется строго определенная область памяти для записи весовых коэффициентов частот в запоминающем устройстве 5.5 и корреспондентском запоминающем устройстве 5.7. После срабатывания таймера первый пункт связи осуществляет передачу в диапазоне Δf2, анализ частот - в диапазоне Δf3, второй пункт связи - передачу в диапазоне Δf4, анализ частот - в диапазоне Δf1. После очередной команды от таймера первый пункт связи осуществляет передачу в диапазоне Δf1, анализ частот - в диапазоне Δf4, второй пункт связи - передачу в диапазоне Δf3, анализ частот - Δf2 и т.д. Такой алгоритм работы радиолинии с ППРЧ предназначен для того, чтобы информация, передаваемая корреспондентом, не влияла на анализ частот программной перестройки, кроме того, способствует увеличению помехозащищенности радиолинии с ППРЧ. Данный алгоритм реализуется программно на основе микропроцессора 5.3.

После первоначального установления радиосвязи в режиме равномерной программной перестройки рабочих частот на каждом пункте связи производится вычисление весовых коэффициентов частот. При этом микропроцессор 5.3 выдает команды "адрес", "считывание", "диапазон" на запоминающее устройство частот 4.4 через порты 4, 3,2. Из запоминающего устройства частот 4.4 на дешифратор 4.3 выдается код частоты, который поступает на измерительный радиоприемник 4.4, производя его настройку на анализируемую частоту. С высокочастотного выхода и выхода блока опорных частот измерительного радиоприемника 4.1 на анализатор частот 4.2 поступают соответственно уровень эффективного значения напряжения помехи и сигнал "конец настройки". Анализатор частот 4.2 преобразует аналоговый сигнал уровня помехи в цифровой код, который считывается микропроцессором через порт 5. После считывания кода уровня помехи микропроцессор 5.3 производит расчет промежуточного весового коэффициента частоты

а1=0 при uпом i≥uпор

и запись значения промежуточного весового коэффициента частоты в промежуточное запоминающее устройство 5.4 путем выдачи сигналов "запись", "разрешение", "адрес", значение промежуточного весового коэффициента частоты через порты 15-18 соответственно. Далее микропроцессор 5.3 осуществляет расчет и запись в промежуточное запоминающее устройство 5.4 промежуточного весового коэффициента следующей частоты и т.д. для всех анализируемых частот.

После расчета промежуточных весовых коэффициентов частот микропроцессор 5.3 определяет сумму промежуточных весовых коэффициентов всех частот. Если значение найденной суммы равно нулю, то микропроцессор 5.3 обеспечивает формирование режима равномерной ППРЧ путем записи весовых коэффициентов частот a=1/N в соответствующие ячейки запоминающего устройства 5.5 (данная операция подробно описана выше), в свободные ячейки памяти запоминающего устройства 5.5 и корреспондентского запоминающего устройства 5.7 записываются нули. Далее микропроцессором 5.3 осуществляется проверка поступления команды от таймера.

Если сумма промежуточных весовых коэффициентов частот больше нуля, то микропроцессор 5.3 последовательно рассчитывает весовые коэффициенты частоты по формуле (1) и сохраняет рассчитанное значение в соответствующих ячейках запоминающего устройства 5.5 для всех анализируемых частот. В свободные ячейки памяти запоминающего устройства 5.5 и корреспондентского запоминающего устройства 5.7 записываются нули. Таким образом осуществляется вычисление и запись весовых коэффициентов частот.

Далее, если команда от таймера не поступила, то микропроцессор 5.3 повторно производит операцию вычисления весовых коэффициентов частоты для данного диапазона и так до поступления команды от таймера.

При поступлении команды от таймера на каждом пункте связи микропроцессор 5.3 осуществляет отключение входа и выхода радиолинии от кодера 1.8 и декодера 7.5 соответственно путем выдачи сигнала логического нуля через порты 11 и 12 на входы 1 и 2 блока коммутации 6 (11). К кодеру 1.8 и декодеру 7.5 подключаются преобразователи параллельного кода в последовательный 5.6 и последовательного кода в параллельный 5.8 путем выдачи микропроцессором 5.3 сигнала логической единицы через порты 13 и 14 на вход 3 и 4 блока коммутации 6 (11). Таким образом производится подготовка каждого пункта связи к передачи и приему весовых коэффициентов частот.

Далее микропроцессор 5.3 производит подготовку запоминающего устройства 5.5 к считыванию весового коэффициента первой частоты, а корреспондентского запоминающего устройства 5.7 к записи весового коэффициента первой частоты путем выдачи сигналов "считывание", "разрешение", "адрес", "весовой коэффициент частоты" через порты 19-22 к запоминающему устройству 5.5 и сигналов "считывание", "разрешение", "адрес" через порты 24-26 к корреспондентскому запоминающему устройству 5.7. После этого производится выдача сигналов синхронизации на входы управления преобразователей параллельного кода в последовательный 5.6 и последовательного кода в параллельный 5.8 через порт 23 в течение времени, необходимого для передачи и приема весового коэффициента частот (определяется быстродействием запоминающих устройств - до 10 мс). Данная процедура повторяется для всех частот программной перестройки.

После передачи и приема весовых коэффициентов частот микропроцессор 5.3 осуществляет подготовку радиолинии к ведению радиосвязи с учетом вычисленных (принятых) весовых коэффициентов частот. Данный процесс описан выше.

После подготовки радиолинии к ведению радиосвязи с учетом вычисленных (принятых) весовых коэффициентов частот микропроцессор 5.3 формирует команды на вычисление весовых коэффициентов частот другого диапазона программной перестройки и т.д.

В интервалах времени передачи/приема весовых коэффициентов частот на каждом пункте связи осуществляется передача и прием информации к и от корреспондента.

В процессе передачи информации входная информационная последовательность импульсов с выхода "информация" блока коммутации 6 (11) поступает на вход кодера 1.8, который преобразует ее в выходную последовательность импульсов с дополнительной кодовой избыточностью. Данная последовательность закодированных импульсов поступает на вход модулятора 1.5, который преобразует ее в модулированный высокочастотный сигнал на текущей несущей частоте, поступающей на задающий вход модулятора 1.5 с выхода синтезатора частот 1.4. Далее высокочастотный сигнал усиливается усилителем мощности 1.6 и излучается радиопередающей антенной 2 (15). Текущая несущая частота формируется в синтезаторе частот 1.4 в соответствии с управляющими сигналами, поступающими на вход синтезатора 1.4 с выхода устройства управления 1.3, на вход которого поступает преобразованная псевдослучайная последовательность.

Принцип преобразования псевдослучайной последовательности состоит в следующем: случайное число, поступающее с генератора ПСП 1.2 (7.3) сравнивается с коэффициентами сравнения передачи (приема). Диапазону соседних значений коэффициентов сравнения соответствует определенная частота программной перестройки. Находится диапазон значений коэффициентов сравнения, в котором случайное число больше текущего значения, но меньше следующего. Так определяется очередная частота программной перестройки. С выхода преобразователя ПСП 1.7 (7.3) выдается число, соответствующее числу генератора ПСП 1.2 (7.3) при обеспечении равномерного режима ППРЧ.

Данный алгоритм преобразования ПСП основывается на известном методе геометрической интерпретации вероятностей N событий как N участков соответствующей длины, укладывающихся на отрезке единичной длины (см. Вентцель Е.С. "Теория вероятностей". - М.: Государственное издательство физико-математической литературы, 1962, с.300-302). Длину участка в данном случае определяет весовой коэффициент частоты.

В процессе приема информации радиосигнал, принятый антенной 8 (9), после усиления во входном усилителе 7.9 поступает на сигнальный вход смесителя-гетеродина 7.8, который обеспечивает перенос радиосигнала с программной перестройкой рабочей частоты на промежуточную частоту. Со смесителя-гетеродина 7.8 радиосигнал поступает на вход детектора 7.7, который выделяет низкочастотную информацию и подает ее на вход решающего устройства 7.6. В решающем устройстве 7.6 производится восстановление закодированной последовательности импульсов. Далее информационные последовательности импульсов подает на вход декодера 7.5, в котором осуществляется процесс исправления ошибок. После декодера 7.5 информационная последовательность через блок коммутации 6 (11) поступает на выход радиолинии.

В заявляемой радиолинии на каждом пункте связи с использованием блока автоматической регулировки усиления 7.10 реализована автоматическая регулировка усиления по огибающей сигнала, что позволяет осуществлять прием радиосигнала в условиях медленных замираний в радиоканале.

При выборе интервала срабатывания таймера следует руководствоваться интервалом квазистационарности канала радиосвязи (в среднем 10-15 минут см. "Военные системы радиосвязи. Часть I" / В.В.Игнатов, Ю.П.Килимник, И.Н.Никольский и др.; Под ред. В.В.Игнатова. - Л.: ВАС, 1989, с.22-23). Интервал срабатывания таймера следует выбирать меньше времени квазистационарности радиоканала на интервал времени передачи/приема весовых коэффициентов частот.

Положительный эффект от заявляемого устройства по сравнению с радиолинией-прототипом продемонстрируем на следующем примере.

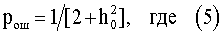

Допустим, что программная перестройка осуществляется по трем частотам с уровнем помех 5 дБ, 10 дБ и 15 дБ соответственно. Пороговое значение уровня помехи - 20 дБ. Уровень эффективного напряжения сигнала 35 дБ. Данные показатели взяты из реальных данных при обеспечении сеанса радиосвязи. Вид модуляции - частотная телеграфия. Радиосвязь осуществляется с использованием механизма отражения радиоволн от ионосферы. С учетом принятых данных весовые коэффициенты частот, рассчитанные по формуле (1), α1=0,42, α2=0,35 и α3=0,23. Вероятность ошибки

h0=uс эфф/uп эфф;

9,98·10-4, 3,142·10-3, 3,142·10-3 на каждой частоте соответственно.

Вероятность ошибки в радиолинии с ППРЧ в данном примере можно рассчитать как (см. Пшеничников А.В., Семисошенко М.А. "Методика расчета помехоустойчивости линии декаметровой связи с ППРЧ." / 58-я научно-техническая конференция. Материалы конференции - СПб: "ЛЭТИ", 2003. С.91-92)

По формуле (6) вероятность ошибки в заявляемой радиолинии и радиолинии-прототипе составляет 3,774·10-3. В радиолинии с равномерной ППРЧ при тех же данных - 4,602·10-3. Выигрыш по вероятности ошибки составляет 1,22.

Предположим также, что через промежуток времени квазистационарности радиоканала (10-15 минут) помеховая обстановка на частотах изменилась и составила 15, 10, 5 дБ соответственно. Значения весовых коэффициентов частот составит α1=0,23, α2=0,35 и α3=0,42. В радиолинии-прототипе не предусмотрено изменение алгоритма перестройки, поэтому вероятность ошибки составит 5,447·10-3. В радиолинии с равномерной ППРЧ значение вероятности ошибки не изменится: 4,602·10-3. В заявляемой радиолинии - 3,774·10-3, т.е. помехоустойчивость радиолинии-прототипа стала хуже, чем в радиолинии с равномерной ППРЧ в 1,18 раза, по сравнению с заявляемой радиолинией - в 1,44 раза.

Далее уровень значения эффективного напряжения помехи на первой частоте превысил пороговое значение и составил 30 дБ. В заявляемой радиолинии первая частота будет исключена из механизма перестройки. Весовые коэффициенты частоты: α1=0, α2=0,45 и α3=0,55. Тогда вероятность ошибки в заявляемой радиолинии составит 1,96·10-3. В радиолинии с равномерной ППРЧ - 7,5·10-3. В радиолинии-прототипе 9,015·10-3. Выигрыш по помехоустойчивости по сравнению с радиолинией-прототипом составил 4,7 раза.

Таким образом, в общем случае при использовании режима адаптации к помехам в радиолинии с ППРЧ приводит к получению выигрыша по помехоустойчивости по сравнению с радиолинией с равномерной ППРЧ

Данный выигрыш, в отличие от радиолинии-прототипа, обеспечивается при изменении помеховой обстановки на частотах, т.е. реализуется сформулированный технический результат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство прерывистой радиосвязи | 1989 |

|

SU1748263A1 |

| Широкополосное приемопередающее устройство | 2016 |

|

RU2628328C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2296420C1 |

| СИСТЕМА РАДИОСВЯЗИ | 2011 |

|

RU2498503C2 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2178237C2 |

| СПОСОБ ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2181527C1 |

| РАДИОСТАНЦИЯ | 2010 |

|

RU2465727C2 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ ФАЗЫ СИГНАЛА | 2017 |

|

RU2646602C1 |

Изобретение относится к области радиотехники и может быть использовано в системах связи с программной перестройкой рабочих частот (ППРЧ), функционирующих в условиях воздействия помех, уровень которых периодически изменяется по частотам программной перестройки. Достигаемым техническим результатом является повышение помехоустойчивости радиолинии с ППРЧ при воздействии нестационарных помех. Для этого в радиолинию с ППРЧ введены блок коммутации, блок формирования весовых коэффициентов частот и блок анализа частот. Благодаря введенным блокам в радиолинии с ППРЧ чаще используются частоты с меньшим уровнем помех, а непригодные частоты исключаются из перестройки. 3 з.п. ф-лы, 9 ил.

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2097923C1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2099886C1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 1999 |

|

RU2157051C1 |

| US 4653068, 24.03.1987 | |||

| US 5361401, 01.11.1994. | |||

Авторы

Даты

2006-03-27—Публикация

2004-10-25—Подача