Изобретение относится к компьютерным системам, основанным на специфических вычислительных моделях с использованием электронных средств.

Известен способ испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей основанного на языках описания аппаратуры (патент США № US 8418012 В2). Способ заключается в том, что получают базовый проект испытываемого электронного устройства на языке описания аппаратуры. Создают математические модели неисправностей для конфигурируемой интегральной схемы испытываемого электронного устройства. Описывают эти неисправности на языке описания аппаратуры. Вносят описанные неисправности в базовый проект особой конфигурируемой интегральной схемы испытываемого устройства. Проводят несколько экспериментов по внесению неисправностей, где каждый эксперимент включает неисправность, по крайней мере, одного сигнала.

Недостатками данного способа являются: невозможность имитации неисправностей устройств, не имеющих в своем составе программируемых логических интегральных схем (ПЛИС), по причине того, что неисправности вносятся в ПЛИС самого испытываемого устройства, при этом в составе испытательного комплекса ПЛИС отсутствует; отсутствие возможности управления включением/выключением неисправностей в моделях без перекомпиляций проекта ПЛИС при помощи программного обеспечения (ПО) высокого уровня; отсутствие в способе описания правил локализации неисправностей; отсутствие описания алгоритмов маршрутизации активации неисправностей, позволяющих повысить полноту контроля.

В рамках заявляемого способа, под термином алгоритм маршрутизации активации неисправностей следует понимать набор и последовательность выполнения операций активации отдельных неисправностей, описанные математически и позволяющие повысить полноту контроля электронной аппаратуры.

В рамках заявляемого способа, под термином набор неисправностей следует понимать совокупность программных модулей на языках описания аппаратуры, каждый из которых реализует функционирование испытательной аппаратуры в режиме наличия одной неисправности. Данные модули могут содержаться в составе программной библиотеки, либо в отдельных файлах, не входящих в библиотеку.

Известен способ испытаний электронной аппаратуры (патент РФ №2549523). Способ заключается в том, что на языке описания аппаратуры создают два проекта модели электронного устройства: с неисправностями и исправный; затем проводят испытания с использованием обоих проектов; сравнивают результаты испытаний от исправной и неисправной моделей на каждой неисправности из заданного массива, если в процессе испытаний исправной модели неисправностей не обнаруживают, а при испытаниях неисправной обнаруживают весь массив внесенных неисправностей, то испытываемую электронную аппаратуру или ее управляющее ПО считают прошедшими испытания. При этом в состав испытательного комплекса входит ПЛИС для вышеописанного моделирования электронных устройств.

Недостатками данного способа являются: отсутствие описания правил локализации неисправностей; отсутствие описания алгоритмов маршрутизации активации неисправностей, позволяющих повысить полноту контроля электронной аппаратуры.

Наиболее близким (прототипом) является способ испытаний электронной аппаратуры (патент РФ №2661535).

Недостатком данного способа является отсутствие описания алгоритмов маршрутизации активации неисправностей, позволяющих повысить полноту контроля.

Для заявленного способа выявлены основные общие с прототипом существенные признаки: на языке описания аппаратуры создают два проекта модели электронного устройства - с неисправностями и исправный; затем проводят испытания с использованием обоих проектов; сравнивают результаты испытаний от исправной и неисправной моделей на каждой неисправности из заданного массива, если в процессе испытаний исправной модели неисправностей не обнаруживают, а при испытаниях неисправной обнаруживают весь массив внесенных неисправностей, то испытываемую электронную аппаратуру или ее управляющее ПО считают прошедшими испытания; при этом в состав испытательного комплекса входит ПЛИС для вышеописанного моделирования электронных устройств.

Технической проблемой прототипа является недостаточный уровень полноты контроля, ввиду отсутствия описания алгоритмов маршрутизации активации неисправностей, которые позволили бы в автоматическом режиме определять все существующие маршруты активации моделируемых неисправностей и проходить их.

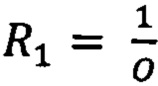

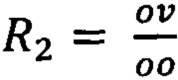

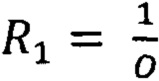

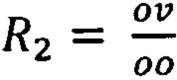

Поставленная техническая проблема изобретения решается тем, что в проекты ПЛИС, реализованные на языках описания аппаратуры, намеренно вносят модели неисправностей; затем проводят испытания с целью оценки вероятности обнаружения внесенных моделей неисправностей испытываемой аппаратурой или ПО; на языке описания аппаратуры создают проект исправной модели электронного устройства, имитирующей поведение каналов ввода-вывода объекта испытаний (электронного устройства, разрабатываемого для конечного потребителя); записывают получившийся проект модели в ПЛИС устройства имитации неисправностей, встроенного в устройство управления процессом испытаний и содержащего интерфейсные каналы ввода-вывода; проводят испытания на этой модели; результаты испытаний заносят в протокол при помощи устройства управления процессом испытаний; разрабатывают номенклатуру неисправностей необходимых для проведения испытаний и описывают каждую из неисправностей входящих в номенклатуру на языках описания аппаратуры; создают проект модели объекта испытаний с неисправностями, причем предусматривают возможность их включения/выключения в процессе испытаний без перекомпиляции проекта, при помощи управляющего ПО высокого уровня; записывают получившийся проект модели в ПЛИС устройства имитации неисправностей, встроенного в устройство управления процессом испытаний; ПО высокого уровня, активирующее и дезактивирующее любые комбинации неисправностей без перекомпиляции проекта ПЛИС разрабатывают на основе следующего далее алгоритма маршрутизации активации неисправностей; каждую из неисправностей, входящих в номенклатуру неисправностей, необходимую для проведения испытаний электронного устройства, представляют в виде вершины ориентированного графа, вершины соединяют дугами, которые выражают строго заданную последовательность активации неисправностей, разработанную на основе исторических данных об их появлении в ходе эксплуатации испытываемого устройства конечным потребителем или в процессе ранее проведенных испытаний, а также результатов теоретического анализа возможных исходов гипотетических ситуаций в рамках определенных входных данных, которыми являются принятые в номенклатуру неисправностей неисправности; для сформированного ориентированного графа составляют матрицу смежности, в которой нули - это отсутствие дуги между вершинами, единицы - наличие дуги между вершинами; на основе матрицы смежности составляют матрицу маршрутов, путем замены всех единиц уникальными для каждого столбца матрицы буквами или любыми другими уникальными знаками; возводят получившуюся матрицу маршрутов в степень соответствующую длине искомых маршрутов, взятой из технического задания на испытания, что позволяет вычислить все вершины, которые необходимо последовательно активировать в процессе испытаний для достижения абсолютной полноты контроля в рамках заданного ограничения -определенной, например, в техническом задании на испытания длины маршрутов; далее, в соответствие с результатами проведенных по вышеописанному алгоритму расчетов, при помощи устройства управления процессом испытаний, формируют массив управляющих воздействий поочередно включающих неисправности, реализованные в модели и указанные в массиве; проводят испытания на этой модели; результаты испытаний заносят в протокол при помощи устройства управления процессом испытаний; при помощи устройства управления испытаниями, сравнивают результаты испытаний от исправной и неисправной моделей на каждой неисправности из заданного массива, если в процессе испытаний исправной модели неисправностей не обнаруживают, а при испытаниях неисправной, обнаруживают весь массив внесенных неисправностей, то испытываемую аппаратуру или ПО считают прошедшими испытания; если в процессе испытаний исправной модели обнаруживают неисправности, то определяют коэффициент первого этапа  , где о - количество обнаруженных неисправностей; если в процессе испытаний неисправной модели обнаруживают не все неисправности, то определяют коэффициент второго этапа

, где о - количество обнаруженных неисправностей; если в процессе испытаний неисправной модели обнаруживают не все неисправности, то определяют коэффициент второго этапа  , где oν - количество внесенных в модель неисправностей, оо - количество обнаруженных неисправностей.

, где oν - количество внесенных в модель неисправностей, оо - количество обнаруженных неисправностей.

Применение вышеописанного алгоритма маршрутизации активации неисправностей позволяет автоматически вычислить все возможные маршруты активации неисправностей в рамках любого заданного ограничения и пройти их в ходе испытаний, что повышает полноту контроля испытаний.

Заявка поясняется изображениями:

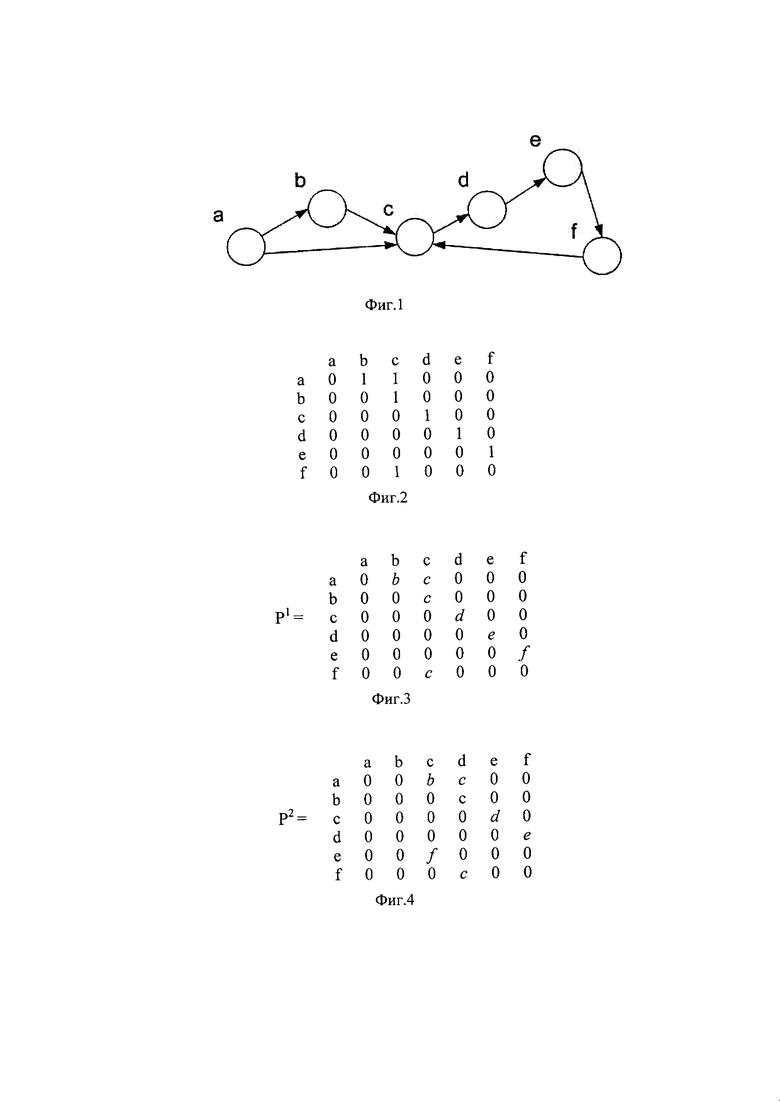

Фиг. 1 - изображение графа составленного на основе исторических данных о фактически произошедших неисправностях в ходе штатной эксплуатации конечным потребителем электронного устройства; шесть вершин графа соответствуют произошедшим неисправностям, дуги соответствуют последовательности появления неисправностей в нештатной ситуации.

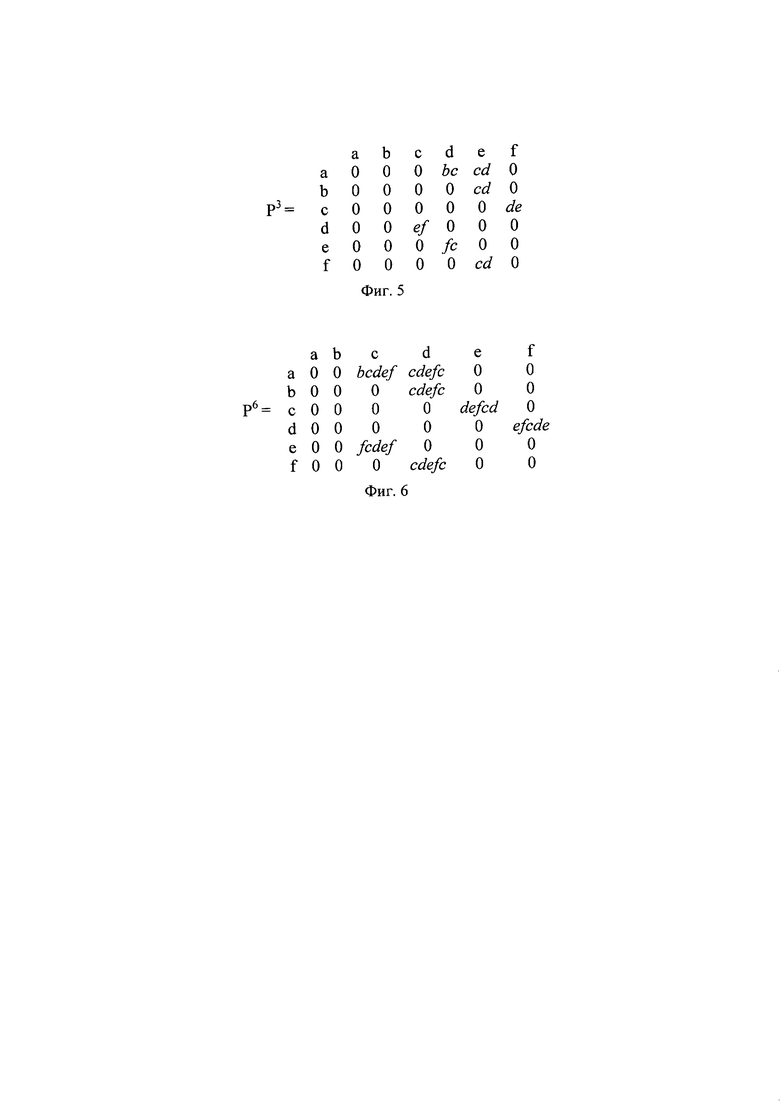

Фиг. 2 - матрица смежности, составленная на основе графа изображенного на фигуре 1; если между вершинами имеется дуга, то на пересечении этих двух вершин в матрице смежности выставлена 1, если дуга отсутствует, то 0.

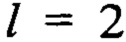

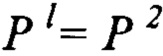

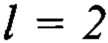

Фиг. 3-матрица маршрутов Р, составленная на основе матрицы смежности изображенной на фигуре 2, путем замены всех единиц буквами, одноименными с названиями столбцов; матрица на данной фигуре отображает маршруты длинной в 1 вершину, т.е  .

.

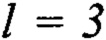

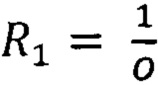

Фиг. 4 - матрица маршрутов Р для маршрутов длинной  , рассчитанная по формуле

, рассчитанная по формуле  .

.

Фиг. 5 - матрица маршрутов Р для маршрутов длинной  , рассчитанная по формуле

, рассчитанная по формуле  .

.

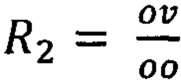

Фиг. 6 - матрица маршрутов Р для маршрутов длинной  , рассчитанная по формуле

, рассчитанная по формуле  .

.

Способ осуществляют следующим образом.

На языке описания аппаратуры создают проект исправной модели электронного устройства, имитирующей поведение каналов ввода-вывода объекта испытаний (электронного устройства или его составных частей), связывающих устройство имитации неисправностей с устройством управления процессом испытаний, содержащим устройства контроля. Записывают получившийся проект в ПЛИС устройства имитации неисправностей, встроенного в устройство управления процессом испытаний и содержащего интерфейсные каналы ввода-вывода. Реализация модели на ПЛИС позволяет исключить моделирование временных промежутков, так как современные ПЛИС поддерживают такой же уровень скоростей, как и аппаратура, создаваемая для конечного потребителя, имеющая исключительно аппаратную реализацию. В то же время на ПЛИС можно реализовывать любые устройства, требуемые для испытаний, путем простого перепрограммирования, что занимает гораздо меньше времени, чем аппаратное макетирование, которое требует приобретения натуральной компонентной базы электроники и сложного процесса ее монтажа на печатные платы. Далее проводят испытания на этой модели. Результаты испытаний автоматически заносят в протокол устройством управления процессом испытаний. На языке описания аппаратуры создают проект модели электронной аппаратуры с неисправностями, причем предусматривают возможность их включения/выключения в процессе испытаний, при помощи управляющего ПО высокого уровня, что сильно сокращает количество перекомпиляций проектов ПЛИС. Например, необходимо имитировать 10 различных неисправностей, причем ввести их в процесс испытаний во всех возможных комбинациях. На каждую комбинацию потребуется переделать проект ПЛИС и провести его перекомпиляцию. Допустим, что наличие неисправности это 1, а отсутствие 0, это значит, что количество перекомпиляций (исключая исправную модель) составит 1023 (1111111111двоичная=1024десятичная)- В предлагаемом способе в проекте ПЛИС модели предусматривают возможность включения/выключения каждой отдельной неисправности путем введения программируемой логической структуры «ЕСЛИ», которая управляется ПО высокого уровня формированием массива управляющих воздействии включения/выключения. Далее записывают получившийся проект в ПЛИС того же самого устройства имитации неисправностей, встроенного в устройство управления процессом испытаний. При помощи устройства управления процессом испытаний формируют массив управляющих воздействий автоматически поочередно включающих неисправности, реализованные в модели и указанные в массиве. Проводят испытания на этой модели. Результаты испытаний автоматически заносят в протокол устройством управления процессом испытаний. При помощи устройства управления процессом испытаний, сравнивают результаты испытаний от исправной и неисправной моделей на каждой неисправности из заданного массива. Если в процессе испытаний исправной модели неисправностей не обнаружено, а также обнаружен весь массив внесенных неисправностей в неисправную модель, то аппаратура или ее управляющее ПО считаются прошедшими испытания. Если в процессе испытаний исправной модели обнаруживают неисправности, то определяют коэффициент первого этапа  , где о - количество обнаруженных неисправностей; если в процессе испытаний неисправной модели обнаруживают не все неисправности, то определяют коэффициент второго этапа

, где о - количество обнаруженных неисправностей; если в процессе испытаний неисправной модели обнаруживают не все неисправности, то определяют коэффициент второго этапа  , где oν - количество внесенных в модель неисправностей, оо - количество обнаруженных неисправностей.

, где oν - количество внесенных в модель неисправностей, оо - количество обнаруженных неисправностей.

Описанный способ осуществим также с реализацией исправной и неисправной моделей в двух отдельных одинаковых устройствах. В этом случае испытания исправной и неисправной моделей можно проводить одновременно, что дополнительно сократит время испытаний.

Для повышения полноты контроля, в ходе испытаний, предлагается алгоритм маршрутизации активации неисправностей, заключающийся в следующем: каждую из неисправностей, входящих в номенклатуру неисправностей, необходимую для проведения испытаний электронного устройства, представляют в виде вершины ориентированного графа, вершины соединяют дугами, которые выражают строго заданную последовательность активации неисправностей, разработанную на основе исторических данных об их появлении в ходе эксплуатации испытываемого устройства конечным потребителем или в процессе ранее проведенных испытаний, а также результатов теоретического анализа возможных исходов гипотетических ситуаций в рамках определенных входных данных, которыми являются принятые в номенклатуру неисправностей неисправности; для сформированного ориентированного графа составляют матрицу смежности, в которой нули - это отсутствие дуги между вершинами, единицы - наличие дуги между вершинами; на основе матрицы смежности составляют матрицу маршрутов, путем замены всех единиц уникальными для каждого столбца матрицы буквами или любыми другими уникальными знаками; возводят получившуюся матрицу маршрутов в степень соответствующую длине искомых маршрутов, взятой из технического задания на испытания, что позволяет вычислить все вершины, которые необходимо последовательно активировать в процессе испытаний для достижения абсолютной полноты контроля в рамках заданного ограничения - определенной в техническом задании на испытания длины маршрутов; далее, в соответствие с результатами проведенных по вышеописанному алгоритму расчетов, при помощи устройства управления процессом испытаний, формируют массив управляющих воздействий поочередно включающих неисправности, реализованные в модели и указанные в массиве.

Рассмотрим предложенный алгоритм маршрутизации активации неисправностей на примере графа изображенного на фигуре 1. Граф имеет 6 вершин, а значит, описывает 6 неисправностей. Дуги графа выражают последовательность активации неисправностей, рассчитанную в результате анализа, например, исторических данных, о ситуации, произошедшей в действительности, в ходе штатной эксплуатации, например, конечным потребителем устройства. Т.е при появлении неисправности а, в ходе штатной эксплуатации, обязательно появятся неисправности b или/и с, при появлении неисправности с последовательно появятся неисправности d, е и f, что спровоцирует факторы, которые повторно приведут к появлению неисправности с и.т.д. Для дальнейших расчетов составляют матрицу смежности для предложенного графа неисправностей (фигура 2). Если из вершины в вершину имеется дуга, то в пересечении столбца и строки выставляют 1, если дуги нет, то 0. На основе матрицы смежности составляют матрицу маршрутов Р, путем замены всех единиц уникальными для каждого столбца матрицы одноименными буквами или любыми другими уникальными знаками, (фигура 3). Возводят получившуюся матрицу маршрутов в степень соответствующую длине искомых маршрутов, взятой из технического задания на испытания, что позволяет вычислить все маршруты, которые необходимо последовательно активировать в процессе испытаний для достижения абсолютной полноты контроля в рамках заданного ограничения - определенной в техническом задании на испытания длины маршрутов. Т.е маршруты длины  рассчитывают по формуле

рассчитывают по формуле  . На фигурах с 4 по 6 приведены расчеты для разных

. На фигурах с 4 по 6 приведены расчеты для разных  :

:  - фигура 4,

- фигура 4,  - фигура 5,

- фигура 5,  - фигура 6. Далее, в соответствие с результатами проведенных по вышеописанному алгоритму расчетов, при помощи устройства управления процессом испытаний, формируют массив управляющих воздействий поочередно включающих неисправности, реализованные в модели и указанные в массиве.

- фигура 6. Далее, в соответствие с результатами проведенных по вышеописанному алгоритму расчетов, при помощи устройства управления процессом испытаний, формируют массив управляющих воздействий поочередно включающих неисправности, реализованные в модели и указанные в массиве.

В качестве доказательства повышения полноты контроля заявляемым способом испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей с маршрутизацией приведем пример, когда предлагаемый алгоритм маршрутизации не используется. Тогда, в виду человеческого фактора или недостатков примененного другого алгоритма расчета маршрутов некоторые маршруты могут быть не рассчитаны и не учтены для их активации в ПЛИС в процессе испытательных прогонов. Например, для приведенного графа (фигура 1) общее количество маршрутов длины 6 составляет 7 штук, т.е {abcdefc}, {acdefcd}, {bcdefcd}, {fcdefcd}, {cdefcde}, {defcdef}, {efcdefc}. Предложенный, в рамках заявляемого способа испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей с маршрутизацией, алгоритм позволил рассчитать все 7 маршрутов, т.е все существующие маршруты длиной 6, когда без его применения было получено, например, 5 маршрутов длиной 6 вершин, тогда полнота контроля  , где λк - количество проконтролированных в ходе испытательных прогонов активированных маршрутов длиной 6 вершин в модели на ПЛИС, рассчитанных по алгоритму маршрутизации; λ0 - суммарное наличие маршрутов длиной 6 вершин в модели на ПЛИС. Тогда для способа испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей с маршрутизацией

, где λк - количество проконтролированных в ходе испытательных прогонов активированных маршрутов длиной 6 вершин в модели на ПЛИС, рассчитанных по алгоритму маршрутизации; λ0 - суммарное наличие маршрутов длиной 6 вершин в модели на ПЛИС. Тогда для способа испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей с маршрутизацией  , для способа противопоставляемого в данном примере

, для способа противопоставляемого в данном примере  . Таким образом, в рамках примера, полнота контроля повышена на 29 процентов. Также следует отметить, что в обнаруженных, в ходе анализа уровня техники, аналогах отсутствует какое либо описание алгоритмов расчета маршрутов активации неисправностей в принципе, что и вынесено в отличительную часть формулы заявляемого изобретения.

. Таким образом, в рамках примера, полнота контроля повышена на 29 процентов. Также следует отметить, что в обнаруженных, в ходе анализа уровня техники, аналогах отсутствует какое либо описание алгоритмов расчета маршрутов активации неисправностей в принципе, что и вынесено в отличительную часть формулы заявляемого изобретения.

Необходимо отметить, что, в рамках предлагаемого способа испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей с маршрутизацией, модели на ПЛИС функционируют как «Черный ящик», лишь функционально имитируя поведение каналов ввода-вывода электронных устройств или их частей, при этом ставится задачей максимально адекватно воспроизвести входные и выходные сигналы по временным параметрам, для обеспечения взаимодействия с внешней аппаратурой, подключенной к данным каналам в процессе испытаний. Внутренняя реализация моделей на ПЛИС имеет лишь отдаленную схожесть с внутренней реализацией имитируемого прибора.

Устройство управления процессом испытаний реализовано в крейт-шасси, управляемом крейт-контроллером, к которому подключаются манипуляторы (мышь и клавиатура). Данные о процессе испытаний выводятся на монитор. Управление крейт-контроллером обеспечивает операционная система и пакет прикладных программ. Также при помощи пакета прикладных программ задается массив неисправностей для неисправной модели. Данные, полученные в процессе испытаний, протоколируются, и результаты сравниваются. Вычисляются коэффициенты покрытия неисправностей проведенных испытаний (R1 и R2). Устройство имитации неисправностей в модульном исполнении, содержащее ПЛИС и каналы ввода-вывода для соединения с устройством управления, встраивают в крейт-шасси устройства управления. При помощи вышеописанного пакета прикладных программ, реализованных на основе алгоритмов маршрутизации активации неисправностей, происходит автоматический перебор всех возможных комбинаций неисправностей в определенной последовательности, что позволяет достичь максимальной полноты контроля в рамках заданного в техническом задании ограничения. Для каждой комбинации неисправностей автоматически поочередно проводится испытательный прогон. Результаты автоматически анализируются и заносятся в протокол, содержащийся в памяти крейт-контроллера устройства управления.

Таким образом, заявляемый способ, содержащий алгоритмы маршрутизации активации неисправностей, позволяет в автоматическом режиме определять, в какой последовательности необходимо вносить моделируемые неисправности в процессе испытаний для полного перебора всех существующих комбинаций неисправностей, что повышает полноту контроля объектов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОПРЕДЕЛЕНИЯ ДОСТАТОЧНОСТИ КОНТРОЛЯ ЭЛЕКТРОННОЙ АППАРАТУРЫ В РЕЖИМЕ ВНЕСЕНИЯ НЕИСПРАВНОСТЕЙ | 2019 |

|

RU2717630C1 |

| СПОСОБ РАЗРАБОТКИ БОРТОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ КОСМИЧЕСКИХ АППАРАТОВ НА ОСНОВЕ ИСПЫТАНИЙ С ПРИМЕНЕНИЕМ ЦЕЛЕВЫХ БЛОКОВ ОПИСАНИЯ АППАРАТУРЫ | 2024 |

|

RU2838133C1 |

| СПОСОБ ИСПЫТАНИЙ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ СИСТЕМ УПРАВЛЕНИЯ КОСМИЧЕСКИХ АППАРАТОВ | 2021 |

|

RU2764837C1 |

| СПОСОБ МУТАЦИОННОГО ТЕСТИРОВАНИЯ ЭЛЕКТРОННОЙ АППАРАТУРЫ И ЕЕ УПРАВЛЯЮЩЕГО ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ С ОПРЕДЕЛЕНИЕМ ЛОКАЛИЗАЦИИ МУТАЦИЙ | 2017 |

|

RU2661535C1 |

| СПОСОБ МУТАЦИОННОГО ТЕСТИРОВАНИЯ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ И ЕЕ УПРАВЛЯЮЩЕГО ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ | 2014 |

|

RU2549523C1 |

| СПОСОБ РАЗРАБОТКИ УСТРОЙСТВ ИНТЕРФЕЙСА SERIAL PERIPHERAL INTERFACE | 2024 |

|

RU2833286C1 |

| Способ моделирования виртуальной сети | 2020 |

|

RU2741262C1 |

| Способ моделирования виртуальных сетей в условиях деструктивных программных воздействий | 2018 |

|

RU2701994C1 |

| УСТРОЙСТВО ПЛАНИРОВАНИЯ ТОПОЛОГИИ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ | 2012 |

|

RU2530275C2 |

| СПОСОБ МОДЕЛИРОВАНИЯ СЕТИ СВЯЗИ С ПАМЯТЬЮ | 2020 |

|

RU2734503C1 |

Изобретение относится к способу испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей с маршрутизацией. Техническим результатом изобретения является повышение точности контроля при испытаниях электронной аппаратурой. Способ содержит операции: при помощи устройства управления процессом испытаний создают проект исправной и неисправной моделей электронного устройства, имитирующей поведение его каналов ввода-вывода, записывают модели в программируемую логическую интегральную схему (ПЛИС) устройства имитации неисправностей, формируют массив управляющих воздействий, поочередно включающих неисправности, реализованные в модели и указанные в массиве, сравнивают результаты испытаний от исправной и неисправной моделей, если в процессе испытаний исправной модели неисправностей не обнаруживают, а при испытаниях неисправной обнаруживают весь массив внесенных неисправностей, то электронную аппаратуру и ее управляющее ПО считают прошедшими испытания. 1 з.п. ф-лы, 6 ил.

1. Способ испытаний электронной аппаратуры на основе аппаратно-программного внесения неисправностей с маршрутизацией, при реализации которого в проекты программируемых логических интегральных схем (ПЛИС), реализованные на языках описания аппаратуры, намеренно вносят модели неисправностей, затем проводят испытания с целью оценки вероятности обнаружения испытываемой аппаратурой или ее управляющим ПО внесенных моделей неисправностей, заключающийся в том, что на языке описания аппаратуры создают проект исправной модели электронного устройства, имитирующей поведение его каналов ввода-вывода; записывают получившийся проект исправной модели в ПЛИС устройства имитации неисправностей содержащего интерфейсные каналы ввода-вывода; проводят испытания исправной модели; результаты испытаний заносят в протокол при помощи устройства управления процессом испытаний (УУПИ); на языках описания аппаратуры создают проект модели электронного устройства с неисправностями (ПМСН), причем предусматривают возможность их включения/выключения без перекомпиляции проекта в процессе испытаний при помощи управляющего программного обеспечения высокого уровня; записывают получившийся ПМСН в ПЛИС устройства имитации неисправностей; при помощи УУПИ формируют массив управляющих воздействий, поочередно включающих неисправности, реализованные в ПМСН и указанные в массиве; проводят такие же испытания на ПМСН, как и в предыдущем случае с исправной моделью; результаты испытаний заносят в протокол при помощи УУПИ; при помощи УУПИ сравнивают результаты испытаний от исправной и неисправной моделей на каждой неисправности из заданного массива, если в процессе испытаний исправной модели неисправностей не обнаруживают, а при испытаниях неисправной обнаруживают весь массив внесенных неисправностей, то испытываемую электронную аппаратуру или ее управляющее ПО считают прошедшими испытания; если в процессе испытаний исправной модели обнаруживают неисправности, то определяют коэффициент первого этапа  , где о - количество обнаруженных неисправностей; если в процессе испытаний неисправной модели обнаруживают не все неисправности, то определяют коэффициент второго этапа

, где о - количество обнаруженных неисправностей; если в процессе испытаний неисправной модели обнаруживают не все неисправности, то определяют коэффициент второго этапа  , где oν - количество внесенных в модель неисправностей, оо - количество обнаруженных неисправностей, отличающийся тем, что каждую из неисправностей, входящих в номенклатуру неисправностей, необходимую для проведения испытаний электронного устройства, представляют в виде вершины ориентированного графа, вершины соединяют дугами, которые выражают строго заданную последовательность активации неисправностей; для сформированного ориентированного графа составляют матрицу смежности, в которой нули - это отсутствие дуги между вершинами, единицы - наличие дуги между вершинами; на основе матрицы смежности составляют матрицу маршрутов путем замены всех единиц уникальными для каждого столбца матрицы буквами или любыми другими уникальными символами; возводят получившуюся матрицу маршрутов в степень, соответствующую длине искомых маршрутов, что позволяет вычислить все вершины, которые необходимо последовательно активировать в процессе испытаний для достижения абсолютной полноты контроля в рамках заданного ограничения - определенной длины маршрутов; далее в соответствии с результатами проведенных по вышеописанному алгоритму расчетов при помощи устройства управления процессом испытаний формируют массив управляющих воздействий, поочередно включающих неисправности, реализованные в модели и указанные в массиве.

, где oν - количество внесенных в модель неисправностей, оо - количество обнаруженных неисправностей, отличающийся тем, что каждую из неисправностей, входящих в номенклатуру неисправностей, необходимую для проведения испытаний электронного устройства, представляют в виде вершины ориентированного графа, вершины соединяют дугами, которые выражают строго заданную последовательность активации неисправностей; для сформированного ориентированного графа составляют матрицу смежности, в которой нули - это отсутствие дуги между вершинами, единицы - наличие дуги между вершинами; на основе матрицы смежности составляют матрицу маршрутов путем замены всех единиц уникальными для каждого столбца матрицы буквами или любыми другими уникальными символами; возводят получившуюся матрицу маршрутов в степень, соответствующую длине искомых маршрутов, что позволяет вычислить все вершины, которые необходимо последовательно активировать в процессе испытаний для достижения абсолютной полноты контроля в рамках заданного ограничения - определенной длины маршрутов; далее в соответствии с результатами проведенных по вышеописанному алгоритму расчетов при помощи устройства управления процессом испытаний формируют массив управляющих воздействий, поочередно включающих неисправности, реализованные в модели и указанные в массиве.

2. Способ по п. 1, отличающийся тем, что испытания исправной модели и модели с неисправностями проводят одновременно.

| СПОСОБ МУТАЦИОННОГО ТЕСТИРОВАНИЯ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ И ЕЕ УПРАВЛЯЮЩЕГО ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ | 2014 |

|

RU2549523C1 |

| СПОСОБ МУТАЦИОННОГО ТЕСТИРОВАНИЯ ЭЛЕКТРОННОЙ АППАРАТУРЫ И ЕЕ УПРАВЛЯЮЩЕГО ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ С ОПРЕДЕЛЕНИЕМ ЛОКАЛИЗАЦИИ МУТАЦИЙ | 2017 |

|

RU2661535C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПРОВЕДЕНИЯ ИСПЫТАНИЙ РАДИОТЕХНИЧЕСКИХ ИЗДЕЛИЙ | 2015 |

|

RU2601534C1 |

| US 0008418012 B2, 09.04.2013 | |||

| Фармацевтическое средство растительного происхождения в виде спрея | 2022 |

|

RU2801872C1 |

Авторы

Даты

2020-07-06—Публикация

2019-02-19—Подача