Уровень техники

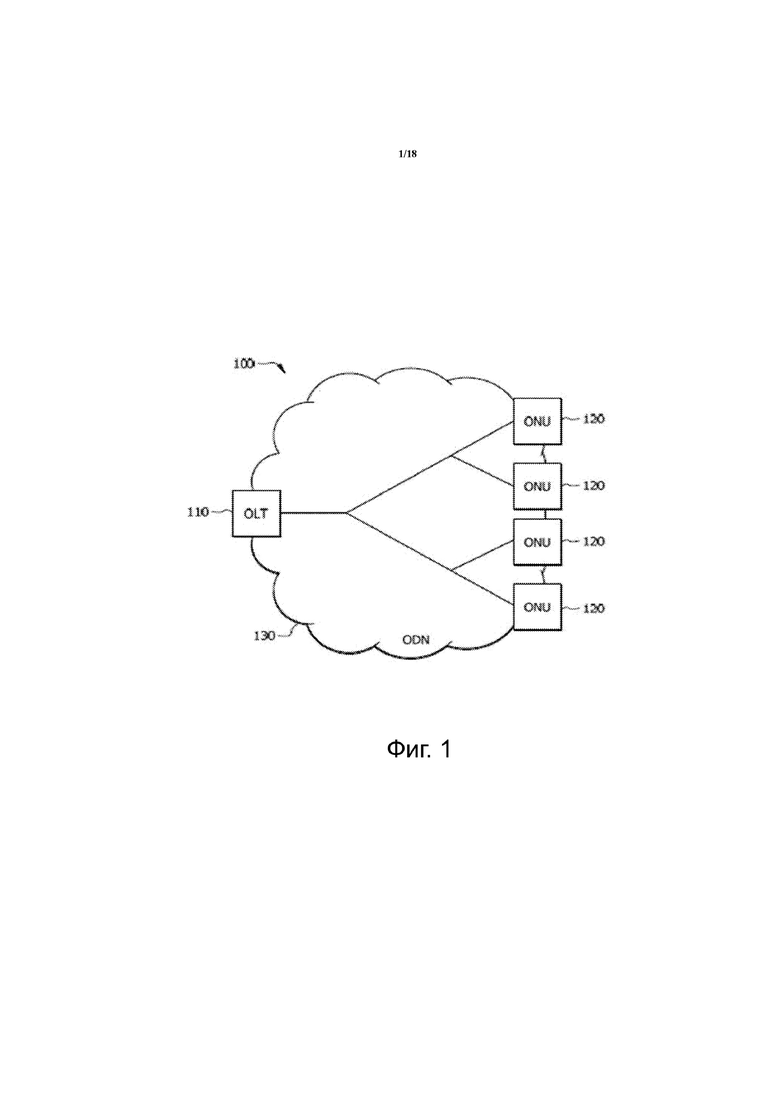

Пассивная оптическая сеть (passive optical network, PON) является системой предоставления сетевого доступа на конечном участке сети связи. PON является сетью типа P2MP, содержащей аппаратуру подключения к оптической линии связи (optical line terminal, OLT) в центральном офисе (central office, CO), к оптической распределительной сети (optical distribution network, ODN) и к блоку оптической связи (optical network unit, ONU) в помещениях пользователя. PON может также содержать удаленные узлы (remote network, RN), расположенные между OLT и ONU, например, на конце маршрута, где многочисленные пользователи присутствуют постоянно.

В последние годы в мире были разработаны PON с мультиплексированием с временным разделением каналов (PON с time-division multiplexing, TDM PON), такие как гигабитная PON (gigabit PON, GPON) и Ethernet PON (EPON), для мультимедийных применений. В TDM PON общая емкость используется совместно многочисленными пользователями, использующими схему TDMA, и, как результат, средняя полоса пропускания для каждого пользователя может соответствовать скорости передачи ниже 100 Мб/с. EPON используют WDM и обеспечивают скорости передачи до 10 Гб/с. Благодаря растущим потребностям пользователей, от EPON следующего поколения может потребоваться реализовывать скорость 100 Гб/с.

Будущие применения содержат четырехканальные сети WDM с битовыми скоростями 25 Гб/с в каждом волновом канале и сети WDM с меньшим количеством каналов с даже более высокими битовыми скоростями в каждом одиночном канале. По мере того, как потребность в битовых скоростях продолжает расти, ограничения по ширине полосы, подразумевающие эффективное использование существующих устройств, могут в результате привести к значительной межсимвольной помехе (inter-symbol interference, ISI). ISI является значительной проблемой для CDR в высокоскоростных PON. В частности, для высокоскоростных передач данных в пакетном режиме по восходящему каналу в сетях PON скорость конвергенции и качество CDR могут значительно влиять на качество передачи данных.

Сущность изобретения

В одном из вариантов осуществления раскрытие содержит устройство, содержащее: оптико-электрический (optical-to-electrical, ОЕ) компонент, выполненный с возможностью преобразования оптического сигнала в первом формате модуляции в аналоговый электрический сигнал; аналого-цифровой преобразователь (analog-to-digital converter, ADC), связанный с OE-компонентом и выполненный с возможностью преобразования аналогового электрического сигнала в первый цифровой сигнал; и подсистему CDR, связанную с ОЕ-компонентом и выполненную с возможностью выравнивания первого цифрового сигнала во второй цифровой сигнал во втором формате модуляции, причем второй формат модуляции имеет больше уровней, чем первый формат модуляции; и выполнения CDR для второго цифрового сигнала. В некоторых вариантах осуществления устройство дополнительно содержит компонент PR-MLSE, связанный с подсистемой CDR и выполненный с возможностью выравнивания второго цифрового сигнала в третий электрический сигнал в первом формате модуляции; компонент PR-MLSE дополнительно выполнен с возможностью выравнивания второго цифрового сигнала, используя PR-MLSE; подсистема CDR содержит выравниватель прямого действия (feed-forward equalizer, FFE), компонент принятия решения, вычитающее устройство и устройство обновления весов ответвлений, которые образуют контур обратной связи и в которой компонент PR-MLSE находится вне контура обратной связи; первый формат модуляции имеет два уровня для сигнала (non-return-to-zero, NRZ), а второй формат модуляции имеет три уровня; первый формат модуляции имеет четыре уровня для сигнала PAM4, а второй формат модуляции имеет семь уровней; подсистема CDR содержит FFE, выполненный с возможностью осуществления CDR для корректирования фазы и осуществления выравнивания для компенсации ISI; FFE дополнительно выполнен с возможностью адаптивного слежения за смещением частоты и джиттером; подсистема CDR дополнительно выполнена с возможностью осуществления выравнивания до тех пор, пока среднеквадратичная ошибка (mean square error, MSE) выровненного сигнала не станет ниже заданного порога; устройство является устройством OLT, в котором аналоговый электрический сигнал является сигналом в пакетном режиме; OE-компонент является PD, TIA или сочетанием PD и TIA.

В другом варианте осуществления раскрытие включает в себя устройство, содержащее: подсистему CDR, содержащую: FFE; компонент принятия решения, связанный с FFE; вычитающее устройство, связанное с FFE и компонентом принятия решения; и устройство обновления весов ответвлений, связанное с вычитающим устройством и FFE; и компонент PR-MLSE, связанный с подсистемой CDR. В некоторых вариантах осуществления устройство дополнительно содержит ADC, связанный с подсистемой CDR; устройство дополнительно содержит генератор, управляемый напряжением (voltage-controlled oscillator, VCO), связанный с ADC; устройство дополнительно содержит TIA, связанный с ADC; устройство дополнительно содержит фотодиод (photodiode, PD), связанный с TIA; устройство дополнительно содержит декодер, связанный с компонентом PR-MLSE, связанным с компонентом PR-MLSE.

В еще одном другом варианте осуществления раскрытие содержит способ, содержащий этапы, на которых: преобразуют оптический сигнал в первом формате модуляции в аналоговый электрический сигнал; преобразуют аналоговый электрический сигнал в первый цифровой сигнал; выравнивают первый цифровой сигнал во второй цифровой сигнал со вторым форматом модуляции, причем второй формат модуляции имеет больше уровней, чем первый формат модуляции; и выполняют CDR для второго цифрового сигнала. В некоторых вариантах осуществления способ дополнительно содержит выравнивание второго цифрового сигнала в третий электрический сигнал в первом формате модуляции, используя PR-MLSE; способ дополнительно содержит выполнение выравнивания до тех пор, пока MSE выровненного сигнала не станет ниже заданного порога.

Для ясности, любой из описанных выше вариантов осуществления может объединяться с любым одним или более другими описанными выше вариантами осуществления, чтобы создать новый вариант осуществления, попадающий в рамки объема настоящего раскрытия.

Эти и другие признаки будут более понятны из последующего подробного описания, рассматриваемого в сочетании с сопроводительными чертежами и формулой изобретения.

Краткое описание чертежей

Для более полного понимания настоящего раскрытия, здесь делается ссылка на последующее краткое описание, рассматриваемое в сочетании с сопроводительными чертежами, на которых схожие ссылочные позиции представляют схожие детали.

Фиг. 1 - схематичное представление PON.

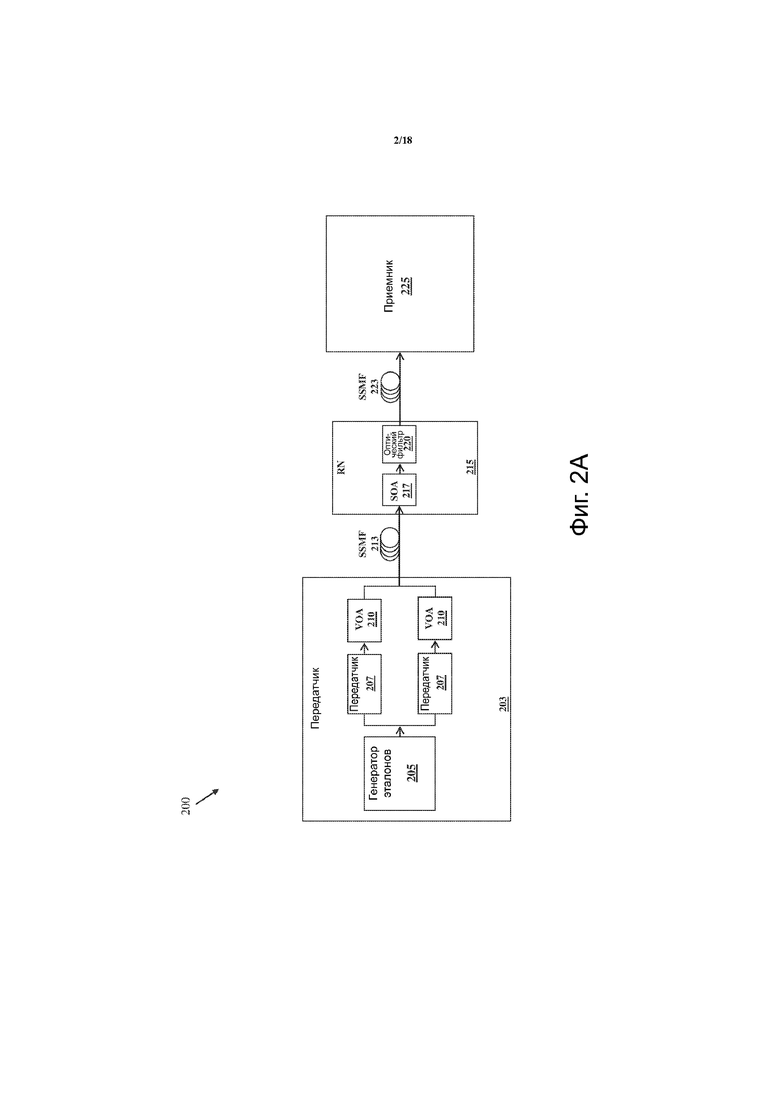

Фиг. 2A - схематичное представление системы передачи данных.

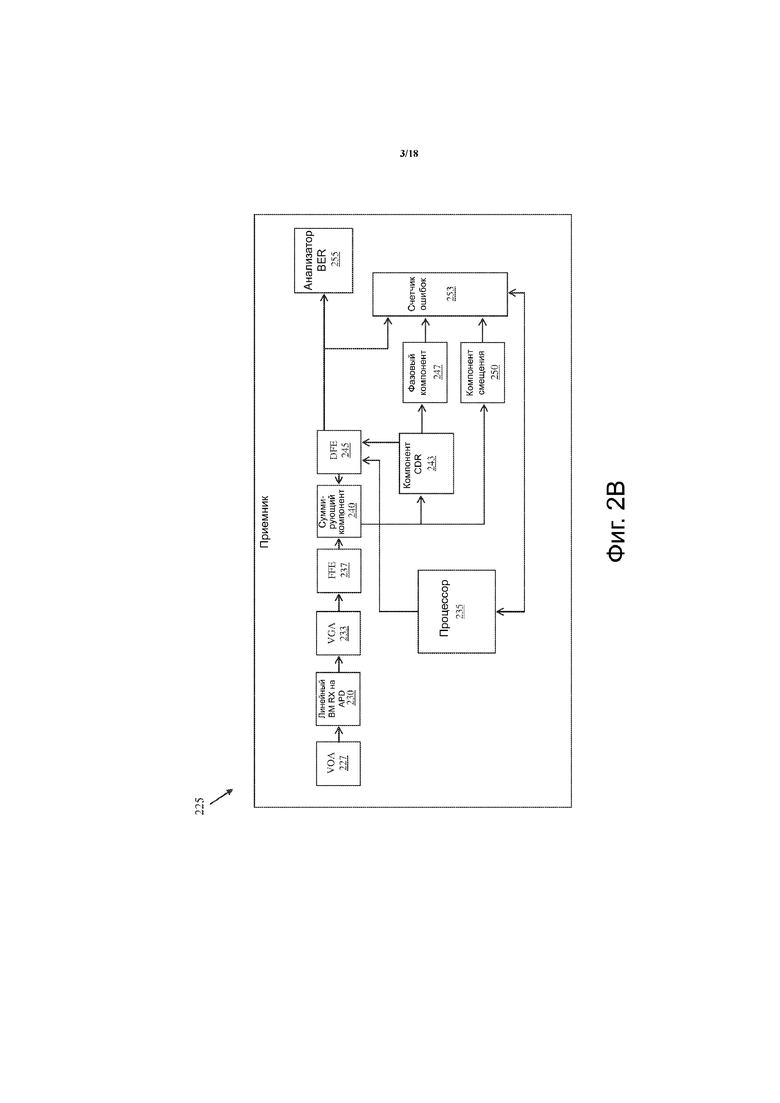

Фиг. 2B - схематичное представление приемника, показанного на фиг. 2A.

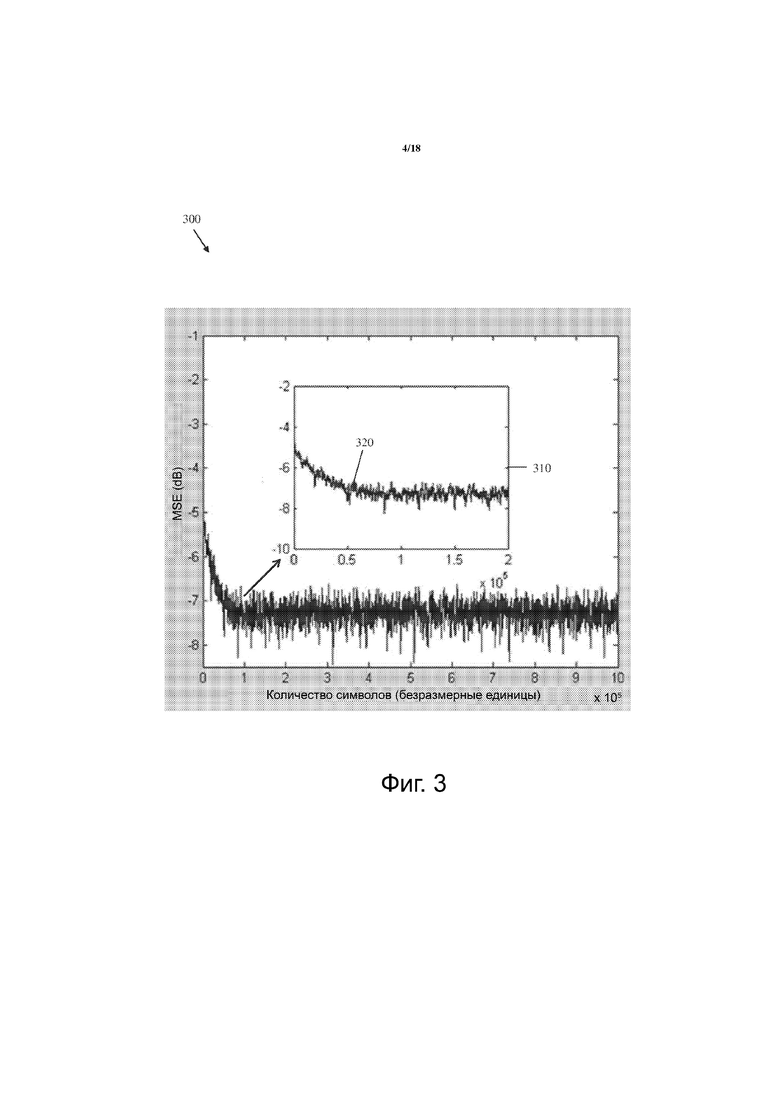

Фиг. 3 - график ошибки при двухуровневом выравнивании в FFE, показанном на фиг. 2B.

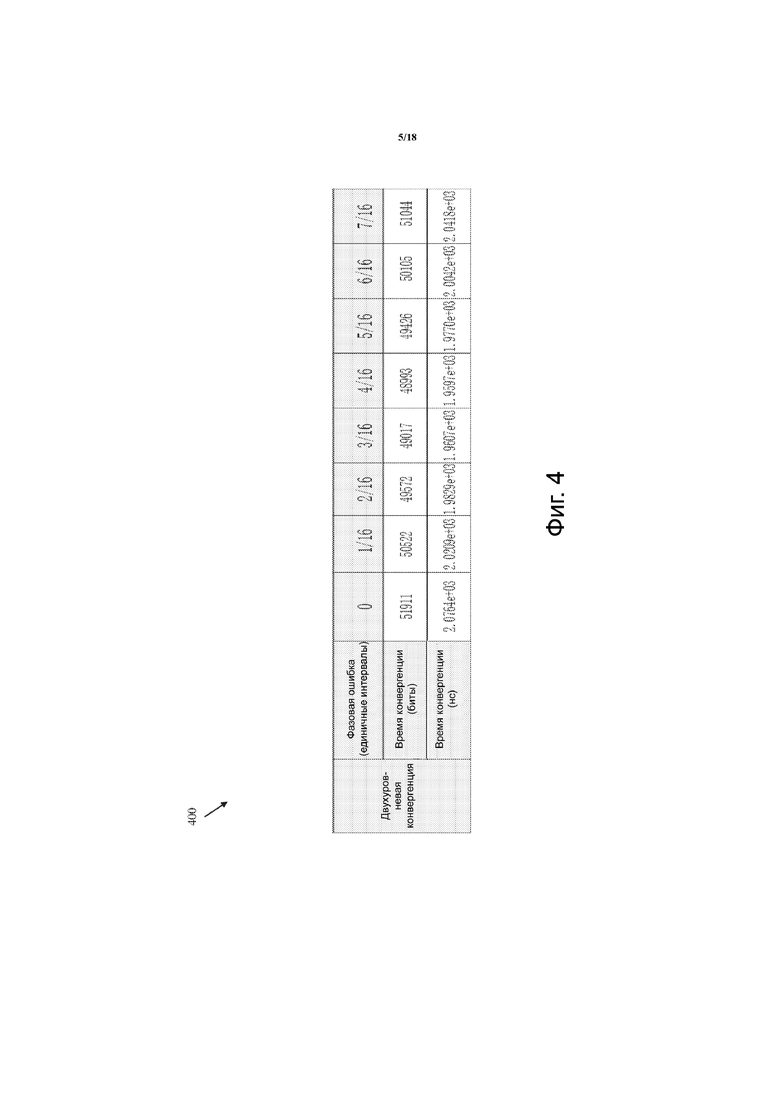

Фиг. 4 - таблица времени двухуровневой конвергенции для различных фазовых ошибок синхронизации FFE, показанного на фиг. 2B.

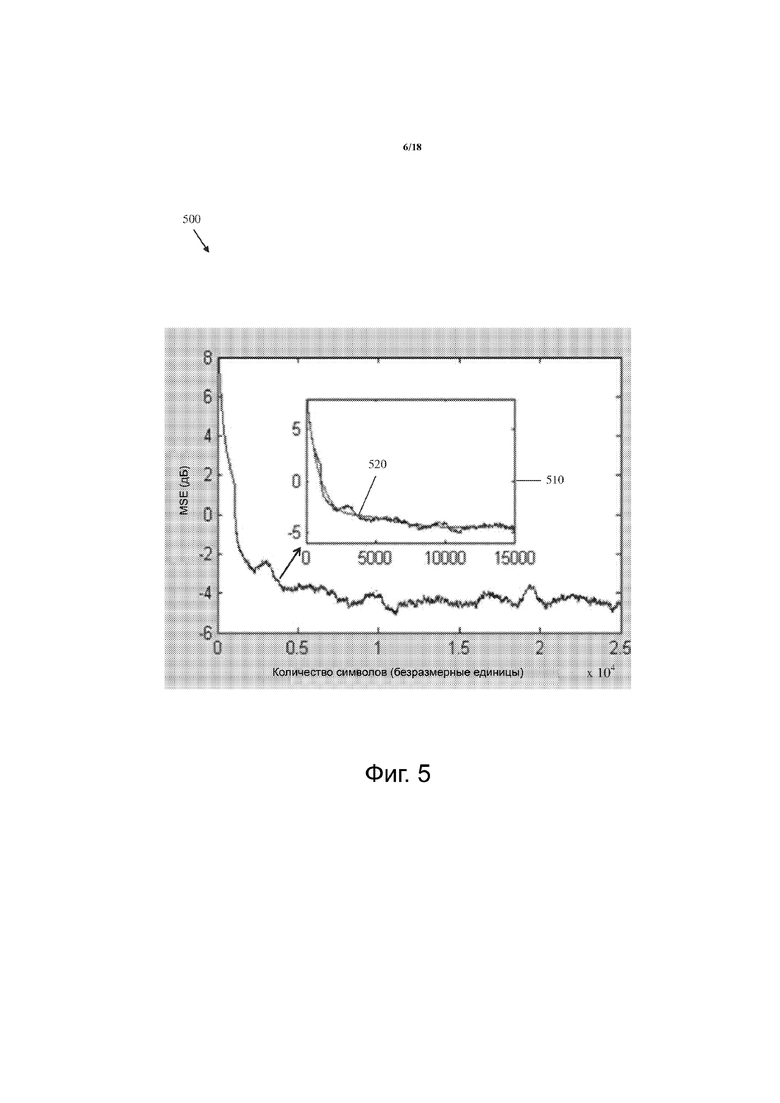

Фиг. 5 - график ошибки при четырехуровневом выравнивании в FFE, показанном на фиг. 2B.

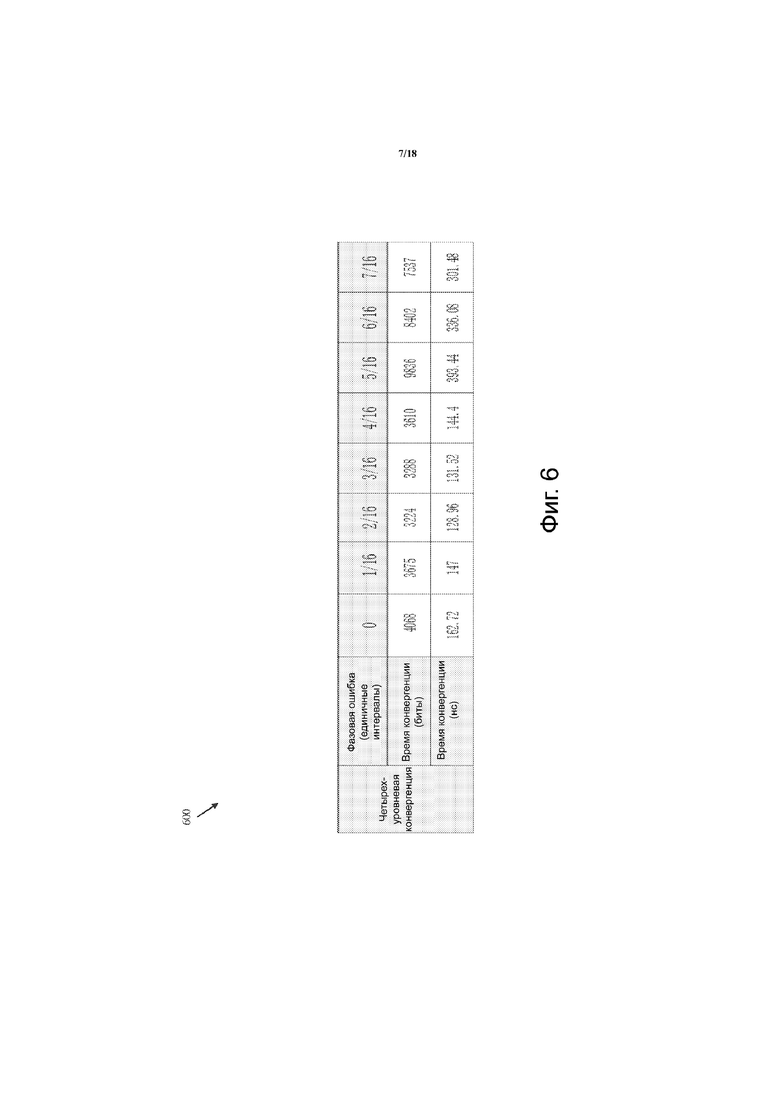

Фиг. 6 - таблица времени четырехуровневой конвергенции для различных фазовых ошибок синхронизации FFE, показанного на фиг. 2B.

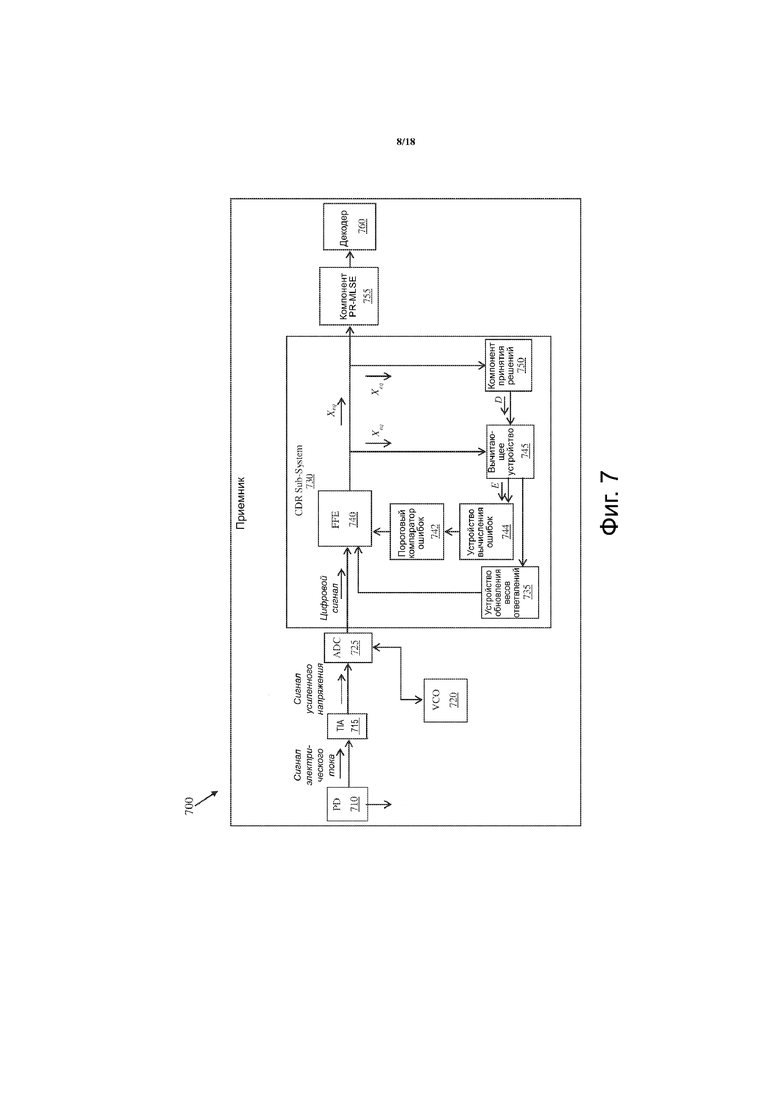

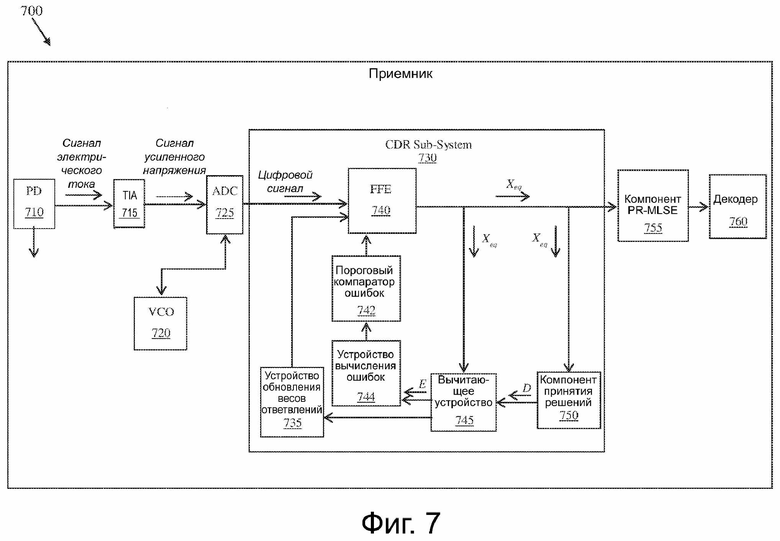

Фиг. 7 - приемник CDR повышенного уровня, соответствующий варианту осуществления раскрытия.

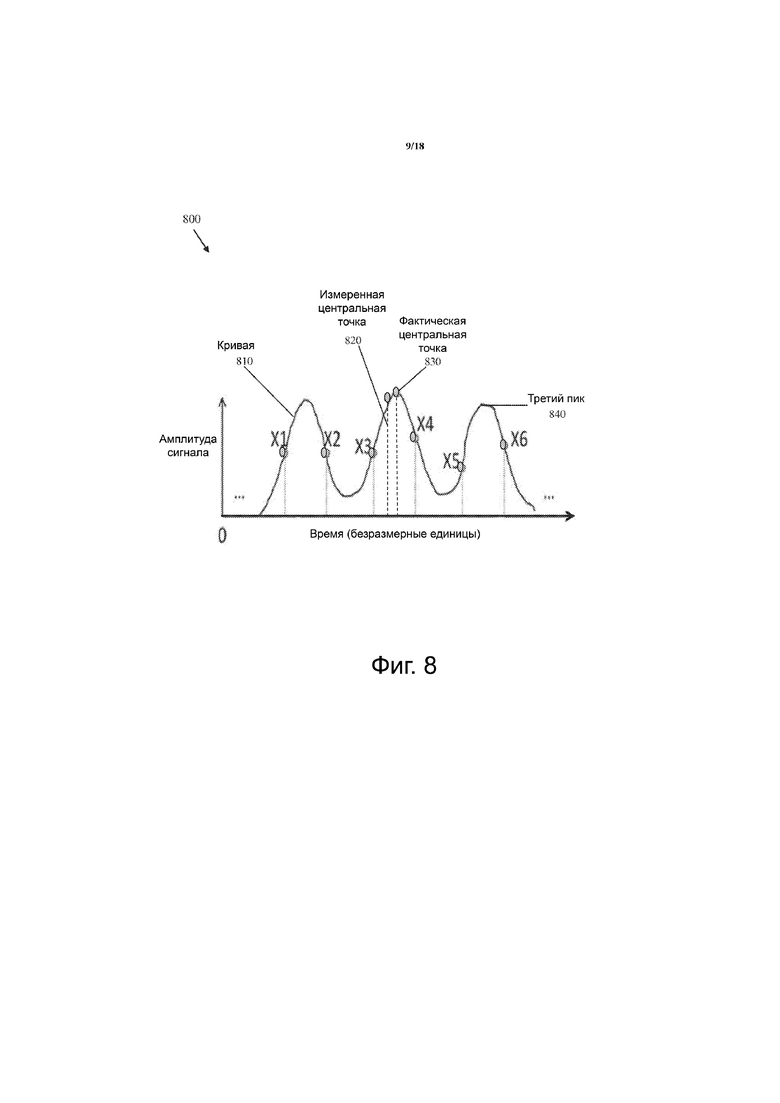

Фиг. 8 - график фазовой ошибки и ISI.

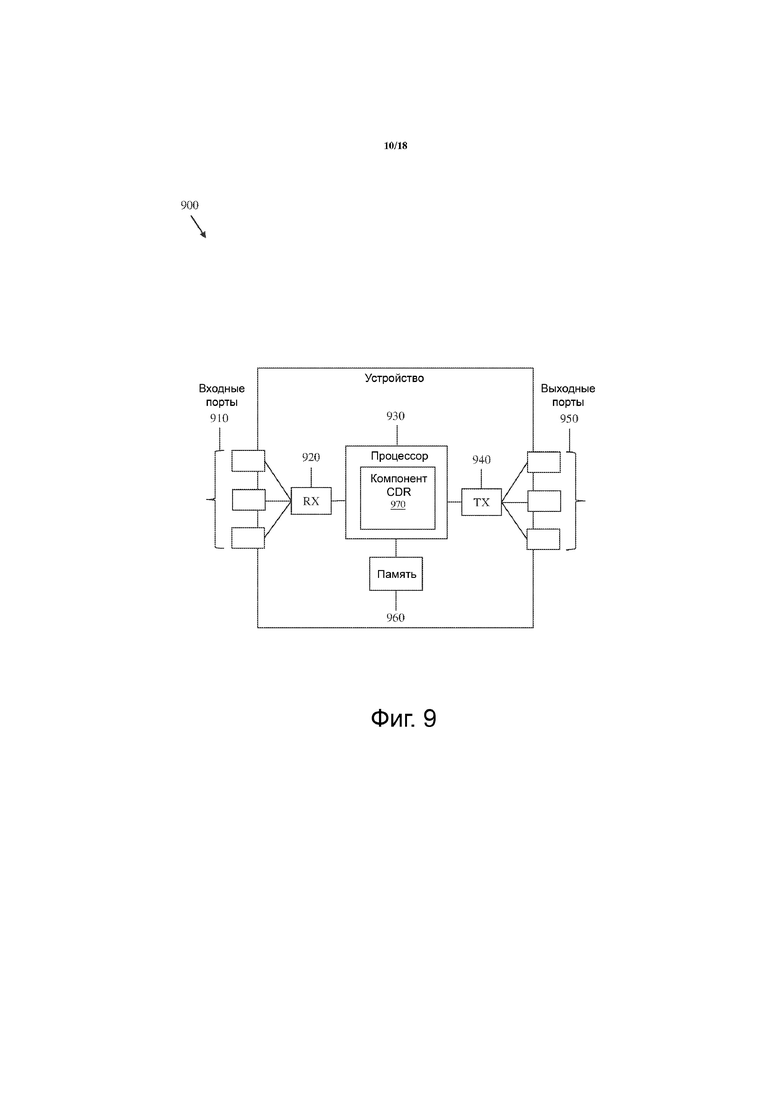

Фиг. 9 - схематичное представление устройства, соответствующего варианту осуществления раскрытия.

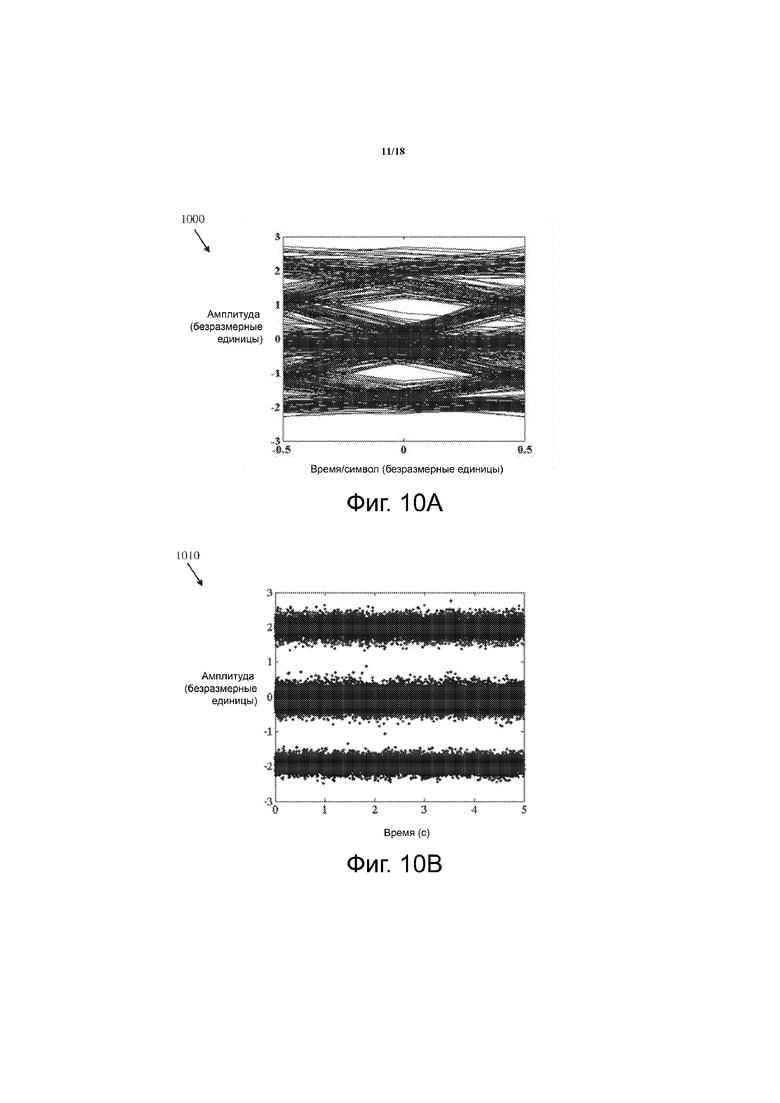

Фиг. 10A - двухуровневый сигнал NRZ, предшествующий трехуровневому CDR.

Фиг. 10B - график трехуровневого сигнала NRZ после CDR повышенного уровня, выполняемого на фиг. 7 в соответствии с вариантом осуществления раскрытия.

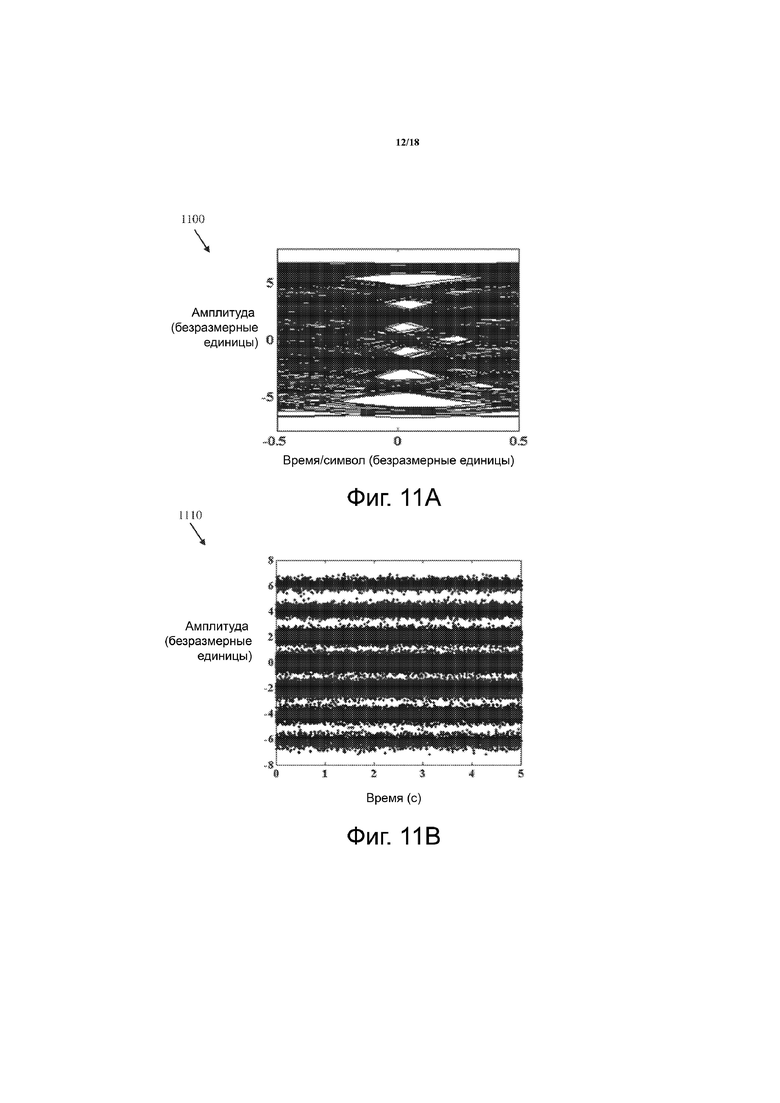

Фиг. 11A - четырехуровневый сигнал PAM4, предшествующий семиуровневому CDR.

Фиг. 11B - семиуровневый сигнал PAM4 после CDR повышенного уровня, соответствующего варианту осуществления раскрытия.

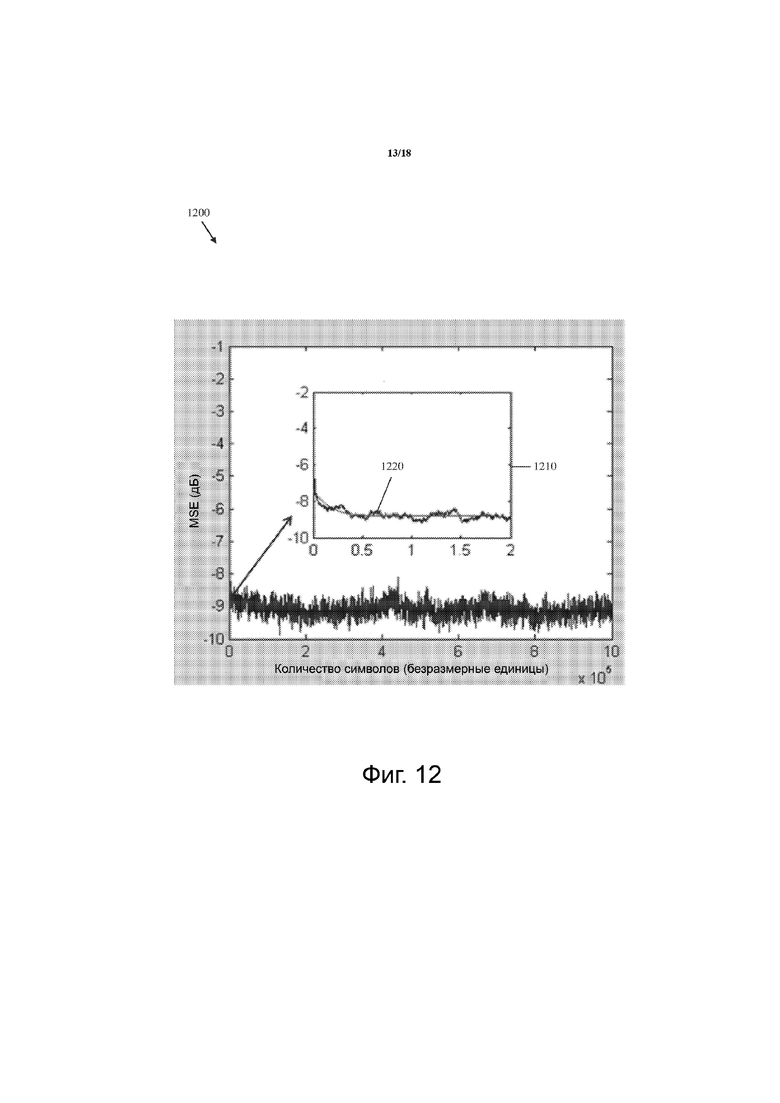

Фиг. 12 - график ошибки выравнивания двухуровневого сигнала NRZ, используя трехуровневое выравнивание в соответствии с вариантом осуществления раскрытия.

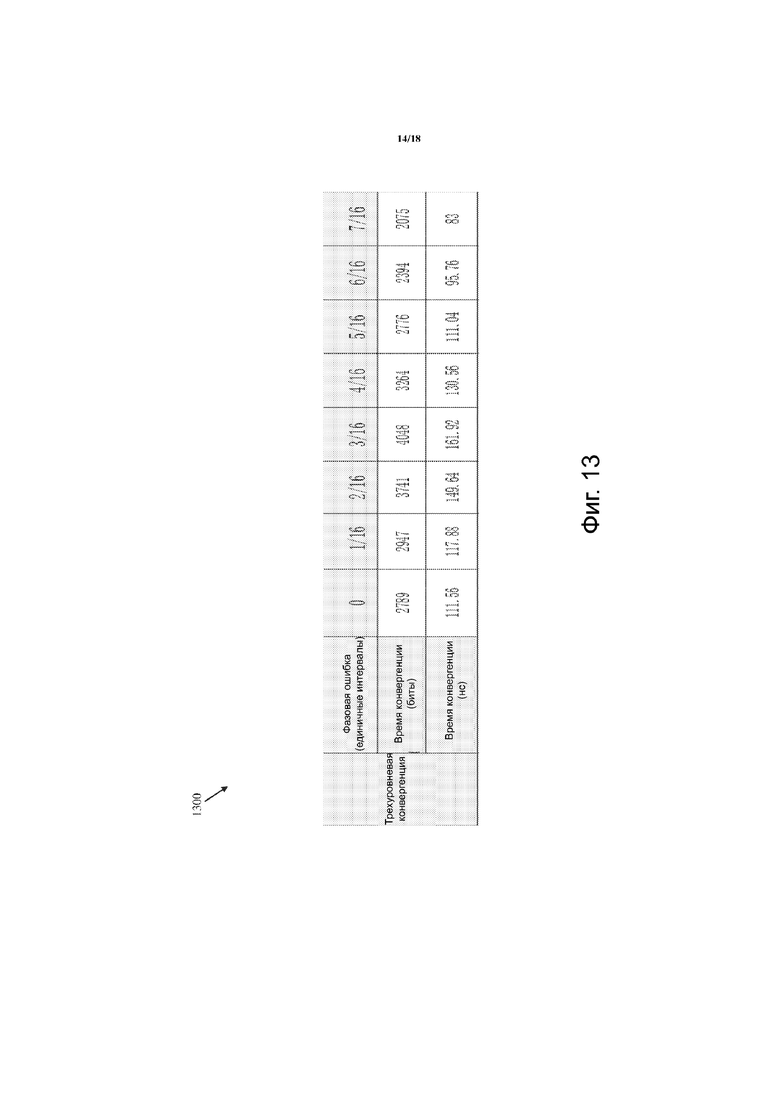

Фиг. 13 - таблица времени конвергенции для FFE, показанного на фиг. 7, выравнивающего двухуровневый сигнал NRZ, используя трехуровневое выравнивание, соответствующее варианту осуществления раскрытия.

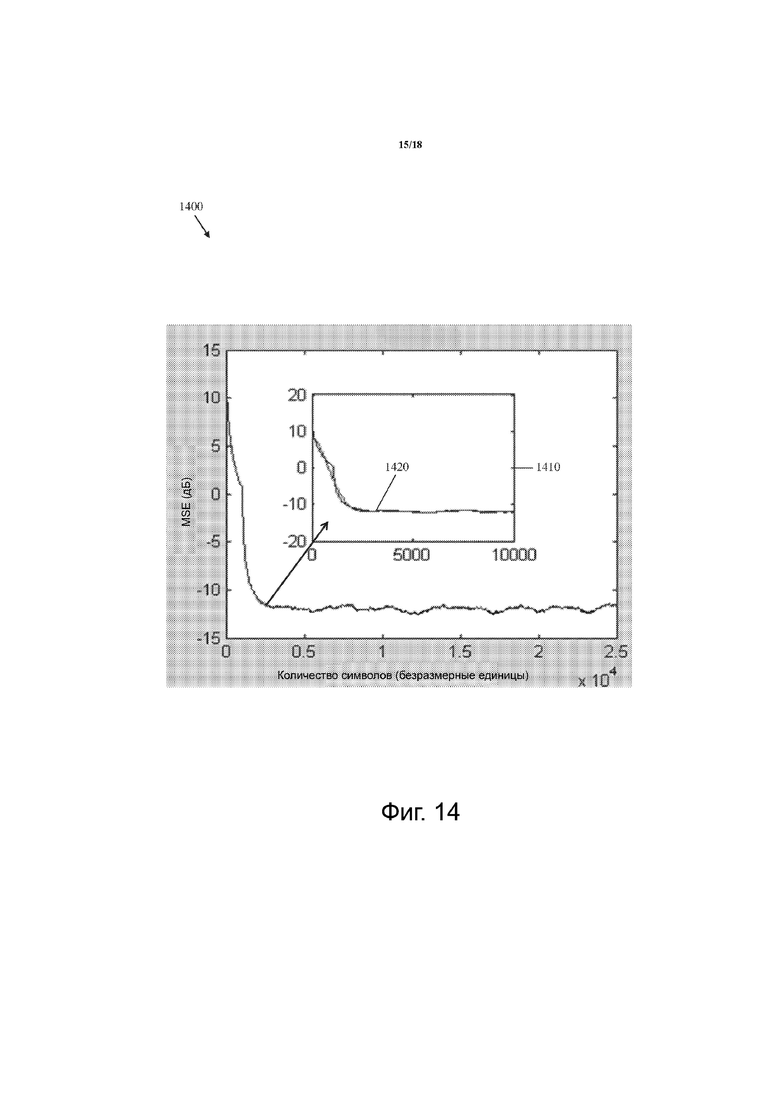

Фиг. 14 - график ошибки выравнивания для FFE, показанного на фиг. 7, выравнивающего четырехуровневый сигнал PAM4, используя семиуровневое выравнивание в соответствии с вариантом осуществления раскрытия.

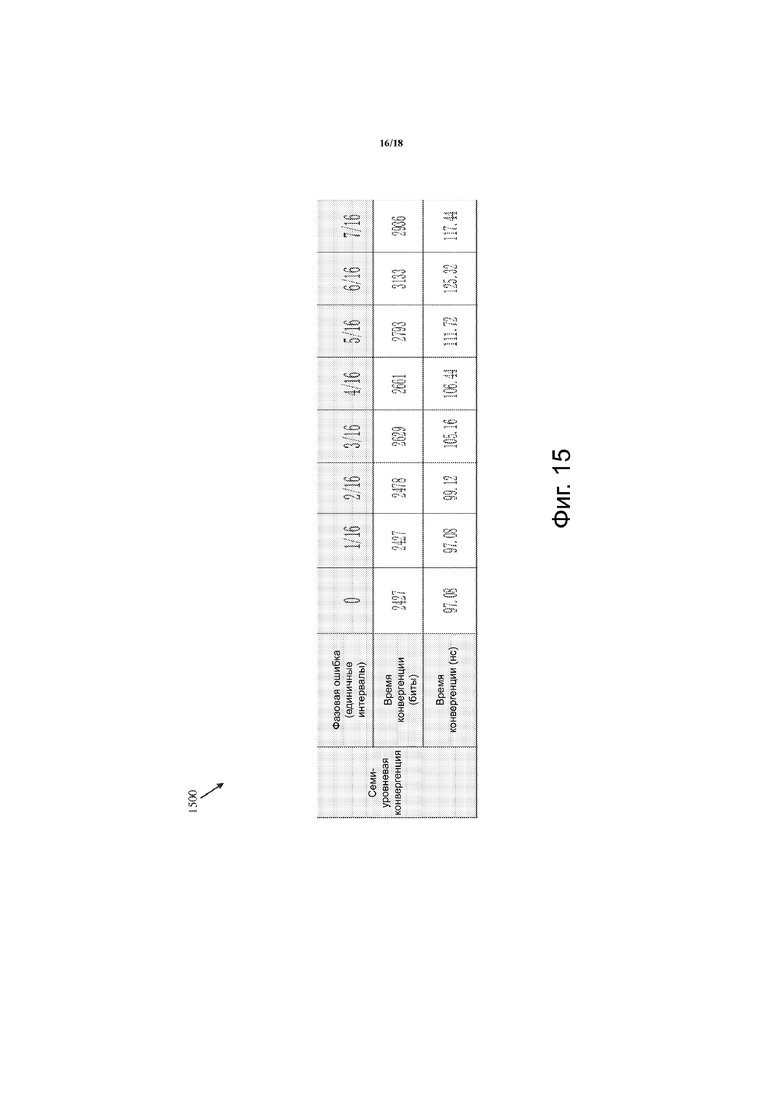

Фиг. 15 - таблица времени конвергенции для FFE, показанного на фиг. 7, выравнивающего четырехуровневый сигнал PAM4, используя семиуровневое выравнивание в соответствии с вариантом осуществления раскрытия.

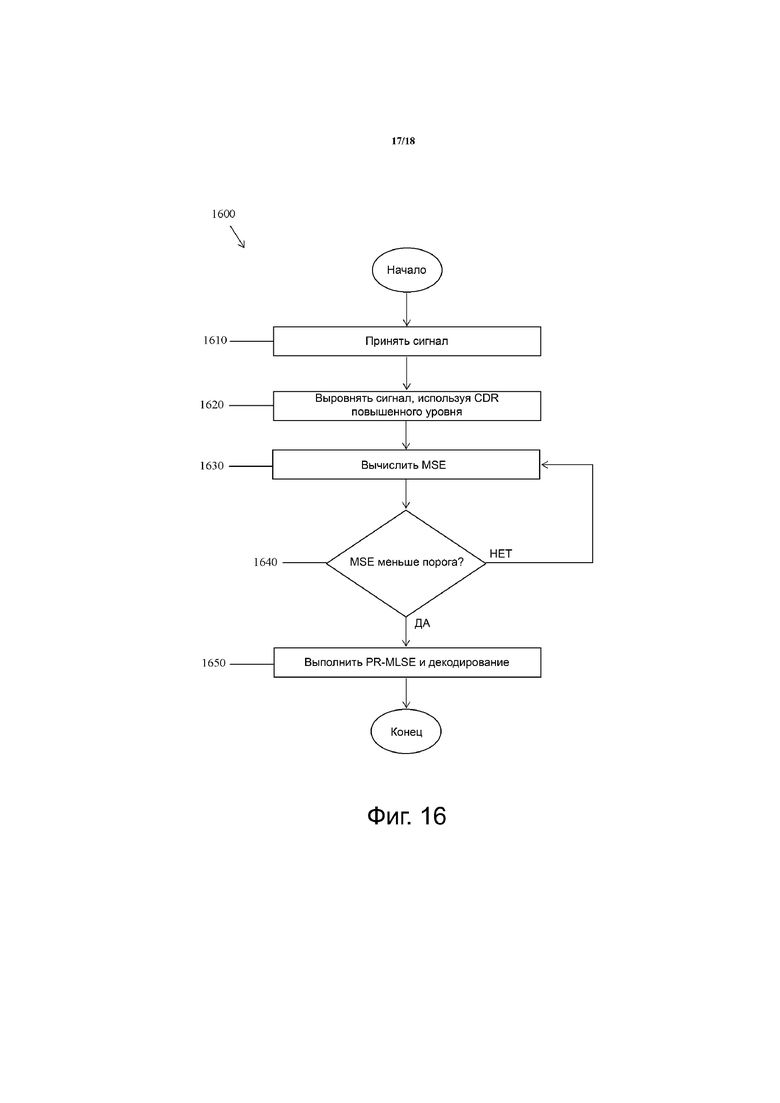

Фиг. 16 - блок-схема последовательности выполнения операций способа осуществления CDR повышенного уровня в соответствии с вариантом осуществления раскрытия.

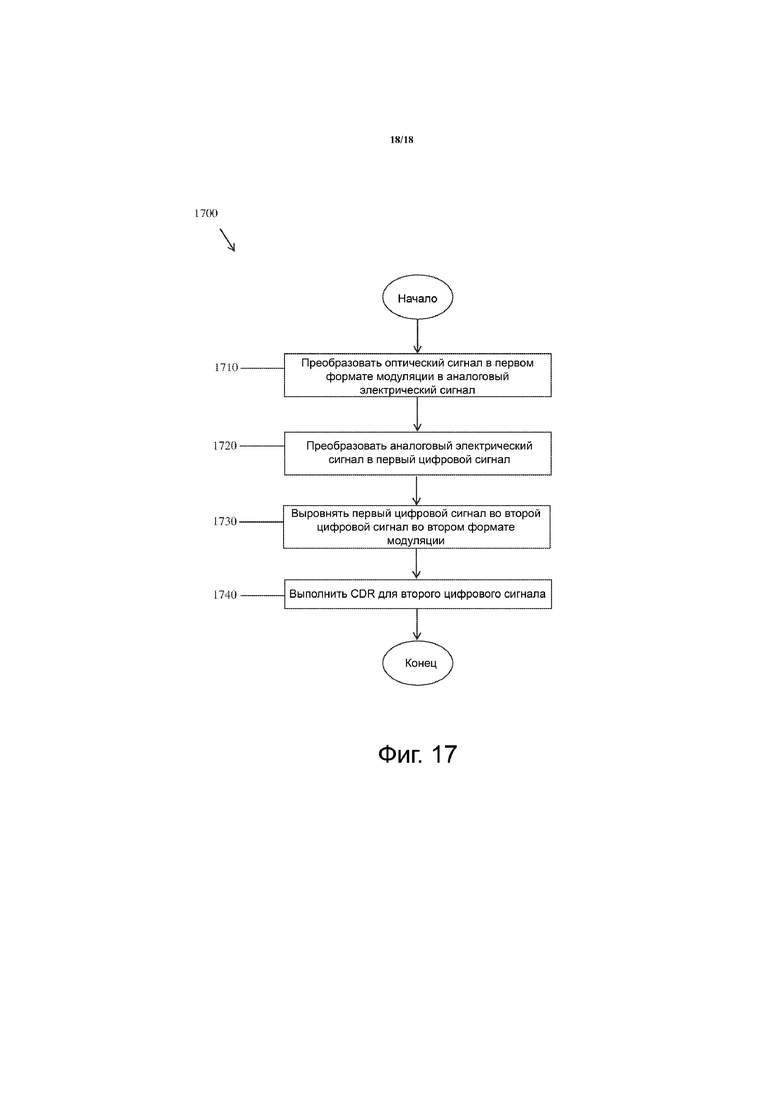

Фиг. 17 - блок-схема последовательности выполнения операций способа осуществления CDR повышенного уровня в соответствии с другим вариантом осуществления раскрытия.

Подробное раскрытие

Прежде всего следует понимать, что хотя ниже представлены иллюстративные реализации одного или более вариантов осуществления, раскрытые системы и/или способы могут быть осуществлены, используя множество способов, независимо от того, известны ли они или существуют. Раскрытие никоим образом не может ограничиваться иллюстративными реализациями, чертежами и способами, показанными ниже, в том числе, примерными конструкциями и реализациями, показанными и описанными здесь, но может модифицироваться в рамках объема приложенной формулы изобретения вместе с их полномасштабными эквивалентами.

Применяются нижеследующие сокращения:

ADC - аналого-цифровой преобразователь

APD - лавинный фотодиод (PD)

ASIC - специализированные интегральные схемы

BER - частота битовых ошибок

BM - пакетный режим

CDR - восстановление синхронизации и данных

CO - центральный офис

CPU - центральный процессор

dB - децибел(-ы)

DFE - выравниватель с решающей обратной связью

DSP - цифровой сигнальный процесс (процессор)

EML - электропоглощающий модулируемый лазер

EPON - пассивная оптическая сеть Ethernet (Ethernet PON)

EO - электрооптический

FFE - выравниватель прямого действия

FPGA - программируемая логическая интегральная схема

GBd - Гигабод

Gb/s - Гигабит в секунду

GPON - гигабитная сеть PON

GEPON - гигабитная сеть Ethernet PON

ISI - межсимвольная помеха

LO - гетеродин

MAC - управление доступом к носителю

Mb/s - Мегабит в секунду

MLSE - оценка последовательности с максимальной вероятностью

ms - миллисекунда(-ы), мс

MSE - среднеквадратичная ошибка

NRZ - без возврата к нулю

ns - наносекунда(-ы), нс

OA - оптический усилитель

ODN - оптическая распределительная сеть

OE - оптоэлектрический

OLT - терминал оптической линии связи

ONU - оптический сетевой блок

P2MP - точка-мультиточка

PAM4 - четырехуровневая амплитудно-импульсная модуляция

PD - фотодиод

PON - пассивная оптическая сеть

PR - парциальный отклик

RAM - оперативная память

RN - удаленный узел

ROM - постоянная память

RX - приемник

SOA - полупроводниковый оптический усилитель

SRAM - статическая RAM

SSMF - стандартный одномодовый оптоволоконный кабель

TCAM - трехзначная ассоциативная память

TDM - мультиплексирование с разделением каналов во времени

TDMA - мультидоступ с разделением каналов во времени

TIA - усилитель напряжения, управляемый током

TX - передатчик

ui - единичный интервал

VCO - генератор, управляемый напряжением

VGA - усилитель с регулируемым коэффициентом усиления

VOA - регулируемый оптический аттенюатор

WDM - мультиплексирование с разделением каналов по длинам волн

µs - микросекунда(-ы), мкс

Желательным является реализация подхода с выравниванием, при котором конвергенция достигается при меньшем количестве символов, в то же время сохраняя или уменьшая MSE. Такой подход должен также уменьшить сложность системы и чувствительность к ISI. В соответствии с различными вариантами осуществления настоящего раскрытия, раскрываются варианты осуществления CDR повышенного уровня в сетях PON. Варианты осуществления содержат единый FFE, который может быть отнесен к долевому FFE, поскольку он выполняет по меньшей мере две функции, а именно, CDR для корректирования фазы и выравнивания для компенсации ISI. FFE является адаптивным, так что он может следить за смещением частоты и джиттером. По этим причинам FFE уменьшает сложность ADC и DSP. Кроме того, FFE реализует CDR повышенного уровня, например, трехуровневое CDR для сигналов NRZ и семиуровневое CDR для сигналов PAM4. CDR повышенного уровня сокращает время конвергенции CDR, что позволяет иметь более дешевые узкополосные варианты, гарантирует удовлетворение требований к временам преобразования, предъявляемых в различных стандартах на PON; и снижает шум выравнивания. Варианты осуществления применяются как к приемникам нисходящих линий связи, таким как ONU, так и к приемникам восходящих линий связи, таким как OLT, хотя приемники восходящих линий связи, принимающие сигналы в пакетном режиме, могут обеспечивать максимальное преимущество. Эти сигналы в пакетном режиме могут иметь скорость передачи, по меньшей мере, до 40 Гб/с.

На фиг. 1 схематично представлена пассивная оптическая сеть 100 PON. PON 100 является сетью связи и содержит терминал оптической линии OLT 110, множество оптических сетевых блоков ONU 120 и оптическую распределительную сеть ODN 130, связывающую OLT 110 с блоками ONU 120. PON 100 пригодна для реализации раскрытых вариантов осуществления.

OLT 110 осуществляет связь с блоками ONU 120 и другой сетью. Конкретно, OLT 110 является промежуточным звеном между другой сетью и блоками ONU 120. Например, OLT 110 направляет данные, принятые от другой сети, к блокам ONU 120, а также направляет данные, принятые от блоков ONU 120, к другой сети. OLT 110 содержит передатчик и приемник. Когда другая сеть использует сетевой протокол, отличающийся от протокола, используемого в PON 100, OLT 110 содержит преобразователь, преобразующий этот сетевой протокол в протокол PON и наоборот. OLT 110 обычно располагается в центральном месте, таком как центральный офис (central office, CO), но может также располагаться в других подходящих местах.

Распределительная сеть ODN 130 является системой распределения данных, содержащей оптоволоконные кабели, соединители, делители, распределители и другие соответствующие компоненты. Компоненты содержат пассивные оптические компоненты, не требующие электропитания, для распределения сигналов между OLT 110 и блоками ONU 120. Компоненты могут также содержать активные компоненты, такие как оптические усилители, требующие электропитания. ODN 130 расходится от OLT 110 по блокам ONU 120 в ветвящейся конфигурации, показанной на чертеже, но ODN 130 может быть конфигурирована любым другим способом, пригодным для систем P2MP.

Блоки ONU 120 осуществляют связь с OLT 110 и потребителями и действуют в качестве промежуточных звеньев между OLT 110 и потребителями. Например, блоки ONU 120 направляют данные от OLT 110 к потребителям, а также направляют данные от потребителей к OLT 110. Блоки ONU 120 содержат оптические передатчики, преобразующие электрические сигналы в оптические сигналы и передающие оптические сигналы к OLT 110, и блоки ONU 120 содержат оптические приемники, принимающие оптические сигналы от OLT 110 и преобразующие оптические сигналы в электрические сигналы. Блоки ONU 120 дополнительно содержат вторые передатчики, передающие электрические сигналы потребителям, и вторые приемники, принимающие электрические сигналы от потребителей. Блоки ONU 120 и терминалы ONT похожи и термины могут использоваться взаимообразно. Блоки ONU 120 обычно располагаются в распределенных местах, таких как помещения пользователей, но они могут также располагаться в других подходящих местах.

На фиг. 2A схематично показана система 200 передачи данных. Система 200 передачи данных описана в статье Xin Yin и др. “A 10Gb/s APD-based linear burst-mode receiver with 31dB dynamic range for reach-extended PON systems,” Optics Express, том 20, № 26, 3 декабря 2012 г., включенной сюда посредством ссылки. Система 200 передачи данных обычно содержит передатчик 203; стандартные одномодовые оптоволоконные кабели SSMF 213, 223; удаленный узел RN 215; и приемник 225. Передатчик 203 может быть реализован в OLT 110, а приемник 225 может быть реализован в одном из блоков ONU 120 или наоборот, и SSMF 213, 223 и RN 215 могут быть реализованы в ODN 130.

Передатчик 203 содержит генератор 205 эталонов, передатчики 207 и регулируемые оптические аттенюаторы VOA 210. Генератор 205 эталонов генерирует оптические сигналы определенных эталонов и подает оптические сигналы первого эталона на первый передатчик 207 и оптические сигналы второго эталона на второй передатчик 207. Передатчики 207 передают оптические сигналы на VOA 210. VOA 210 усиливают оптические сигналы и передают оптические сигналы на удаленный узел RN 215 через SSMF 213.

RN 215 содержит SOA 217 и оптический фильтр 220. SOA 217 усиливает оптические сигналы. Оптический фильтр 220 выборочно модифицирует оптические сигналы, чтобы добиться оптимальных свойств сигнала для высококачественной передачи, и передает оптические сигналы на приемник 225 через SSMF 223. Приемник 225 выполняет выравнивание каналов для оптических сигналов. Приемник 225 дополнительно описывается ниже со ссылкой на фиг. 2B.

На фиг. 2B схематично представлен приемник, показанный на фиг. 2A. Приемник 225 содержит VOA 227, линейный приемник RX 230 на APD, работающий в пакетном режиме BM, регулируемый усилитель VGA 233, процессор 235, выравниватель FFE 237, суммирующий компонент 240, компонент 243 CDR, выравниватель DFE 245, фазовый компонент 247, компонент 250 смещения, счетчик 253 ошибок и анализатор BER 255. Как упомянуто выше, приемник 225 принимает оптические сигналы от RN 215 через SSMF 223. VOA 227 уменьшает мощность оптического сигнала, чтобы согласовать ее с желаемым качеством приема. Линейный приемник RX 230 на APD преобразует оптические сигналы в электрические сигналы. VGA 233 усиливает и оцифровывает электрические сигналы, чтобы сформировать пакетированные цифровые сигналы. FFE 237 выполняет линейное выравнивание пакетированных цифровых сигналов, чтобы сформировать линейные выровненные сигналы.

Суммирующий компонент 240 суммирует линейный выровненный сигнал от FFE 237 и сигнал DFE от DFE 245, чтобы сформировать суммарный выровненный сигнал. Суммирующий компонент 240 выполняет суммирование периодически до тех пор, пока не закончится выравнивание каналов, которое означает, что фаза дискретизации оптимизирована и суммарный выровненный сигнал конвергирован. Компонент CDR 243 выполняет CDR, чтобы сформировать восстановленный сигнал. DFE 245 выполняет оценку восстановленного сигнала, чтобы сформировать сигнал DFE.

Фазовый компонент 247 выравнивает фазу восстановленного сигнала с тактовым сигналом во время выравнивания каналов. Компонент 250 смещения регулирует сигналы в соответствии с потерями смещения. Счетчик 253 ошибок вычисляет данные ошибок, основываясь на сигнале DFE, значениях, полученных от фазового компонента 247, и значениях, полученных от компонента 250 смещения. Анализатор BER 255 выполняет анализ сигнала DFE, чтобы определить количество битовых ошибок. Выравнивание и CDR выполняются непрерывно до тех пор, пока сигналы не будут конвергированы и фаза дискретизации не оптимизируется. Процессор 235 определяет, когда выравнивание оптических сигналов завершено. Как показано на чертеже, чтобы гарантировать характеристики приемника 225, компонент CDR 243, FFE 237 и DFE 245 независимы друг от друга, но это увеличивает сложность, затраты, время конвергенции и чувствительность приемника 225 к ISI.

На фиг. 3 представлен график 300, показывающий ошибку при двухуровневом выравнивании в FFE 237, показанном на фиг. 2B. Конкретно, график 300 демонстрирует экспериментальные результаты для PON, работающей со скоростью 25 Гб/с, использующей модуляцию NRZ с применением EML (скорость 10 Гб/с) и APD. График 300 содержит субграфик 310, показывающий увеличенный участок графика 300, указанный стрелкой. По оси x представлено количество символов в безразмерных единицах, а по оси y представлена MSE в дБ. Конвергенция происходит, когда кривая 320 320 становится горизонтальной, что имеет место при 51911 символах после 2,07 мкс, что является относительно большим временем для выравнивания каналов. После конвергенции MSE равна приблизительно -8 дБ.

На фиг. 4 представлена таблица 400, показывающая время двухуровневой конвергенции для различных фазовых ошибок сигнала синхронизации FFE 237, показанного на фиг. 2B. Чтобы всесторонне оценить время конвергенции CDR, получают и обрабатывают данные с различными начальными фазами дискретизации. Таким образом, таблица 400 дополнительно показывает, что фазовая ошибка отрицательно влияет на времена конвергенции, показанные на фиг. 3. Таблица 400 содержит три набора значений, фазовую ошибку в безразмерных единичных интервалах ui, первое время конвергенции, измеренное в битах, и второе время конвергенции, измеренное в нс. Как видно из таблицы, максимальное время конвергенции CDR, равное 51911 символов и 2,07 мкс (2,0764×103 нс), имеет место в точке дискретизации с нулевой фазовой ошибкой, выраженной в единичных интервалах ui.

На фиг. 5 представлен график 500, показывающий ошибку при четырехуровневом выравнивании в FFE 237, показанном на фиг. 2B. Конкретно, график 500 демонстрирует экспериментальные результаты для PON, работающей со скоростью 50 Гб/с, использующей модуляцию PAM4 со скоростью 25 Гбод с применением EML (скорость 10 Гб/с) и APD. График 500 содержит субграфик 510, являющийся увеличенным участком графика 500, указанным стрелкой. По оси x представлено количество символов в безразмерных единицах, а по оси y представлена MSE в дБ. Конвергенция происходит, когда кривая 520 становится горизонтальной, что имеет место при 7537 символах после 301,48 нс. После конвергенции MSE равна приблизительно -5 дБ.

На фиг. 6 представлена таблица 600, показывающая время четырехуровневой конвергенции для различных фазовых ошибок синхронизации FFE 237, показанного на фиг. 2B. Таблица 600 дополнительно показывает, что фазовая ошибка отрицательно влияет на времена конвергенции, показанные на фиг. 5. Таблица 600 содержит три набора значений, фазовую ошибку в безразмерных единичных интервалах (ui), первое время конвергенции, выраженное в битах, и второе время конвергенции, выраженное в нс. Как видно из таблицы, максимальное время конвергенции CDR 9836 символов и 393,44 нс имеет место в точке дискретизации с фазовой ошибкой 5/16 единичного интервала.

По мере того, как растет потребность в более высокой скорости передачи данных, скорость обработки и выравнивания этих данных также должна повышаться. В частности, когда скорости разработки дешевых узкополосных электрических компонент растут не столь быстро, как растут скорости передачи данных PON, ограничения по ширине полосы будут вносить значительные ISI. В этой ситуации такие подходы к выравниванию каналов, как двухуровневое и четырехуровневое выравнивание, показанные выше, не могут быть достаточно скоростными. Следовательно, желательно реализовать подход с выравниванием, при котором конвергенция достигается при меньшем количестве символов, в то же время, сохраняя или уменьшая MSE. Такой подход должен также снизить сложность системы и чувствительность к ISI.

В представленной заявке раскрыты варианты осуществления CDR повышенного уровня в сетях PON. Варианты осуществления содержат единый FFE, который может упоминаться как парциальный FFE, поскольку он выполняет по меньшей мере две функции, а именно, CDR для фазовой коррекции и выравнивания для компенсации ISI. FFE является адаптивным, поэтому он может также следить за смещением частоты и джиттером. По этим причинам FFE уменьшает сложности ADC и DSP. Кроме того, FFE реализует CDR повышенного уровня, например, трехуровневое CDR для сигналов NRZ и семиуровневое CDR для сигналов PAM4. CDR повышенного уровня сокращает время конвергенции CDR, что позволяет использование дешевых узкополосных опций, гарантирует удовлетворение требований к временам конвергенции, содержащихся в различных стандартах для PON, и уменьшает шумы выравнивания. Варианты осуществления применяются как к приемникам нисходящих каналов, таким как блоки ONU, так и к приемникам восходящих каналов, таким как OLT, хотя приемники восходящих каналов, принимающие сигналы в пакетном режиме, могут обеспечивать максимальный выигрыш. Такие пакетированные сигналы могут иметь скорость по меньшей мере до 40 Гб/с.

На фиг. 7 схематично представлен приемник 700, соответствующий варианту осуществления раскрытия. Приемник 700 может быть реализован в OLT и в блоках ONU 120 и приемник 700 может реализовать приемник 225. Приемник 700 содержит PD 710, TIA 715, VCO 720, ADC 725, подсистему CDR 730, компонент PR-MLSE 755 и декодер 760.

Фотодиод PD 710 преобразует оптический сигнал в пакетном режиме в сигнал электрического тока. TIA 715 преобразует сигнал электрического тока в сигнал усиленного напряжения. ADC 725 оцифровывает сигнал усиленного напряжения и преобразует сигнал усиленного напряжения, являющийся аналоговым электрическим сигналом, в цифровой электрический сигнал. VCO 720 оцифровывает ADC 725, чтобы синхронизировать частоту между приемником 700 и передатчиком. Однако, приемник 700 и передатчик могут работать с разными фазами, которые могут упоминаться как фазовая ошибка. Фазовая ошибка и ISI показаны на фиг. 8.

На фиг. 8 представлен график 800, показывающий фазовую ошибку и ISI. По оси x представляется время в безразмерных единицах, а по оси y представляется амплитуда сигнала в безразмерных единицах. График 800 содержит кривую 810, представляющую оцифрованный сигнал, например, оцифрованный сигнал от ADC 725, который оцифрован в шести точках выборки X1, X2, X3, X4, X5, X6. Точки выборки должны находиться в середине амплитуды сигнала каждого пика сигнала усиленного напряжения. Однако, из-за несовершенств канала, вносимых, например, кабелями SSMF 213, 223, точки выборки могут быть не этими точками. Прежде всего, может существовать фазовая ошибка и поэтому ADC оцифровывает упрощенный сигнал напряжения в ложных точках. Таким образом, измеренная центральная точка 820 между точками оцифровки X3 и X4 должна находиться слева от фактической центральной точки 830 между точками выборки X3 и X4. Кроме того, ISI может искажать пики кривой 810. Таким образом, третий пик расширяется в левую сторону, так что точка выборки X5 находится ниже, чем средняя амплитуда сигнала третьего пика 840.

Возвращаясь к фиг. 7, подсистема 730 CDR содержит устройство 735 обновления весов ответвлений, FFE 740, пороговый компаратор 742 ошибки, устройство 744 вычисления ошибки, вычитающее устройство 745 и компонент 750 принятия решения, которые вместе образуют контур с обратной связью для выполнения CDR и выравнивания и, таким образом, компенсируют описанные выше фазовую ошибку и ISI. Конкретно, в первой итерации FFE 740 передает вычитающему устройству 745 выровненный сигнал Xeq, являющийся сигналом выборки от ADC 725, для первой итерации. Компонент 750 принятия решения передает вычитающему устройству 745 данные D решения, которые являются обучающей последовательностью для первой итерации. Вычитающее устройство 745 вычисляет сигнал E ошибки следующим образом:

E = Xeq - D (1)

Вычитающее устройство 745 передает сигнал ошибки на устройство 735 обновления весов ответвлений и на устройство вычисления ошибки. На основе сигнала ошибки устройство 735 обновления весов ответвлений вычисляет веса ответвлений W(1), W(2), W(3), W(4), W(5), W(6), соответствующие точкам выборки X1, X2, X3, X4, X5, X6, соответственно.

В последующих итерациях FFE 740 вычисляет выровненный сигнал следующим образом:

Xeq = W(1)X(1) + W(2)X(2) + W(3)X(3) + W(4)X(4) + W(5)X(5) + W(6)X(6) (2)

где X(1), X(2), X(3), X(4), X(5), X(6) соответствуют амплитудам оцифрованного сигнала в точках выборки X1, X2, X3, X4, X5, X6, соответственно. FFE 740 передает выровненный сигнал на вычитающее устройство 745 и компонент 750 принятия решения. Как показано ниже на фиг. 10A 11A, при значительной помехе ISI, создаваемой ограничением, осуществляемым оптическими устройствами, принятый сигнал побитно перекрывается во временной области и больше похож на сигнал повышенного уровня, например, трехуровневый сигнал для NRZ и семиуровневый сигнал для PAM-4, чем на переданный двухуровневый сигнал NRZ или четырехуровневый сигнал PAM-4. Поэтому получить конвергенцию становится легче, если компонент 750 принятия решения определяет данные решения, основываясь на следующем принципе принятия решения повышенного уровня:

{6 если Xeq > 5

{4 если Xeq > 3

{2 если Xeq > 1

D = {0 если -1 ≤ Xeq ≤ 1 (3)

{-2 если Xeq < -1

{-4 если Xeq < -3

{-6 если Xeq < -5

Устройство 745 вычитания сигнал ошибки, используя уравнение (1), устройство 735 обновления весов ответвлений вычисляет веса ответвлений, основываясь на сигнале ошибки, и FFE 740 снова вычисляет выровненный сигнал, используя уравнение (2).

Этот контур обратной связи продолжает действовать, пока выровненный сигнал не будет конвергирован, и поэтому будет иметь ошибку выравнивания, равную или ниже заданного порога. Конкретно, устройство 744 вычисления ошибки вычисляет MSE ошибки выравнивания. Пороговый компаратор 742 ошибки определяет, является ли MSE меньше порога. Если ошибка равна или меньше порога, то пороговый компаратор 742 ошибки подает команду на подсистему 730 CDR прекратить работу контура обратной связи. Если ошибка больше порога, то пороговый компаратор 742 ошибки не дает никаких команд на подсистему 730 CDR или подает на подсистему 730 CDR команду продолжить работу контура обратной связи. Порог равен, например, -6 дБ.

Хотя описаны шесть весов ответвлений, точек выборки и амплитуд, подсистема 730 CDR может использовать любое количество весов ответвлений, точек выборки и амплитуд. Кроме того, данные для принятия решения являются трехуровневыми данными принятия решения, применимыми, например, к двухуровневым сигналам NRZ. Аналогично, данные для принятия решения могут быть семиуровневыми данными для принятия решения, применимыми, например, к сигналам PAM4. Независимо от уровня входящего сигнала, подсистема 730 CDR может реализовывать данные для принятия решения повышенного уровня. Дополнительно, хотя для определения конвергенции предлагается порог, подсистема 730 CDR может реализовать любой подходящий индикатор конвергенции.

Устройство 735 обновления весов ответвлений уведомляет FFE 740, что выровненный сигнал конвергирован. После этого FFE 740 передает выровненный сигнал на компонент PR-MLSE 755. Компонент PR-MLSE 755 использует известную реакцию канала, чтобы отобразить бит двоичного решения в битах повышенного уровня посредством суммирования предшествующего и более позднего бита в индивидуальные моменты времени. Сочетания различных битов возможных решений образуют треллисные траектории. Компонент PR-MLSE 755 использует траекторию с наименьшим евклидовым расстоянием по сравнению с выровненным сигналом, после чего FFE 740 должен быть самой надежной битовой траекторией. Компонент PR-MLSE 755 выводит биты на самую надежную битовую траекторию и преобразует эти биты обратно в двоичный сигнал. На описанных выше этапах компонент 755 PR-MLSE выполняет MLSE для выровненного сигнала, чтобы преобразовать выровненный сигнал в вычисленный сигнал, который является двоичным двухуровневым сигналом. Декодер 760 декодирует вычисленный сигнал, чтобы сформировать декодированный сигнал для дальнейшей обработки.

На фиг. 9 схематично представлено устройство 900, соответствующее варианту осуществления раскрытия. Устройство 900 может реализовывать раскрытые варианты осуществления, например, приемник 700. Устройство 900 содержит входные порты 910 и приемник RX 920 для приема данных; процессор, логический блок или CPU 930 для обработки данных; передатчик TX 940 и выходные порты 950 для передачи данных; и память 960 для хранения данных. Устройство 900 может также содержать OE-компоненты и EO-компоненты, связанные с входными портами 910, приемником RX 920, передатчиком TX 940 и выходными портами для 950 для ввода или вывода оптических или электрических сигналов.

Процессор 930 реализуется любым подходящим сочетанием аппаратных средств, промежуточного программного обеспечения, встроенного программного обеспечения и программного обеспечения. Процессор 930 может быть реализован как одна или более микросхем CPU, ядер (как, например, многоядерный процессор), FPGA, ASIC или DSP. Процессор 930 осуществляет связь с входными портами 910, RX 920, TX 940, выходными портами 950 и памятью 960. Процессор 930 содержит компонент 970 CDR, который может осуществлять раскрытые варианты осуществления. Введение компонента 970 CDR поэтому обеспечивает существенное улучшение функциональных возможностей устройства 900 и осуществляет перевод устройства 900 в различные состояния. Альтернативно, память 960 хранит компонент 970 CDR в качестве команд и процессор 930 выполняет эти команды.

Память 960 содержит один или более дисков, ленточных приводов или приводов твердотельных дисков и может использоваться в качестве запоминающего устройства при перегрузке, чтобы хранить программы, когда такие программы выбираются для исполнения, или для хранения команд и данных, которые считываются во время выполнения программ. Память 960 может быть энергозависимой или энергонезависимой и может быть любым сочетанием ROM, RAM, TCAM или SRAM.

В примерном варианте осуществления устройство 900 содержит модуль электрического преобразования, преобразующий оптический сигнал в первом формате модуляции в аналоговый электрический сигнал, модуль оцифровки, преобразующий аналоговый электрический сигнал в первый цифровой сигнал, модуль выравнивания, выравнивающий первый цифровой сигнал во второй цифровой сигнал со вторым форматом модуляции, где второй формат модуляции имеет больше уровней, чем первый формат модуляции, и модуль восстановления, выполняющий восстановление данных и синхронизации (CDR) для второго цифрового сигнала. В некоторых вариантах осуществления устройство 900 может содержать другие или дополнительные модули для выполнения любого одного или сочетания этапов, описанных в вариантах осуществления. Дополнительно, любой из дополнительных или альтернативных вариантов осуществления или подходов способа, показанных на любом из чертежей или перечисленных в любом из пунктов формулы изобретения, также рассматриваются как содержащие подобные модули.

На фиг. 10A представлена диаграмма 1000, показывающая двухуровневый сигнал NRZ, предшествующий трехуровневому CDR. По оси x представлена временную длительность или длительность в символах в безразмерных единицах, а по оси y представлена амплитуда в безразмерных единицах. Как можно видеть, двухуровневый сигнал NRZ представляется как имеющий почти три уровня и четко не определен из-за ISI.

На фиг. 10B представлен график 1010, показывающий трехуровневый сигнал NRZ после CDR повышенного уровня, соответствующий варианту осуществления раскрытия. По оси x представлено время в секундах и по оси y представлена амплитуда в безразмерных единицах. Как видно на графике, CDR повышенного уровня, по существу, удаляет ISI, чтобы получить четко определенный трехуровневый сигнал NRZ, в отличие от двухуровневого сигнала NRZ на фиг. 10A.

На фиг. 11A представлена диаграмма 1100, показывающая четырехуровневый сигнал PAM4, предшествующий семиуровневому CDR. По оси x представлено время в секундах, по оси y представлена амплитуда в безразмерных единицах. Как можно видеть на чертеже, четырехуровневый сигнал PAM4 представляется как имеющий почти семь уровней и нечетко определен из-за ISI.

На фиг. 11B представлен график 1110, показывающий семиуровневый сигнал PAM4 после CDR повышенного уровня, соответствующего варианту осуществления раскрытия. По оси x представлено время в секундах, по оси y представлена амплитуда в безразмерных единицах. Как показано на чертеже, CDR повышенного уровня, по существу, удаляет ISI, чтобы получить четко определенный семиуровневый сигнал, в отличие от четырехуровневого сигнала PAM4, показанного на фиг. 11A.

На фиг. 12 представлен график 1200, показывающий ошибку выравнивания для FFE 740, показанного на фиг. 7, выравнивающего двухуровневый сигнал NRZ, используя трехуровневое выравнивание, соответствующее варианту осуществления раскрытия. График 1200 содержит субграфик 1210, являющийся увеличенным участком графика 1200, указанным стрелкой. По оси x представлено количество символов в безразмерных единицах, по оси y представлена MSE в дБ. Конвергенция происходит, когда кривая 1220 становится горизонтальной, что имеет место примерно при 2789 символах после 111,56 нс. После конвергенции MSE равно приблизительно -9 дБ, что примерно на 2 дБ ниже, чем на фиг. 3.

На фиг. 13 представлена таблица 1300, показывающая время конвергенции для FFE 740, показанного на фиг. 7, выравнивающего двухуровневый сигнал NRZ, используя трехуровневое выравнивание в соответствии с вариантом осуществления раскрытия. Таблица 1300 дополнительно показывает время конвергенции, показанное на фиг. 12. Таблица 1300 содержит три набора значений, фазовую ошибку, выраженную в единичных интервалах, первое время конвергенции, выраженное в битах, и второе время конвергенции, выраженное в нс. Как видно из чертежа, в точке конвергенции 2789 символов и 111,56 нс фазовой ошибки не существует. Максимальное время конвергенции CDR 4048 символов и 161,92 нс имеет место в точке выборки с фазовой ошибкой 3/16 единичного интервала.

На фиг. 14 представлен график 1400, показывающий ошибку выравнивания для FFE 740, показанного на фиг. 7, выравнивающего четырехуровневый сигнал PAM4, используя семиуровневое выравнивание, соответствующее варианту осуществления раскрытия. График 1400 содержит субграфик 1410, являющийся увеличенным участком графика 1400, указанным стрелкой. По оси x представлено количество символов в безразмерных единицах, по оси y представлена MSE в дБ. Конвергенция происходит, когда кривая 1420 становится горизонтальной, что имеет место примерно при 2936 символах после 117,44 нс. После конвергенции MSE равно приблизительно -12 дБ, что примерно на 7 дБ ниже, чем на фиг. 5.

На фиг. 15 представлена таблица 1500, показывающая время конвергенции для FFE 740, показанного на фиг. 7, выравнивающего четырехуровневый сигнал PAM4, используя семиуровневое выравнивание в соответствии с вариантом осуществления раскрытия. Таблица 1500 дополнительно показывает время конвергенции, показанное на фиг. 14. Таблица 1500 содержит три набора значений, фазовую ошибку, выраженную в единичных интервалах, первое время конвергенции, выраженное в битах, и второе время конвергенции, выраженное в нс. Как видно из чертежа, максимальное время конвергенции CDR 2783 символов и 111,72 нс имеет место в точке выборки с фазовой ошибкой 6/16 единичного интервала.

При сравнении фиг. 3-4 с фиг. 12-13, CDR повышенного уровня уменьшает время конвергенции для двухуровневых сигналов NRZ с 51911 символов после 2,07 мкс до 2789 символов после 111,56 нс. Другими словами, CDR повышенного уровня осуществляет конвергенцию, по меньшей мере, в 18,5 раз быстрее. При сравнении фиг. 5-6 с фиг. 14-15, CDR повышенного уровня уменьшает время конвергенции для четырехуровневых сигналов PAM4 с 7537 символов после 301,48 нс до 2936 символов после 117,44 нс. Другими словами, CDR повышенного уровня осуществляет конвергенцию, по меньшей мере, в 2,5 раза быстрее.

На фиг. 16 представлена блок-схема последовательности выполнения операций способа 1600 осуществления CDR повышенного уровня в соответствии с вариантом осуществления раскрытия. Приемник 700 выполняет способ 1600. На этапе 1610 принимают сигнал. Например, PD 710 принимает оптический сигнал. На этапе 1620 сигнал выравнивается, используя CDR повышенного уровня. Например, после того, как PD 710, TIA 715 и ADC 725 преобразуют оптический сигнал в цифровой сигнал, подсистема 730 CDR выполняет CDR, в том числе, FFE, как описано выше. При этом, подсистема 730 CDR адаптивно обновляет веса ответвлений. В качестве первого примера, подсистема 730 CDR выполняет CDR двухуровневого сигнала NRZ, используя трехуровневое выравнивание. В качестве второго примера, подсистема 730 CDR выполняет CDR четырехуровневого сигнала PAM4, используя семиуровневое выравнивание. На этапе 1630 вычисляют MSE. Например, устройство 744 вычисления ошибки вычисляет MSE ошибки выравнивания. На этапе 1640 ромба с принятием решения определяют, является ли MSE меньше порога. Например, пороговый компаратор 742 ошибки определяет, является ли MSE меньше порога, описанного выше. Если нет, то способ 1600 возвращается к этапу 1630. Если да, то способ переходит к этапу 1650. Наконец, на этапе 1650 выполняют PR-MLSE и декодирование. Например, компонент 755 PR-MLSE выполняет PR-MLSE и декодер 760 выполняет декодирование.

На фиг. 17 представлена блок-схема последовательности выполнения операций способа 1700 осуществления CDR повышенного уровня в соответствии с другим вариантом осуществления раскрытия. Приемник 700 выполняет способ 1700. На этапе 1710 оптический сигнал в первом формате модуляции преобразуется в аналоговый электрический сигнал. Например, PD 710 преобразует оптический сигнал в сигнал электрического тока и TIA 715 преобразует сигнал электрического тока в сигнал усиленного напряжения, который является аналоговым электрическим сигналом. На этапе 1720 аналоговый электрический сигнал преобразуется в первый цифровой сигнал. Например, ADC 725 преобразует этот аналоговый электрический сигнал в первый цифровой сигнал на первом уровне. На этапе 1730 первый цифровой сигнал выравнивается во второй цифровой сигнал со вторым форматом модуляции. Например, подсистема 730 CDR выравнивает первый цифровой сигнал во второй цифровой сигнал на втором уровне. Второй формат модуляции имеет больше уровней, чем первый формат модуляции. Наконец, на этапе 1740 CDR выполняется для второго цифрового сигнала. Например, подсистема 730 CDR выполняет CDR для второго цифрового сигнала.

В примерном варианте осуществления устройство содержит: OE-элемент, выполненный с возможностью преобразования оптического сигнала в первом формате модуляции в аналоговый электрический сигнал; элемент ADC, связанный с OE-элементом и выполненный с возможностью преобразования аналогового электрического сигнала в первый цифровой сигнал; и элемент CDR, связанный с OE-элементом и выполненный с возможностью выравнивания первого цифрового сигнала во второй цифровой сигнал со вторым форматом модуляции, где второй формат модуляции имеет больше уровней, чем первый формат модуляции; и выполнения CDR для второго цифрового сигнала.

Первый компонент напрямую связывается со вторым компонентом, когда между первым компонентом и вторым компонентом отсутствуют промежуточные компоненты, за исключением линии, трассы или другой среды. Первый компонент косвенно связывается со вторым компонентом, когда между первым компонентом и вторым компонентом существуют промежуточные компоненты, отличные от линии, трассы или другой среды. Термин “связывается” и его варианты содержит как прямое связывание, так и косвенное связывание. Использование термина “приблизительно” означает диапазон ±10% включительно от следующего за ним количества, если не установлено иначе.

Хотя в настоящем раскрытии были представлены несколько вариантов осуществления, следует понимать, что раскрытые системы и способы могут быть реализованы во многих других конкретных формах, не отступая от сущности или объема настоящего раскрытия. Представленные примеры должны рассматриваться как иллюстративные, а не как ограничительные, и идея не должна ограничиваться приведенными здесь подробностями. Например, различные элементы или компоненты могут объединяться или интегрироваться в другой системе или некоторые признаки могут быть пропущены или не реализовываться.

Кроме того, технологии, системы, подсистемы и способы, описанные и показанные в различных вариантах осуществления как дискретные или отдельные, могут объединяться или интегрироваться с другими системами, блоками, технологиями или способами, не отступая от объема настоящего раскрытия. Другие позиции, показанные или обсуждавшиеся как связанные или напрямую связанные или осуществляющие связь друг с другом, могут электрически, механически или как-либо иначе быть косвенно связаны или осуществлять связь через какой-либо интерфейс, устройство или промежуточный компонент. Другие примеры изменений, замен и перемен могут вводиться специалистами в данной области техники и могут осуществляться, не отступая от раскрытых здесь сущности и объема защиты.

Изобретение относится к системам предоставления сетевого доступа на конечном участке сети связи. Технический результат заключается в обеспечении восстановления данных и синхронизации (CDR) повышенного уровня в пассивных оптических сетях. Устройство содержит оптико-электрический (optical-to-electrical, OE) компонент, выполненный с возможностью преобразования оптического сигнала в первом формате модуляции в аналоговый электрический сигнал, аналого-цифровой преобразователь (analog-to-digital converter, ADC), связанный с OE-компонентом и выполненный с возможностью преобразования аналогового электрического сигнала в первый цифровой сигнал и подсистему восстановления синхронизации и данных (clock and data recovery, CDR), связанную с OE-компонентом и выполненную с возможностью выравнивания первого цифрового сигнала во второй цифровой сигнал со вторым форматом модуляции, в которой второй формат модуляции имеет больше уровней, чем первый формат модуляции и выполнения CDR для второго цифрового сигнала. 3 н. и 17 з.п. ф-лы, 17 ил.

1. Устройство, содержащее:

оптико-электрический (optical-to-electrical, OE) компонент, выполненный с возможностью преобразования оптического сигнала в первом формате модуляции в аналоговый электрический сигнал;

аналого-цифровой преобразователь (analog-to-digital converter, ADC), связанный с OE-компонентом и выполненный с возможностью преобразования аналогового электрического сигнала в первый цифровой сигнал; и

подсистема восстановления синхронизации и данных (clock and data recovery, CDR), связанная с OE-компонентом и выполненная с возможностью:

выравнивания первого цифрового сигнала во второй цифровой сигнал со вторым форматом модуляции, в которой второй формат модуляции имеет больше уровней, чем первый формат модуляции; и

выполнения CDR для второго цифрового сигнала.

2. Устройство по п. 1, дополнительно содержащее компонент оценки последовательности с максимальной вероятностью для парциального отклика (partial response maximum-likelihood sequence estimation, PR-MLSE), связанный с подсистемой CDR и выполненный с возможностью выравнивания второго цифрового сигнала в третий электрический сигнал в первом формате модуляции.

3. Устройство по п. 2, в котором компонент PR-MLSE дополнительно выполнен с возможностью выравнивания второго цифрового сигнала, используя PR-MLSE.

4. Устройство по п. 2, в котором подсистема CDR содержит выравниватель прямого действия (feed-forward equalizer, FFE), компонент принятия решения, вычитающее устройство и устройство обновления весов ответвлений, которые образуют контур обратной связи, и в котором компонент PR-MLSE находится вне контура обратной связи.

5. Устройство по любому из пп. 1-4, в котором первый формат модуляции имеет два уровня сигнала без возврата к нулю (non-return-to-zero, NRZ), а второй формат модуляции имеет три уровня.

6. Устройство по любому из пп. 1-5, в котором первый формат модуляции имеет четыре уровня для сигнала с четырехуровневой амплитудно-импульсной модуляцией (four-level pulse-amplitude modulation, PAM4), а второй формат модуляции имеет семь уровней.

7. Устройство по любому из пп. 1-6, в котором подсистема CDR содержит выравниватель прямого действия (feed-forward equalizer, FFE), выполненный с возможностью:

выполнения CDR для регулирования фазы; и

выполнения выравнивания для компенсации межсимвольной помехи (inter-symbol interference, ISI).

8. Устройство по п. 7, в котором FFE дополнительно выполнен с возможностью адаптивного слежения за смещением частоты и джиттером.

9. Устройство по пп. 1-8, в котором подсистема CDR дополнительно выполнена с возможностью осуществления выравнивания до тех пор, пока среднеквадратичная ошибка (mean square error, MSE) выровненного сигнала не станет ниже заданного порога.

10. Устройство по любому из пп. 1-9, в котором устройство является терминалом оптической линии (optical line terminal, OLT) и в котором аналоговый электрический сигнал является сигналом в пакетном режиме.

11. Устройство по любому из пп. 1-10, в котором OE-компонент является фотодиодом (photodiode, PD), усилителем напряжения, управляемым током, (transimpedance amplifier, TIA) или сочетанием PD и TIA.

12. Устройство, содержащее:

подсистему восстановления синхронизации и данных (clock and data recovery, CDR), содержащую:

выравниватель прямого действия (feed-forward equalizer, FFE);

компонент принятия решения, связанный с FFE;

вычитающее устройство, связанное с FFE и компонентом принятия решения; и

устройство обновления весов ответвлений, связанное с вычитающим устройством и FFE; и

компонент оценки последовательности с максимальной вероятностью для парциального отклика (partial response maximum-likelihood sequence estimation, PR-MLSE), связанный с подсистемой CDR.

13. Устройство по п. 12, дополнительно содержащее аналого-цифровой преобразователь (analog-to-digital converter, ADC), связанный с подсистемой CDR.

14. Устройство по п. 13, дополнительно содержащее генератор, управляемый напряжением (voltage-controlled oscillator, VCO), связанный с ADC.

15. Устройство по п. 14, дополнительно содержащее усилитель напряжения, управляемый током (transimpedance amplifier, TIA), связанный с ADC.

16. Устройство по п. 15, дополнительно содержащее фотодиод (photodiode, PD), связанный с TIA.

17. Устройство по п. 16, дополнительно содержащее декодер, связанный с компонентом PR-MLSE.

18. Способ, содержащий этапы, на которых:

преобразуют оптический сигнал в первом формате модуляции в аналоговый электрический сигнал;

преобразуют аналоговый электрический сигнал в первый цифровой сигнал;

выравнивают первый цифровой сигнал во второй цифровой сигнал со вторым форматом модуляции, где второй формат модуляции имеет больше уровней, чем первый формат модуляции; и

выполняют восстановление синхронизации и данных (clock and data recovery, CDR) для второго цифрового сигнала.

19. Способ по п. 18, дополнительно содержащий выравнивание второго цифрового сигнала в третий электрический сигнал в первом формате модуляции, используя оценку последовательности с максимальной вероятностью для парциального отклика (PR-MLSE).

20. Способ по любому из пп. 18, 19, дополнительно содержащий этап, на котором выполняют выравнивание до тех пор, пока среднеквадратичная ошибка (MSE) выровненного сигнала не станет ниже заданного порога.

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| US 9184906 B1, 10.11.2015 | |||

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| СПОСОБ И СХЕМА СИНХРОННОГО ПРИЕМА ПРИ ВЫСОКОСКОРОСТНОЙ ПЕРЕДАЧЕ ДАННЫХ ОТ АБОНЕНТА НА ЦЕНТРАЛЬНЫЙ УЗЕЛ В СИСТЕМЕ ОПТИЧЕСКОЙ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2271069C2 |

Авторы

Даты

2021-05-21—Публикация

2017-12-06—Подача