Изобретение в общем случае относится к производству структур на подложках в результате мокрого осаждения. Оно делает возможным использование мокрого осаждения в том смысле, что оно позволяет избежать возникновения коротких замыканий между электропроводящими слоями для достижения приемлемых выхода и надежности даже при наличии на подложке относительно крупных частиц или неоднородности.

В частности, изобретение относится к изготовлению так называемых объединительных панелей или структур на таких объединительных панелях, в частности, для изготовления плоскопанельных дисплеев (FPD).

Говоря более конкретно, изобретение относится к осаждению на подложке первого диэлектрического слоя путем мокрого осаждения, причем на первом диэлектрическом слое осаждают первый электропроводящий слой, на нем путем мокрого осаждения осаждают второй диэлектрический слой, а на нем осаждают второй электропроводящий слой.

Использование объединительных панелей хорошо известно при производстве FPD. Объединительная панель состоит из массива элементов изображения («пикселей»), формирующих активную матрицу. Каждый элемент изображения образован запоминающим конденсатором и по меньшей мере одним полевым транзистором FET, которые небезусловным образом образованы из органических или неорганических полупроводниковых и диэлектрических материалов. Объединительная панель с активной матрицей на основе FET может быть подвергнута переработке на гибкой подложке.

Использование объединительных панелей хорошо известно при производстве дисплеев на основе электронной бумаги (EPD), дисплеев на органических светодиодах (OLED), жидкокристаллических дисплеев (LCD) или других печатных плат.

Для изготовления таких продуктов на объединительную панель наносят специфические для продукта структуры. В принципе могут быть использованы печать или нанесение структурного покрытия. Это технологические процессы, которые действуют из влажной фазы, то есть, используют жидкий материал для структурирования, например, чернильно-струйная печать или центрифугирование.

Технологические процессы мокрого структурирования могут быть осуществлены при низких издержках и с достаточной точностью.

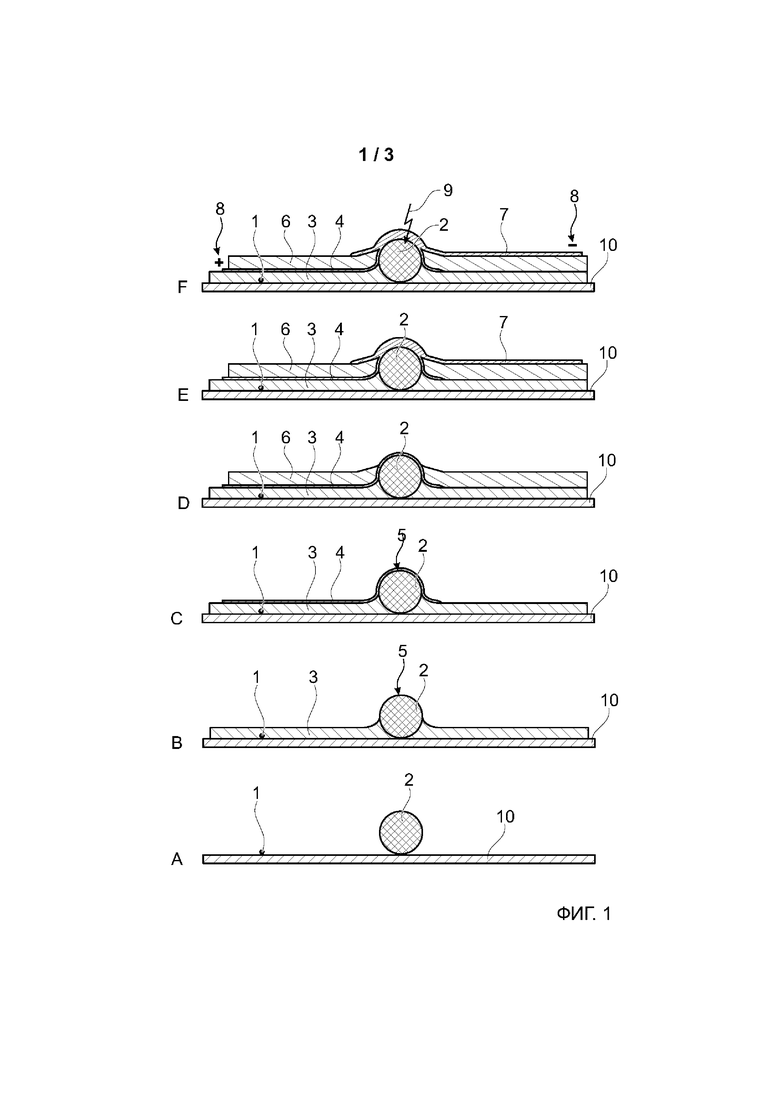

Преимущества и недостатки использования разъясняются ниже при обращении к фиг. 1.

Преимущество технологических процессов мокрого осаждения заключается в возможности выравнивания данными слоями мелкой топографии. Маленькие частицы 1 могут быть полностью покрыты, как это продемонстрировано на левой стороне фиг. 1. Недостаток заключается в том, что частицы 2, более крупные, чем толщина слоя 3, после последующего высушивания осажденной влажной пленки, выступают наружу из данного слоя, как это продемонстрировано в середине фиг. 1В. Это обуславливается обтеканием материалом жидкого покрытия слоя 3 более крупных частиц 2 до высушивания и/или усадкой материала покрытия во время высушивания, что, тем самым, приводит к утрате толщины и высвобождению частицы 2.

Обычно слой 3 осаждают в качестве первого диэлектрического слоя 3 при использовании такого технологического процесса мокрого осаждения. На первый диэлектрический слой 3 осаждают первый электропроводящий слой 4, обычно при использовании технологических процессов напыления. Такой первый электропроводящий слой 4 конформно покрывает топографию поверхности, то есть, как поверхность первого диэлектрического слоя 3, так и непокрытую обнаженную поверхность 5 более крупной частицы 2, как это продемонстрировано на фиг. 1С.

Осаждают второй диэлектрический слой 6, также осажденный при использовании мокрых технологических процессов. В данном случае существует та же самая проблема, что и описанная выше, которая заключается также в невозможности покрытия вторым диэлектрическим слоем крупной частицы или неоднородности, обусловленной данной частицей, как это продемонстрировано на фиг. 1D. Это обуславливает непокрытость и обнаженность первого электропроводящего слоя 4 поверх крупной частицы 2.

Теперь при осаждении второго электропроводящего слоя 7 для обеспечения конкретной функции опять-таки обычно при использовании технологического процесса напыления данный второй электропроводящий слой 7 вступает в контакт с первым электропроводящим слоем 4, как это продемонстрировано на фиг. 1Е.

При приложении теперь между первым электропроводящим слоем 4 и вторым электропроводящим слоем 7 электрического напряжения 8, как это продемонстрировано на фиг. 1F, в результате происходит короткое замыкание 9. Структура на подложке 10 является непригодной для использования. Если подложка 10 представляет собой основу для объединительной панели, может быть повреждена вся объединительная панель. Если сама подложка является объединительной панелью, последовательность слоев, нанесенная данным образом, может привести к утрате FPD.

Вследствие невозможности исключения присутствия крупных частиц 2 и стимулирования возникновения описанных выше проблем при использовании мокрого осаждения, использование мокрого осаждения не является экономически обоснованным.

По этой причине цель изобретения заключается в обеспечении возможности использования мокрого осаждения в том смысле, что оно позволяет избежать возникновения коротких замыканий между электропроводящими слоями для достижения приемлемых выхода и надежности даже при наличии на подложке относительно крупных частиц или неоднородности.

Достижения цели изобретения добиваются при использовании способа изготовления структур на подложках при использовании мокрого осаждения, в котором первый диэлектрический слой осаждают на подложке путем мокрого осаждения осаждают. На первый диэлектрический слой осаждают первый электропроводящий слой, а на него осаждают второй диэлектрический слой путем мокрого осаждения. На него осаждают второй электропроводящий слой. Изобретательский уровень в данном способе заключается в осаждении диэлектрического промежуточного слоя между первым диэлектрическим слоем и вторым электропроводящим слоем при использовании технологического процесса сухого осаждения.

Промежуточный слой может быть осажден при использовании технологического процесса химического осаждения из паровой фазы (CVD), технологического процесса физического осаждения из паровой фазы (PVD) или технологического процесса осаждения полимеров из паровой фазы (PVPD). Также возможны и другие технологические процессы сухого осаждения, если они удовлетворяют условию, заключающемуся в том, что промежуточный слой должен быть нанесен конформно (то есть, промежуточный слой будет покрывать всю поверхность) и необходимости отсутствия точечных дефектов.

Изобретение может быть использовано по множеству вариантов.

В одном варианте осуществления изобретения предлагается осаждение слоев на подложке для изготовления объединительной панели.

В еще одном варианте осуществления слои могут быть осаждены на объединительной панели для изготовления плоскопанельного дисплея (FDP).

В еще одном варианте осуществления изобретения предлагается возможность осаждения слоев для изготовления дисплеев на основе электронной бумаги (EPD), дисплеев на органических светодиодах (OLED), жидкокристаллических дисплеев (LCD).

В еще одном варианте осуществления промежуточный слой состоит из парилена (поли-пара-ксилилен), например парилена-С. Однако также возможными являются и парилен-N или парилен-F. Поэтому в последующем изложении в общем случае будет упоминаться только парилен. Поэтому промежуточный слой может быть осажден в виде парилена при использовании технологического процесса PVPD. В стандартных условиях изготовления FPD данный технологический процесс PVPD является недоступным. В данном случае париленовый технологический процесс может быть замещен технологическим процессом PVD или CVD, как это упоминалось выше. Поэтому в одном варианте осуществления изобретения предлагается возможность осаждения промежуточного слоя в виде нитрида кремния, а в еще одном варианте осуществления изобретения предлагается возможность осаждения промежуточного слоя в виде диоксида кремния. В любом случае промежуточный слой должен быть нанесен в виде конформного покрытия и должен быть свободным от точечных дефектов.

Изобретение должно быть описано более подробно при использовании одного примера. На прилагающихся чертежах демонстрируются:

фиг. 1 - проблема с возможным использованием мокрого осаждения в соответствии с описанием в начале данного описания изобретения;

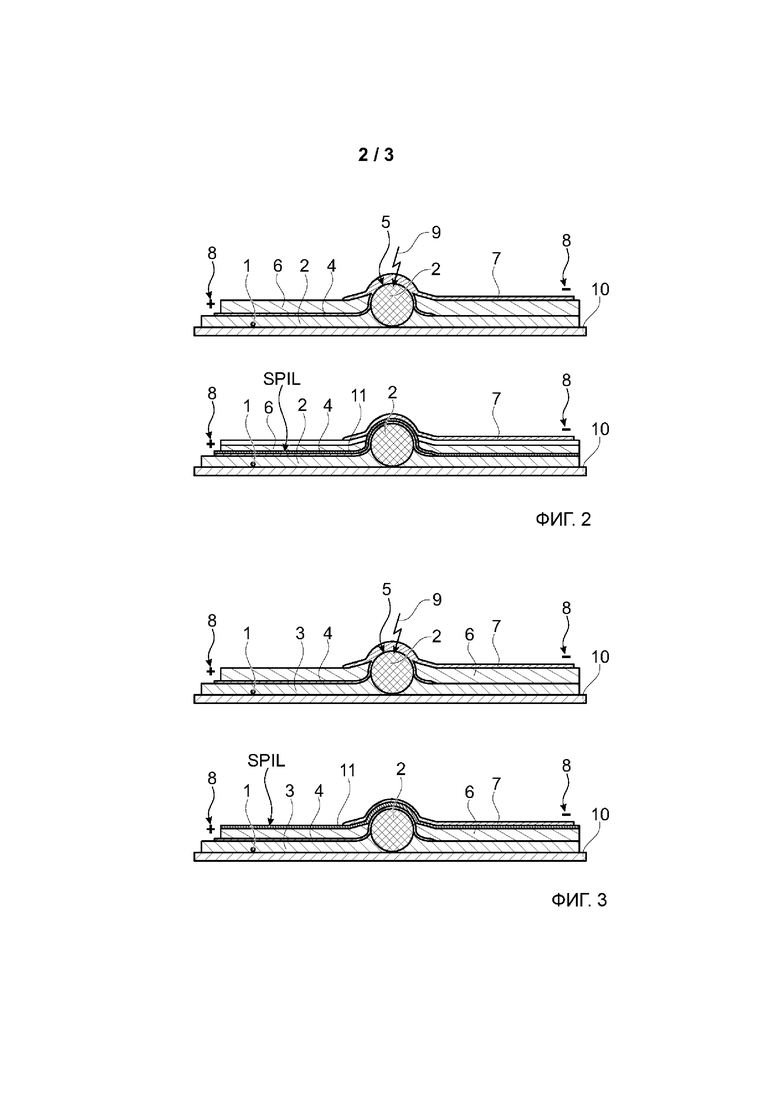

фиг. 2 - компоновка в соответствии с изобретением с промежуточным слоем, расположенным выше первого проводящего слоя, в сопоставлении с компоновкой не в соответствии с изобретением (верхняя часть чертежа) для крупной частицы;

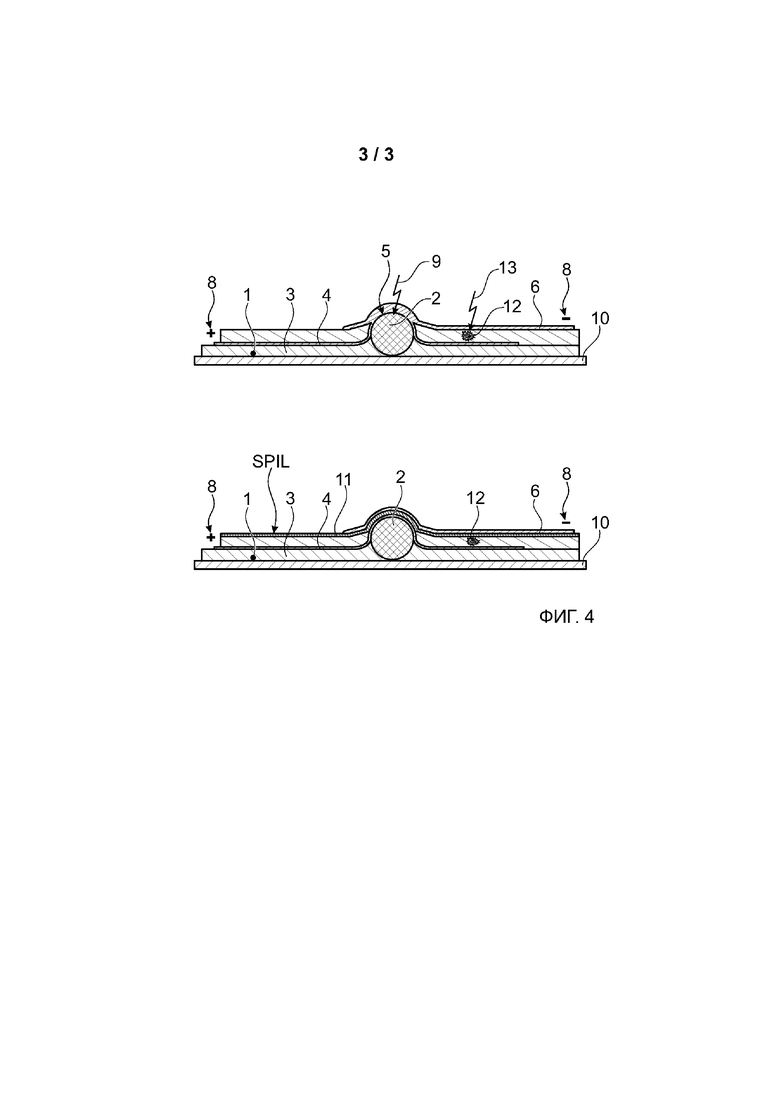

фиг. 3 - компоновка в соответствии с изобретением с промежуточным слоем, расположенным ниже второго проводящего слоя, в сопоставлении с компоновкой не в соответствии с изобретением (верхняя часть чертежа) для крупной частицы; и

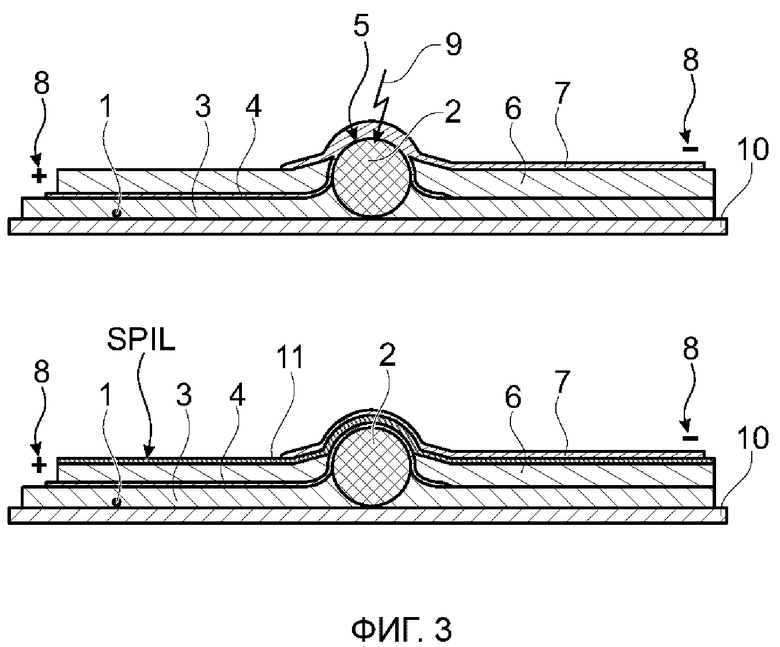

фиг. 4 - компоновка в соответствии с изобретением с промежуточным слоем, расположенным ниже второго проводящего слоя, в сопоставлении с компоновкой не в соответствии с изобретением (верхняя часть чертежа) для электропроводящей частицы.

Основной признак изобретения заключается во введении диэлектрического промежуточного слоя 11.

Промежуточный слой 11 (конкретно обозначенный на фиг. 2-4 как «SPIL» = промежуточный слой для защиты от короткого замыкания) позволяет избежать возникновения непосредственного контакта между первым электропроводящим слоем 4 и вторым электропроводящим слоем 7 и, тем самым, улучшает выход при производстве и надежность продукта.

В отличие от полученных в результате мокрого осаждения диэлектрических слоев 3 и 6 данный промежуточный слой 11 должен быть осажден конформно. Это подразумевает покрывание промежуточным слоем 11 топографии при однородной толщине. Обычно материалы промежуточного слоя 11 осаждают при использовании технологических процессов PVD или CVD.

В общем случае промежуточный слой 11 формируют между первым диэлектрическим слоем 3 и вторым электропроводящим слоем 7 при использовании технологического процесса сухого осаждения. Как это продемонстрировано на фиг. 2, промежуточный слой 11 может быть расположен непосредственно выше нижнего первого электропроводящего слоя 4. Еще одна возможность демонстрируется на фиг. 3 и фиг. 4, где промежуточный слой 11 расположен непосредственно ниже верхнего проводящего слоя 7.

Если промежуточный слой 11 формируют непосредственно ниже верхнего второго электропроводящего слоя 7, во избежание возникновения короткого замыкания может быть эффективно изолирована и электропроводящая частица 12, также способная стимулировать возникновение короткого замывания 13.

Промежуточный слой для защиты от короткого замыкания (SPIL) 11 может быть использован для улучшения выхода и надежности объединительных панелей на органических тонкопленочных транзисторах (oTFT) и других электронных продуктов, которые в основном изготавливают при использовании технологических процессов мокрого нанесения покрытия. В данном примере промежуточный слой 11 может состоять из парилена, осажденного при использовании технологического процесса PVPD.

Парилен относится к группе инертных, гидрофобных, оптически прозрачных, полимерных материалов для нанесения покрытий, характеризующихся наличием широкого спектра промышленных областей применения. Покрытие наносят на подложку в вакууме в результате повторного сублимирования из газовой фазы в виде свободной от пор и прозрачной полимерной пленки.

Но подходящими для использования являются и другие диэлектрические материалы, осажденные при использовании других технологических процессов, в случае удовлетворения условиям как нанесения конформного покрытия из промежуточного слоя 11, так и отсутствия у него точечных дефектов.

Ссылочные позиции

1 маленькая частица

2 крупная частица

3 слой, первый диэлектрический слой

4 первый электропроводящий слой

5 обнаженная поверхность

6 второй диэлектрический слой

7 второй электропроводящий слой

8 напряжение

9 короткое замыкание

10 подложка

11 промежуточный слой

12 электропроводящая частица

13 короткое замыкание.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННОЕ ПЕРЕКЛЮЧАЮЩЕЕ УСТРОЙСТВО И СПОСОБ ИЗГОТОВЛЕНИЯ ЭТОГО УСТРОЙСТВА | 2008 |

|

RU2475893C2 |

| ЭЛЕКТРИЧЕСКАЯ СБОРКА С ПОКРЫТИЕМ | 2013 |

|

RU2620413C2 |

| ЭЛЕКТРОЛЮМИНЕСЦЕНТНАЯ СИСТЕМА И СПОСОБ | 2017 |

|

RU2763376C2 |

| СЛОИ ДЛЯ МИНИМИЗАЦИИ ВЛИЯНИЯ ДЕФЕКТОВ В ЭЛЕКТРОХРОМНЫХ УСТРОЙСТВАХ | 2014 |

|

RU2647998C2 |

| КАТОДОЛЮМИНЕСЦЕНТНЫЙ ЭКРАН И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1999 |

|

RU2152662C1 |

| ЭЛЕКТРОЛЮМИНЕСЦЕНТНЫЕ УСТРОЙСТВА И ИХ ИЗГОТОВЛЕНИЕ | 2013 |

|

RU2639294C2 |

| СПОСОБЫ И АППАРАТ ДЛЯ ФОРМИРОВАНИЯ ПЕЧАТНЫХ АККУМУЛЯТОРОВ НА ОФТАЛЬМОЛОГИЧЕСКИХ УСТРОЙСТВАХ | 2013 |

|

RU2620401C2 |

| ПОДЛОЖКА ДИСПЛЕЯ И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 2019 |

|

RU2759445C1 |

| СИСТЕМА И СПОСОБ ЗАЩИТЫ МИКРОСТРУКТУРЫ МАТРИЦЫ ОТОБРАЖЕНИЯ С ИСПОЛЬЗОВАНИЕМ ПРОКЛАДОК В ЗАЗОРЕ ВНУТРИ УСТРОЙСТВА ОТОБРАЖЕНИЯ | 2005 |

|

RU2383043C2 |

| ИНТЕНСИВНО ОКРАШЕННЫЕ И/ИЛИ ОПТИЧЕСКИ ИЗМЕНЯЮЩИЕСЯ ПИГМЕНТЫ С ЭЛЕКТРОПРОВОДЯЩИМ ЯДРОМ | 2008 |

|

RU2506294C2 |

Изобретение относится к способу изготовления структурного покрытия на подложке для защиты подложки от короткого замыкания. Первый диэлектрический слой осаждают на подложке путем мокрого осаждения. На первом диэлектрическом слое осаждают первый электропроводящий слой. На нем осаждают второй диэлектрический слой путем мокрого осаждения, а на нем осаждают второй электропроводящий слой. Диэлектрический промежуточный слой осаждают между первым диэлектрическим слоем и вторым электропроводящим слоем при использовании технологического процесса сухого осаждения. Обеспечивается возможность использования мокрого осаждения без возникновения коротких замыканий между электропроводящими слоями для достижения приемлемых выхода и надежности даже при наличии на подложке относительно крупных частиц или неоднородности. 10 з.п. ф-лы, 4 ил., 1 пр.

1. Способ изготовления структурного покрытия на подложке для защиты подложки от короткого замыкания, в котором первый диэлектрический слой (3) осаждают на подложке (10) путем мокрого осаждения, на первом диэлектрическом слое (3) осаждают первый электропроводящий слой (4), на нем осаждают второй диэлектрический слой (6) путем мокрого осаждения, а на нем осаждают второй электропроводящий слой (7), отличающийся тем, что диэлектрический промежуточный слой (11) осаждают между первым диэлектрическим слоем (3) и вторым электропроводящим слоем (7) при использовании технологического процесса сухого осаждения.

2. Способ по п. 1, отличающийся тем, что диэлектрический промежуточный слой (11) осаждают при использовании технологического процесса химического осаждения из паровой фазы (CVD).

3. Способ по п. 1, отличающийся тем, что диэлектрический промежуточный слой (11) осаждают при использовании технологического процесса физического осаждения из паровой фазы (PVD).

4. Способ по п. 1, отличающийся тем, что диэлектрический промежуточный слой (11) осаждают при использовании технологического процесса осаждения полимеров из паровой фазы (PVPD).

5. Способ по любому из пп. 1-4, отличающийся тем, что слои (3; 4; 6; 11; 7) осаждают на подложку (10) для изготовления объединительной панели.

6. Способ по любому из пп. 1-4, отличающийся тем, что слои (3; 4; 6; 11; 7) осаждают на подложку (10) в виде объединительной панели.

7. Способ по п. 6, отличающийся тем, что слои (3; 4; 6; 11; 7) осаждают для изготовления плоскопанельного дисплея (FPD).

8. Способ по п. 7, отличающийся тем, что слои (3; 4; 6; 11; 7) осаждают для изготовления дисплеев на основе электронной бумаги (EPD), дисплеев на органических светодиодах (OLED) или жидкокристаллических дисплеев (LCD).

9. Способ по любому из пп. 1-8, отличающийся тем, что диэлектрический промежуточный слой (11) состоит из парилена.

10. Способ по любому из пп. 1-8, отличающийся тем, что диэлектрический промежуточный слой (11) осаждают в виде нитрида кремния.

11. Способ по любому из пп. 1-8, отличающийся тем, что диэлектрический промежуточный слой (11) осаждают в виде диоксида кремния.

| US 6891327 B2, 10.05.2005 | |||

| ОРГАНИЧЕСКИЙ СВЕТОИЗЛУЧАЮЩИЙ ДИОД СО СЛОЕМ МОДИФИКАЦИИ ПОВЕРХНОСТИ | 2015 |

|

RU2663085C2 |

| ЭЛЕКТРОННОЕ ПЕРЕКЛЮЧАЮЩЕЕ УСТРОЙСТВО И СПОСОБ ИЗГОТОВЛЕНИЯ ЭТОГО УСТРОЙСТВА | 2008 |

|

RU2475893C2 |

| Устройство для определения продолжительности протекания физико-химических, производственных и тому подобных процессов | 1933 |

|

SU32219A1 |

| JP 2002348680 A, 04.12.2002 | |||

| KR 20010032312 A, 16.04.2001. | |||

Авторы

Даты

2021-12-01—Публикация

2020-08-11—Подача