Настоящее изобретение относится к многоканальным системам сигнальной обработки, в которых для последовательного обмена данными используются синхронные протоколы I2S (Inter-IC Sound Bus) и SPI (Serial Peripheral Bus) и обеспечивается единая синхронизация обрабатываемых данных.

Популярность протоколов I2S и SPI обмена данными обусловлена их широким использованием для подключения различных типов микросхем к управляющим микроконтроллерам, микрокомпьютерам, мощным процессорным системам, а также тем, что многие аналого-цифровые преобразователи (АЦП) и цифро-аналоговые преобразователи (ЦАП) снабжаются интерфейсами, работающими на указанных протоколах. Так, подобные АЦП находят самое широкое применение при построении многоканальных систем, в составе которых используются микрофонные решетки, радиочастотные фазированные решетки, SDR (от Software Defined Radio, программно-определяемая радиосистема, или радио, определяемое программным обеспечением), многоканальные приемники для авиационной или железнодорожной связи, многоканальные когерентные приемники для систем высокоточной звуковой, ультразвуковой или радиопеленгации с нулевой или близкой к нулевой промежуточной частотой (Zero IF, или Near Zero IF), многоканальные приемники для радио мониторинга вещательных радиостанций и другое.

В перечисленных областях применения возникают две важные задачи. Первая задача заключается в объединении многочисленных последовательных цифровых потоков данных I2S или SPI в единый высокоуровневый сетевой интерфейс (чаще всего USB или Ethernet) для сопряжения с хост компьютером. Вторая задача заключается в сохранении временных соотношений между канальными сигналами или группами канальных сигналов.

Требование сохранения временных соотношений между канальными сигналами или группами канальных сигналов является особо важным, так как в перечисленных примерах применения временные (фазовые) соотношения между сигналами являются определяющими для качественных характеристик многоканальных систем.

Известными способами решения задачи преобразования синхронных последовательных цифровых потоков в асинхронный поток USB или Ethernet являются способы, основанные на применении микросхем IC FPGA (от Integrated Circuit Field-Programmable Gate Array) и IC FIFO (от Integrated Circuit First In First Out). Так, в статье «MICARRAY - A System for Multichannel Audio Streaming over Ethernet» авторов Christoph Reitbauer, Harald Rainer, Markus Noisternig, Bernhard Rettenbacher, Franz Graf, 5th Congress of Alps-Adria Acoustics Association, 12-14 September 2012, Petrčane, Croatia рассматривается использование FPGA Spartan-6 для объединения n количества потоков I2S, создаваемых n-АЦП микрофонной решетки.

Аналогичное техническое решение предлагается и в проекте «The NIST Smart Space Project-Microphone Array» (см. в сети Интернет https://www.nist.gov/itl/iad/mig/nist-smart-space-project/nist-smart-space-project-microphone-array), разработанном в National Institute of Standards and Technology, US Department of Commerce, 2016.

В статье «An Universal USB 3.0 FIFO Interface For Data Acquisition» автора K. Mroczek, Measurement Automation Monitoring, Dec.2016, vol.62, ISSN 2450-2855 рассматривается возможность сбора различных данных, получаемых от n-АЦП, с помощью IC FIFO. Анализируются микросхемы IC двух производителей: FTDI (Future Technology Devices International) - FT601Q и Cypress Semiconductor - SuperSpeed FX3.

Использование буферных IC FIFO для объединения нескольких потоков I2S или SPI раскрыто в патенте США US9,842,071 «Multi-Channel I2S Transmit control System and Method» для реализации процедуры ввода потока цифровых данных в микроконтроллер. Недостатком этого решения является обеспечение синхронизации между данными разных каналов только в рамках одного микроконтроллера, имеющего ограниченное количество встроенных FIFO. При необходимости увеличения количества объединяемых каналов с использованием группы микроконтроллеров возникает проблема синхронизации канальных потоков данных, принадлежащих разным микроконтроллерам.

Известны также способы и устройства фирмы XMOS, основанные на использовании серии IC xCore - многоядерных многопоточных контроллерах (см., например, Руководство по применению “Multichannel Digital Audio Connectivity», Document Number: XM10299A, XMOS, 2016. “USB Audio Design Guide”, Document Number: XM0088546.1, XMOS, 2016). Указанные IC обеспечивают преобразование входных и выходных потоков I2S в интерфейс USB 2.0.

Другим известным решением, раскрытым в заявке на патент США US2013/0223259 «Simultaneous Data Packet Processing», является пакетный контроллер, имеющий в своем составе 16 приемных каналов квадратурных I/Q сигналов с низкой промежуточной частотой (Low IF). Объединение оцифрованных данных, поступающих с АЦП по интерфейсу SPI, происходит с помощью микросхемы FPGA, снабженной контроллером USB для подключения к хост компьютеру.

Общим недостатком перечисленных известных решений является ограниченное число каналов, в которых может быть обеспечен единый уровень временной задержки канальных сигналов при масштабировании портов USB/Ethernet от двух и более. Это связано с тем, что при объединении синхронных потоков I2S или SPI в асинхронные интерфейсы USB/Ethernet возникает плавающая задержка между данными, поступающими от разных портов USB/Ethernet. Существующие ограничения по количеству каналов в IC FPGA, FIFO, xCore, как правило, лимитируют количество возможных каналов в пределах 16, 24, 32, в которых обеспечивается единый уровень временной задержки.

Известны способ и устройство, обеспечивающие одинаковый уровень временной задержки в рамках одной IC FPGA, опубликованные в материалах конференции Audio Engineering Society, Yonghao Wang, Xiangyu Zhu and Qiang Fu «A low latency multichannel audio processing evaluation platform», 132nd Convention, Budapest, Hungary, 2012. Авторы анализируют 12-ти канальную систему с 24-битным кодированием при использовании цифровых фильтров разной архитектуры. Недостатком данного решения также является отсутствие возможности синхронизировать и выравнивать временные задержки в масштабируемых системах, в которых применяются более одной IC FPGA.

Известен способ определения времени задержки сигнала путем измерения взаимной корреляционной функции, связывающей сигналы на входе и выходе системы, опубл. в книге Бендат Дж., Пирсол А. Измерение и анализ случайных процессов: Пер. с англ. - М.: Мир, 1974. - 463 с. Отмечается, что поскольку сигнал на выходе системы смещен во времени относительно сигнала на входе, взаимная корреляционная функция будет иметь пик при значении сдвига, равном времени, которое необходимо для прохождения сигнала через данную систему. Это утверждение справедливо, потому что среднее значение произведения двух линейно связанных сигналов достигает максимума, когда сдвиг во времени между сигналами равен нулю. Следовательно, время задержки сигнала можно определить по значению сдвига, соответствующему наблюдаемому пику на взаимной коррелограмме, которая связывает сигналы на входе и выходе. Однако данный способ на практике удобен при больших значениях задержки сигнала и слабо приспособлен при его малых значениях.

Метод, при котором для калибровки канальных временных задержек вычисляются взаимно-корреляционные функции, описан в патенте США US5056051 «Signal Directional Finding Processor using Fast Fourier Transforms for Receiver matching». Недостатком этого метода является необходимость использования генератора шума и высокочастотного антенного переключателя для подачи калибровочного шумового напряжения на входы канальных приемников. Также возрастает нагрузка на процессорное устройство, обеспечивающее вычисление взаимно корреляционных функций.

Наиболее близким аналогом заявленного изобретения являются способ и система, реализующая этот способ, описанные в заявке на патент Китая CN109245841 «Multichannel FM broadcast audio information collecting device, method and system». Система включает в себя источник принимаемых сигналов (антенна, сплиттер), блок предварительной обработки (тюнер), 16 АЦП с цифровыми выходами в формате I2S, главный процессор, хост компьютер и тактовый генератор.

В известной системе-аналоге объединение потоков I2S или SPI осуществляется в главном процессоре (Primary Processor), реализованном на основе использования многоядерного многопоточного контроллера xCore, а временная синхронизация потоковых данных осуществляется только в рамках одного главного процессора.

При реализации системы из нескольких главных процессоров существенным недостатком ближайшего аналога является необходимость для синхронизации использовать дополнительный порт для приема данных главного процессора, что уменьшает и без того ограниченный ресурс по количеству объединяемых потоков, как и отмечается в самом патенте при описании Фиг.4. Тюнеры Si4731, используемые в блоках предварительной обработки, уже содержат в своем составе по два АЦП, однако авторы используют внешние дополнительные 8-канальные АЦП CS5368 с дополнительным временным уплотнением каналов (TDM Interface Format).

Другим недостатком известной системы является низкая используемая частота дискретизации 44,1 kHz, обусловленная ограниченной производительностью применяемого xCore главного процессора.

Техническая проблема, на решение которой направлена заявленная группа изобретений, заключается в синхронизации потоков данных в форматах I2S или SPI, получаемых от разных источников или групп источников сигналов в многоканальных каскадных конфигурациях с асинхронными интерфейсами без использования дополнительных отдельных портов главного процессора для временной синхронизации.

Технический результат, достигаемый при решении технической проблемы, заключается в снятии ограничения на количество полностью синхронизированных потоков данных в форматах I2S или SPI, то есть обеспечение возможности построения многоканальных систем с неограниченным количеством полностью синхронизированных потоков данных в форматах I2S или SPI, при одновременном упрощении системы и способа синхронизации и снижении требований к аппаратным ресурсам.

По сути, техническая проблема решается, а технический результат достигается за счет того, что заявленные система и способ синхронного объединения потоков данных в форматах I2S или SPI предполагают трансформацию стандартного тактового сигнала дискретизации Left/Right Clock (LRCK) формата I2S (далее также импульсный сигнал LRCK) или стандартного сигнала выбора микросхемы Chip Select (CS) формата SPI (далее также импульсный сигнал CS) в сигнал LRCLt, содержащий код временной метки, а также коды маркеров начала и конца импульсного сигнала соответственно LRCK или CS. Наличие кодов маркеров и временной метки позволяет в процессе программной обработки потоков данных восстановить импульсный сигнал соответственно LRCK или CS с привязкой значения каждой дискретной выборки к временной метке.

В виду идентичности сигнальных цепей как импульсного сигнала LRCK формата I2S, так и импульсного сигнала CS формата SPI, в дальнейшем в обозначениях на структурной схеме и временных диаграммах используется обозначение «LRCK/CS», указывающее на то, что в зависимости от формата сигнальная цепь может быть или LRCK или CS.

В частности, для реализации заявленного изобретения с достижением заявленного технического результата система объединения цифровых потоков, в частности, цифровых потоков синхронного протокола I2S или SPI в многоканальных каскадных конфигурациях с асинхронными интерфейсами, включает m канальных групп сбора синхронных данных в формате синхронного протокола I2S или SPI, тактовый генератор, хост процессор и средство трансформации импульсного сигнала LRCK или CS в сигнал LRCKt.

Каждая канальная группа сбора синхронных данных в формате синхронного протокола I2S или SPI включает средство предварительной обработки аналоговых сигналов, имеющее N входов для обработки сигналов, поступающих от N источников аналоговых сигналов, и N выходов, N/2 парных аналого-цифровых преобразователей (АЦП), каждый из которых имеет N входов, вход тактовой синхронизации потока данных, вход общей синхронизации, вход кадровой синхронизации и N/2 выходов, и главный процессор с асинхронным интерфейсом, имеющий N/2 входов и вход записи данных, причем N выходы средства предварительной обработки подключены к N входам N/2 АЦП, а N/2 выходов АЦП подключены к N/2 входам главного процессора.

Тактовый генератор содержит управляющий вход, первый выход, формирующий тактовый сигнал синхронизации потока данных BCLK (далее также тактовый сигнал BCLK), второй выход, формирующий служебный сигнал общей синхронизации MCLK, и третий выход, формирующий импульсный сигнал LRCK или CS.

Хост процессор содержит шину управления и по меньшей мере два асинхронных интерфейса, к которым соответственно подключены указанные по меньшей мере две канальные группы.

Средство трансформации импульсного сигнала LRCK или CS в сигнал LRCKt включает схему выделения фронта и спада импульсного сигнала LRCK или CS, регистр сдвига, имеющий вход сдвига данных, первую схему «И» и вторую схему «И», каждая из которых имеет первый вход управления, второй вход управления и цифровой выход, и двоичный счетчик, имеющий счетный вход, цифровые выходы.

Управляющий вход тактового генератора подключен к шине управления хост процессора. Первый выход тактового генератора подключен к входу тактовой синхронизации потока данных АЦП, входу записи данных главных процессоров и входу сдвига данных регистра сдвига. Второй выход тактового генератора подключен ко входам общей синхронизации АЦП. Третий выход тактового генератора подключен к входу кадровой синхронизации АЦП, входу схемы выделения фронта и спада импульсного сигнала LRCK или CS, первому входу управления первой схемы «И» и первому входу управления второй схем «И». Второй вход управления первой схемы «И» и второй вход управления второй схемы «И» выполнены с возможностью предварительной установки фиксированных кодов соответственно маркера начала Nstart и маркера конца Nend импульсного сигнала LRCK или CS. Цифровой выход первой схемы «И» подключен к младшим разрядам D0 регистра сдвига, цифровой выход второй схемы «И» подключен к старшим разрядам D2 регистра сдвига, а цифровой выход двоичного счетчика подключен к промежуточным разрядам D1 регистра сдвига. Выходу схемы выделения фронта и спада импульсного сигнала LRCK или CS подключен счетный вход двоичного счетчика и вход записи регистра сдвига.

Для реализации заявленного изобретения с достижением заявленного технического результата способ объединения цифровых потоков формата I2S, в частности, посредством указанной выше системы объединения цифровых потоков, включает получение массива аналоговых сигналов объемом mN, поступающих от m канальных групп сбора синхронных данных в формате синхронного протокола, где каждая канальная группа включает N аналоговых сигналов, предварительную обработку указанного массива аналоговых сигналов, направление обработанного массива аналоговых сигналов на парные АЦП и осуществление преобразования его в последовательный цифровой код в формате I2S с формированием N/2 цифровых потоков последовательных данных, направление указанных цифровых потоков последовательных данных на входы главного процессора с записью по фронту импульсов тактового сигнала BCLK, поступающих от тактового генератора, встраивание временной метки в импульсный сигнал LRCK и, после записи в регистр кодов Nstart, Nt и Nend под действием импульсов тактового сигнала BCLK на выходе регистра сдвига, формирование последовательности импульсов комплексного тактового сигнала LRCKt. При этом встраивание временной метки в импульсный сигнал LRCK включает трансформирование импульсного сигнала LRCK в сигнал LRCKt, при котором цифровой код временной метки создают двоичным счетчиком, по фронту импульсов производят запись кода временной метки Nt в регистр сдвига, а по спаду импульсов фиксируют изменение состояния двоичного счетчика, причем одновременно с записью кода временной метки Nt в регистр сдвига записывают маркеры начала Nstart и конца Nend импульсного сигнала LRCK только в моменты времени, когда импульсный сигнал LRCK имеет высокий уровень.

Для реализации заявленного изобретения с достижением заявленного технического результата способ объединения цифровых потоков формата SPI, в частности, посредством указанной выше системы объединения цифровых потоков, включает получение массива аналоговых сигналов объемом mN, поступающих от m канальных групп сбора синхронных данных в формате синхронного протокола, где каждая канальная группа включает N аналоговых сигналов, предварительную обработку указанного массива аналоговых сигналов, направление обработанного массива аналоговых сигналов на парные АЦП и осуществление преобразования его в последовательный цифровой код в формате SPI с формированием N/2 цифровых потоков последовательных данных, направление указанных цифровых потоков последовательных данных на входы главного процессора с записью по фронту импульсных сигналов CS, поступающих от тактового генератора, встраивание временной метки в импульсный сигнал CS и, после записи в регистр кодов Nstart, Nt и Nend под действием импульсов тактового сигнала BCLK на выходе регистра сдвига, формирование последовательности импульсов комплексного тактового сигнала LRCKt. При этом встраивание временной метки в импульсный сигнал CS включает трансформирование импульсного сигнала CS в сигнал LRCKt, при котором цифровой код временной метки создают двоичным счетчиком, по фронту импульсов производят запись кода временной метки Nt в регистр сдвига, а по спаду импульсов фиксируют изменение состояния двоичного счетчика, причем одновременно с записью кода временной метки Nt в регистр сдвига записывают маркеры начала Nstart и конца Nend импульсного сигнала CS только в моменты времени, когда импульсный сигнал CS имеет высокий уровень.

Указанная предварительная обработка массива аналоговых сигналов может включать, в частности, усиление, фильтрацию и преобразование в зависимости от свойств, присущих аналоговым сигналам.

Далее настоящее изобретение более подробно описывается на возможном варианте его осуществления со ссылками на фигуры.

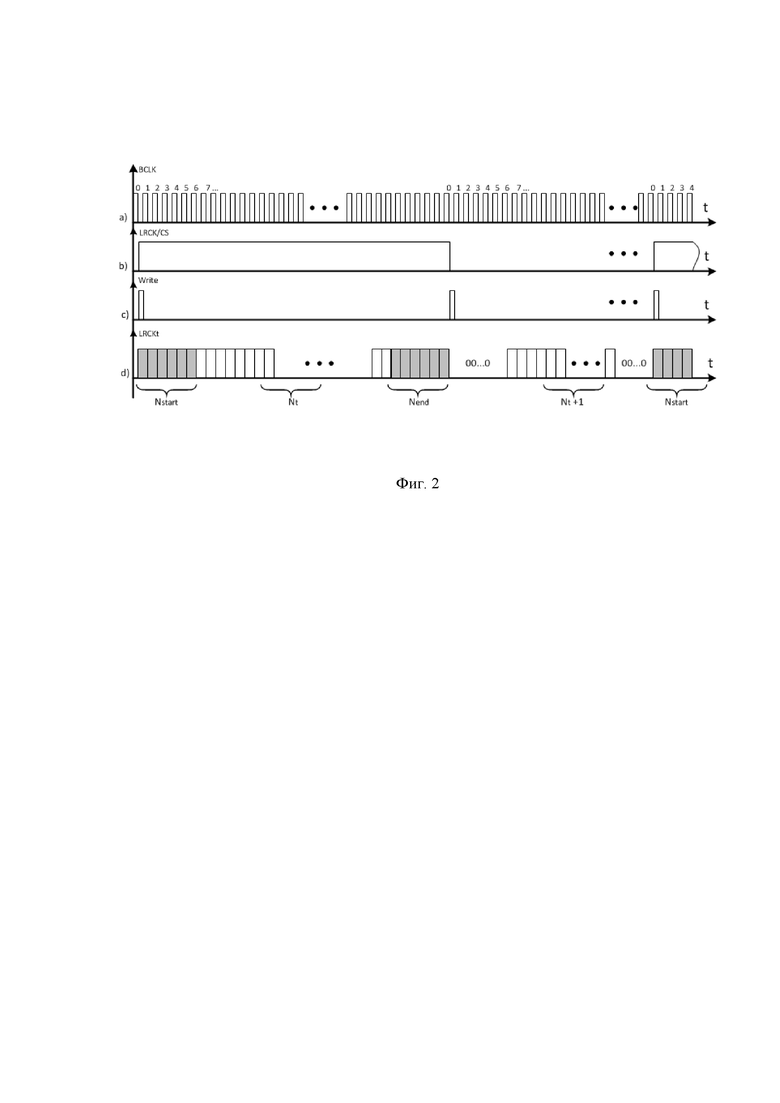

На фиг.1 представлена структурная схема системы для синхронного объединения цифровых I2S или SPI потоков в многоканальных каскадных конфигурациях с асинхронными интерфейсами.

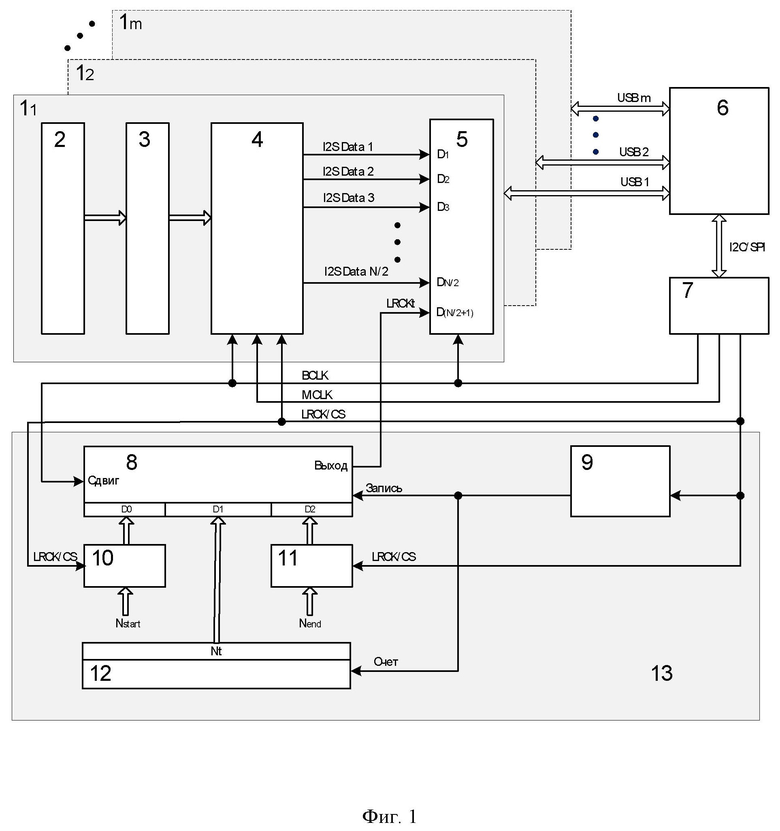

На фиг.2 представлены временные диаграммы, поясняющие работу системы для синхронного объединения цифровых I2S или SPI потоков в многоканальных каскадных конфигурациях с асинхронными интерфейсами.

Позициями на фигурах отмечены следующие элементы заявленной системы объединения цифровых потоков:

1 - группа каналов по N каналов в группе для сбора синхронных данных в формате I2S или SPI. Групповое деление (m групп) обусловлено ограниченными ресурсами существующих IC FIFO, FPGA, xCore, допускающих конфигурации, не превышающие 32 порта в одной группе;

2 - источники аналоговых сигналов. Ими могут быть, например, антенна с разветвителем (сплиттером) высокочастотных сигналов, группа антенн фазированной антенной решетки, группа микрофонов микрофонной решетки, группа антенн псевдодопплеровской системы пеленгации;

3 - средство предварительной обработки. Осуществляет выделение информационных сигналов, поступающих от источников аналоговых сигналов, с помощью фильтрации, дополнительного усиления, частотного преобразования, демодуляции. Используемые методы предварительной обработки аналоговых сигналов определяются характерными свойствами, присущими входящим аналоговым сигналам, и они хорошо известны специалисту. Например, для акустических сигналов могут использоваться процедуры усиления и фильтрации, для радиочастотных сигналов - усиление, фильтрация, частотное преобразование, демодуляция, декодирование, вторичная фильтрация, и так далее;

4 - парные аналого-цифровые преобразователи (АЦП). Осуществляют преобразование аналоговых сигналов в цифровой последовательный код в формате I2S или SPI;

5 - главный процессор. Служит для приема N/2 цифровых потоков данных, добавления к дискретным выборкам временной метки и преобразования модифицированных N/2 цифровых потоков с временными метками в асинхронный поток формата USB или Ethernet. Может быть реализован в виде IC FIFO, FPGA или xCore;

6 - хост процессор. Предназначен для приема асинхронных данных, поступающих от m канальных групп, декодирования их с помощью матричных алгоритмов и финальной обработки;

7 - программируемый тактовый генератор. Программируется по шине I2C или SPI хост процессором. Формирует все необходимые тактовые сигналы для работы системы, в частности:

a) тактовый сигнал дискретизации LRCK для потока формата I2S или сигнал выбора микросхемы CS для потока формата SPI с частотами 48 kHz, 96 kHz, 192 kHz, 394 kHz или 768 kHz, или других частот, применяемых для потока формата SPI;

b) тактовый сигнал синхронизации потока данных BCLK. Определяет битовую скорость потока последовательных данных потока формата I2S или SPI. Выбирается из условия:

FBCLK = fd⋅2k,

где FBCLK - тактовая частота потока данных тактового сигнала BCLK; fd = fLRCLK - частота дискретизации; k - количество разрядов АЦП. Например, при частоте дискретизации 48 kHz для 32-разрядного кодирования тактовая частота потока данных составит 3072 kHz;

c) служебный тактовый сигнал общей синхронизации работы АЦП. Задается в спецификации на АЦП, обычно имеет значение 24576 kHz или 49152 kHz;

8 - регистр сдвига. Предназначен для трансформации стандартного импульсного сигнала LRCK или CS в модифицированный сигнал LRCKt, содержащий код временной метки, а также коды маркеров начала и конца импульсного сигнала LRCK или CS. Разрядность регистра, равная сумме младших разрядов D0, промежуточных разрядов D1 и старших разрядов D2, определяется разрядностью кодирования АЦП. Например, для потока формата I2S разрядность обычно составляет 16, 24 или 32 разряда;

9 - схема выделения фронта и спада импульсного сигнала LRCK или CS. По фронту каждого из этих коротких импульсов осуществляется запись кода двоичного счетчика в регистр сдвига, а по спаду происходит изменение состояния двоичного счетчика;

10, 11 - логические схемы «И». С их помощью осуществляется стробирование фиксированных кодов маркеров начала и конца Nstart и Nend импульсным сигналом LRCK или CS;

12 - двоичный счетчик. Предназначен для формирования цифрового кода временной метки, которая с помощью регистра сдвига встраивается в импульсный сигнал LRCK или CS, образуя тем самым модифицированный сигнал LRCKt. Разрядность двоичного счетчика Nt определяется из условия:

NАЦП = Nstart + Nt + Nend,

где NАЦП - разрядность используемых АЦП; Nstart - разрядность, а также значение фиксированного кода маркера начала импульсного сигнала LRCK или CS; Nt - разрядность, а также значение двоичного счетчика (разрядность временной метки); Nend - разрядность, а также значение фиксированного кода маркера спада импульсного сигнала LRCK или CS;

13 - средство трансформации импульсного сигнала LRCK или CS в сигнал LRCKt. Осуществляет преобразование стандартного импульсного сигнала LRCK или CS в комплексный сигнал, содержащий временную метку и маркеры начала и конца импульсного сигнала LRCK или CS.

Заявленные способы объединения цифровых потоков в многоканальных каскадных конфигурациях с асинхронными интерфейсами и заявленная система, реализующая данные способы, могут работать следующим образом.

Как показано на фиг.1, массив аналоговых сигналов объемом mN, поступающий от m групп 11, 12,.. 1m по N сигналов в группе от источников 2 аналоговых сигналов, например, от микрофонной решетки, подается на средство 3 предварительной обработки, где усиливается, фильтруется и преобразовывается в зависимости от свойств, присущих аналоговым сигналам. Обработанный массив аналоговых сигналов со средства 3 предварительной обработки поступает на парные АЦП 4, где преобразуются в последовательный цифровой код в формате потока I2S или SPI. Парные или двухканальные АЦП - стандартные устройства, используемые в аудиотехнике для формата I2S, в отличие от формата SPI, где имеют место как одноканальные, так многоканальные конфигурации. Здесь следует пояснить, что протокол потока SPI имеет две линии передачи данных - MOSI и MISO (соответственно запись и чтение), а протокол I2S - только одну линию данных. По своей структуре эти линии очень схожи. Поскольку для целей настоящего изобретения актуальным является только чтение, линия записи протокола потока SPI не рассматривается. В общем же случае можно предусмотреть переключатель режимов I2S/SPI и дополнительную связь с главным процессором.

В результате попарного объединения на выходе АЦП 4 формируется N/2 цифровых потоков последовательных данных. Эти данные поступают на входы главного процессора 5, в который записываются по фронту импульсов тактового сигнала BCLK, поступающих с тактового генератора 7 (см. фиг.2а).

Тактовый генератор 7 программируется хост компьютером по шине I2C или SPI таким образом, чтобы обеспечить различные скоростные режимы работы АЦП и потоков данных. Так, частота дискретизации (импульсный сигнал LRCK или CS) может программным способом устанавливаться для разных стандартных режимов: 48 kHz, 96 kHz, 192 kHz, 384 kHz или 768 kHz, или иных частот для формата потока SPI.

Импульсный сигнал LRCK или CS используется также для кадровой синхронизации потоков данных, поступая на вход кадровой синхронизации АЦП 4 (фиг.2b).

Аналогичным образом устанавливается и соответствующая частоте дискретизации частота потока данных FBCLK.

Для встраивания временной метки в импульсный сигнал LRCK или CS используется средство 13 трансформации импульсного сигнала LRCK или CS в сигнал LRCKt. Цифровой код временной метки создается двоичным счетчиком 12, который меняет свое состояния под действием коротких импульсов, формируемых схемой 9 выделения фронта и спада импульсного сигнала LRCK или CS (фиг.2c). По фронту коротких импульсов производится запись кода временной метки Nt в регистр сдвига 8, а по спаду - изменение состояния двоичного счетчика 12.

Одновременно с записью кода временной метки Nt в регистр сдвига записываются маркеры начала Nstart и конца Nend импульсного сигнала LRCK или CS. Запись маркеров Nstart и Nend производится через схемы «И» 10, 11 только в моменты времени, когда импульсный сигнал LRCK или CS имеет высокий уровень. После записи в регистр 8 кодов Nstart, Nt и Nend под действием импульсов тактового сигнала BCLK на выходе регистра сдвига образуется последовательность импульсов комплексного тактового сигнала LRCKt, как показано на фиг.2d.

Как видно из фиг.2d, по каждому импульсу записи происходит увеличение кода временной метки на единицу: Nt, Nt+1, Nt+2 и т.д. Так как сигнал кадровой синхронизации одновременно является и импульсным сигналом LRCK или CS, каждый дискретный отсчет сигнала на выходе АЦП 4 будет сопровождаться собственной временной меткой.

Таким образом, во всех каналах всех групп все дискретные отчеты в одно и то же время будут сопровождаться присвоением им временных меток. Это обстоятельство дает возможность в процессе дальнейшей программной обработки привязать все дискретные отсчеты к единому временному базису, несмотря на временные задержки, возникающие при асинхронной передаче данных.

Наличие встроенных временных меток позволяет создавать системы с неограниченным количеством синхронных каналов без необходимости использования дополнительного порта для временной привязки в главном процессоре.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ПЕРЕПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ПРИЕМНЫЙ ТРАКТ | 2004 |

|

RU2289202C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| ЦИФРОВОЙ МАГНИТОФОН | 1992 |

|

RU2054715C1 |

| МИКРОФОННЫЙ МОДУЛЬ, СИСТЕМА МИКРОФОННОЙ РЕШЕТКИ, СОДЕРЖАЩАЯ МИКРОФОННЫЕ МОДУЛИ, И СПОСОБ СБОРА И ОБРАБОТКИ ЗВУКОВЫХ ДАННЫХ | 2022 |

|

RU2793077C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1996 |

|

RU2128890C1 |

| СИСТЕМА ЦИФРОВОГО ЦВЕТНОГО ТЕЛЕВИДЕНИЯ | 1993 |

|

RU2103839C1 |

| ЦИФРОВОЙ МОДЕМ ИНФОРМАЦИОННОЙ РАДИОЛИНИИ ЦМ ИРЛ | 2013 |

|

RU2583715C2 |

| ЦИФРОВОЙ КОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ С ДВОИЧНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2016 |

|

RU2633183C1 |

| ЦИФРОВОЕ КВАДРАТУРНОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ И ДЕМОДУЛЯЦИИ | 2015 |

|

RU2591032C1 |

Группа изобретений относится к многоканальным системам сигнальной обработки, в которых для последовательного обмена данными используются синхронные протоколы I2S (Inter-IC Sound Bus) и SPI (Serial Peripheral Bus) и обеспечивается единая синхронизация обрабатываемых данных. Технический результат - снятие ограничения на количество полностью синхронизированных потоков данных в форматах I2S или SPI, то есть обеспечение возможности построения многоканальных систем с неограниченным количеством полностью синхронизированных потоков данных, при одновременном упрощении синхронизации и снижении требований к аппаратным ресурсам. Для этого предложены система и способ синхронного объединения потоков данных, в которых предполагают трансформацию стандартного импульсного сигнала дискретизации LRCK формата I2S или импульсного сигнала выбора микросхемы CS формата SPI в сигнал LRCLt, содержащий код временной метки, а также коды маркеров начала и конца тактового сигнала синхронизации. Наличие кодов маркеров и временной метки позволяет восстановить импульсный сигнал соответственно LRCK или CS с привязкой значения каждой дискретной выборки к временной метке. 3 н. и 4 з.п. ф-лы, 2 ил.

1. Система объединения цифровых потоков, содержащая:

m канальных групп сбора синхронных данных в формате синхронного протокола, причем каждая канальная группа включает:

средство предварительной обработки аналоговых сигналов, имеющее N входов для обработки сигналов, поступающих от N источников аналоговых сигналов, и N выходов,

N/2 парных аналого-цифровых преобразователей (АЦП), каждый из которых имеет N входов, вход тактовой синхронизации потока данных, вход общей синхронизации, вход кадровой синхронизации и N/2 выходов, и

главный процессор с асинхронным интерфейсом, имеющий N/2 входов и вход записи данных,

причем N выходы средства предварительной обработки подключены к N входам N/2 АЦП, a N/2 выходов АЦП подключены к N/2 входам главного процессора, тактовый генератор, имеющий:

управляющий вход, первый выход, формирующий тактовый сигнал синхронизации потока данных BCLK, второй выход, формирующий служебный сигнал общей синхронизации MCLK, и третий выход, формирующий импульсный сигнал соответствующего синхронного протокола,

хост процессор, имеющий:

шину управления и

по меньшей мере два асинхронных интерфейса, к которым соответственно подключены указанные по меньшей мере две канальные группы, и

средство трансформации импульсного сигнала соответствующего синхронного протокола в сигнал LRCKt, содержащий код временной метки, а также коды маркеров начала и конца импульсного сигнала, включающее:

схему выделения фронта и спада указанного импульсного сигнала,

регистр сдвига, имеющий вход сдвига данных,

первую схему «И» и вторую схему «И», каждая из которых имеет первый вход управления, второй вход управления и цифровой выход, и

двоичный счетчик, имеющий счетный вход, цифровые выходы,

при этом управляющий вход тактового генератора подключен к шине управления хост процессора,

первый выход тактового генератора подключен к входу тактовой синхронизации потока данных АЦП, входу записи данных главных процессоров и входу сдвига данных регистра сдвига, второй выход тактового генератора подключен ко входам общей синхронизации АЦП,

третий выход тактового генератора подключен к входу кадровой синхронизации АЦП, входу схемы выделения фронта и спада импульсного сигнала соответствующего синхронного протокола, первому входу управления первой схемы «И» и первому входу управления второй схемы «И»,

второй вход управления первой схемы «И» и второй вход управления второй схемы «И» выполнены с возможностью предварительной установки фиксированных кодов соответственно маркера начала Nstart и маркера конца Nend импульсного сигнала соответствующего синхронного протокола,

цифровой выход первой схемы «И» подключен к младшим разрядам регистра сдвига, цифровой выход второй схемы «И» подключен к старшим разрядам регистра сдвига, а цифровой выход двоичного счетчика подключен к промежуточным разрядам регистра сдвига, и

к выходу схемы выделения фронта и спада импульсного сигнала соответствующего синхронного протокола подключен счетный вход двоичного счетчика и вход записи регистра сдвига.

2. Система по п. 1, в которой синхронный протокол является протоколом I2S, а импульсным сигналом является тактовый сигнал дискретизации Left/Right Clock (LRCK) формата I2S.

3. Система по п. 1, в которой синхронный протокол является протоколом SPI, а импульсным сигналом является сигнал выбора микросхемы Chip Select (CS) формата SPI.

4. Способ объединения цифровых потоков формата I2S, в котором:

получают массив аналоговых сигналов объемом mN, поступающих от m канальных групп сбора синхронных данных в формате синхронного протокола, где каждая канальная группа включает N аналоговых сигналов;

производят предварительную обработку указанного массива аналоговых сигналов; направляют обработанный массив аналоговых сигналов на парные АЦП и осуществляют преобразование его в последовательный цифровой код в формате I2S с формированием N/2 цифровых потоков последовательных данных;

направляют указанные цифровые потоки последовательных данных на входы главного процессора с записью по фронту импульсов тактового сигнала синхронизации потока данных BCLK, поступающих от тактового генератора;

встраивают временную метку в импульсный сигнал дискретизации Left/Right Clock (LRCK) формата I2S, при котором:

трансформируют сигнал LRCK в сигнал LRCKt, содержащий код временной метки, а также коды маркеров начала и конца импульсного сигнала, при этом цифровой код временной метки создают двоичным счетчиком, по фронту импульсов производят запись кода временной метки Nt в регистр сдвига, а по спаду импульсов фиксируют изменение состояния двоичного счетчика, причем одновременно с записью кода временной метки Nt в регистр сдвига записывают маркеры начала Nstart и конца Nend сигнала LRCK только в моменты времени, когда сигнал LRCK имеет высокий уровень; и

после записи в регистр кодов Nstart, Nt и Nend под действием импульсов тактового сигнала BCLK на выходе регистра сдвига формируют последовательность импульсов комплексного тактового сигнала LRCKt.

5. Способ по п. 4, отличающийся тем, что предварительная обработка массива аналоговых сигналов включает усиление, фильтрацию и преобразование в зависимости от свойств, присущих аналоговым сигналам.

6. Способ объединения цифровых потоков формата SPI, в котором:

получают массив аналоговых сигналов объемом mN, поступающих от m канальных групп сбора синхронных данных в формате синхронного протокола, где каждая канальная группа включает N аналоговых сигналов;

производят предварительную обработку указанного массива аналоговых сигналов;

направляют обработанный массив аналоговых сигналов на парные АЦП и осуществляют преобразование его в последовательный цифровой код в формате SPI с формированием N/2 цифровых потоков последовательных данных;

направляют указанные цифровые потоки последовательных данных на входы главного процессора с записью по фронту импульсов тактового сигнала синхронизации потока данных BCLK, поступающих от тактового генератора;

встраивают временную метку в импульсный сигнал выбора микросхемы Chip Select (CS) формата SPI, при котором:

трансформируют сигнал CS в сигнал LRCKt, содержащий код временной метки, а также коды маркеров начала и конца импульсного сигнала, при этом цифровой код временной метки создают двоичным счетчиком, по фронту импульсов производят запись кода временной метки Nt в регистр сдвига, а по спаду импульсов фиксируют изменение состояния двоичного счетчика, причем одновременно с записью кода временной метки Nt в регистр сдвига записывают маркеры начала Nstart и конца Nend сигнала CS только в моменты времени, когда сигнал CS имеет высокий уровень; и

после записи в регистр кодов Nstart, Nt и Nend под действием импульсов тактового сигнала BCLK на выходе регистра сдвига формируют последовательность импульсов комплексного тактового сигнала LRCKt.

7. Способ по п. 6, отличающийся тем, что предварительная обработка массива аналоговых сигналов включает усиление, фильтрацию и преобразование в зависимости от свойств, присущих аналоговым сигналам.

| CN 109245841 A, 18.01.2019 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

| 0 |

|

SU159037A1 | |

Авторы

Даты

2021-12-15—Публикация

2020-11-06—Подача