ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

[0001] Глубокие нейронные сети (“DNN”) свободно моделируются по образцам (паттернам) обработки информации и коммуникации в биологических нервных системах, таких как человеческий мозг. DNN могут использоваться для решения сложных задач классификации, таких как, но без ограничения, обнаружение объектов, семантическая маркировка и извлечение признаков. В результате, DNN формируют основу для многих приложений искусственного интеллекта (“AI”), таких как компьютерное зрение, распознавание речи и машинный перевод. DNN могут соответствовать или превосходить человека по точности во многих из этих областей.

[0002] Высокий уровень производительности DNN проистекает из их способности извлекать признаки высокого уровня из входных данных после использования статистического обучения на больших наборах данных, чтобы получить эффективное представление входного пространства. Однако превосходные характеристики DNN достигаются ценой высокой вычислительной сложности. Высокопроизводительные процессоры общего назначения, такие как блоки обработки графики (графические процессоры) (“GPU”), обычно используются, чтобы обеспечить высокий уровень вычислительной производительности, необходимой во многих приложениях DNN.

[0003] В то время как процессоры общего назначения, такие как GPU, могут обеспечить высокий уровень вычислительной производительности для реализации DNN, эти типы процессоров, как правило, непригодны для использования при выполнении операций DNN в течение длительного времени в вычислительных устройствах, где низкое энергопотребление является критическим. Например, процессоры общего назначения, такие как GPU, могут быть непригодными для использования при выполнении длительно исполняющихся задач DNN в портативных устройствах с батарейным питанием, таких как смартфоны или устройства альтернативной/виртуальной реальности (“AR/VR”), где требуется пониженное энергопотребление, чтобы увеличить срок службы батареи.

[0004] Пониженное энергопотребление при выполнении непрерывных задач DNN, таких как обнаружение движения человека, также может быть важным в устройствах с не–батарейным питанием, таких, например, как камеры безопасности с питанием через Ethernet (“POE”). В этом конкретном примере, POE коммутаторы могут обеспечивать только ограниченную величину питающей мощности, и снижение энергопотребления устройств POE, таких как камеры безопасности, позволяет использовать коммутаторы POE, которые обеспечивают меньшую питающую мощность.

[0005] Разработаны специализированные интегральные схемы (“ASIC”), которые могут обеспечить производительную обработку DNN при одновременном снижении энергопотребления по сравнению с процессорами общего назначения. Несмотря на успехи в этой области, однако, существует постоянная необходимость в повышении производительности и снижении энергопотребления ASIC, которые выполняют обработку DNN, в частности, для использования в вычислительных устройствах, где низкое энергопотребление является критическим.

[0006] Именно на решение этих и других технических проблем направлено раскрытие, представленное в данном документе.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0007] Раскрыт модуль DNN, или процессор, который может сжимать и распаковывать данные активации, чтобы снизить использование пропускной способности шины памяти. В частности, модуль DNN может использовать сжатие, чтобы снизить использование пропускной способности шины между выходом нейрона и внутриплатной или внеплатной памятью. Модуль DNN может также использовать распаковку (декомпрессию), чтобы снизить использование пропускной способности шины памяти между внутриплатной или внеплатной памятью и входом нейрона. Снижение использования пропускной способности может обеспечить возможность более быструю обработку и, следовательно, может также уменьшить энергопотребление. Другие технические преимущества, конкретно не указанные здесь, могут также быть достигнуты посредством реализаций раскрытого предмета.

[0008] Для того чтобы реализовать технические преимущества, кратко упомянутые выше, раскрыт процессор DNN, который включает в себя один или несколько нейронов и блок сжатия. Блок сжатия может принимать несжатую порцию данных, сгенерированных одним или несколькими нейронами. Несжатая порция данных включает в себя фиксированное число байтов, например, 64 байта, в некоторых вариантах осуществления.

[0009] Для того чтобы сжать несжатую порцию данных, блок сжатия может генерировать часть маски и часть данных в сжатой выходной порции. Часть маски сжатой выходной порции включает в себя число битов, эквивалентное фиксированному числу байтов в несжатой порции данных. Например, если несжатая порция данных включает в себя 64 байта данных, часть маски будет включать в себя 64 бита (то есть 8 байтов).

[0010] Каждый бит в части маски сжатой выходной порции соответствует байту в несжатой порции данных в некоторых вариантах осуществления. Например, бит один маски части может соответствовать первому байту в несжатой порции данных, бит два части маски может соответствовать второму байту в несжатой порции данных и так далее. В других вариантах осуществления, два или более бита в части маски сжатой выходной порции соответствуют байту в несжатой порции данных. В этих вариантах осуществления, биты в части маски сжатой выходной порции могут указывать, что не только имеется соответствующий байт в несжатой порции, но и его приблизительную величину.

[0011] Когда отдельные биты части маски соответствуют байтам в несжатой порции, блок сжатия устанавливает каждый бит в части маски сжатой выходной порции в логическое “ложно” (что также может упоминаться здесь как “логический нуль”), где соответствующий байт в несжатой порции данных содержит все нули (т.е. “нулевой байт”). Блок сжатия также устанавливает каждый бит в части маски сжатой выходной порции в логическое “истинно” (что также может упоминаться здесь как “логическая единица”), где соответствующий байт в несжатой порции данных содержит по меньшей мере один ненулевой бит (то есть “ненулевой байт”). Таким образом, часть маски сжатой выходной порции кодирует наличие и местоположение нулевых и ненулевых байтов в несжатой порции данных.

[0012] Блок сжатия формирует часть данных сжатой выходной порции путем определения числа ненулевых байтов в несжатой порции данных. Блок сжатия затем определяет, на основе числа ненулевых байтов в несжатой порции данных и числа байтов, имеющихся в части данных сжатой выходной порции, число битов в части данных сжатой выходной порции, которые доступны для сохранения каждого ненулевого байта несжатой порции данных. Например, если часть данных сжатой порции данных составляет 24 байта в ширину (то есть 192 бита), и имеется 47 ненулевых байтов в несжатой порции данных, то четыре бита доступны в части данных для сохранения каждого ненулевого байта из несжатой порции данных.

[0013] В некоторых вариантах осуществления, блок сжатия может также определить число дополнительных битов, если таковые имеются, в части данных сжатой выходной порции, которые доступны для сохранения ненулевых байтов несжатой порции данных. В примере, приведенном выше, например, четыре дополнительных бита доступны для сохранения ненулевых байтов (т.е. 192 mod 47=четыре бита). Блок сжатия может назначить эти дополнительные биты одному или нескольким ненулевым байтам в несжатой порции данных перед усечением одного или нескольких ненулевых байтов. Например, модуль сжатия может назначить эти дополнительные биты первым нескольким байтам в части данных сжатой выходной порции.

[0014] Блок сжатия затем усекает ненулевые байты в несжатой порции данных до определенного числа битов, доступных в части данных, чтобы сохранять каждый ненулевой байт (т.е. четыре в приведенном выше примере). Блок сжатия усекает младшие биты (“LSB”) ненулевых байтов, чтобы соответствовать имеющемуся числу битов в части данных в одном варианте осуществления. В другом варианте осуществления, блок сжатия усекает старшие биты (“MSB”) ненулевых байтов. Затем блок сжатия сохраняет усеченные ненулевые байты в части данных сжатой выходной порции. Сжатая выходная порция, включая часть маски и часть данных, затем может быть выведена, например, во внутриплатную память в процессоре DNN или внеплатную память хоста приложения процессора DNN.

[0015] Модуль DNN может также включать в себя блок распаковки (декомпрессии), который может распаковывать порции данных, которые были сжаты, как описано выше. Например, блок распаковки может принять сжатую порцию данных из памяти в процессоре DNN или памяти хоста приложения. Блок распаковки может затем определить число ненулевых байтов в части данных несжатой порции данных на основе числа логических истинных битов в части маски сжатой выходной порции. Блок распаковки может также определить местоположения ненулевых байтов в несжатой порции данных на основе местоположений логических истинных битов в части маски сжатой выходной порции. Блок распаковки может определить местоположение нулевых байтов в несжатой порции данных таким же образом.

[0016] Блок распаковки может также определить число битов, используемых блоком сжатия для сохранения усеченных ненулевых байтов в части данных сжатой выходной порции. Блок распаковки может определить число битов, используемых для сохранения каждого усеченного ненулевого байта, на основе числа ненулевых байтов в сжатой порции данных и числа байтов, доступных в части данных несжатой выходной порции.

[0017] В примере, приведенном выше, например, если часть данных сжатой порции данных составляет 24 байта (то есть 192 бита), и имеется 47 ненулевых байтов в несжатой порции данных, блок сжатия используется четыре бита для сохранения каждого усеченного ненулевого байта несжатой порции данных в части данных. Блок распаковки может также определить число дополнительных битов, если таковые имеются, которые блок сжатия выделил одному или нескольким усеченным ненулевым байтам, сохраненным в части данных сжатой выходной порции.

[0018] Для каждой битовой позиции в части маски сжатой выходной порции, которая представляет собой логический нуль, блок распаковки вставляет нулевой байт в соответствующую позицию распакованной выходной порции. Для каждой позиции в части маски, которая представляет собой логическую единицу, блок распаковки вставляет усеченный ненулевой байт из соответствующей позиции сжатой входной порции в соответствующую позицию распакованной выходной порции вместе с числом нулевых битов, эквивалентным числу битов, усеченных во время сжатия сжатой выходной порции. Нулевые биты могут быть вставлены в LSB или MSB усеченных ненулевых байтов в зависимости от того, какие биты были усечены во время сжатия.

[0019] В некоторых вариантах осуществления, блок распаковки также добавляет смещение (например, 00000001) к одному или нескольким усеченным ненулевым байтам, сохраненным в распакованной выходной порции. Например, смещение может быть добавлено к ненулевым байтам несжатой порции данных, которые становятся нулевыми байтами после сжатия. Таким образом, ненулевые байты не будут становиться нулевыми байтами при сжатии и распаковки. Смещение может быть добавлено ко всем байтам в распакованной выходной порции в других вариантах осуществления.

[0020] Как кратко описано выше, реализации технологий, раскрытых здесь, могут уменьшить использование пропускной способности шины памяти в модуле DNN, позволяют модулю DNN завершать операции обработки более быстро и уменьшают энергопотребление. Другие технические преимущества, конкретно не выявленные здесь, также могут быть достигнуты посредством реализации раскрытых технологий.

[0021] Следует понимать, что описанный выше предмет может быть реализован как устройство с компьютерным управлением, реализуемый компьютером способом, вычислительное устройство или продукт производства, такой как считываемый компьютером носитель. Эти и различные другие признаки будут очевидны из нижеследующего подробного описания и обзора соответствующих чертежей.

[0022] Настоящее краткое описание сущности изобретения предусмотрено, чтобы кратко описать некоторые аспекты раскрытых технологий в упрощенной форме, которые дополнительно описаны ниже в подробном описании. Это краткое описание сущности изобретения не предназначено для определения ключевых признаков или существенных признаков заявленного предмета, а также не предполагается, что это краткое описание будет использоваться для ограничения объема заявленного предмета. Кроме того, заявленный предмет не ограничивается реализациями, которые преодолевают любые или все недостатки, отмеченные в любой части данного раскрытия.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

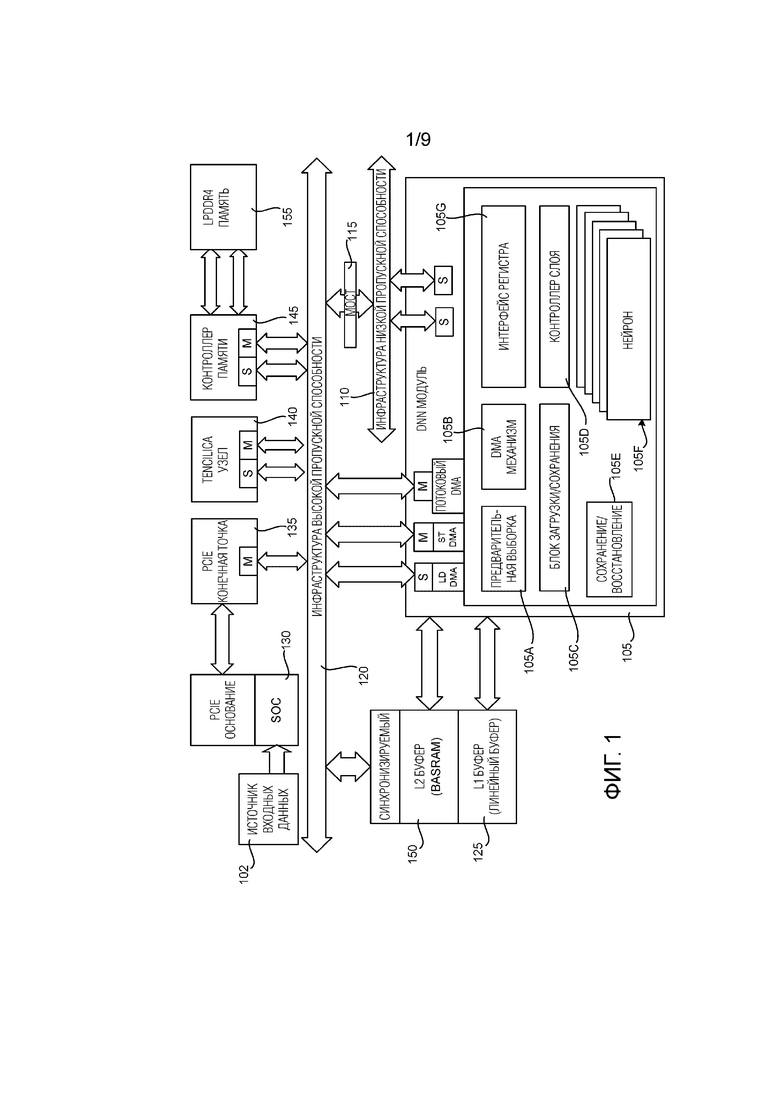

[0023] Фиг. 1 представляет собой схему вычислительной архитектуры, которая показывает аспекты конфигурации и работы модуля DNN, который реализует аспекты технологий, раскрытых в данном документе, в соответствии с одним вариантом осуществления;

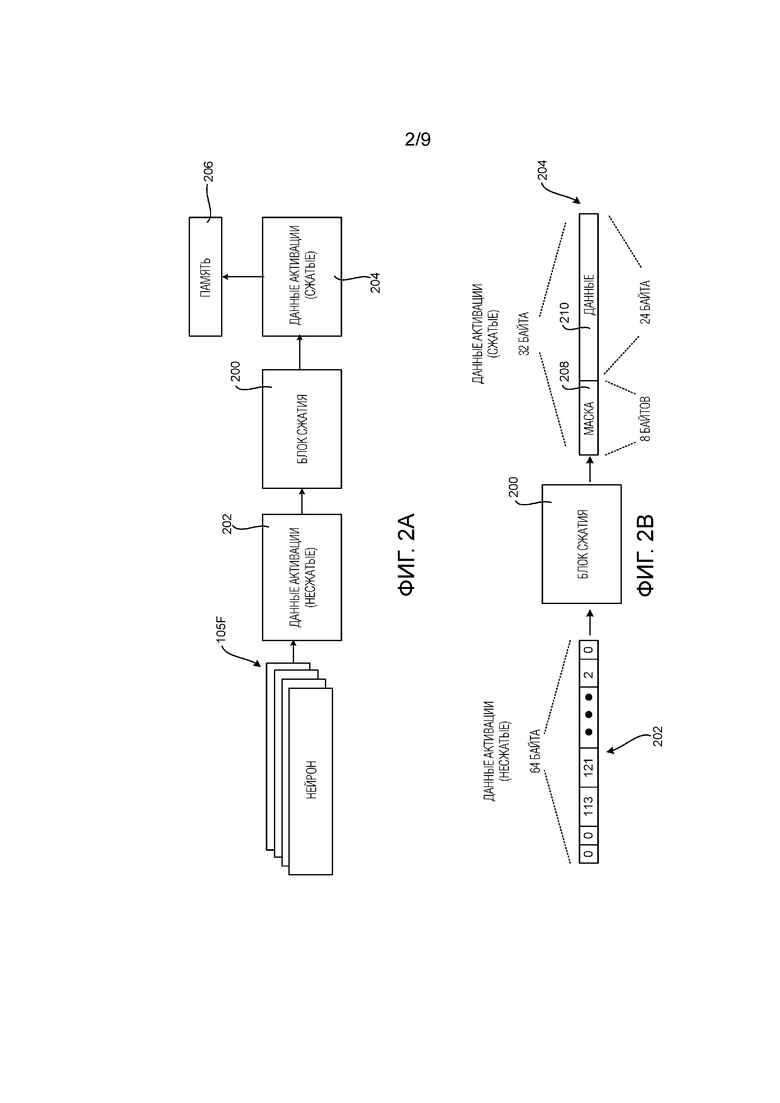

[0024] Фиг. 2А и 2В представляют собой схемы архитектуры вычислительной системы, показывающие аспекты конфигурации и работы модуля DNN для сжатия данных активации, в соответствии с одним вариантом осуществления;

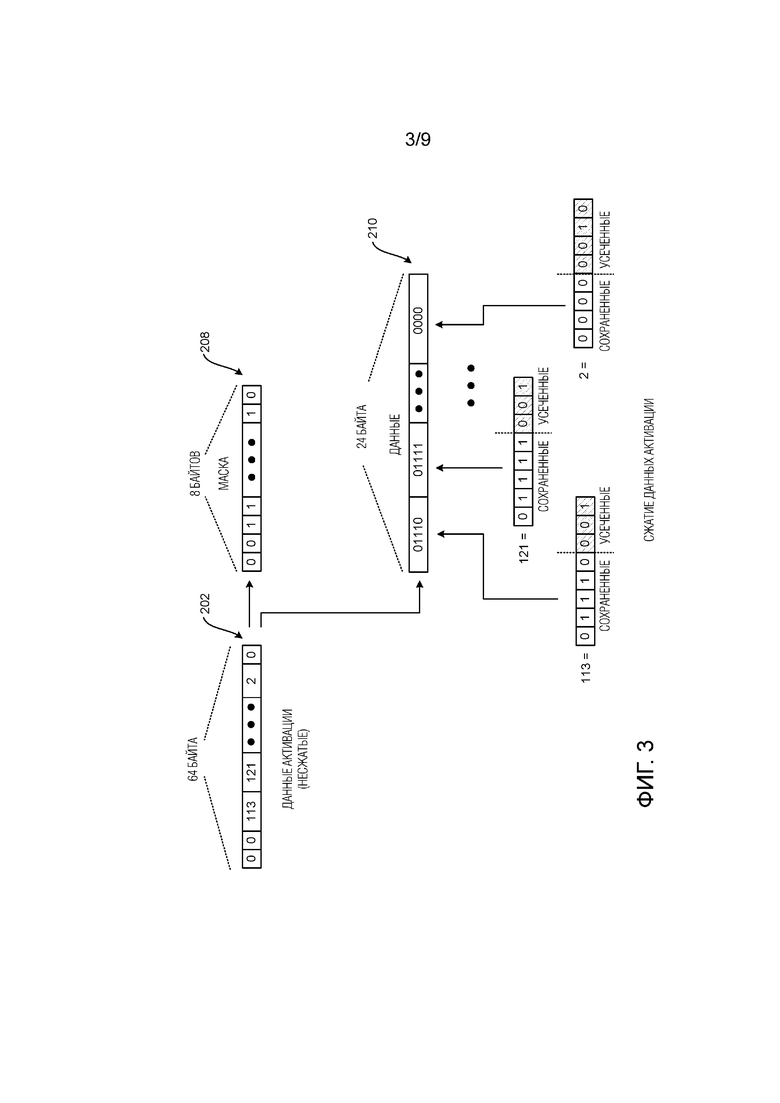

[0025] Фиг. 3 представляет собой диаграмму структуры данных, которая иллюстрирует аспекты работы модуля DNN для сжатия данных активации со ссылкой на примерную порцию несжатых данных активации, в соответствии с одним вариантом осуществления;

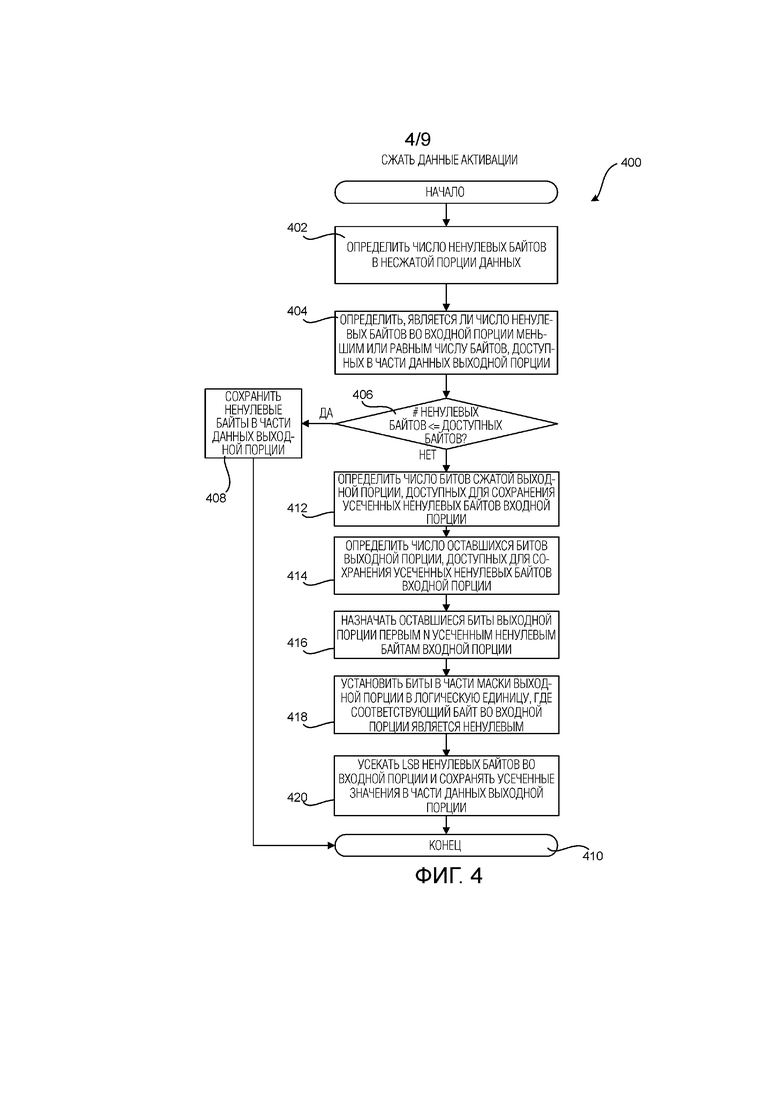

[0026] Фиг. 4 представляет собой блок–схему последовательности операций, показывающую процедуру, которая иллюстрирует аспекты работы раскрытого модуля DNN для сжатия данных активации, в соответствии с одним вариантом осуществления, раскрытым в данном документе;

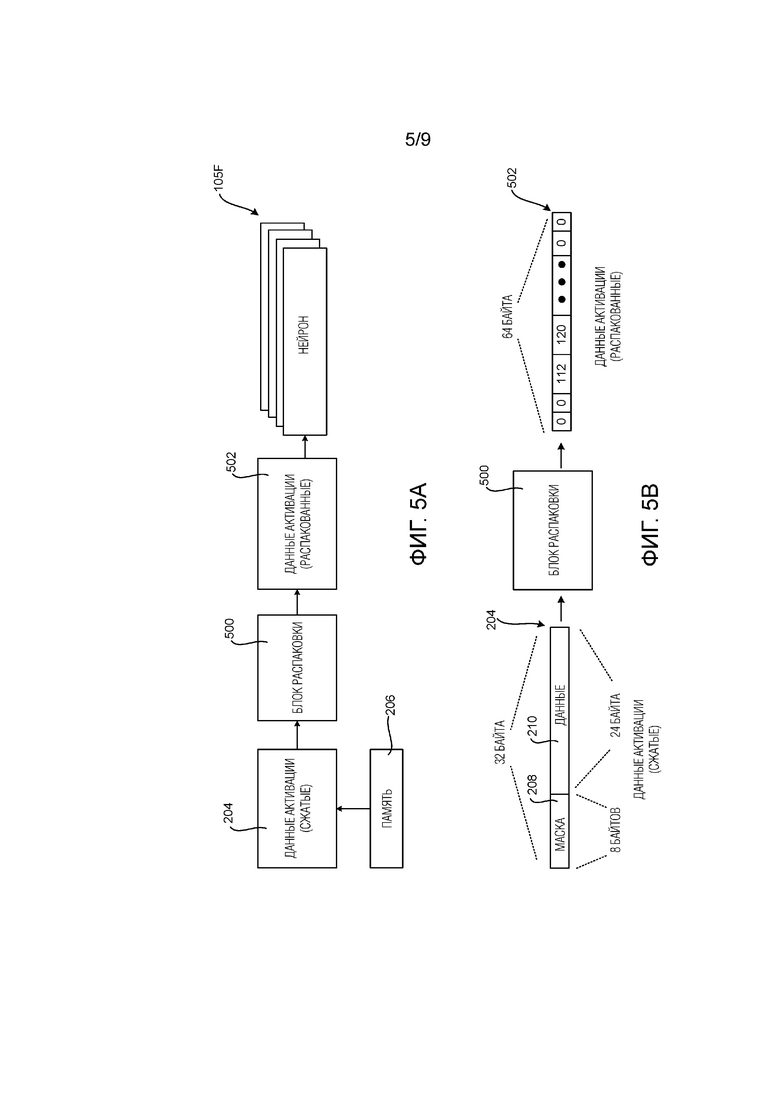

[0027] Фиг. 5А и 5В представляют собой схемы архитектуры вычислительной системы, показывающие аспекты конфигурации и работы модуля DNN для распаковки данных активации, в соответствии с одним вариантом осуществления;

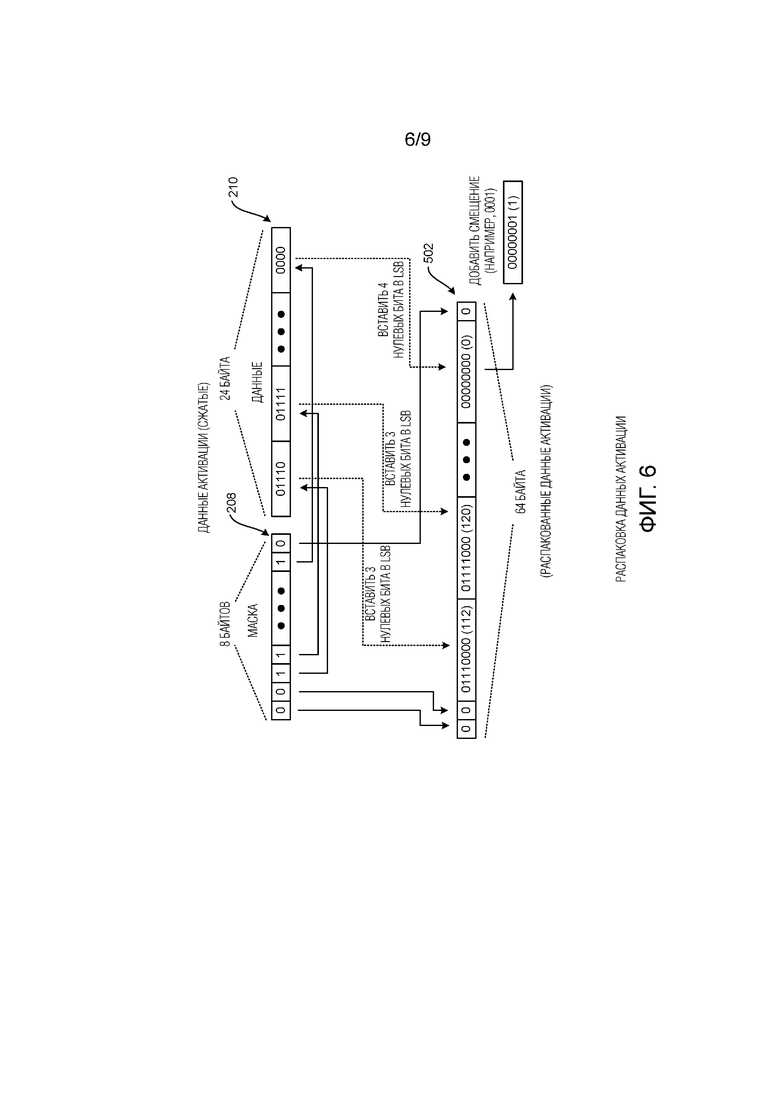

[0028] Фиг. 6 представляет собой диаграмму структуры данных, которая иллюстрирует аспекты работы модуля DNN для распаковки данных активации со ссылкой на примерную порцию сжатых данных активации, в соответствии с одним вариантом осуществления;

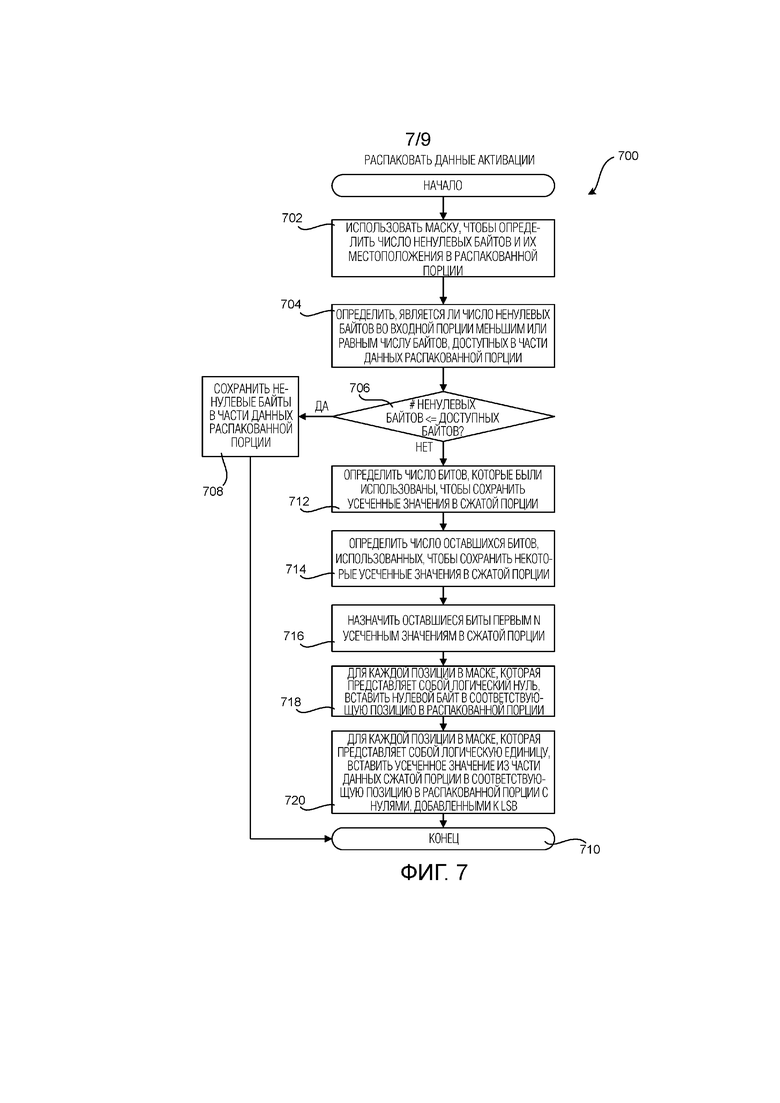

[0029] Фиг. 7 представляет собой блок–схему последовательности операций, показывающую процедуру, которая иллюстрирует аспекты работы раскрытого модуля DNN для распаковки данных активации, в соответствии с одним вариантом осуществления, раскрытым в данном документе;

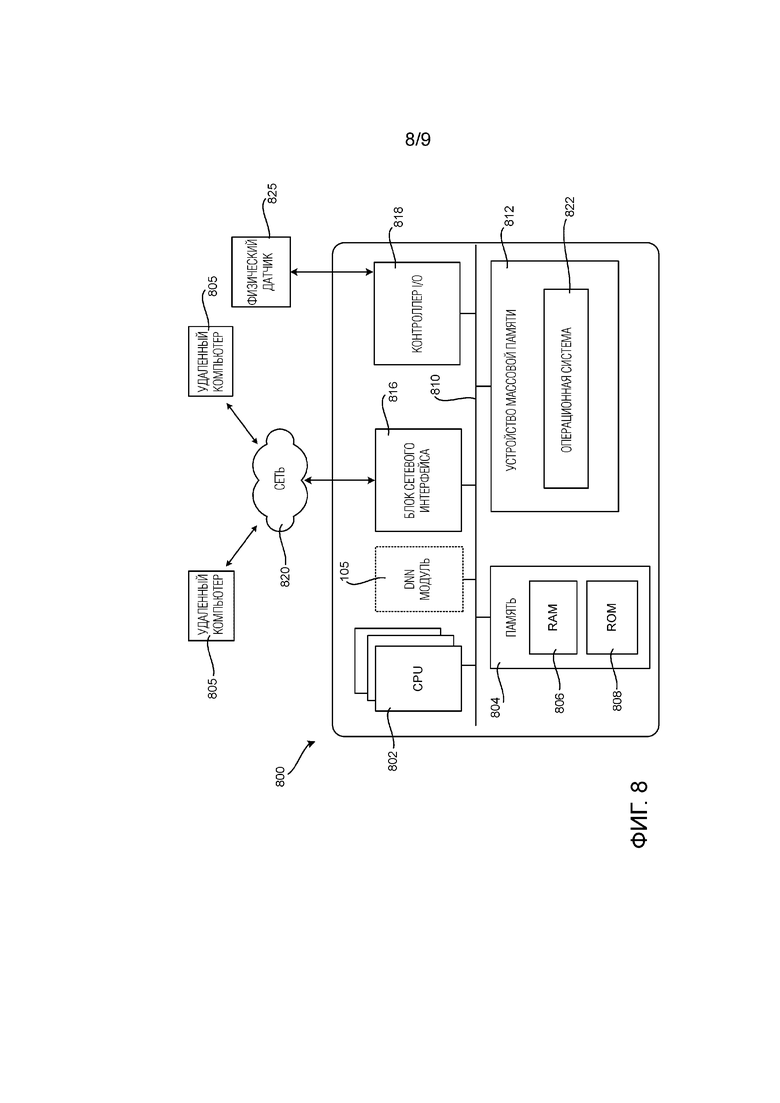

[0030] Фиг. 8 представляет собой схему архитектуры компьютера, показывающую иллюстративную архитектуру компьютерных аппаратных средств и программного обеспечения для вычислительного устройства, которое может действовать как хост приложения для модуля DNN, представленного в данном документе, в соответствии с одним вариантом осуществления; и

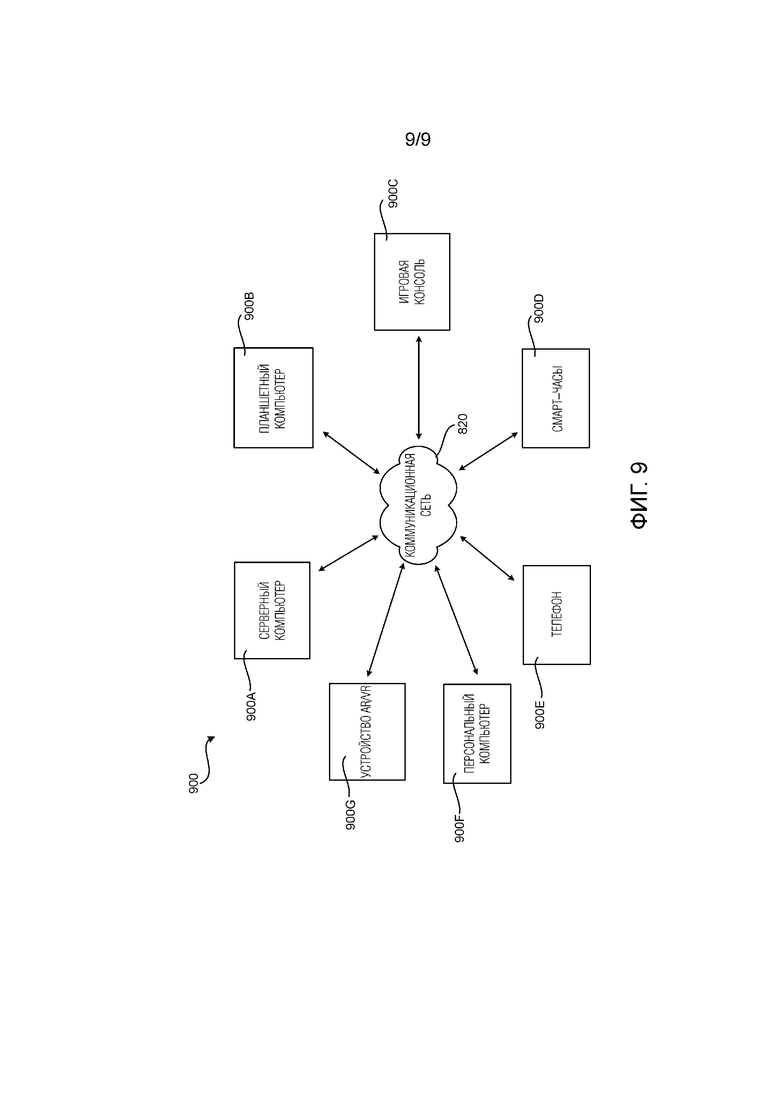

[0031] Фиг. 9 представляет собой структурную схему сети, иллюстрирующую распределенную вычислительную среду, в которой аспекты раскрытых технологий могут быть реализованы в соответствии с различными вариантами осуществления, представленными в данном документе.

ПОДРОБНОЕ ОПИСАНИЕ

[0032] Следующее подробное описание относится к модулю DNN, который может сжимать и распаковывать данные активации, чтобы снизить использование пропускной способности шины памяти. Как кратко описано выше, реализации раскрытых технологий могут уменьшить использование пропускной способности шины памяти в модуле DNN, позволяют модулю DNN завершать операции обработки более быстро и уменьшают энергопотребление. Другие технические преимущества, конкретно не упомянутые здесь, также могут быть достигнуты посредством реализации раскрытого предмета.

[0033] Хотя предмет, описанный здесь, представлен в общем контексте аппаратного модуля DNN, специалистам в данной области техники будет понятно, что другие варианты осуществления могут быть выполнены в комбинации с другими типами вычислительных систем и модулей. Специалистам в данной области техники будет также понятно, что предмет, описанный здесь, может быть осуществлен на практике с другими конфигурациями компьютерных систем, включая портативные устройства, многопроцессорные системы, основанные на микропроцессорах или программируемые бытовые электронные приборы, вычислительные или процессорные системы, встроенные в устройства (например, носимые вычислительные устройства, автомобили, домашняя автоматика и т.д.), миникомпьютеры, универсальные компьютеры и тому подобное.

[0034] Как будет описано более подробно ниже, раскрыт модуль DNN, который сконфигурирован, чтобы сжимать выход его нейронов. Сжатый выход может быть сохранен в памяти на модуле DNN или в памяти, которая является внешней по отношению к модулю DNN, такой как память, обеспеченная на хосте приложения для модуля DNN. Модуль DNN может затем распаковывать ранее сжатые данные и предоставить распакованные данные в нейроны.

[0035] Согласно одному варианту осуществления, блок сжатия в процессоре DNN сжимает порции фиксированной длины (например, 64 байта) несжатых данных активации при фиксированном отношении сжатия (например, 2:1). Сжатые данные активации, генерируемые блоком сжатия, могут включать в себя порции данных, имеющие фиксированную длину (например, 32 байта), которые включают в себя часть маски фиксированной длины (например, 8 байтов) и часть данных фиксированной длины (например, 24 байта).

[0036] Биты части маски сжатой выходной порции соответствуют байтам в пределах несжатой входной порции в одном варианте осуществления. Например, первый бит части маски может соответствовать первому байту в несжатой входной порции, второй бит части маски может соответствовать второму байту в несжатой входной порции и так далее. Биты в части маски сжатых данных активации могут быть установлены в логический нуль, если соответствующий байт в несжатой входной порции равен нулю, и могут быть установлены в логическую единицу, если соответствующий байт в несжатой входной порции не равен нулю.

[0037] Как описано кратко выше, два или более битов в части маски сжатой выходной порции соответствуют байту в несжатой порции данных в некоторых вариантах осуществления. В этих вариантах осуществления, биты в части маски сжатой выходной порции могут указывать, что не только имеется соответствующий байт в несжатой порции, но и его приблизительную величину.

[0038] Часть данных сжатой выходной порции включает в себя ненулевые байты несжатой входной порции, которые были усечены, чтобы представлять ненулевые байты входной порции с использованием числа доступных битов в сжатой части данных. Число доступных битов в части данных сжатой выходной порции для каждого ненулевого байта определяется в некоторых вариантах осуществления путем деления общего числа доступных битов в части данных (например, 192 бита) на число ненулевых байтов в несжатой входной порции. Результат этого вычисления указывает число битов в части данных сжатой выходной порции, которые доступны для представления каждого байта ненулевых данных в несжатой входной порции. Любые оставшиеся биты могут быть использованы, чтобы обеспечить дополнительный бит для представления некоторых из ненулевых значений в части данных сжатой выходной порции.

[0039] После того, как число битов, доступных в части данных сжатой выходной порции, чтобы представлять каждый ненулевой байт в несжатой входной порции, было определенно, LSB ненулевых значений в несжатой входной порции усекаются, чтобы соответствовать доступному числу битов. MSB ненулевых значений могут быть усечены в других вариантах осуществления. Усеченные ненулевые значения могут быть затем сохранены в части данных сжатой выходной порции. Этот процесс может быть повторен для каждой порции несжатых входных значений активации. Сжатые выходные порции затем могут быть сохранены во внутри– или внеплатной памяти для последующей распаковки и использования нейронами.

[0040] Раскрытый модуль DNN также может включать в себя блок распаковки для распаковки значений активации, которые были сжаты блоком сжатия, как описано выше. Блок распаковки принимает порции сжатых данных активации, которые включают в себя часть маски и часть данных. Блок распаковки может использовать биты части маски, чтобы идентифицировать число ненулевых байтов, которые будут присутствовать в распакованной выходной порции, и их местоположение в пределах распакованной выходной порции. Маска также указывает местоположения нулевых байтов в распакованной выходной порции.

[0041] В некоторых вариантах осуществления, блок распаковки определяет число битов, которые были использованы блоком сжатия, чтобы представлять каждый ненулевой байт, путем деления общего числа доступных битов в части данных (например, 192 бита) сжатой порции на число ненулевых байтов в несжатой входной порции, как задается маской. Блок распаковки может также предположить, что блок сжатия использовал любые оставшиеся биты, чтобы обеспечить дополнительный бит для представления некоторых из ненулевых значений в части данных сжатой порции (например, первые N значений).

[0042] Для каждой битовой позиции в маске, которая представляет собой логический нуль, блок распаковки может вставить нулевой байт в распакованную выходную порцию в ее соответствующей позиции. Для каждой битовой позиции в маске, которая представляет собой логическую единицу, блок распаковки вставляет усеченные ненулевые байты из соответствующей позиции в части данных сжатой входной порции в соответствующей позиции в распакованной выходной порции. Блок распаковки также вставляет нули в LSB или MSB, при необходимости, ненулевых значений, чтобы заменить те биты, которые были усечены при сжатии.

[0043] В некоторых вариантах осуществления, блок распаковки добавляет значение смещения к усеченным ненулевым значениям, чтобы гарантировать, что ненулевые несжатые значения не становятся нулевыми байтами при распаковке. Распакованная выходная порция может быть сохранена во внутри– или внеплатной памяти для использования нейронами. Дополнительные подробности, касающиеся работы модуля DNN, блока сжатия и блока распаковки, будут описаны ниже.

[0044] В приведенном ниже подробном описании делаются ссылки на приложенные чертежи, которые составляют часть данного описания и которые приведены в качестве иллюстрации конкретных конфигураций или примеров. Со ссылкой на чертежи, на которых одинаковые ссылочные позиции представляют одинаковые элементы на различных чертежах, будут описаны аспекты модуля DNN, который может сжимать и распаковывать данные активации, чтобы снизить использование пропускной способности шины памяти.

[0045] Фиг. 1 представляет собой схему вычислительной архитектуры, которая показывает аспекты конфигурации и работы модуля DNN 105, который реализует технологии, раскрытые в данном документе, в соответствии с одним вариантом осуществления. Модуль DNN 105, раскрытый в данном документе, сконфигурирован в некоторых вариантах осуществления, чтобы решать проблемы классификации (и связанные с этим проблемы), такие как, но без ограничения, обнаружение объекта, семантическая маркировка и извлечение признаков.

[0046] Для того чтобы обеспечить эту функциональность, модуль DNN 105 может реализовать нейронную сеть, характеризуемую показателем recall–only (полнота классификации), и программно поддерживать широкий спектр сетевых структур. Обучение сети, реализуемое с помощью модуля DNN 105, может быть выполнено офлайн в подсистеме серверов, центрах обработки данных или другой подходящей вычислительной среде. Результат обучения DNN представляет собой набор параметров, которые могут быть известны как “веса” или “ядра”. Эти параметры представляют собой функцию преобразования, которая может быть применена к входу, причем результатом является классификация или семантически маркированный выход.

[0047] Модуль DNN 105, раскрытый в данном документе, может рассматриваться как суперскалярный процессор. Модуль DNN 105 может послать одну или несколько инструкций на множество исполнительных блоков, называемых нейронами 105F. Эти исполнительные блоки могут определяться как “одновременная отправка – одновременное завершение”, где каждый исполнительный блок синхронизирован с каждым из других исполнительных блоков. Модуль DNN 105 может быть классифицирован как архитектура одиночного потока инструкций, множественного потока данных (“SIMD”).

[0048] Модуль DNN 105 включает в себя некоторое число нейронов 105F (например, равное степени двух). Нейрон 105F является базовой единицей в искусственных нейронных сетях, которые используются для моделирования биологического нейрона в головном мозге. Модель нейрона 105F может включать в себя скалярное произведение входного вектора на весовой вектор, суммированное со смещением, с примененной функцией активации. Обработка, выполняемая нейроном 105F в модуле DNN 105, описанная в данном документе, близко отображается на искусственный нейрон.

[0049] Каждый нейрон 105F в модуле DNN 105 способен выполнять взвешенное суммирование, максимальный пулинг (объединение), обход и потенциально другие типы операций. Нейроны 105F обрабатывают вход и весовые данные на каждый тактовый цикл. Каждый нейрон 105F синхронизирован со всеми другими нейронами 105F с точки зрения прогресса в ядре, чтобы минимизировать поток данных ядра в модуле DNN 105.

[0050] Каждый нейрон 105F может содержать умножитель, сумматор, компаратор и ряд накопителей (не показаны на фиг. 1). При наличии нескольких накопителей нейроны 105F способны поддерживать контекст для множества различных активных ядер одновременно. Каждый накопитель способен загружаться считыванием из BaSRAM 150 (описано ниже). Накопители могут суммировать себя с содержимым других накопителей из других нейронов 105F.

[0051] Модуль DNN 105 принимает в качестве входа планарные данные, такие как данные изображения. Однако вход в модуль DNN 105 не ограничивается данными изображения. Напротив, модуль DNN 105 может работать на любых входных данных, представленных в модуль DNN 105 в однородном планарном формате. В одном конкретном варианте осуществления, модуль DNN 105 может принимать в качестве входа мульти–планарные однобайтовые или двухбайтовые кадры данных.

[0052] Каждый входной кадр может подвергаться свертке с NxKxHxW набором ядер, где N – число ядер, K – число каналов на ядро, Н – высота и W – ширина. Свертка выполняется на перекрывающихся интервалах на входных данных, где интервал определяется шагами в направлениях X и Y. Эти функции выполняются нейронами 105F и управляются модулем DNN 105 и регистрами управления с возможностью программного управления.

[0053] Модуль DNN 105 поддерживает три основные типа данных: веса, входные данные/карты признаков и данные активации. Входные данные/карты признаков и данные активации, в большинстве случаев, являются двумя названиями для тех же самых данных с тем отличием, что когда речь идет о выходе слоя, используется термин данные активации. Когда речь идет о входе слоя, используется термин входные данные/карта признаков.

[0054] Нейроны 105F в модуле DNN 105 вычисляют взвешенную сумму их входов и пропускают взвешенную сумму через “функцию активации” или “передаточную функцию”. Передаточная функция обычно имеет сигмоидальную форму, но может также принимать форму кусочно–линейной функции, ступенчатой функции или другого типа функции. Функция активации позволяет нейронам 105F обучаться на большем наборе входов и желательных выходов, где границы классификации являются нелинейными.

[0055] Модуль 105 DN работает на списке дескрипторов слоев, которые соответствуют слоям нейронной сети. Список дескрипторов слоев может интерпретироваться модулем DNN 105 как инструкции. Эти дескрипторы могут предварительно извлекаться из памяти в модуль DNN 105 и выполняться в порядке. Список дескрипторов действует как набор инструкций для модуля DNN 105. Программные инструменты и/или компиляторы могут быть выполнены на устройствах внешних по отношению к модулю DNN 105 для создания списков дескрипторов, которые исполняются на модуле DNN 105.

[0056] В общем случае, может иметься два основных класса дескрипторов: дескрипторы перемещения из памяти в память (“М2М”) и дескрипторы операций. M2M дескрипторы могут быть использованы для перемещения данных в/из основной памяти в/из локального буфера (т.е. линейного буфера 125, описанного ниже) для потребления посредством дескрипторов операций. M2M дескрипторы следуют конвейеру исполнения иному, чем для дескрипторов операций. Целевой конвейер для M2M дескрипторов может быть внутренним механизмом DMA 105В или регистрами 105G конфигурации, в то время как целевой конвейер для дескрипторов операций может быть нейронами 105F.

[0057] Дескрипторы операций указывают конкретную операцию, которую должны выполнять нейроны 105F на структуре данных, расположенной в локальной статической памяти с произвольным доступом (“SRAM”). Дескрипторы операций обрабатываются в порядке и приспособлены для многих различных операций слоя, по меньшей мере некоторые из них описаны в настоящем документе.

[0058] Как показано на фиг. 1, модуль DNN 105 имеет подсистему памяти с уникальной структурой буфера LI и L2. Буферы LI и L2, показанные на фиг. 1, предназначены специально для обработки нейронной сети. В качестве примера, буфер L2 150 может поддерживать выбранную емкость хранения с высокоскоростным частным интерфейсом, работающим на выбранной частоте. Буфер LI 125 может поддерживать выбранную емкость хранения, которая может быть разделена между ядром и данными активации. Буфер LI 125 может упоминаться здесь как “линейный буфер 125”, и буфер L2 150 может упоминаться здесь как BaSRAM 150.

[0059] Вычислительные данные (т.е. данные входов, веса и данные активации) сохраняются в BaSRAM 150 в порядке построчно в некоторых вариантах осуществления. Вычислительные данные могут быть организованы в виде двух линейных буферов, где один линейный буфер содержит входные данные, который может упоминаться здесь как “входной буфер”, а другой линейный буфер, который может упоминаться здесь как “буфер весов”, содержит веса ядра. Линейные буферы заполняются из BaSRAM 150 посредством блока 105С загрузки/сохранения. Данные накапливаются в каждом линейном буфере до тех пор, пока он не достигнет своей предопределенной емкости. Данные линейного буфера копируются в теневой буфер в некоторых вариантах осуществления изобретения и представляются нейронам 105F.

[0060] Модуль DNN 105 может также содержать ряд других компонентов, в том числе, но без ограничения, интерфейс 105G регистра, блок 105A предварительной выборки, блок 105E сохранения/восстановления, контроллер 105D слоя и интерфейс 105G регистра. Модуль DNN 105 может включать в себя дополнительные или альтернативные компоненты в некоторых вариантах осуществления.

[0061] Модуль DNN 105 работает в сочетании с другими внешними вычислительными компонентами в некоторых конфигурациях. Например, модуль DNN 105 соединен с хост–системой на чипе (“хост–SoC”) 130 процессора приложения в некоторых вариантах осуществления. Модуль DNN 105 может быть соединен с хост–SoC 130 через интерфейс PCIe, например. Соответствующие компоненты PCIe, такие как PCIe–конечная точка 135, могут быть использованы для задействования этих соединений.

[0062] Хост–SoC 130 служит в качестве процессора приложения для модуля DNN 105. Основная операционная система, приложение и вспомогательная обработка датчиков выполняются хост–SoC 130. Хост–SoC 130 также может соединяться с источником 102 входных данных, например, внешней камерой, которая предоставляет входные данные, такие как данные изображения, в модуль DNN 105.

[0063] DDR DRAM 155 также может соединяться с хост–SoC 130, которая может использоваться в качестве основной системной памяти. Эта память доступна из хост–SoC 130 через инфраструктуру 120 с высокой пропускной способностью (например PCIe–шину) посредством контроллера памяти 145. Инфраструктура 120 с высокой пропускной способностью обеспечивает мелкие транзакции передачи сообщений двунаправленного прямого доступа к памяти (“DMA”) и более крупные транзакции DMA. Мост 115 и инфраструктура 110 с низкой пропускной способностью могут соединять модуль DNN 105 с хостом–SoC 130 для суб–модульной конфигурации и других функций.

[0064] Модуль DNN 105 может включать в себя механизм DMA 105В, который сконфигурирован, чтобы перемещать данные в основную память 155 и из нее. Механизм DMA 105B имеет два канала в некоторых вариантах осуществления. Один канал предназначен для выборки дескрипторов операций, в то время как другой канал предназначен для операций М2М. Дескриптор DMA, может быть встроен в дескриптор M2M. Дескрипторы в этом контексте являются дескрипторами DMA, которые используются для перемещения содержимого памяти, что не следует путать с дескрипторами операций, описанными выше.

[0065] Для того, чтобы разгрузить локальную память BaSRAM 150, а также обеспечить больше места для входных данных и данных весов, выход активации может опционально передаваться непосредственно на DDR память 155. При потоковой передаче данных в DDR память 155, модуль DNN 105 будет накапливать достаточно данных для пакетной транзакции по инфраструктуре 120 с высокой пропускной способностью и будет буферизовать достаточно транзакций, чтобы минимизировать противодавление на нейроны 105F. Дополнительные подробности, касающиеся операции модуля DNN 105, будут описаны ниже.

[0066] Фиг. 2А и 2В представляют собой структурные схемы архитектуры вычислительной системы, показывающие аспекты конфигурации и работы модуля DNN 105 для сжатия данных активации, согласно одному варианту осуществления. Как показано на фиг. 2A и кратко описано выше, модуль DNN 105 включает в себя один или несколько нейронов 105F и блок 200 сжатия. Блок 200 сжатия реализован с помощью блока 105C загрузки/сохранения в некоторых вариантах осуществления, но может быть реализован другими способами в других вариантах осуществления.

[0067] Блок 200 сжатия может получить несжатую порцию данных 202 активации, генерируемых одним или несколькими нейронами 105F. Несжатая порция данных 202 включает в себя фиксированное число байтов, например 64 байта, в некоторых вариантах осуществления.

[0068] Блок 200 сжатия может сжимать несжатую порцию данных 202, чтобы генерировать сжатую порцию данных 204 активации. Сжатая порция данных 204 активации затем может быть сохранена в памяти 206. Например, сжатая порция данных 204 активации может быть сохранена в LPDDR4 памяти 155, обеспеченной хостом приложения, или может быть сохранена в BASRAM 150, обеспеченной модулем DNN 105. Как будет описано более подробно ниже, технологии, раскрытые в данном документе, могут использовать сжатие и распаковку, чтобы снижать использование шины памяти при сохранении или извлечении сжатых или распакованных данных активации из LPDDR4 памяти 155 или BASRAM 150. Дополнительные подробности, касающиеся этих технологий, описаны ниже со ссылкой на фиг. 2A–9.

[0069] Как показано на фиг. 2B, блок 200 сжатия может генерировать часть 208 маски и часть 210 данных из сжатой выходной порции данных 204. Часть 208 маски сжатой выходной порции 204 включает в себя число битов, эквивалентное фиксированному числу байтов в несжатой порции данных 202. Например, если несжатая порция данных 202 включает в себя 64 байта данных, часть 208 маски сжатой выходной порции 204 будет включать в себя 64 бита (то есть 8 байтов).

[0070] Каждый бит в части 208 маски сжатой выходной порции 204 соответствует байту в несжатой порции данных 202 в некоторых вариантах осуществления. Например, бит один части 208 маски может соответствовать первому байту в несжатой порции данных 202, бит два части 208 маски может соответствовать второму байту в несжатой порции данных 202 и так далее.

[0071] Блок 200 сжатия устанавливает каждый бит в части 208 маски сжатой выходной порции 204 в логический нуль, где соответствующий байт в несжатой порции данных 202 является нулевым байтом. Блок 200 сжатия также устанавливает каждый бит в части 208 маски сжатой выходной порции 204 в логическую единицу, где соответствующий байт в несжатой порции данных 202 представляет собой ненулевой байт. Таким образом, часть 208 маски сжатой выходной порции 204 кодирует наличие и местоположение нулевых и ненулевых байтов в несжатой порции данных 202.

[0072] Блок 200 сжатия генерирует часть 210 данных сжатой выходной порции 204 путем определения числа ненулевых байтов в несжатой порции данных 202. Блок сжатия 200 затем определяет, на основе числа ненулевых байтов в несжатой порции данных 202 и числа байтов, доступных в части 210 данных сжатой выходной порции 204, число битов в части 210 данных сжатой выходной порции 204, которые доступны для сохранения каждого ненулевого байта несжатой порции данных 202. Например, если часть 210 данных сжатой порции данных 204 составляет 24 байтов в ширину (то есть 192 бита), и имеется 47 ненулевых байтов в несжатой порции данных 202, четыре бита доступны в части 210 данных для сохранения каждого ненулевого байта из несжатой порции данных 202.

[0073] В некоторых вариантах осуществления, блок 200 сжатия может также определить число дополнительных битов, если таковые имеются, в части 210 данных сжатой выходной порции 204, которые доступны для сохранения ненулевых байтов несжатой порции данных 202. В примере, приведенном выше, например, четыре дополнительных бита доступны для сохранения ненулевых байтов (т.е. 192 mod 47=четыре бита). Модуль 200 сжатия может назначить эти дополнительные биты одному или нескольким ненулевым байтам в несжатой порции данных 204 перед усечением одного или нескольких ненулевых байтов. Например, модуль 200 сжатия может назначить эти дополнительные биты первым N байтам в части 210 данных сжатой выходной порции 204.

[0074] Блок 200 сжатия затем усекает ненулевые байты в несжатой порции данных 202 до определенного числа битов, доступных в части 210 данных для сохранения каждого ненулевого байта (т.е. четыре в приведенном выше примере). Блок 200 сжатия отсекает LSB ненулевых байтов, чтобы соответствовать доступному числу битов в части 210 данных, в одном варианте осуществления. В другом варианте осуществления, блок 200 сжатия усекает MSB ненулевых байтов. Блок 200 сжатия затем сохраняет усеченные ненулевые байты в части 210 данных сжатой выходной порции 204. Сжатая выходная порция 204, включая часть 208 маски и часть 210 данных, затем может быть выведена, например, во внутриплатную память в модуле DNN 105 или во внеплатную память хоста приложения модуля DNN 105. Дополнительные подробности, касающиеся процесса сжатия, описанного выше, будут приведены ниже в отношении фиг. 3 и 4.

[0075] Как кратко описано выше, два или более битов в части 208 маски сжатой выходной порции 204 соответствуют байту в несжатой порции данных 202 в некоторых вариантах осуществления. В этих вариантах осуществления, биты в части 208 маски сжатой выходной порции 204 могут указывать, что не только имеется соответствующий байт в несжатой порции 202, но и его приблизительную величину. Например, и без ограничения, часть 208 маски может включать в себя два бита на байт в несжатой порции данных 202. В этом примере, 00 может указывать, что MSB соответствующего ненулевого значения в несжатой порции данных 202 является нулем, 01 может указывать, что MSB <64, 10 может указывать, что MSB <128, и 11 может указывать, что MSB >128. Эти значения могут быть использованы, чтобы идентифицировать, какие MSB байтов в несжатой порции данных 202 могут быть усечены. Например, если MSB конкретного байта <64, то верхние два MSB могут быть усечены без потери данных.

[0076] Фиг. 3 представляет собой диаграмму структуры данных, которая иллюстрирует аспекты работы модуля DNN 105 для сжатия порций несжатых данных 202 активации со ссылкой на примерную порцию несжатых данных 202 активации, в соответствии с одним вариантом осуществления. В примере, показанном на фиг. 3, несжатая порция данных 202 активации имеет длину 64 байта. Байты нуль, один и 63 порции несжатых данных 202 активации являются нулевыми байтами. Байты два, три и 62 порции несжатых данных 202 активации являются ненулевыми байтами, хранящими значения 112, 121 и два соответственно. Байты с 4 по 61 примерной порции несжатых данных 202 активации могут хранить нулевые или ненулевые байты.

[0077] Как описано выше, модуль 200 сжатия может генерировать часть 208 маски, которая кодирует наличие и местоположение нулевых и ненулевых байтов в несжатой порции данных 202 активации. В этом примере, например, биты нуль, один и 63 части 208 маски были установлены в логические нули, чтобы указывать наличие нулевых байтов в соответствующих местоположениях в несжатой порции данных 202 активации. Аналогично, биты два, три и 62 части 208 маски были установлены в логическую единицу, чтобы указывать, что байты два, три и 62 несжатой порции данных 202 активации хранят ненулевые байты.

[0078] Как описано выше, модуль 200 сжатия генерирует часть 210 данных сжатой выходной порции 204 путем определения числа ненулевых байтов в несжатой порции данных 202. В примере, показанном на фиг. 3, например, несжатая порция данных 202 включает в себя 47 ненулевых байта (не все из которых показаны на фиг. 3). Блок 200 сжатия затем определяет, на основе числа ненулевых байтов в несжатой порции данных 202, и числа байтов, доступных в части 210 данных сжатой выходной порции 204, число битов в блоке 210 данных сжатой выходной порции 204, которые доступны для сохранения каждого ненулевого байта несжатой порции данных 202.

[0079] В примере, показанном на фиг. 3, например, часть 210 данных сжатой порции данных 204 составляет 24 байта (то есть 192 бита), и имеется 47 ненулевых байтов в несжатой порции данных 202. В результате, четыре бита доступны в части 210 данных для сохранения каждого ненулевого байта из несжатой порции данных 202 (т.е. 192/47=4 остаток 4).

[0080] Кроме того, как обсуждалось выше, блок 200 сжатия может также определить число дополнительных битов, если таковые имеются, в части 210 данных сжатой выходной порции 204, которые доступны для сохранения ненулевых байтов несжатой порции данных 202. В примере, показанном на фиг. 3, например, четыре дополнительных бита доступны для сохранения ненулевых байтов (т.е. 192 mod 47=четыре бита). Модуль 200 сжатия может назначить эти дополнительные биты одному или нескольким ненулевым байтам в несжатой порции данных 204 перед усечением одного или нескольких ненулевых байтов. В примере, показанном на фиг. 3, один из четырех дополнительных битов назначены каждому из первых четырех ненулевых байтов в порции несжатых данных 202 активации. В результате, первые четыре байта несжатой порции данных 202 активации будут усечены до пяти битов, а не четырех.

[0081] Блок 200 сжатия затем усекает ненулевые байты в несжатой порции данных 202 до определенного числа битов, доступных в части 210 данных для сохранения каждого ненулевого байта (т.е. пяти битов для первых четырех ненулевых байтов в приведенном выше примере). В примере, показанном на фиг. 3, блок 200 сжатия усекает LSB ненулевых байтов, чтобы соответствовать доступному числу битов (т.е. четырем в этом примере) в части 210 данных, в одном варианте осуществления. В другом варианте осуществления, блок 200 сжатия усекает MSB ненулевых байтов.

[0082] Как показано на фиг. 3, второй байт несжатой порции данных 202 активации сохраняет значение 113 (01110001). Поскольку пять битов были назначены первым четырем ненулевым значениям в несжатой порции данных 202 активации, три LSB этого значения усекаются, приводя в результате к значению 01110, сохраненному в первом местоположении в сжатой порции данных 210 активации. Третий байт несжатой порции данных 202 активации сохраняет значение 121 (01111001). Поскольку пять битов были назначены первым четырем ненулевым значениям в несжатой порции данных 202 активации, три LSB этого значения усекаются, приводя в результате к значению 01111, сохраненному во втором местоположении в сжатой порции данных 210 активации.

[0083] В примере, показанном на фиг. 3, 62–ой байт несжатой порции данных 202 активации сохраняет значение 2 (00000010). Поскольку четыре бита были назначены с 5–го по 63–ое ненулевым значениям в несжатой порции данных 202 активации, четыре LSB этого значения усекаются, приводя в результате к значению 0000, сохраненному в 62–ом местоположении в сжатой порции данных 210 активации. Другие ненулевые байты в несжатой порции данных 202 активации могут быть усечены и сохранены в части 210 данных сжатой порции данных 204 активации аналогичным образом.

[0084] После того, как все ненулевые байты порции несжатых данных 202 активации, были сохранены в части 203 данных, блок 200 сжатия сохраняет сжатую выходную порцию 204, включая часть 208 маски и часть 210 данных, например, во внутриплатной памяти в модуле DNN 105 или внеплатной памяти хоста приложения модуля DNN 105. Дополнительные подробности, касающиеся процесса сжатия, представлены ниже со ссылкой на фиг. 4.

[0085] На фиг. 4 показана схема последовательности операций, показывающая процедуру 400, которая иллюстрирует аспекты работы модуля DNN 105 для сжатия порций несжатых данных 202 активации, в соответствии с одним вариантом осуществления, раскрытым в данном документе. Следует иметь в виду, что логические операции, описанные здесь со ссылкой на фиг. 4 и другие фиг., могут быть реализованы (1) как последовательность реализуемых компьютером действий или программных модулей, работающих на вычислительном устройстве, и/или (2) как взаимосвязанные машинные логические схемы или схемные модули в вычислительном устройстве.

[0086] Конкретное осуществление технологий, раскрытых в данном документе, является вопросом выбора в зависимости от производительности и других требований вычислительного устройства. Соответственно, логические операции, описанные в настоящем документе, упоминаются по–разному как состояния, операции, структурные устройства, действия или модули. Эти состояния, операции, структурные устройства, действия и модули могут быть реализованы в аппаратных средствах, программном обеспечении, встроенном программном обеспечении, в цифровой логике специального назначения и любой их комбинации. Следует иметь в виду, что может выполняться больше или меньше операций, чем показано на чертежах и описано в данном документе. Эти операции также могут выполняться в порядке ином, чем описано здесь.

[0087] Процедура 400 начинается с операции 402, при которой устройство 200 сжатия определяет число ненулевых байтов в несжатой порции данных 202 активации. Процедура 400 затем переходит к операции 404, при которой устройство 200 сжатия определяет, является ли число ненулевых байтов в несжатой порции данных 202 активации меньшим или равным числу байтов, доступных в части 210 данных сжатой порции данных 204 активации. Ненулевые байты несжатой порции данных 202 активации не требуется сжимать, если число ненулевых байтов меньше или равно числу байтов, доступных в части 210 данных сжатой порции данных 204 активации. Соответственно, в этом случае процедура 400 переходит к операции 408, где ненулевые байты сохраняются в части 210 данных без усечения.

[0088] Если число ненулевых байтов в несжатой порции данных 202 активации больше, чем число байтов, доступных в части 210 данных сжатой порции данных 204 активации, процедура 400 переходит от операции 406 к операции 412. В операции 412, блок 200 сжатия определяет число битов части 210 данных сжатой порции выходных данных 204, доступных для сохранения усеченных ненулевых байтов несжатой порции данных 202 активации, как описано выше. Процедура 400 затем переходит от операции 412 к операции 414.

[0089] В операции 414, блок 200 сжатия определяет число дополнительных битов, если таковые имеются, в части 210 данных сжатой выходной порции 204, которые доступны для сохранения ненулевых байтов несжатой порции данных 202. Как обсуждалось выше, модуль 200 сжатия может назначать эти дополнительные биты, одному или нескольким ненулевым байтам в несжатой порции данных 204 перед усечением одного или нескольких ненулевых байтов. Это происходит в операции 416.

[0090] От операции 416, процедура 400 переходят к операции 418, в которой блок 200 сжатия устанавливает биты в части 208 маски сжатой порции данных 204 активации в логическую единицу, когда соответствующий байт в несжатой порции активации 202 является ненулевым. Блок 200 сжатия также устанавливает биты в части 208 маски сжатой порции данных 204 активации в логический нуль, когда соответствующий байт в несжатой порции активации 202 является нулевым.

[0091] От операции 418, процедура 400 переходят к операции 420, при которой блок 200 сжатия усекает LSB или MSB ненулевых байтов в несжатой порции данных 202 до определенного количества битов, доступных в части 210 данных для каждого ненулевого байта. Усеченные ненулевые байты затем сохраняются в части 210 данных сжатой порции данных 204 активации. Блок 200 сжатия затем сохраняет сжатую выходную порцию 204, включая часть 208 маски и часть 210 данных во внутриплатной памяти в модуле DNN 105 или внеплатной памяти хоста приложения модуля DNN 105. От операций 408 и 420, процедура 400 переходит к операции 410, где она заканчивается.

[0092] Фиг. 5А и 5В представляют собой схемы архитектуры вычислительной системы, показывающие аспекты конфигурации и работы модуля DNN 105 для распаковки сжатых данных активации, согласно одному варианту осуществления. Как кратко описано выше и как показано на фиг. 5А и 5В, модуль DNN 105 может также включать в себя блок 500 распаковки, который может распаковывать порции данных 204 активации, которые были сжаты, как описано выше.

[0093] Например, блок 500 распаковки может принять сжатую порцию данных 204 активации из памяти 206, такой как память в процессоре DNN или память хоста приложения. Блок 500 распаковки может затем определить число ненулевых байтов в части 210 данных сжатой порции данных 204 на основе числа битов логического истинного значения в части 208 маски сжатой порции 204. Блок 500 распаковки может также определить местоположения ненулевых байтов в распакованной порции данных 502 на основе местоположений битов логического истинного значения в части 208 маски сжатой выходной порции 204. Блок 500 распаковки может определить местоположения нулевых байтов в распакованной порции данных 502 аналогичным образом.

[0094] Блок 500 распаковки может также определить число битов, используемых блоком 200 сжатия для сохранения каждого из усеченных ненулевых байтов в части 210 данных сжатой выходной порции 204. Блок 500 распаковки может определить число битов, используемых для сохранения каждого усеченного ненулевого байта на основе числа ненулевых байтов в сжатой порции данных 204 (как указано в части 208 маски) и целевого размера распакованной выходной порции 502.

[0095] В приведенном выше примере, например, если часть данных сжатой порции данных 204 составляет 24 байта (то есть 192 бита), и имеется 47 ненулевых байтов в несжатой порции данных 202, это означает, что блок 200 сжатия использовал четыре бита для сохранения каждого усеченного ненулевого байта несжатой порции данных 202 в части 210 данных. Блок 500 распаковки может также определить число дополнительных битов, если таковые имеются, которые блок 200 сжатия выделил одному или нескольким усеченным ненулевым байтам, сохраненным в части 210 данных сжатой выходной порции 204.

[0096] Для каждой битовой позиции в части 208 маски сжатой выходной порции 204, которая представляет собой логический нуль, блок 500 распаковки вставляет нулевой байт в соответствующую позицию распакованной выходной порции 502. Для каждой позиции в части 208 маски, которая является логической единицей, блок 500 распаковки вставляет усеченные ненулевые байты из соответствующей позиции сжатой входной порции 204 в соответствующую позицию распакованной выходной порции 502 вместе с числом нулевых битов, эквивалентным числу битов, усеченных во время сжатия сжатой выходной порции 204. Нулевые биты могут быть вставлены в LSB или MSB усеченных ненулевых байтов в зависимости от того, какие биты были усечены во время сжатия.

[0097] Как упоминалось выше, блок 500 распаковки также добавляет смещение (например, 00000001) к одному или нескольким усеченным ненулевым байтам, сохраненным в распакованной выходной порции 502 в некоторых вариантах осуществления. Например, смещение может быть добавлено к ненулевым байтам несжатой порции данных 202, которые становятся нулевыми байтами после сжатия. Таким образом, ненулевые байты не будут становиться нулевыми байтами при распаковке.

[0098] Фиг. 6 представляет собой диаграмму структуры данных, которая иллюстрирует аспекты работы модуля DN 105 для распаковки данных активации со ссылкой на примерную порцию сжатых данных активации, согласно одному варианту осуществления. Пример, показанный на фиг. 6, иллюстрирует распаковку сжатых данных 204 активации, полученных в примере, описанном выше со ссылкой на фиг. 3. Как показано на фиг. 6, часть 208 маски сохраняет нули в битах нуль, один и 63, и сохранят единицу в битах два, три и 62. Часть 210 данных сохраняет значения 01110, 01111 и 0000, как показано на фиг. 6.

[0099] Когда блок 500 распаковки выполняет операции обработки, описанные выше, логический нуль в первой битовой позиции части 208 маски будет вынуждать блок 500 распаковки сохранять нулевой байт как первый байт распакованной порции данных 502 активации. Аналогичным образом, логический нуль во второй битовой позиции части 208 маски будет вынуждать блок 500 распаковки сохранять нулевой байт как второй байт распакованной порции данных 502.

[00100] Логическая единица в третьей позиции части 208 маски будет вынуждать блок 500 распаковки извлекать первые пять битов (т.е. 01110) части 210 данных и вставлять три LSB, в результате чего значение 01110000 (112) сохраняется как третий байт распакованной порции данных 502 активации. Аналогичным образом, логическая единица в четвертой битовой позиции части 208 маски будет вынуждать блок 500 распаковки извлекать вторые пять битов (т.е. 01111) части 210 данных и вставлять три LSB, в результате чего значение 01111000 (120) сохраняется как четвертый байт распакованной порции данных 502 активации.

[00101] Логическая единица в 63–ей битовой позиции части 208 маски будет вынуждать блок 500 распаковки извлекать последние четыре бита части 210 данных (т.е. 0000) и вставлять четыре нулевых LSB, в результате чего значение нуля сохраняется в 63–ой байтовой позиции распакованной порции данных 502 активации. Логический нуль в последней битовой позиции части 208 маски будет вынуждать блок 500 распаковки сохранять нулевой байт как последний байт распакованной порции 502 данных.

[00102] Как описано выше, блок 500 распаковки может добавить значение смещения к определенным байтам в распакованной порции данных 502 активации. Например, блок 500 распаковки может добавить значение смещения, такое как 00000001, к байтам, которые были ненулевыми в несжатой порции данных 202 активации, но которые были сжаты в нулевые байты в сжатой порции данных 204 активации.

[00103] В примере, показанном на фиг. 6, последний байт в порции 210 данных был ненулевым (то есть два) в несжатой порции данных 202 активации, но стал нулем в сжатой порции данных 504 активации. Соответственно, блок 500 распаковки может добавить значение смещения, такое как 00000001, к этому байту, тем самым гарантируя, что ненулевые байты в несжатых порциях данных 202 активации не будет сжиматься до нулевых байтов.

[00104] Фиг. 7 является блок–схемой последовательности операций, показывающей процедуру 700, которая иллюстрирует аспекты работы модуля DNN 105 для распаковки данных активации, в соответствии с одним вариантом осуществления, раскрытым в данном документе. Процедура 700 начинается в операции 702, где блок 500 распаковки использует часть 208 маски сжатой порции данных 204 активации, чтобы определить число ненулевых байтов и их местоположения в распакованной порции данных 502 активации.

[00105] Процедура 700 переходит от операции 702 к операции 704, где блок 500 распаковки определяет, является ли число ненулевых байтов в сжатой порции данных 204 активации меньшим или равным числу байтов распакованной порции данных 502 активации. Как обсуждалось выше, ненулевые байты сжатой порции данных 204 активации не требуется распаковывать, если число ненулевых байтов меньше или равно числу байтов распакованной порции данных 502 активации. Соответственно, в этом случае процедура 700 переходит к операции 708, где ненулевые байты в сжатой порции данных 204 активации сохраняются в распакованной порции данных 502 активации без изменений.

[00106] Если число ненулевых байтов в сжатой порции данных 504 активации больше, чем число байтов в распакованной порции данных 502 активации, процедура 700 переходит от операции 4706 к операции 712. В операции 712, блок 500 распаковки определяет число битов части 210 данных сжатой порции выходных данные 204, которые блок 200 сжатия использовал, чтобы сохранить каждый усеченный ненулевой байт несжатой порции данных 202 активации. Процедура 700 затем переходит от операции 712 к операции 714, как описано выше.

[00107] В операции 714, блок 500 распаковки определяет число дополнительных битов, если таковые имеются, которые были использованы, чтобы сохранять ненулевые байты несжатой порции данных 202. Блок 500 распаковки может назначить эти дополнительные биты одному или нескольким ненулевым байтам в распакованной порции данных 502, как описано выше. Это происходит в операции 716.

[00108] От операции 716 процедура 700 переходят к операции 718, в которой блок 500 распаковки вставляет нулевой байт в соответствующую позицию распакованной выходной порции 502 для каждой битовой позиции в части 208 маски сжатой порции 204, которая представляет собой логический нуль. Для каждой битовой позиции в части 208 маски сжатой выходной порции 204, которая представляет собой логическую единицу, блок 500 распаковки вставляет усеченные ненулевые байты из соответствующих позиций сжатой входной порции 204 в соответствующую позицию распакованной выходной порции 502 вместе с числом нулевых битов, эквивалентным числу битов, усеченных во время сжатия сжатой выходной порции 204. Нулевые биты могут быть вставлены в LSB или MSB усеченных ненулевых байтов, в зависимости от того, какие биты были усечены во время сжатия. Это происходит в операции 720.

[00109] Блок 500 распаковки может также добавить значение смещения к одному или нескольким усеченным ненулевым байтам, сохраненным в распакованной выходной порции 502, в некоторых вариантах осуществления. Например, смещение может быть добавлено к ненулевым байтам несжатой порции данных 202, которые становятся нулевыми байтами после сжатия. Таким образом, ненулевые байты не будут становиться нулевые байтами при сжатии и распаковке. Смещение может быть добавлено ко всем байтам в распакованной порции данных 502 активации в других вариантах осуществления.

[00110] Блок 500 распаковки затем сохраняет распакованную выходную порцию 502 во внутриплатной памяти в модуле DNN 105 или внеплатной памяти хоста приложения модуля DNN 105 для использования нейронами 105F. От операций 708 и 720, процедура 400 переходит к операции 710, где она заканчивается.

[00111] Фиг. 8 представляет собой схему архитектуры компьютера, показывающую иллюстративное компьютерные аппаратные средства и программное обеспечение для архитектуры вычислительного устройства, которое может действовать в качестве хоста приложения для модуля DNN 105, представленного в данном документе. В частности, архитектура, показанная на фиг. 8, может быть использована для реализации серверного компьютера, мобильного телефона, электронного читающего устройства, смартфона, настольного компьютера, устройства AR/VR, планшетного компьютера, портативного компьютера или другого типа вычислительного устройства, пригодного для использования с модулем DNN 105.

[00112] Компьютер 800, иллюстрируемый на фиг. 8, включает в себя центральный процессор (“CPU”) 802, системную память 804, включающую в себя память с произвольным доступом (“RAM”) 806 и постоянную память (“ROM”) 808, и системную шину 810, которая соединяет память 804 с CPU 802. Базовая система ввода/вывода (“BIOS” или “прошивка”), содержащая основные процедуры, которые помогают передавать информацию между элементами в пределах компьютера 800, например, во время запуска, может храниться в ROM 808. Компьютер 800 дополнительно включает в себя устройство 812 массовой памяти для хранения операционной системы 822, прикладных программ и других типов программ. Устройство 812 массовой памяти также может быть сконфигурировано для хранения других типов программ и данных.

[00113] Устройство 812 массовой памяти соединено с CPU 802 через контроллер массовой памяти (не показан), соединенный с шиной 810. Устройство 812 массовой памяти и ассоциированные с ним считываемые компьютером носители обеспечивают энергонезависимое устройство хранения для компьютера 800. Хотя описание считываемых компьютером носителей, содержащееся в данном документе, ссылается на устройство массовой памяти, такое как жесткий диск, накопитель CD–ROM, накопитель DVD–ROM или USB устройство хранения, специалистам в данной области техники должно быть понятно, что считываемые компьютером носители могут представлять собой любые имеющиеся компьютерные носители хранения или коммуникационные среды, доступ к которым может осуществляться компьютером 800.

[00114] Коммуникационные среды включают в себя считываемые компьютером инструкции, структуры данных, программные модули или другие данные в виде модулированного сигнала данных, такого как несущая волна или другой транспортный механизм, и включают в себя любые средства доставки. Термин “модулированный сигнал данных” означает сигнал, который имеет одну или несколько его характеристик, установленных или изменяемых таким образом, чтобы кодировать информацию в сигнале. В качестве примера, а не ограничения, коммуникационные среды включают в себя проводные среды, такие как проводная сеть или прямое проводное соединение, и беспроводные среды, такие как акустические, радиочастотные, инфракрасные и другие беспроводные среды. Комбинации любых из вышеупомянутых также должны быть включены в объем считываемых компьютером носителей.

[00115] В качестве примера, а не ограничения, компьютерные носители хранения могут включать в себя энергозависимые и энергонезависимые, съемные и несъемные носители, реализованные любым способом или технологией для хранения информации, такой как считываемые компьютером инструкции, структуры данных, программные модули или другие данные. Например, компьютерные носители хранения включают в себя, но без ограничения, RAM, ROM, EPROM, EEPROM, флэш–память или другую технологию твердотельной памяти, CD–ROM, цифровые универсальные диски (“DVD”), HD–DVD, BLU–RAY или другое оптическое устройство хранения, магнитные кассеты, магнитную ленту, накопитель на магнитных дисках или другие магнитные устройства хранения или любой другой носитель, который может использоваться для хранения требуемой информации и к которому можно осуществлять доступ с помощью компьютера 800. Для целей формулы изобретения, фраза “компьютерный носитель хранения” и ее варианты не включают в себя волны или сигналы как таковые или коммуникационные среды.

[00116] В соответствии с различными конфигурациями, компьютер 800 может работать в сетевой среде, используя логические соединения с удаленными компьютерами через сеть, такую как сеть 820. Компьютер 800 может соединяться с сетью 820 через блок 816 сетевого интерфейса, соединенный с шиной 810. Следует отметить, что блок 816 сетевого интерфейса также может быть использован для соединения с другими типами сетей и удаленных компьютерных систем. Компьютер 800 также может включать в себя контроллер 818 ввода/вывода для приема и обработки ввода от ряда других устройств, включая клавиатуру, мышь, сенсорный ввод, электронный стилус (не показаны на фиг. 8) или физический датчик, такой как видеокамера. Аналогичным образом, контроллер 818 ввода/вывода может обеспечивать вывод на экран дисплея или другой тип устройства вывода (также не показаны на фиг. 8).

[00117] Следует понимать, что компоненты программного обеспечения, описанные в данном документе, при загрузке в CPU 802 и исполнении, могут трансформировать CPU 802 и весь компьютер 800 из универсального вычислительного устройства в специализированное вычислительное устройство, настроенного, чтобы обеспечивать функциональность, представленную в данном документе. CPU 802 может быть изготовлен из любого числа транзисторов или других дискретных схемных элементов, которые могут индивидуально или совместно предполагать ряд состояний. Более конкретно, CPU 802 может работать как конечный автомат, в ответ на исполняемые инструкции, содержащихся в программных модулях, раскрытых в данном документе. Эти исполняемые компьютером инструкции могут трансформировать CPU 802 путем определения того, как CPU 802 переходит между состояниями, тем самым трансформируя транзисторы или другие дискретные аппаратные элементы, образующие CPU 802.

[00118] Кодирование программных модулей, представленных в данном документе, также может трансформировать физическую структуру считываемых компьютером носителей, представленных в настоящем документе. Конкретная трансформация физической структуры зависит от различных факторов, в разных реализации этого описания. Примеры таких факторов включают, но без ограничения, технологию, используемую для реализации считываемого компьютером носителя, независимо от того, характеризуется ли считываемый компьютером носитель как первичное или вторичное устройство хранения, и тому подобное. Например, если считываемый компьютером носитель реализован как память на основе полупроводников, то описанное здесь программное обеспечение может быть закодировано на считываемом компьютером носителе путем трансформации физического состояния полупроводниковой памяти. Например, программное обеспечение может трансформировать состояние транзисторов, конденсаторов или других дискретных схемных элементов, образующих полупроводниковую память. Программное обеспечение также может трансформировать физическое состояние таких компонентов, чтобы сохранять на них данные.

[00119] В качестве другого примера, считываемые компьютером носители, описанные в данном документе, могут быть реализованы с использованием магнитных или оптических технологий. В таких реализациях, представленное здесь программное обеспечение может трансформировать физическое состояние магнитных или оптических носителей, когда программное обеспечение кодируется в них. Эти трансформации могут включать в себя изменение магнитных характеристик конкретных мест (ячеек) в пределах данного магнитного носителя. Эти трансформации могут также включать в себя изменениях физических признаков или характеристик конкретных мест в пределах данного оптического носителя, чтобы изменить оптические характеристики этих мест. Другие трансформации физических носителей возможны без отклонения от объема и сущности настоящего описания, причем вышеизложенные примеры приведены только для облегчения этого обсуждения.

[00120] В свете вышеизложенного, следует понимать, что многие типы физических трансформаций происходят в компьютере 800 для того, чтобы сохранять и исполнять представленные здесь программные компоненты. Следует также отметить, что архитектура, показанная на фиг. 8 для компьютера 800, или аналогичная архитектура может быть использована для реализации других типов вычислительных устройств, включая портативные компьютеры, видеоигровые устройства, встроенные компьютерные системы, мобильные устройства, такие как смартфоны, планшеты и устройства AR/VR, и другие типы вычислительных устройств, известные специалистам в данной области техники. Также предполагается, что компьютер 800 может не только включать в себя все из компонентов, показанных на фиг. 8, но может включать в себя другие компоненты, которые явно не показаны на фиг. 8, или может использовать архитектуру совершенно иную, чем архитектура, показанная на фиг. 8.

[00121] Фиг. 9 представляет собой структурную схему сети, иллюстрирующую распределенную сетевую вычислительную среду 900, в которой аспекты раскрытых технологий могут быть реализованы в соответствии с различными вариантами осуществления, представленными в данном документе. Как показано на фиг. 9, один или несколько серверных компьютеров 900A могут быть соединены между собой через коммуникационную сеть 820 (которая может быть любой из фиксированной проводной или беспроводной LAN, WAN, интранета, экстранета, одноранговой сети, виртуальной частной сети, Интернета, сети связи Bluetooth, проприетарной низковольтной коммуникационной сети или других коммуникационных сетей или их комбинацией) с рядом клиентских вычислительных устройств, таких как, но без ограничения, планшетный компьютер 900B, игровая консоль 900C, смарт–часы 900D, телефон 900E, например смартфон, персональный компьютер 900F и устройства AR/VR 900G.

[00122] В сетевой среде, в которой сеть связи 820 представляет собой Интернет, например, серверный компьютер 900A может быть специализированным серверным компьютером, действующим, чтобы обрабатывать и передавать данные на и от клиентских вычислительных устройств 900B–900G с помощью любого из множества известных протоколов, таких как протокол передачи гипертекста (“HTTP”), протокол передачи файлов (“FTP”) или простой протокол доступа к объекту (“SOAP”). Кроме того, сетевая вычислительная среда 900 может использовать различные протоколы защиты данных, такие как протокол безопасных сокетов (“SSL”) или очень хорошей конфиденциальности (“PGP”). Каждое из клиентских вычислительных устройств 900B–900G может быть оснащено операционной системой, действующей для поддержки одного или нескольких вычислительных приложений или терминальных сеансов, таких как веб–браузер (не показано на фиг. 9) или другой графический пользовательский интерфейс (не показано фиг. 9) или мобильная среда рабочего стола (не показано на фиг. 9), чтобы получить доступ к серверному компьютеру 900A.

[00123] Серверный компьютер 900A может быть коммуникативно связан с другими вычислительными средами (не показаны на фиг. 9) и получает данные о взаимодействиях участвующего пользователя/сетевых ресурсов. В иллюстративной операции, пользователь (не показан на фиг. 9) может взаимодействовать с вычислительным приложением, работающим на клиентском вычислительном устройстве 900B–900G, чтобы получить требуемые данные и/или выполнять другие вычислительные приложения.

[00124] Данные и/или вычислительные приложения могут сохраняться на сервере 900A или серверах 900A и передаваться взаимодействующим пользователям через клиентские вычислительные устройства 900B–900G через примерную сеть связи 820. Участвующий пользователь (не показан на фиг. 9) может запросить доступ к определенным данным и приложениям, хостируемым полностью или частично на серверном компьютере 8800А. Эти данные могут передаваться между клиентскими вычислительными устройствами 900B–900G и серверным компьютером 900A для обработки и хранения.

[00125] Серверный компьютер 900A может хостировать вычислительные приложения, процессы и апплеты для генерации, аутентификации, шифрования и передачи данных и приложений, а также может взаимодействовать с другими серверными вычислительными средами (не показаны на фиг. 9), поставщиками услуг третьей стороны (не показаны на фиг. 9), сетевыми устройствами хранения данных (“NAS”) и сетями хранения данных (“SAN”) для реализации транзакций приложения/данных.

[00126] Следует понимать, что вычислительная архитектура, показанная на фиг. 8, и распределенная сетевая вычислительная среда, показанная на фиг. 9, были упрощены для простоты обсуждения. Следует также понимать, что вычислительная архитектура и распределенная вычислительная сеть могут включать в себя и использовать намного больше вычислительных компонентов, устройств, программного обеспечения, устройств сетевого взаимодействия и других компонентов, конкретно не описанных в настоящем документе.

[00127] Раскрытие, представленное в данном документе, также включает в себя предмет, изложенный в следующих пунктах:

[00128] Пункт 1. Процессор нейронной сети, содержащий: один или несколько нейронов и блок сжатия, сконфигурированный, чтобы принимать несжатую порцию данных, сгенерированных по меньшей мере одним из нейронов в процессоре нейронной сети, несжатая порция данных содержит фиксированное число байтов; генерировать часть маски сжатой выходной порции, часть маски содержит число битов, эквивалентное фиксированному числу байтов в несжатой порции данных, каждый бит в части маски соответствует байту в несжатой порции данных, и причем каждый бит в части маски устанавливается в логический нуль, где соответствующий байт в несжатой порции данных является нулевым, и устанавливается в логическую единицу, где соответствующий байт в несжатой порции данных является ненулевым; генерировать часть данных сжатой выходной порции путем определения числа ненулевых байтов в несжатой порции данных, определения, на основе числа ненулевых байтов в несжатой порции данных, числа битов в части данных сжатой выходной порции, доступных для сохранения усеченных ненулевых байтов несжатой порции данных, усечения ненулевых байтов в несжатой порции данных до определенного числа битов, и сохранения усеченных ненулевых байтов в части данных сжатой выходной порции; и выводить сжатую выходную порцию, причем сжатая выходная порция содержит часть маски и часть данных.

[00129] Пункт 2. Процессор нейронной сети пункта 1, причем процессор нейронной сети дополнительно содержит блок распаковки, сконфигурированный, чтобы: принимать сжатую выходную порцию; определять число ненулевых байтов в части данных несжатой порции данных на основе части маски сжатой выходной порции; определять местоположения ненулевых байтов в несжатой порции данных на основе части маски сжатой выходной порции; определять число битов, используемых блоком сжатия для сохранения усеченных ненулевых байтов в части данных сжатой выходной порции; для каждой позиции в части маски сжатой выходной порции, которая представляет собой логический нуль, вставлять нулевой байт в соответствующую позицию распакованной выходной порции; и для каждой позиции в части маски, которая является логической единицей, вставлять усеченный ненулевой байт из соответствующей позиции сжатой входной порции в соответствующую позицию распакованной выходной порции и число нулевых битов, эквивалентное числу битов, усеченных во время сжатия сжатой выходной порции.

[00130] Пункт 3. Процессор нейронной сети любого из пунктов 1 и 2, причем блок сжатия дополнительно сконфигурирован, чтобы: определять число дополнительных битов в части данных сжатой выходной порции доступных для сохранения усеченных ненулевых байтов несжатой порции данных; и выделять дополнительные биты одному или нескольким ненулевым байтам в несжатой порции данных перед усечением одного или нескольких ненулевых байтов.

[00131] Пункт 4. Процессор нейронной сети любого из пунктов 1–3, причем блок распаковки дополнительно сконфигурирован, чтобы определять число дополнительных битов, выделенных одному или нескольким ненулевым байтам, сохраненным в части данных сжатой выходной порции.

[00132] Пункт 5. Процессор нейронной сети любого из пунктов 1–4, причем блок распаковки дополнительно сконфигурирован, чтобы добавлять смещение к одному или нескольким усеченным ненулевым байтам, сохраненным в распакованной выходной порции.

[00133] Пункт 6. Процессор нейронной сети любого из пунктов 1–5, причем один или несколько младших битов (LSB) ненулевых байтов усекаются.

[00134] Пункт 7. Процессор нейронной сети любого из пунктов 1–6, причем один или несколько старших битов (MSB) ненулевых байтов усекаются.

[00135] Пункт 8. Процессор нейронной сети, содержащий: один или несколько нейронов; и блок распаковки, сконфигурированный, чтобы принимать сжатую порцию данных, содержащую часть маски и часть данных; определять число ненулевых байтов в распакованной порции данных на основе битов в части маски; определять, основываясь, по меньшей мере частично, на числе ненулевых байтов, число битов, используемых, чтобы сохранять усеченные ненулевые байты в части данных сжатой выходной порции данных; для каждой битовой позиции в части маски сжатой порции данных, которая представляет собой логический нуль, вставлять нулевой байт в соответствующую позицию распакованной порции данных; и для каждой позиции в части маски сжатой порции данных, которая представляет собой логическую единицу, вставлять усеченный ненулевой байт из соответствующей позиции в части данных сжатой порции данных в соответствующую позицию в распакованной порции данных и число нулевых битов, эквивалентное числу битов, усеченных во время сжатия сжатой порции данных.

[00136] Пункт 9. Процессор нейронной сети пункта 8, дополнительно содержащий блок сжатия, сконфигурированный, чтобы: принимать несжатую порцию данных, сгенерированных по меньшей мере одним из нейронов в процессоре нейронной сети, несжатая порция данных содержит фиксированное число байтов; генерировать часть маски сжатой порции данных, часть маски содержит число битов, эквивалентное фиксированному число байтов в несжатой порции данных, каждый бит в части маски соответствует байту в несжатой порции данных, и причем каждый бит в части маски содержит логический нуль, где соответствующий байт в несжатой порции данных является нулевым, и содержит логическую единицу, где соответствующий байт в несжатой порции данных является ненулевым; генерировать часть данных сжатой порции данных путем определения числа ненулевых байтов в несжатой порции данных, определения, на основе числа ненулевых байтов в несжатой порции данных, числа битов в части данных сжатой порции данных, доступных, чтобы сохранять усеченные ненулевые байты несжатой порции данных, усечения ненулевых байтов в несжатой порции данных до определенного числа битов, и сохранения усеченных ненулевых байтов в части данных сжатой порции данных; и выводить сжатую порцию данных, причем сжатая порция данных содержит часть маски и часть данных.

[00137] Пункт 10. Процессор нейронной сети любого из пунктов 8 и 9, причем блок сжатия дополнительно сконфигурирован, чтобы сохранять ненулевые байты в несжатой порции данных в части данных сжатой порции данных без усечения, если число ненулевых байтов в несжатой порции данных меньше или равно числу байтов в части данных сжатой порции данных.

[00138] Пункт 11. Процессор нейронной сети любого из пунктов 8–10, причем блок сжатия дополнительно сконфигурирован, чтобы: определять число дополнительных битов в части данных сжатой выходной порции, доступных для сохранения усеченных ненулевых байтов несжатой порции данных; и выделять дополнительные биты одному или нескольким ненулевым байтам в несжатой порции данных перед усечением одного или нескольких ненулевых байтов.

[00139] Пункт 12. Процессор нейронной сети любого из пунктов 8–11, причем блок распаковки дополнительно сконфигурирован, чтобы определять число дополнительных битов, выделенных одному или нескольким ненулевым байтам, сохраненным в части данных сжатой выходной порции.

[00140] Пункт 13. Процессор нейронной сети любого из пунктов 8–12, причем один или несколько младших битов (LSB) ненулевых байтов усекаются во время сжатии сжатой порции данных.

[00141] Пункт 14. Процессор нейронной сети любого из пунктов 8–13, причем один или несколько старших битов (MSB) ненулевых байтов усекаются во время сжатия сжатой порции данных.