Предлагаемое изобретение относится к области вычислительной техники, автоматики, связи и может использоваться в различных цифровых структурах и системах автоматического управления, передачи цифровой информации и т.п.

В различных вычислительных и управляющих системах широко используются компараторы, реализованные на основе эмиттерно-связанной логики [1-20], работающие по законам булевой алгебры и имеющие по выходу два логических состояния «0» и «1», характеризующихся низким и высоким потенциалами.

В работах [21-22], а также монографиях [23-25] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство «Токовый пороговый троичный D-триггер» относится к этому типу логических элементов.

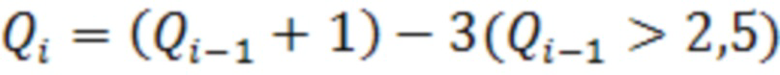

Ближайшим прототипом заявляемого устройства является логический элемент, представленный в патенте RU 2624581 («Многозначный триггер», МПК H03K 3/289, 2017 г.). Он содержит (фиг. 1) первый 1 логический элемент прямого циклического сдвига с первым 2 и вторым 3 токовыми входами, а также первым 4 и вторым 5 токовыми выходами, второй 6 логический элемент прямого циклического сдвига с первым 7 и вторым 8 токовыми входами, а также первым 9 и вторым 10 токовыми выходами, третий 11 логический элемент прямого циклического сдвига с первым 12 и вторым 13 токовыми входами, а также первым 14 и вторым 15 токовыми выходами, причем первый 7 токовый вход второго 6 логического элемента прямого циклического сдвига соединен с первым 4 токовым выходом первого 1 логического элемента прямого циклического сдвига, первый 12 токовый вход третьего 11 логического элемента прямого циклического сдвига соединен с первым 9 токовым выходом второго 6 логического элемента прямого циклического сдвига, второй 3 токовый вход первого 1 логического элемента прямого циклического сдвига соединен с первым 16 входом предустановки, второй 8 вход второго 6 логического элемента прямого циклического сдвига связан со вторым 17 входом предустановки, второй 13 вход третьего 11 логического элемента прямого циклического сдвига подключен к третьему 18 входу предустановки, второй 5 токовый выход первого 1 логического элемента прямого циклического сдвига соединен с первым 19 токовым выходом состояния устройства, второй 10 токовый выход второго 6 логического элемента прямого циклического сдвига подключен ко второму 20 токовому выходу состояния устройства, второй 15 токовый выход третьего 11 логического элемента прямого циклического сдвига соединен с третьим 21 токовым выходом состояния устройства, первый 14 токовый выход третьего 11 логического элемента прямого циклического сдвига связан с первым 2 токовым входом первого 1 логического элемента прямого циклического сдвига.

Существенным недостатком данного троичного триггера (фиг. 1), так же как и у его функционального аналога - двоичного RS-триггера, является неопределенность состояния триггера в режиме хранения данных после подачи активных уровней сигналов на 2 и более установочных входа. Применение таких триггеров ограничено в связи с невозможностью полностью исключить поступление запрещенных для корректной работы элемента памяти комбинаций установочных сигналов, а это не позволяет создать полный базис средств автоматики и вычислительной техники. Применение пороговых функций и соответствующих им пороговых элементов, кроме реализации заданной логической функции, обеспечивает масштабирование и нормализацию уровней выходных сигналов и тем самым устраняет все погрешности сигналов, возникающие до порогового элемента.

Основная задача предлагаемого изобретения состоит в создании токового порогового D-триггера, в котором внутреннее преобразование информации производится в токовой форме сигналов. В конечном итоге это позволяет обеспечить надежное функционирования при всех возможных комбинациях входных сигналов, повысить быстродействие и создать элементную базу вычислительных устройств, работающих на принципах многозначной линейной алгебры [17-19].

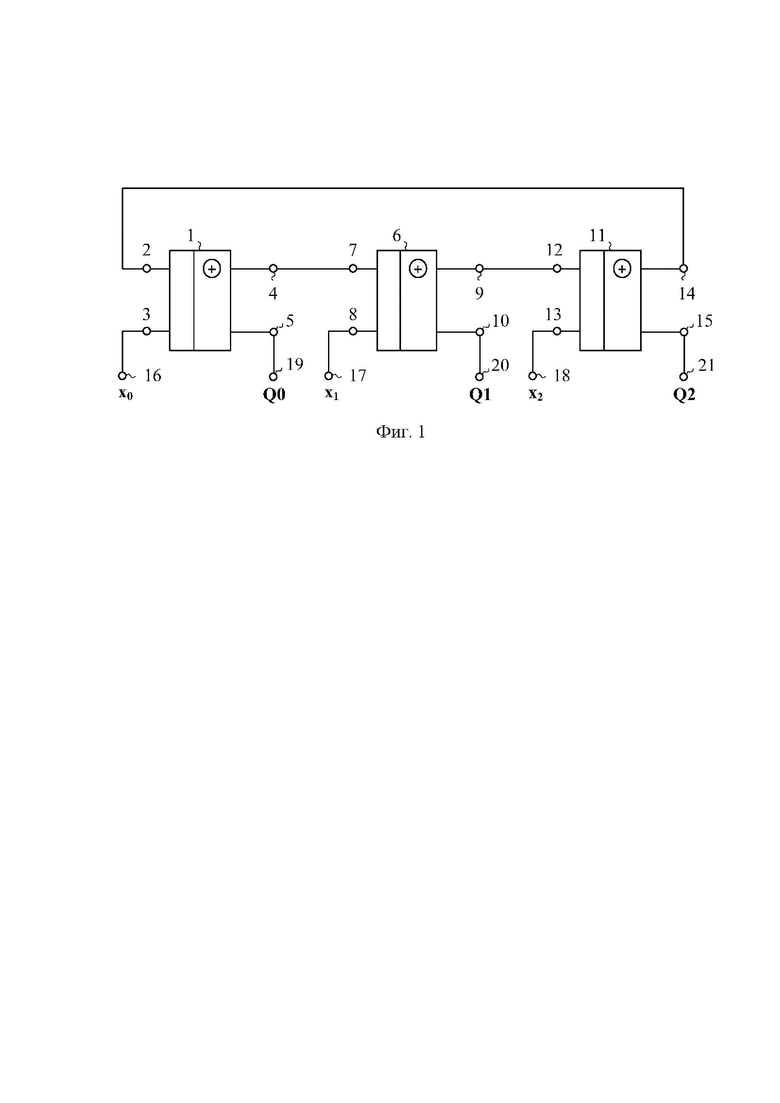

Поставленная задача решается тем, что в логическом элементе (фиг. 1), содержащем первый 1 логический элемент прямого циклического сдвига с первым 2 и вторым 3 токовыми входами, а также первым 4 и вторым 5 токовыми выходами, второй 6 логический элемент прямого циклического сдвига с первым 7 и вторым 8 токовыми входами, а также первым 9 и вторым 10 токовыми выходами, третий 11 логический элемент прямого циклического сдвига с первым 12 и вторым 13 токовыми входами, а также первым 14 и вторым 15 токовыми выходами, причем первый 7 токовый вход второго 6 логического элемента прямого циклического сдвига соединен с первым 4 токовым выходом первого 1 логического элемента прямого циклического сдвига, первый 12 токовый вход третьего 11 логического элемента прямого циклического сдвига соединен с первым 9 токовым выходом второго 6 логического элемента прямого циклического сдвига, второй 3 токовый вход первого 1 логического элемента прямого циклического сдвига соединен с первым 16 входом предустановки, второй 8 вход второго 6 логического элемента прямого циклического сдвига связан со вторым 17 входом предустановки, второй 13 вход третьего 11 логического элемента прямого циклического сдвига подключен к третьему 18 входу предустановки, второй 5 токовый выход первого 1 логического элемента прямого циклического сдвига соединен с первым 19 токовым выходом состояния устройства, второй 10 токовый выход второго 6 логического элемента прямого циклического сдвига подключен ко второму 20 токовому выходу состояния устройства, второй 15 токовый выход третьего 11 логического элемента прямого циклического сдвига соединен с третьим 21 токовым выходом состояния устройства, первый 14 токовый выход третьего 11 логического элемента прямого циклического сдвига связан с первым 2 токовым входом первого 1 логического элемента прямого циклического сдвига, предусмотрены новые элементы и связи - в схему добавлен блок входных сигналов и синхронизации 22, содержащий токовый вход данных 23, токовый вход синхронизации 24, а также первый 25, второй 26 и третий 27 токовые выходы, первый 25 токовый выход блока входных сигналов и синхронизации 22 соединен с первым 16 входом предустановки, второй 26 токовый выход блока входных сигналов и синхронизации 22 соединен со вторым 17 входом предустановки, третий 27 токовый выход блока входных сигналов и синхронизации 22 соединен с третьим 18 входом предустановки.

На чертеже фиг. 1 показана схема прототипа, а на чертеже фиг. 2 - схема заявляемого токового порогового троичного D-триггера в соответствии с п. 1 формулы изобретения.

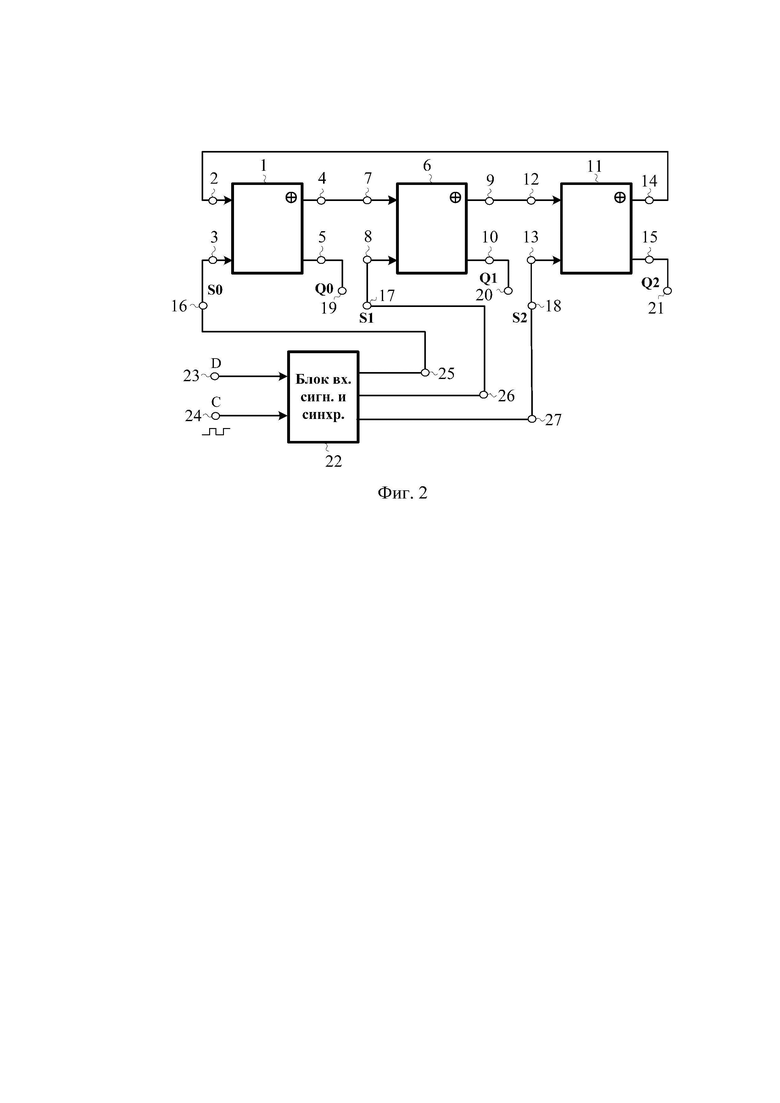

На чертеже фиг. 3 представлена реализация блока входных сигналов и синхронизации 22 на полевых транзисторах в соответствии с п. 2 формулы изобретения.

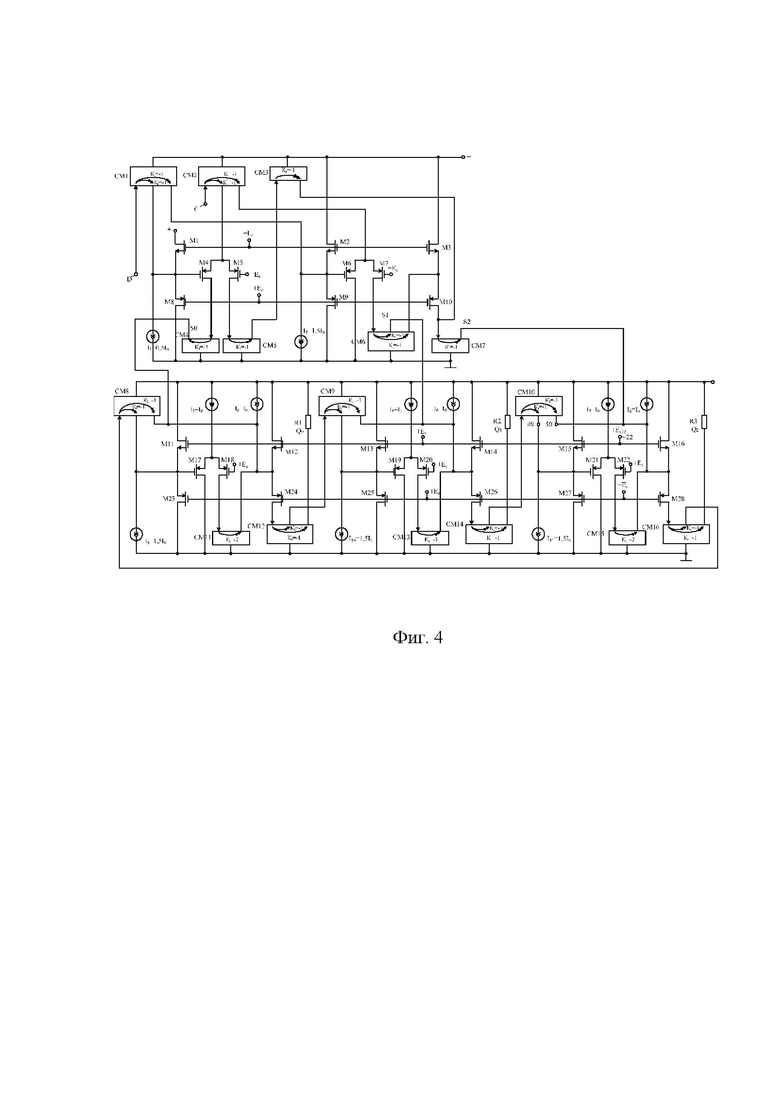

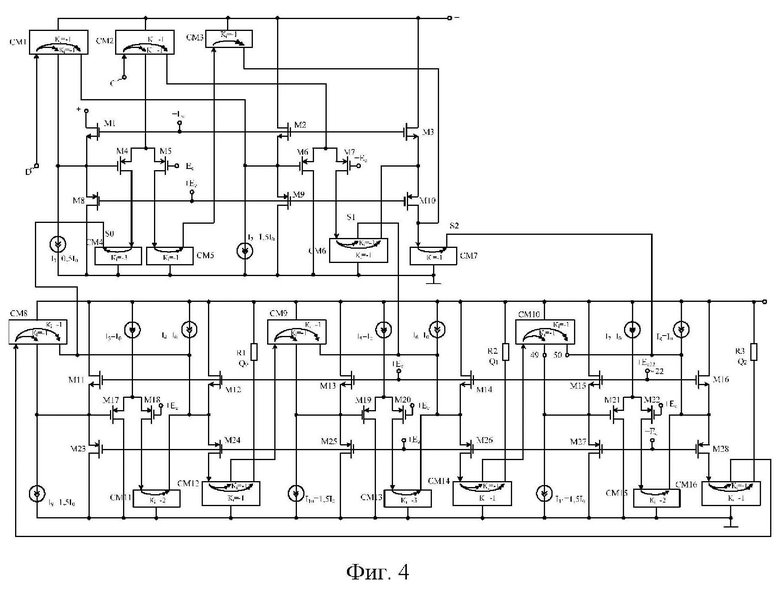

На чертеже фиг. 4 представлена принципиальная схема токового порогового троичного D-триггера фиг. 2 на полевых транзисторах.

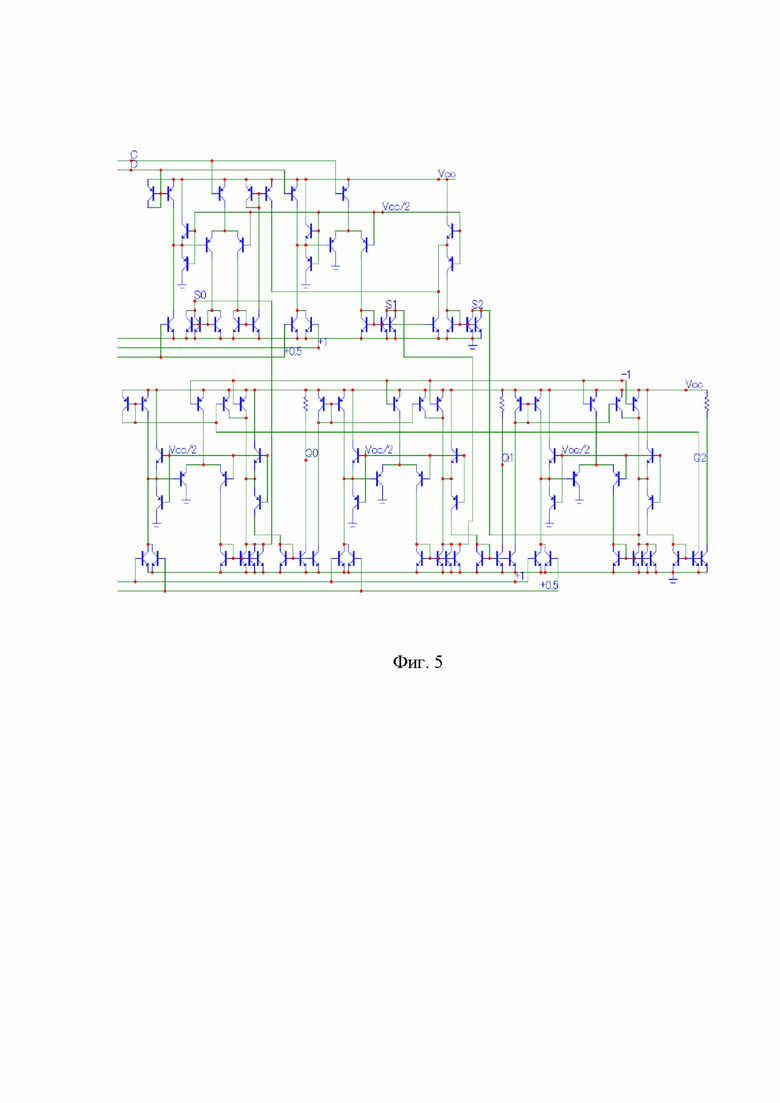

На чертеже фиг. 5 представлена схема токового порогового троичного D-триггера фиг. 4 в среде компьютерного моделирования Micro-Cap на моделях биполярных транзисторов.

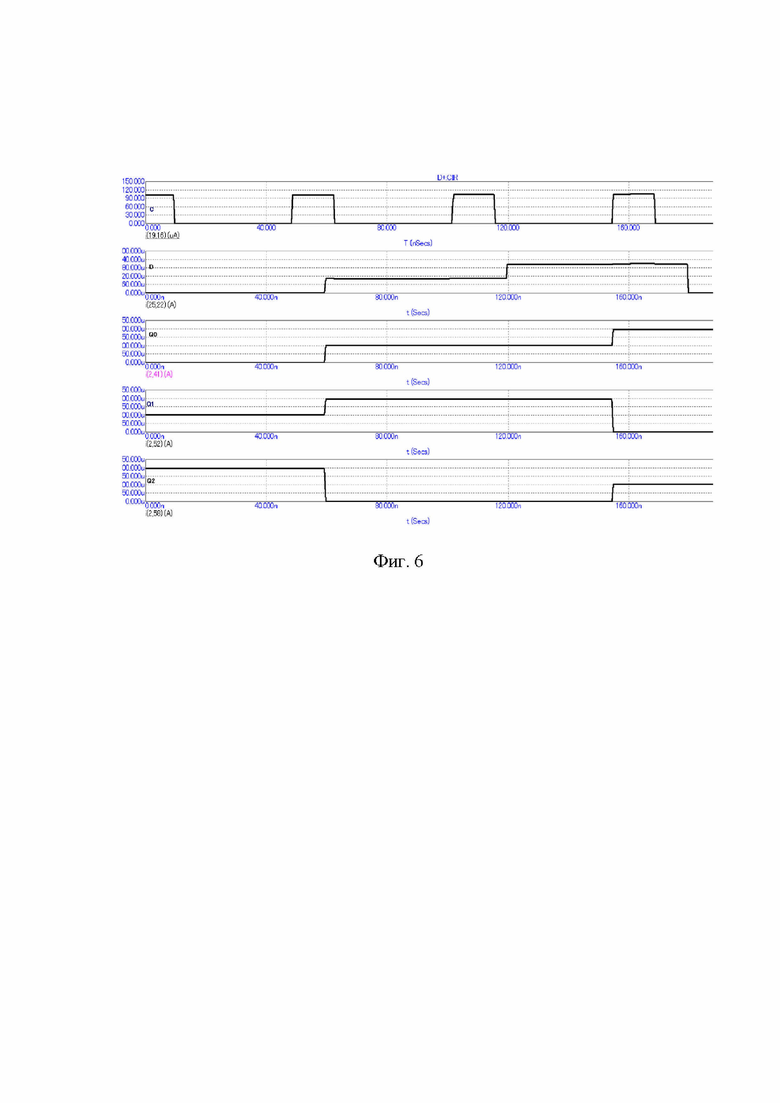

На чертеже фиг. 6 приведены осциллограммы входных и выходных сигналов схемы D-триггера фиг. 5.

Токовый пороговый троичный D-триггер (фиг. 2) содержит первый 1 логический элемент прямого циклического сдвига с первым 2 и вторым 3 токовыми входами, а также первым 4 и вторым 5 токовыми выходами, второй 6 логический элемент прямого циклического сдвига с первым 7 и вторым 8 токовыми входами, а также первым 9 и вторым 10 токовыми выходами, третий 11 логический элемент прямого циклического сдвига с первым 12 и вторым 13 токовыми входами, а также первым 14 и вторым 15 токовыми выходами, причем первый 7 токовый вход второго 6 логического элемента прямого циклического сдвига соединен с первым 4 токовым выходом первого 1 логического элемента прямого циклического сдвига, первый 12 токовый вход третьего 11 логического элемента прямого циклического сдвига соединен с первым 9 токовым выходом второго 6 логического элемента прямого циклического сдвига, второй 3 токовый вход первого 1 логического элемента прямого циклического сдвига соединен с первым 16 входом предустановки, второй 8 вход второго 6 логического элемента прямого циклического сдвига связан со вторым 17 входом предустановки, второй 13 вход третьего 11 логического элемента прямого циклического сдвига подключен к третьему 18 входу предустановки, второй 5 токовый выход первого 1 логического элемента прямого циклического сдвига соединен с первым 19 токовым выходом состояния устройства, второй 10 токовый выход второго 6 логического элемента прямого циклического сдвига подключен ко второму 20 токовому выходу состояния устройства, второй 15 токовый выход третьего 11 логического элемента прямого циклического сдвига соединен с третьим 21 токовым выходом состояния устройства, первый 14 токовый выход третьего 11 логического элемента прямого циклического сдвига связан с первым 2 токовым входом первого 1 логического элемента прямого циклического сдвига. В схему добавлен блок входных сигналов и синхронизации 22, содержащий токовый вход данных 23, токовый вход синхронизации 24, а также первый 25, второй 26 и третий 27 токовые выходы, первый 25 токовый выход блока входных сигналов и синхронизации 22 соединен с первым 16 входом предустановки, второй 26 токовый выход блока входных сигналов и синхронизации 22 соединен со вторым 17 входом предустановки, третий 27 токовый выход блока входных сигналов и синхронизации 22 соединен с третьим 18 входом предустановки.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, блок входных сигналов и синхронизации 22 содержит первый 28, второй 29 и третий 30 входные транзисторы с объединенными затворами, которые подключены к первому 31 источнику напряжения смещения, четвертый 32, пятый 33 и шестой 34 входные транзисторы другого типа проводимости с объединенными затворами, которые подключены ко второму 35 источнику напряжения смещения, седьмой 36, восьмой 37, девятый 38 и десятый 39 входные транзисторы, первое 40 токовое зеркало, согласованное с первой 41 шиной источников питания и содержащее первый 42 и второй 43 выходы, вход которого является токовым входом данных 23 блока входных сигналов и синхронизации 22, второе 44 токовое зеркало, согласованное с первой 41 шиной источников питания и содержащее первый 45 и второй 46 выходы, вход которого является токовым входом синхронизации 24 блока входных сигналов и синхронизации 22, третье 47 токовое зеркало, согласованное с первой 41 шиной источников питания, четвертое 48 токовое зеркало, согласованное со второй 49 шиной источников питания, выход которого является первым 25 токовым выходом блока входных сигналов и синхронизации 22, пятое 50 токовое зеркало, согласованное со второй 49 шиной источников питания, шестое 51 токовое зеркало, согласованное со второй 49 шиной источников питания и содержащее первый 52 и второй 53 выходы, седьмое 54 токовое зеркало, согласованное со второй 49 шиной источников питания, выход которого является третьим 27 токовым выходом блока входных сигналов и синхронизации 22, первый 55 и второй 56 источники опорного тока, первый 57 и второй 58 источники напряжения смещения, затвор седьмого 36 входного транзистора подключен к объединенным истокам первого 28 и четвертого 32 входных транзисторов, затвор девятого 38 входного транзистора подключен к объединенным истокам второго 29 и пятого 33 входных транзисторов, стоки первого 28, второго 29 и третьего 30 входных транзисторов соединены с первой 41 шиной источников питания, стоки четвертого 32, пятого 33 и девятого 38 входных транзисторов соединены со второй 49 шиной источников питания, истоки третьего 30 и шестого 34 входных транзисторов объединены и подключены ко второму 53 выходу шестого 51 токового зеркала, первый 52 выход шестого 51 токового зеркала является вторым 26 токовым выходом блока входных сигналов и синхронизации 22, первый 42 выход первого 40 токового зеркала подключен к затвору седьмого 36 входного транзистора и связан со второй 49 шиной источников питания через первый 55 источник опорного тока, второй 43 выход первого 40 токового зеркала подключен к затвору девятого 38 входного транзистора и связан со второй 49 шиной источников питания через второй 56 источник опорного тока, первый 45 выход второго 44 токового зеркала подключен к объединенным истокам седьмого 36 и восьмого 37 входных транзисторов, второй 46 выход второго 44 токового зеркала подключен к объединенным истокам девятого 38 и десятого 39 входных транзисторов, вход четвертого 48 токового зеркала соединен со стоком седьмого 36 входного транзистора, вход пятого 50 токового зеркала подключен ко стоку восьмого 37 входного транзистора, выход пятого 50 токового зеркала соединен со входом третьего 47 токового зеркала, выход третьего 47 токового зеркала подключен ко входу седьмого 54 токового зеркала и стоку шестого 34 входного транзистора, сток десятого 39 входного транзистора соединен со входом шестого 51 токового зеркала, затвор восьмого 37 входного транзистора подключен к первому 57 источнику напряжения смещения, затвор десятого 39 входного транзистора соединен со вторым 58 источником напряжения смещения.

Рассмотрим работу предлагаемой схемы D-триггера фиг. 2.

D-триггер реализуется на элементах прямого циклического сдвига, сигналы установки S0, S1, S2 формировать блоком входных сигналов и синхронизации 22 (фиг. 2) так, чтобы в режиме записи при сигнале синхронизации C=1, сигнал Q0=D, а Q1=D⊕1 и Q2=D⊕2. При С=0 триггер переходит в режим хранения.

Три логических элемента прямого циклического сдвига (нижняя часть схемы на фиг. 4) реализуют функцию  и образуют логическое кольцо элемента памятию. Сигналы установки в режиме хранения Si=0, для переключения триггера по сигналам управления соответствующий Si принимает значение 2 и вычитается из

и образуют логическое кольцо элемента памятию. Сигналы установки в режиме хранения Si=0, для переключения триггера по сигналам управления соответствующий Si принимает значение 2 и вычитается из , принудительно определяя на этом выходе значение 0. Верхняя часть схемы (фиг.3) преобразует сигналы C и D в сигналы установки по формулам:

, принудительно определяя на этом выходе значение 0. Верхняя часть схемы (фиг.3) преобразует сигналы C и D в сигналы установки по формулам:

S0=2(D<0,5)*sign(C), S1=2(D>1,5) *sign(C), S2=2((D<0,5)– (D>1,5))*sign(C).

Т.е. в режиме хранения при C=0 все сигналы установки равны 0 независимо от сигнала D, а в режиме ввода значения D при С=1 один из сигналов установки, соответствующий значению D, становится равным 2. Управление по входу синхронизации при С=0 производится отключение опорных токов ДК.

Показанные на фиг. 6 результаты моделирования подтверждают указанные свойства заявляемой схемы.

Таким образом, рассмотренное схемотехническое решение токового порогового троичного триггера характеризуется многозначным состоянием внутренних сигналов и сигналов на его токовых входах и выходах, что может быть положено в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.742.154, 1998 г.

2. Патентная заявка US 2007/0018694, 2007 г.

3. Патент US 6.414.519, 2002 г.

4. Патент US 6.566.912, 2003 г.

5. Патент US 6.700.413, 2004 г.

6. Патентная заявка US 2004/0263210, 2004 г.

7. Патент US 6.680.625, 2004 г.

8. Патент SU 1621164, 1991 г.

9. Патент US 6.573.758, 2003 г.

10. Патент US 5.155.387, 1992 г.

11. Патент US 4.713.790, 1987 г.

12. Патент US 5.608.741, 1997 г.

13. Патент US 4.185.210, fig.2, 1980 г.

14. Патент RU 2692573, 2019 г.

15. Патент RU 2725149, 2020 г.

16. Патент RU 2624581, 2017 г.

17. Jing Shen, K. Tanno, O. Ishizuka and Zheng Tang, "Application of neuron-MOS to current-mode multi-valued logic circuits, "Proceedings. 1998 28th IEEE International Symposium on Multiple- Valued Logic (Cat. No.98CB36138), 1998, pp.128-133, doi: 10.1109/ISMVL.1998.679320.

18. P. S. Budyakov, "Current Logic Based Serial to Parallel Converter, "2018 26th Telecommunications Forum (TELFOR), 2018, pp.1-4, doi: 10.1109/TELFOR.2018.8612153.

19. C. Vinod Vijayan, T. Ayoob Khan and S. Hammed, "High Speed Current Mode Threshold Logic Gates," 2018 International Conference on Emerging Trends and Innovations In Engineering And Technological Research (ICETIETR), 2018, pp.1-4, doi: 10.1109/ICETIETR.2018.8529074.

20. S. C. Mane, S. P. Hajare and P. Dakhole, "Current mode quaternary logic circuit," 2017 International Conference on Communication and Signal Processing (ICCSP), 2017, pp.0825-0829, doi: 10.1109/ICCSP.2017.8286481.

21. N.N. Prokopenko, N.I. Chernov, V.Ya. Yugai, N.V. Butyrlagin.”The Element Base of the Multivalued Threshold Logic for the Automation and Control Digital Devices,” on International Siberian Conference on Control and Communications, SIBCON-2017, Astana, Kazakhstan, 29-30 June, 2017.

22. N. I. Chernov, N. N. Prokopenko, V. Yugai and N. V. Butyrlagin, "Threshold synthesis of digital structures in current-mode logic," 2017 IEEE East-West Design & Test Symposium (EWDTS), 2017, pp.1-4, doi: 10.1109/EWDTS.2017.8110146.

23. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001. - 147 с.

23. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог. - ТРТУ, 2004 г., 118 с.

25. Чернов Н.И., Прокопенко Н. Н., Бутырлагин Н.В., Югай В.Я. Двузначные и многозначные токовые логические элементы и вычислительные модули: монография. - М.: СОЛОН-Пресс, 2022. - 268 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ТРИГГЕР | 2021 |

|

RU2777029C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ПРЯМОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693639C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ЛЕВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2021 |

|

RU2776031C1 |

| МНОГОЗНАЧНЫЙ ТРИГГЕР | 2016 |

|

RU2624581C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ОБРАТНОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693590C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ | 2020 |

|

RU2729887C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ПРАВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2020 |

|

RU2725149C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ "МИНИМУМ" | 2020 |

|

RU2727145C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ПАРАЛЛЕЛЬНЫЙ ТРОИЧНЫЙ КОМПАРАТОР | 2020 |

|

RU2723672C1 |

| МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ОБРАТНОГО ЦИКЛИЧЕСКОГО СДВИГА | 2014 |

|

RU2553071C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в быстродействующих аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков. Технический результат заключается в повышении быстродействия за счет осуществления преобразования информации в токовой форме сигналов. Токовый пороговый троичный D-триггер содержит первый (1) логический элемент прямого циклического сдвига с первым (2) и вторым (3) токовыми входами, а также первым (4) и вторым (5) токовыми выходами, второй (6) логический элемент прямого циклического сдвига с первым (7) и вторым (8) токовыми входами, а также первым (9) и вторым (10) токовыми выходами, третий (11) логический элемент прямого циклического сдвига с первым (12) и вторым (13) токовыми входами, а также первым (14) и вторым (15) токовыми выходами, блок входных сигналов и синхронизации (22), содержащий токовый вход данных (23), токовый вход синхронизации (24), а также первый (25), второй (26) и третий (27) токовые выходы, первый (25) токовый выход блока входных сигналов и синхронизации (22) соединен с первым (16) входом предустановки первого (1) логического элемента, второй (26) токовый выход блока входных сигналов и синхронизации (22) соединен со вторым (17) входом предустановки второго (6) логического элемента, третий (27) токовый выход блока входных сигналов и синхронизации (22) соединен с третьим (18) входом предустановки третьего (11) логического элемента. 1 з.п. ф-лы, 6 ил.

1. Токовый пороговый троичный D-триггер, содержащий первый (1) логический элемент прямого циклического сдвига с первым (2) и вторым (3) токовыми входами, а также первым (4) и вторым (5) токовыми выходами, второй (6) логический элемент прямого циклического сдвига с первым (7) и вторым (8) токовыми входами, а также первым (9) и вторым (10) токовыми выходами, третий (11) логический элемент прямого циклического сдвига с первым (12) и вторым (13) токовыми входами, а также первым (14) и вторым (15) токовыми выходами, причем первый (7) токовый вход второго (6) логического элемента прямого циклического сдвига соединён с первым (4) токовым выходом первого (1) логического элемента прямого циклического сдвига, первый (12) токовый вход третьего (11) логического элемента прямого циклического сдвига соединён с первым (9) токовым выходом второго (6) логического элемента прямого циклического сдвига, второй (3) токовый вход первого (1) логического элемента прямого циклического сдвига соединен с первым (16) входом предустановки, второй (8) вход второго (6) логического элемента прямого циклического сдвига связан со вторым (17) входом предустановки, второй (13) вход третьего (11) логического элемента прямого циклического сдвига подключен к третьему (18) входу предустановки, второй (5) токовый выход первого (1) логического элемента прямого циклического сдвига соединён с первым (19) токовым выходом состояния устройства, второй (10) токовый выход второго (6) логического элемента прямого циклического сдвига подключен ко второму (20) токовому выходу состояния устройства, второй (15) токовый выход третьего (11) логического элемента прямого циклического сдвига соединён с третьим (21) токовым выходом состояния устройства, первый (14) токовый выход третьего (11) логического элемента прямого циклического сдвига связан с первым (2) токовым входом первого (1) логического элемента прямого циклического сдвига, отличающийся тем, что в схему добавлен блок входных сигналов и синхронизации (22), содержащий токовый вход данных (23), токовый вход синхронизации (24), а также первый (25), второй (26) и третий (27) токовые выходы, первый (25) токовый выход блока входных сигналов и синхронизации (22) соединён с первым (16) входом предустановки, второй (26) токовый выход блока входных сигналов и синхронизации (22) соединён со вторым (17) входом предустановки, третий (27) токовый выход блока входных сигналов и синхронизации (22) соединён с третьим (18) входом предустановки.

2. Токовый пороговый D-триггер по п. 1, отличающийся тем, что блок входных сигналов и синхронизации (22) содержит первый (28), второй (29) и третий (30) входные транзисторы с объединенными затворами, которые подключены к первому (31) источнику напряжения смещения, четвертый (32), пятый (33) и шестой (34) входные транзисторы другого типа проводимости с объединенными затворами, которые подключены ко второму (35) источнику напряжения смещения, седьмой (36), восьмой (37), девятый (38) и десятый (39) входные транзисторы, первое (40) токовое зеркало, согласованное с первой (41) шиной источников питания и содержащее первый (42) и второй (43) выходы, вход которого является токовым входом данных (23) блока входных сигналов и синхронизации (22), второе (44) токовое зеркало, согласованное с первой (41) шиной источников питания и содержащее первый (45) и второй (46) выходы, вход которого является токовым входом синхронизации (24) блока входных сигналов и синхронизации (22), третье (47) токовое зеркало, согласованное с первой (41) шиной источников питания, четвертое (48) токовое зеркало, согласованное со второй (49) шиной источников питания, выход которого является первым (25) токовым выходом блока входных сигналов и синхронизации (22), пятое (50) токовое зеркало, согласованное со второй (49) шиной источников питания, шестое (51) токовое зеркало, согласованное со второй (49) шиной источников питания и содержащее первый (52) и второй (53) выходы, седьмое (54) токовое зеркало, согласованное со второй (49) шиной источников питания, выход которого является третьим (27) токовым выходом блока входных сигналов и синхронизации (22), первый (55) и второй (56) источники опорного тока, первый (57) и второй (58) источники напряжения смещения, затвор седьмого (36) входного транзистора подключен к объединённым истокам первого (28) и четвертого (32) входных транзисторов, затвор девятого (38) входного транзистора подключен к объединённым истокам второго (29) и пятого (33) входных транзисторов, стоки первого (28), второго (29) и третьего (30) входных транзисторов соединены с первой (41) шиной источников питания, стоки четвертого (32), пятого (33) и девятого (38) входных транзисторов соединены со второй (49) шиной источников питания, истоки третьего (30) и шестого (34) входных транзисторов объединены и подключены ко второму (53) выходу шестого (51) токового зеркала, первый (52) выход шестого (51) токового зеркала является вторым (26) токовым выходом блока входных сигналов и синхронизации (22), первый (42) выход первого (40) токового зеркала подключен к затвору седьмого (36) входного транзистора и связан со второй (49) шиной источников питания через первый (55) источник опорного тока, второй (43) выход первого (40) токового зеркала подключен к затвору девятого (38) входного транзистора и связан со второй (49) шиной источников питания через второй (56) источник опорного тока, первый (45) выход второго (44) токового зеркала подключен к объединённым истокам седьмого (36) и восьмого (37) входных транзисторов, второй (46) выход второго (44) токового зеркала подключен к объединённым истокам девятого (38) и десятого (39) входных транзисторов, вход четвертого (48) токового зеркала соединён со стоком седьмого (36) входного транзистора, вход пятого (50) токового зеркала подключен к стоку восьмого (37) входного транзистора, выход пятого (50) токового зеркала соединён с входом третьего (47) токового зеркала, выход третьего (47) токового зеркала подключен к входу седьмого (54) токового зеркала и стоку шестого (34) входного транзистора, сток десятого (39) входного транзистора соединён с входом шестого (51) токового зеркала, затвор восьмого (37) входного транзистора подключен к первому (57) источнику напряжения смещения, затвор десятого (39) входного транзистора соединён со вторым (58) источником напряжения смещения.

| МНОГОЗНАЧНЫЙ ТРИГГЕР | 2016 |

|

RU2624581C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ПРАВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2020 |

|

RU2725149C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕРАВНОЗНАЧНОСТЬ" | 2018 |

|

RU2692573C1 |

| US 4185210 A1, 22.01.1980 | |||

| US 6573758 B2, 03.06.2003 | |||

| US 5155387 A1, 13.10.1992. | |||

Авторы

Даты

2022-11-24—Публикация

2022-07-17—Подача