Предлагаемое изобретение относится к области вычислительной техники, автоматики, связи и может использоваться в различных цифровых структурах и системах автоматического управления, передачи цифровой информации и т.п.

В различных вычислительных и управляющих системах широко используются компараторы, реализованные на основе эмиттерно-связанной логики [1-14], работающие по законам булевой алгебры и имеющие по выходу два логических состояния «0» и «1», характеризующихся низким и высоким потенциалами. В настоящее время двоичная элементная база практически достигла предельных функциональных возможностей, одним из перспективных путей дальнейшего повышения эффективности цифровых устройств является переход от двоичных булевых функций к многозначным логическим функциям и реализация соответствующей многозначной элементной базы.

В патенте [15], работах [16-17] и монографиях [18-19] показано, что булева алгебра является частным случаем более общей линейной алгебры, практическая реализация которой в структуре вычислительных и логических устройств автоматики нового поколения требует создания специальной элементной базы, реализуемой на основе логики с многозначным внутренним представлением сигналов, в которой эквивалентом стандартного логического сигнала является квант тока I0. Заявляемое устройство «Токовый пороговый троичный элемент» относится к этому типу логических элементов. Логическая функция «максимум» для k-значных переменных является естественным обобщением логической функции дизъюнкция, определяемой только для булевых двоичных переменных, т.е. логический элемент максимум является обобщением элемента ИЛИ для переменных со значностью более 2.

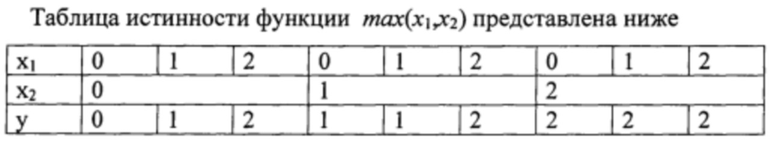

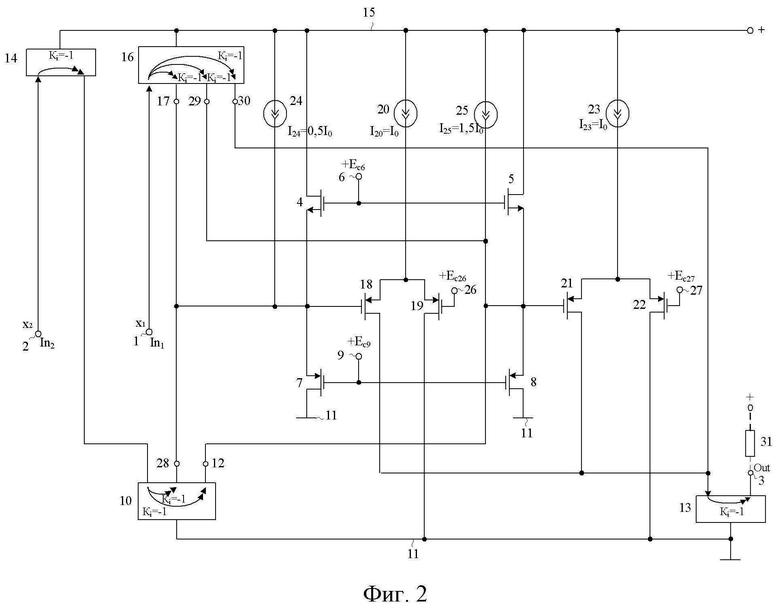

Ближайшим прототипом заявляемого устройства является логический элемент, представленный в патенте RU 2701108 («Токовый пороговый логический элемент «Неравнозначность»», МПК H03K 19/21, H03K 19/212, H03K 19/215, G03F 3/26, 2019 г.). Он содержит (фиг.1) первый 1 и второй 2 входы устройства, выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы с объединенными затворами, которые подключены к первому 6 источнику напряжения смещения, третий 7 и четвертый 8 входные полевые транзисторы другого типа проводимости с объединенными затворами, которые подключены ко второму 9 источнику напряжения смещения, истоки первого 4 и третьего 7 входных полевых транзисторов соединены друг с другом, истоки второго 5 и четвертого 8 входных полевых транзисторов подключены друг к другу, первое 10 токовое зеркало, согласованное с первой 11 шиной источника питания, содержащее выход 12, второе 13 токовое зеркало, согласованное с первой 11 шиной источника питания, выход которого подключен к выходу 3 устройства, третье 14 токовое зеркало, согласованное со второй 15 шиной источника питания, вход которого подключен ко второму 2 входу устройства, стоки первого 4 и второго 5 входных полевых транзисторов соединены со второй 15 шиной источника питания, четвертое 16 токовое зеркало, согласованное со второй 15 шиной источника питания, имеющее выход 17, пятый 18 и шестой 19 входные полевые транзисторы, истоки которых объединены и связаны со второй 15 шиной источника питания через первый 20 источник опорного тока, затвор пятого 18 входного полевого транзистора подключен к объединенным истокам первого 4 и третьего 7 входных полевых транзисторов и выходу 17 четвертого 16 токового зеркала, седьмой 21 и восьмой 22 входные полевые транзисторы, истоки которых объединены и связаны со второй 15 шиной источника питания через второй 23 источник опорного тока, затвор седьмого 21 входного полевого транзистора подключен к объединенным истокам второго 5 и четвертого 8 входных полевых транзисторов, а также к выходу 12 первого 10 токового зеркала, сток седьмого 21 входного полевого транзистора подключен ко входу второго 13 токового зеркала, стоки третьего 7, четвертого 8 и восьмого 22 входных полевых транзисторов подключены к первой 11 шине источника питания, третий 24 источник опорного тока, четвертый 25 источник опорного тока, включенный между второй 15 шиной источника тока и выходом 12 первого 10 токового зеркала, третий 26 источник напряжения смещения подключен к затвору шестого 19 входного полевого транзистора, четвертый 27 источник напряжения смещения подключен к затвору восьмого 22 входного полевого транзистора.

Существенный недостаток известного логического элемента состоит в том, что он реализует двоичную булеву функцию и не предоставляет возможность работы с многозначными входными и выходными токовыми сигналами, что в конечном итоге приводит к сокращению функциональных возможностей и снижению его быстродействия. Это не позволяет создать функционально полный базис средств цифровой техники, функционирующих на принципах преобразования многозначных токовых сигналов. Применение многозначных пороговых функций и соответствующих им пороговых элементов, кроме реализации заданной логической функции, обеспечивает масштабирование и нормализацию уровней выходных сигналов и тем самым устраняет все погрешности сигналов, возникающие до порогового элемента.

Основная задача предлагаемого изобретения состоит в создании токового порогового троичного элемента, в котором внутреннее преобразование информации производится в токовой форме сигналов. В конечном итоге это позволяет повысить быстродействие и создать элементную базу цифровых устройств, работающих на принципах многозначной линейной алгебры [18-19].

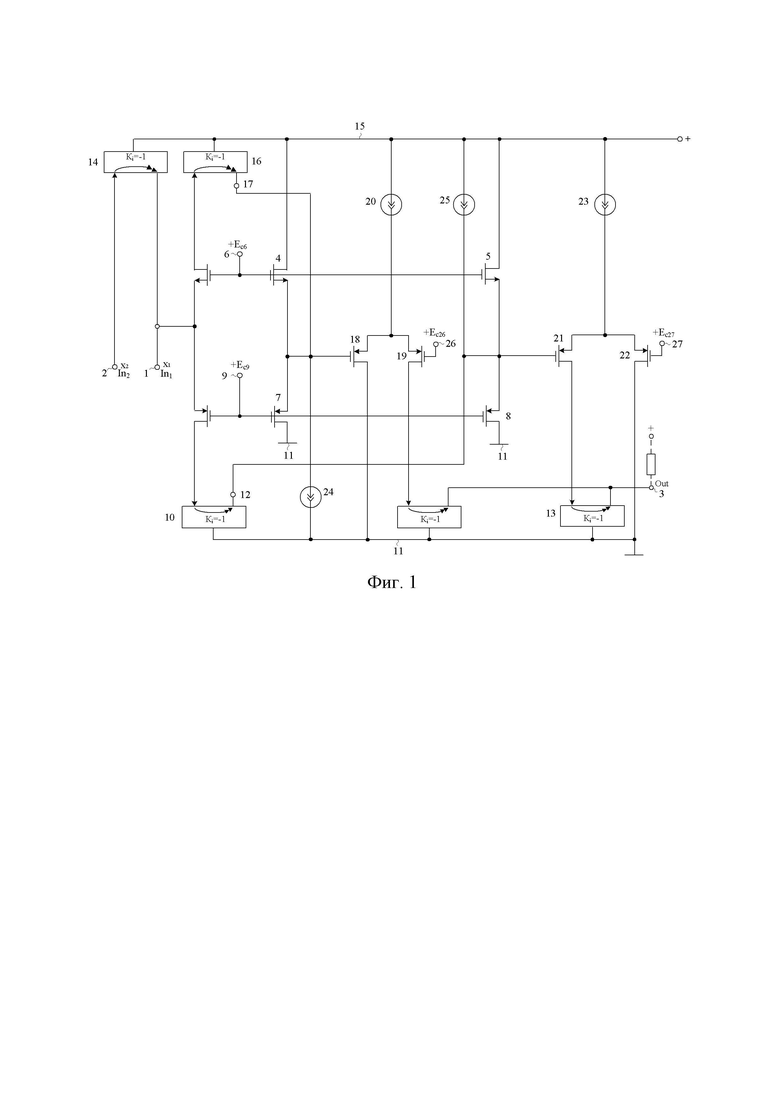

Поставленная задача решается тем, что в логическом элементе (фиг. 1), содержащем первый 1 и второй 2 входы устройства, выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы с объединенными затворами, которые подключены к первому 6 источнику напряжения смещения, третий 7 и четвертый 8 входные полевые транзисторы другого типа проводимости с объединенными затворами, которые подключены ко второму 9 источнику напряжения смещения, истоки первого 4 и третьего 7 входных полевых транзисторов соединены друг с другом, истоки второго 5 и четвертого 8 входных полевых транзисторов подключены друг к другу, первое 10 токовое зеркало, согласованное с первой 11 шиной источника питания, содержащее выход 12, второе 13 токовое зеркало, согласованное с первой 11 шиной источника питания, выход которого подключен к выходу 3 устройства, третье 14 токовое зеркало, согласованное со второй 15 шиной источника питания, вход которого подключен ко второму 2 входу устройства, стоки первого 4 и второго 5 входных полевых транзисторов соединены со второй 15 шиной источника питания, четвертое 16 токовое зеркало, согласованное со второй 15 шиной источника питания, имеющее выход 17, пятый 18 и шестой 19 входные полевые транзисторы, истоки которых объединены и связаны со второй 15 шиной источника питания через первый 20 источник опорного тока, затвор пятого 18 входного полевого транзистора подключен к объединенным истокам первого 4 и третьего 7 входных полевых транзисторов и выходу 17 четвертого 16 токового зеркала, седьмой 21 и восьмой 22 входные полевые транзисторы, истоки которых объединены и связаны со второй 15 шиной источника питания через второй 23 источник опорного тока, затвор седьмого 21 входного полевого транзистора подключен к объединенным истокам второго 5 и четвертого 8 входных полевых транзисторов, а также к выходу 12 первого 10 токового зеркала, сток седьмого 21 входного полевого транзистора подключен ко входу второго 13 токового зеркала, стоки третьего 7, четвертого 8 и восьмого 22 входных полевых транзисторов подключены к первой 11 шине источника питания, третий 24 источник опорного тока, четвертый 25 источник опорного тока, включенный между второй 15 шиной источника тока и выходом 12 первого 10 токового зеркала, третий 26 источник напряжения смещения подключен к затвору шестого 19 входного полевого транзистора, четвертый 27 источник напряжения смещения подключен к затвору восьмого 22 входного полевого транзистора, предусмотрены новые элементы и связи - первое 10 токовое зеркало снабжено дополнительным выходом 28, четвертое 16 токовое зеркало содержит первый 29 и второй 30 дополнительные выходы, выход третьего 14 токового зеркала подключен ко входу первого 10 токового зеркала, первый 1 вход устройства соединен со входом четвертого 16 токового зеркала, дополнительный 28 выход первого 10 токового зеркала подключен к выходу 17 четвертого 16 токового зеркала и связан со второй 15 шиной источника питания через третий 24 источник опорного тока, первый 29 дополнительный выход четвертого 16 токового зеркала соединен с затвором седьмого 21 входного полевого транзистора, второй 30 дополнительный выход четвертого 16 токового зеркала подключен ко входу второго 13 токового зеркала и соединен со стоком пятого 18 входного полевого транзистора, сток шестого 19 входного полевого транзистора согласован с первой 11 шиной источника питания.

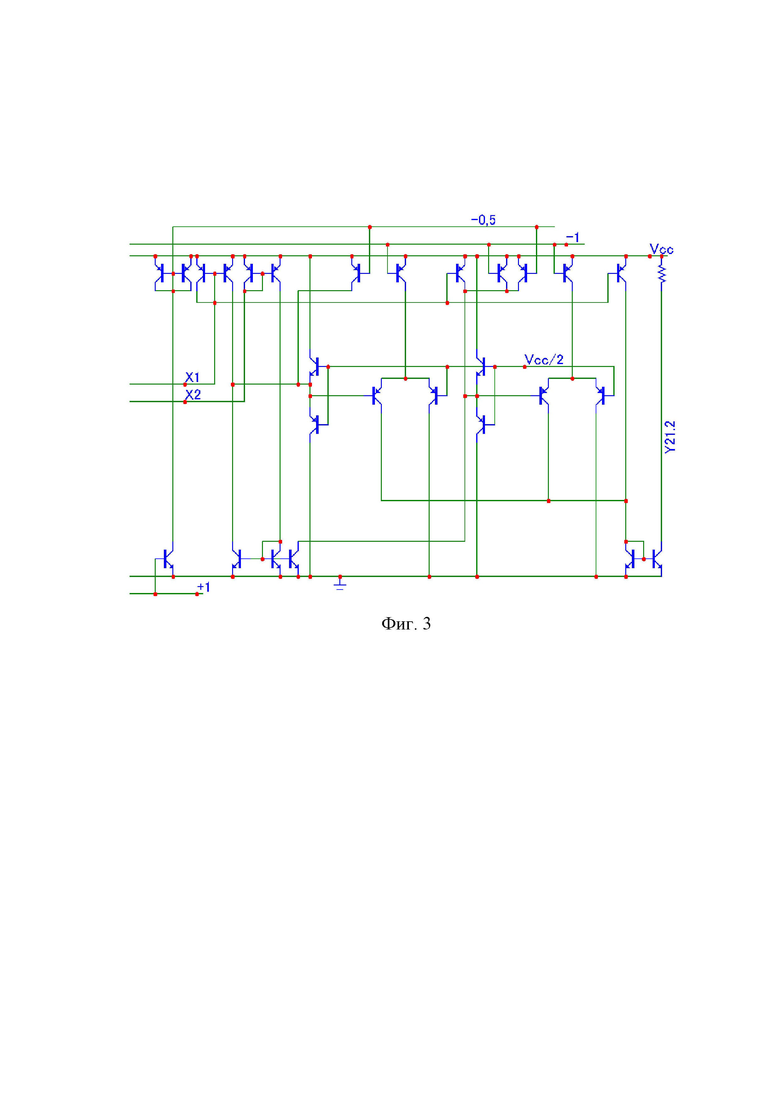

На чертеже фиг. 1 показана схема прототипа, а на чертеже фиг. 2 - схема заявляемого токового порогового троичного элемента на полевых транзисторах в соответствии с п. 1 формулы изобретения.

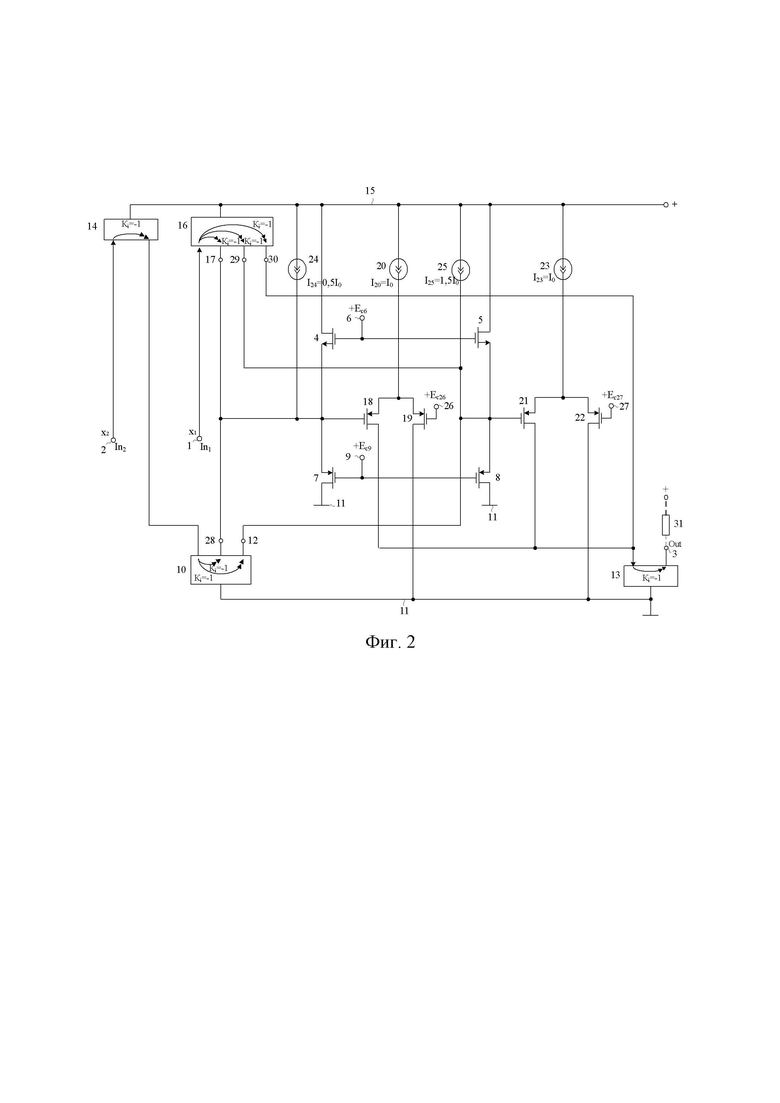

На чертеже фиг. 3 представлена схема токового порогового троичного элемента фиг. 2 в среде компьютерного моделирования Micro-Cap на моделях биполярных транзисторов.

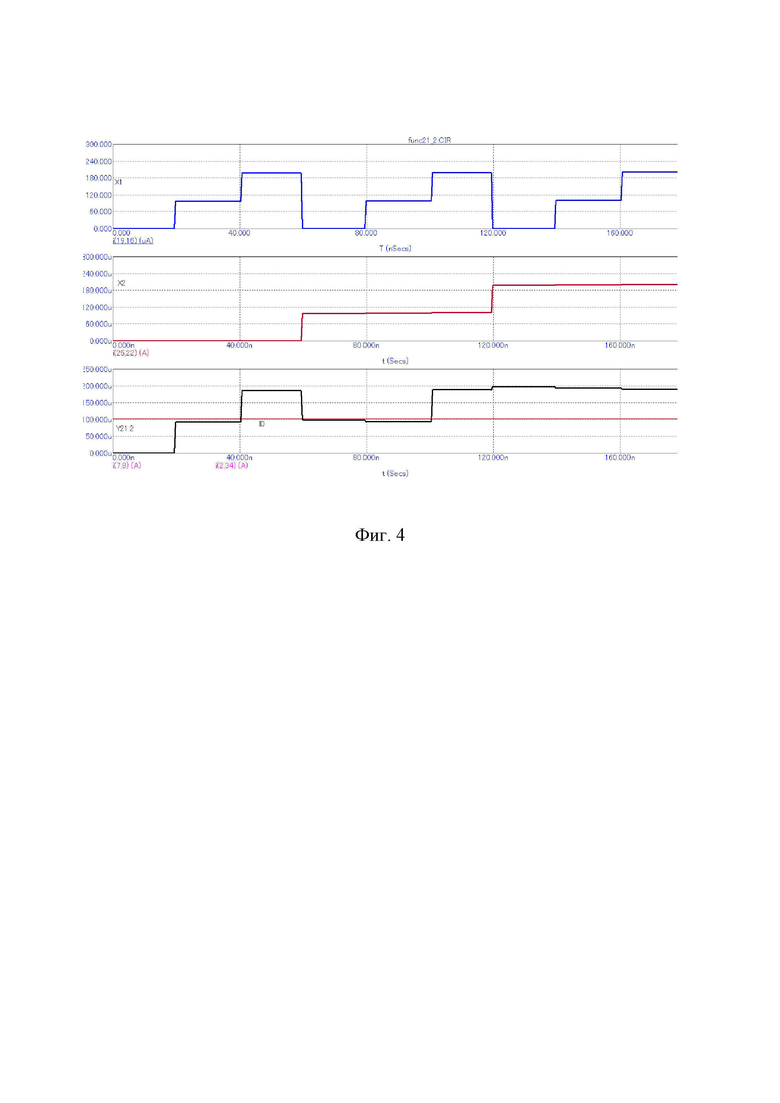

На чертеже фиг. 4 приведены осциллограммы входных и выходных сигналов элемента фиг. 3.

Токовый пороговый троичный элемент фиг. 2 содержит первый 1 и второй 2 входы устройства, выход 3 устройства, первый 4 и второй 5 входные полевые транзисторы с объединенными затворами, которые подключены к первому 6 источнику напряжения смещения, третий 7 и четвертый 8 входные полевые транзисторы другого типа проводимости с объединенными затворами, которые подключены ко второму 9 источнику напряжения смещения, истоки первого 4 и третьего 7 входных полевых транзисторов соединены друг с другом, истоки второго 5 и четвертого 8 входных полевых транзисторов подключены друг к другу, первое 10 токовое зеркало, согласованное с первой 11 шиной источника питания, содержащее выход 12, второе 13 токовое зеркало, согласованное с первой 11 шиной источника питания, выход которого подключен к выходу 3 устройства, третье 14 токовое зеркало, согласованное со второй 15 шиной источника питания, вход которого подключен ко второму 2 входу устройства, стоки первого 4 и второго 5 входных полевых транзисторов соединены со второй 15 шиной источника питания, четвертое 16 токовое зеркало, согласованное со второй 15 шиной источника питания, имеющее выход 17, пятый 18 и шестой 19 входные полевые транзисторы, истоки которых объединены и связаны со второй 15 шиной источника питания через первый 20 источник опорного тока, затвор пятого 18 входного полевого транзистора подключен к объединенным истокам первого 4 и третьего 7 входных полевых транзисторов и выходу 17 четвертого 16 токового зеркала, седьмой 21 и восьмой 22 входные полевые транзисторы, истоки которых объединены и связаны со второй 15 шиной источника питания через второй 23 источник опорного тока, затвор седьмого 21 входного полевого транзистора подключен к объединенным истокам второго 5 и четвертого 8 входных полевых транзисторов, а также к выходу 12 первого 10 токового зеркала, сток седьмого 21 входного полевого транзистора подключен ко входу второго 13 токового зеркала, стоки третьего 7, четвертого 8 и восьмого 22 входных полевых транзисторов подключены к первой 11 шине источника питания, третий 24 источник опорного тока, четвертый 25 источник опорного тока, включенный между второй 15 шиной источника тока и выходом 12 первого 10 токового зеркала, третий 26 источник напряжения смещения подключен к затвору шестого 19 входного полевого транзистора, четвертый 27 источник напряжения смещения подключен к затвору восьмого 22 входного полевого транзистора. Первое 10 токовое зеркало снабжено дополнительным выходом 28, четвертое 16 токовое зеркало содержит первый 29 и второй 30 дополнительные выходы, выход третьего 14 токового зеркала подключен ко входу первого 10 токового зеркала, первый 1 вход устройства соединен со входом четвертого 16 токового зеркала, дополнительный 28 выход первого 10 токового зеркала подключен к выходу 17 четвертого 16 токового зеркала и связан со второй 15 шиной источника питания через третий 24 источник опорного тока, первый 29 дополнительный выход четвертого 16 токового зеркала соединен с затвором седьмого 21 входного полевого транзистора, второй 30 дополнительный выход четвертого 16 токового зеркала подключен ко входу второго 13 токового зеркала и соединен со стоком пятого 18 входного полевого транзистора, сток шестого 19 входного полевого транзистора согласован с первой 11 шиной источника питания.

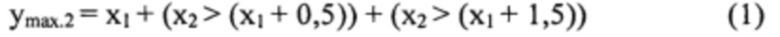

Рассмотрим работу предлагаемой схемы ЛЭ фиг. 2. Пороговая реализация троичной логической функции max(x1,x2) описывается следующим уравнением:

Входная переменная «x2» в виде сигнала втекающего тока поступает на второй 2 вход устройства и далее на выход третьего 14 токового зеркала. Выходной сигнал с выхода третьего 14 токового зеркала подается на вход первого 10 токового зеркала. Входная переменная «x1» в виде сигнала втекающего тока поступает на первый 1 вход устройства и далее на вход четвертого 16 токового зеркала. Выходной сигнал с выхода 17 четвертого 16 токового зеркала вычитается из сигнала дополнительного 28 выхода первого 10 токового зеркала, а также из конечного сигнала вычитается сигнал 0,5 кванта тока I0 третьего 24 источника опорного тока и далее поступает на объединенные истоки первого 4 и третьего 7 входных полевых транзисторов, а также подается на затвор пятого 18 входного полевого транзистора. Режимы работы первого 4 и третьего 7 входных транзисторов задаются значениями напряжений первого 6 и второго 9 источников напряжения смещения. Пятый 18 и шестой 19 входные полевые транзисторы образуют дифференциальный каскад (ДК), переключение токов стоков этих транзисторов определяется сигналом, поступающим на затвор пятого 18 входного полевого транзистора. ДК в данном случае выполняет функции порогового элемента, выполняя сравнение переменной x2-x1 с пороговым уровнем тока 0,5I0. Выбор такого порогового уровня обеспечивает независимость результатов преобразования сигналов от погрешностей преобразования в пределах диапазона изменения тока 0,5I0. При положительной разности сигналов (x2-x1)-0,5 ток первого 20 источника опорного тока через сток пятого 18 входного полевого транзистора в виде кванта тока подается на второе 13 токовое зеркало, реализуя первое слагаемое выражения (1). Выходной сигнал с выхода 12 первого 10 токового зеркала вычитается из сигнала порогового уровня тока 1,5I0 четвертого 25 источника опорного тока, сравнивается с выходным сигналом первого 29 дополнительного выхода четвертого 16 токового зеркала и далее поступает на объединенные истоки второго 5 и четвертого 8 входных полевых транзисторов, а также подается на затвор седьмого 21 входного полевого транзистора. Режимы работы второго 5 и четвертого 8 входных транзисторов задаются значениями напряжений первого 6 и второго 9 источников напряжения смещения. Седьмой 21 и восьмой 22 входные полевые транзисторы образуют ДК, переключение токов стоков этих транзисторов определяется сигналом, поступающим на затвор седьмого 21 входного полевого транзистора. ДК в данном случае выполняет функции порогового элемента, выполняя сравнение переменной x2-x1 с пороговым уровнем тока 1,5I0. Выбор такого порогового уровня обеспечивает независимость результатов преобразования сигналов от погрешностей преобразования в пределах диапазона изменения тока 0,5I0. При положительной разности сигналов (x2-x1)-1,5 ток второго 23 источника опорного тока через сток седьмого 21 входного полевого транзистора реализует второе слагаемое выражения (1) и в виде сигнала тока подается на вход второго 13 токового зеркала. Сигналы со стоков пятого 18 и седьмого 21 входных полевых транзисторов суммируются с сигналом второго 30 дополнительного выхода четвертого 16 токового зеркала и подаются на вход второго 13 токового зеркала, где преобразуются в равный им втекающий ток и передаются на выход 3 устройства.

В схеме на фиг. 3 двухполюсник 31 служит для обнаружения наличия кванта тока в выходной цепи в процессе экспериментальных исследований.

Показанные на фиг. 4 результаты моделирования подтверждают указанные свойства заявляемой схемы.

Таким образом, рассмотренное схемотехническое решение токового порогового троичного элемента является необходимым компонентом функционально полных базисов, характеризуется многозначным состоянием внутренних сигналов и сигналов на его токовых входах и выходах, что может быть положено в основу вычислительных и управляющих устройств, использующих многозначную линейную алгебру, частным случаем которой является булева алгебра.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.155.387, 1992 г.

2. Патентная заявка US 2007/0018694, 2007 г.

3. Патент US 6.566.912, 2003 г.

4. Патент US 6.414.519, 2002 г.

5. Патент US 6.700.413, 2004 г.

6. Патентная заявка US 2004/0263210, 2004 г.

7. Патент US 4.713.790, 1987 г.

8. Патент SU 1621164, 1991 г.

9. Патент US 6.573.758, 2003 г.

10. Патент US 5.742.154, 1998 г.

11. Патент US 6.680.625, 2004 г.

12. Патент US 5.608.741, 1997 г.

13. Патент US 4.185.210, fig. 2, 1980 г.

14. Патент US 3.040.192, fig. 1. 1962 г.

15. Патент RU 2701108, 2019 г.

16. Малюгин В. Д. Реализация булевых функций арифметическими полиномами // Автоматика и телемеханика, 1982. №4. С.84-93.

17. Butyrlagin N.V., Chernov N.I., Prokopenko N.N., Yugai V.Ya. Design of Two-Valued and Multivalued Current Digital Adders Based on the Mathematical Tool of Linear Algebra. 2018 IEEE East-West Design & Test Symposium (EWDTS). Kazan, 2018. pp. 384-389. DOI:10.1109/EWDTS.2018.8524855

18. Чернов Н.И. Основы теории логического синтеза цифровых структур над полем вещественных чисел // Монография. - Таганрог: ТРТУ, 2001.- 147 с.

19. Чернов Н.И. Линейный синтез цифровых структур АСОИУ» // Учебное пособие Таганрог.- ТРТУ, 2004 г., 118 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ЭЛЕМЕНТ "МИНИМУМ" | 2020 |

|

RU2727145C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ПРАВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2020 |

|

RU2725149C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ПАРАЛЛЕЛЬНЫЙ ТРОИЧНЫЙ КОМПАРАТОР | 2020 |

|

RU2723672C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ ТРИГГЕР | 2021 |

|

RU2777029C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ЛЕВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2021 |

|

RU2776031C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ D-ТРИГГЕР | 2022 |

|

RU2784374C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ПРЯМОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693639C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ "СУММАТОР ПО МОДУЛЮ ТРИ" | 2020 |

|

RU2725165C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ОБРАТНОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693590C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕРАВНОЗНАЧНОСТЬ" | 2018 |

|

RU2692573C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в быстродействующих аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков. Технический результат - создание токового порогового троичного элемента, в котором внутреннее преобразование информации производится в многозначной токовой форме сигналов, что позволяет повысить быстродействие устройств преобразования информации. Токовый пороговый троичный элемент содержит шесть входных полевых транзисторов, четыре источника напряжения смещения, четыре токовых зеркала, четыре источника опорного тока, входы и выходы устройства. 4 ил.

Токовый пороговый троичный элемент, содержащий первый (1) и второй (2) входы устройства, выход (3) устройства, первый (4) и второй (5) входные полевые транзисторы с объединенными затворами, которые подключены к первому (6) источнику напряжения смещения, третий (7) и четвертый (8) входные полевые транзисторы другого типа проводимости с объединенными затворами, которые подключены ко второму (9) источнику напряжения смещения, истоки первого (4) и третьего (7) входных полевых транзисторов соединены друг с другом, истоки второго (5) и четвертого (8) входных полевых транзисторов подключены друг к другу, первое (10) токовое зеркало, согласованное с первой (11) шиной источника питания, содержащее выход (12), второе (13) токовое зеркало, согласованное с первой (11) шиной источника питания, выход которого подключен к выходу (3) устройства, третье (14) токовое зеркало, согласованное со второй (15) шиной источника питания, вход которого подключен ко второму (2) входу устройства, стоки первого (4) и второго (5) входных полевых транзисторов соединены со второй (15) шиной источника питания, четвертое (16) токовое зеркало, согласованное со второй (15) шиной источника питания, имеющее выход (17), пятый (18) и шестой (19) входные полевые транзисторы, истоки которых объединены и связаны со второй (15) шиной источника питания через первый (20) источник опорного тока, затвор пятого (18) входного полевого транзистора подключен к объединенным истокам первого (4) и третьего (7) входных полевых транзисторов и выходу (17) четвертого (16) токового зеркала, седьмой (21) и восьмой (22) входные полевые транзисторы, истоки которых объединены и связаны со второй (15) шиной источника питания через второй (23) источник опорного тока, затвор седьмого (21) входного полевого транзистора подключен к объединенным истокам второго (5) и четвертого (8) входных полевых транзисторов, а также к выходу (12) первого (10) токового зеркала, сток седьмого (21) входного полевого транзистора подключен ко входу второго (13) токового зеркала, стоки третьего (7), четвертого (8) и восьмого (22) входных полевых транзисторов подключены к первой (11) шине источника питания, третий (24) источник опорного тока, четвертый (25) источник опорного тока, включенный между второй (15) шиной источника тока и выходом (12) первого (10) токового зеркала, третий (26) источник напряжения смещения подключен к затвору шестого (19) входного полевого транзистора, четвертый (27) источник напряжения смещения подключен к затвору восьмого (22) входного полевого транзистора, отличающийся тем, что первое (10) токовое зеркало снабжено дополнительным выходом (28), четвертое (16) токовое зеркало содержит первый (29) и второй (30) дополнительные выходы, выход третьего (14) токового зеркала подключен ко входу первого (10) токового зеркала, первый (1) вход устройства соединен со входом четвертого (16) токового зеркала, дополнительный (28) выход первого (10) токового зеркала подключен к выходу (17) четвертого (16) токового зеркала и связан со второй (15) шиной источника питания через третий (24) источник опорного тока, первый (29) дополнительный выход четвертого (16) токового зеркала соединен с затвором седьмого (21) входного полевого транзистора, второй (30) дополнительный выход четвертого (16) токового зеркала подключен ко входу второго (13) токового зеркала и соединен со стоком пятого (18) входного полевого транзистора, сток шестого (19) входного полевого транзистора согласован с первой (11) шиной источника питания.

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2016 |

|

RU2618901C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ОБРАТНОГО ЦИКЛИЧЕСКОГО СДВИГА | 2018 |

|

RU2693590C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| US 2010321061 A1, 23.12.2010. | |||

Авторы

Даты

2020-08-13—Публикация

2020-03-04—Подача