Изобретение относится к области микроэлектроники, а именно к полупроводниковым кремниевым транзисторам с увеличенным значением напряжения пробоя «исток-сток» и малой занимаемой площадью на кристалле.

Изготовление высоковольтного транзистора по самосовмещенной технологии является важной задачей в микроэлектронике. Зачастую увеличение напряжения пробоя «исток-сток» транзистора производится вследствие уменьшения концентрации примеси в дрейфовой области латерального ДМОП-транзистора (латеральный метал-оксид-полупроводник транзистор с двойной диффузией - ЛДМОП - транзистор) и увеличения ее геометрического размера (длины). Вследствие ограниченного количества места на кристалле стоит задача уменьшения занимаемой площади элементов интегральных схем (ИС). При этом для увеличения длины дрейфовой области зачастую используют LOCOS (сформированные посредством высокотемпературного окисления по маске островки оксида кремния). Такой метод ограничен уменьшением скорости окисления кремния с увеличением выращенного оксида кремния (С.Зи, Физика полупроводниковых приборов: Кн.1. Пер.с англ. - 2-е перераб. и доп.Изд. - М: Мир, 1984. - 456 с., ил.).

В патенте «СВЧ LDMOS - транзистор» RU 2338297 С1 опубл. 10.11.2008, бюл. №31 приведен способ изготовления ЛДМОП-транзистора. В СВЧ LDMOS-транзисторе, содержащем полупроводниковую подложку с высокоомным и высоколегированными слоями первого типа проводимости, элементарные транзисторные ячейки в высокоомном слое подложки с канальной областью первого типа проводимости, высоколегированной истоковой, высоколегированной и слаболегированной стоковой областями второго типа проводимости, подзатворный диэлектрик из термической двуокиси кремния и электрод затвора над канальной областью транзисторных ячеек, термическую двуокись кремния и межслойный диэлектрик над слаболегированной областью транзисторных ячеек, электроды истока и стока транзисторных ячеек на лицевой стороне подложки, полевые экранирующие электроды в промежутке между электродами стока и затвора, соединенные с одним из торцов электрода истока транзисторных ячеек за пределами электродов затвора, общий электрод истока транзисторной структуры на тыльной стороне подложки, полевые экранирующие электроды транзисторных ячеек выполнены из материала электрода затвора и размещены на границе раздела термическая двуокись кремния - межслойный диэлектрик, причем толщина термической двуокиси кремния над слаболегированной областью стока составляет от 1,0 до 3,5 толщины подзатворного диэлектрика.

Недостатком такого транзистора является большая занимаемая площадь на кристалле вследствие своей геометрии.

В патенте «Quasi-vertical LDMOS device having closed cell layout» H01L 29/76 US 2007/ 0215939 A1 опубл. 14.03.2006 описан способ изготовления квазивертикального ЛДМОП транзистора, где контакт к истоку расположен с верхней стороны пластины, а контакт к стоку расположен с нижней стороны пластины. Затвор в свою очередь расположен с верхней стороны пластины. Таким образом, движение носителей заряда в открытом состоянии такого транзистора имеет квазивертикальную геометрию.

Недостатком такой структуры являются сложности с формированием контакта к нижней стороне пластины, а также ограничение толщины используемой пластины приборной возможностью имплантера - глубиной имплантации примеси при формировании слаболегированной области стока.

В патенте «LDMOS device and method for manucacturing the same» автора C.J. Ко US 7582533 B2 опубл. 2.03.2007 описан способ изготовления ЛДМОП, где методом высокотемпературного окисления формируется слой оксида кремния и на нем формируется затвор транзистора.

Недостатком способа является ограниченная толщина формируемого термическим окислением слоя оксида кремния.

В статье «The boost transistor: a field plate controlled LDMOST» авторов A. Ferrara, A. Heringa, B.K. Bokstreen и др. (Proceedings of the 27th International Symposium on Power Semiconductor devices and IC's, may 10-14, 2015, Kowloon Shangri-La, Hong Kong) описан способ изготовления ЛДМОП, где в дрейфовой области формируют щелевую изоляцию (STI) и дополнительный контакт над ней. Эта щелевая изоляция играет роль конденсатора, подача положительного напряжения на контакт над этой изоляцией приводит к притягиванию отрицательных зарядов к противоположной границе щелевой изоляции. Из книги Зи С.(Физика полупроводниковых приборов: Кн. 1. Пер.с англ. - 2е перераб. и доп.Изд. - М.: Мир, 1984. - 456 с.) известно, что значение напряжения, поданное на плоский конденсатор, обратно пропорционально расстоянию между обкладками (в нашем случае толщине щелевой изоляции). Таким образом, толщина щелевой изоляции ограничена. Например посредством численного расчета получено, что при подаче напряжения 70 В на верхний контакт щелевой изоляции, высота, ширина и толщина которой равны 1 мкм, изменение концентрации отрицательных носителей заряда под щелевой изоляцией составило порядка 10-12 см-3.

Таким образом, недостатком такого способа формирования дрейфовой области является ограничение толщины формируемой щелевой изоляции (менее 1 мкм).

В патенте US9601595 В2 High breakdown voltage LDMOS device, H.Yang, D.J. Blomberg, J.Zuo опубл. 07.04.2016, выбранном за прототип, описан способ изготовления ЛДМОП на подложке КНИ, где посредством эпитаксии легированных слоев кремния и ионной имплантации примеси по маске формируются необходимые области ЛДМОП. В данном случае щелевая изоляция (STI) формируется в сформированных слаболегированных дрейфовых областях и ограничена их размерами. Так как толщина дрейфовых областей составляет 0,5-4 мкм, то толщина щелевой изоляции должна быть значительно меньше этого значения.

Недостатками данной конструкции являются: ограниченная толщина щелевой изоляции в дрейфовой области; использование КНИ структур приводит к затруднению отвода тепла от ИС; сложность в изготовлении и удлинение процесса изготовления вследствие использования процесса эпитаксии.

Задачей, на решение которой направлено изобретение, является создание способа изготовления субмикронного ЛДМОП-транзистора, характеризующегося повышенным напряжением пробоя.

Техническим результатом предлагаемого способа изготовления ЛДМОП-транзистора с увеличенным напряжением пробоя является расширение области применения изготавливаемых ИС на таких транзисторах, высокая степень интеграции транзисторов на кристалле.

Технический результат достигается тем, что в способе изготовления ЛДМОП-транзистора с увеличенным значением напряжения пробоя, включающем формирование областей стока, истока, затвора, подзатворного диэлектрика, на пластине объемного кремния создают углубление в форме колодца травлением кремния по маске, соответствующей проектной норме используемой технологии, создают карман транзистора путем легирования кремния по маске. Далее создают дрейфовую область транзистора путем ионной имплантации примеси по маске, таким образом, чтобы эта область смыкалась с областью кармана. Далее заполняют углубление оксидом кремния путем осаждения оксида кремния из газовой фазы с последующей химико-механической полировкой. После химической очистки полученной структуры формируют слой подзатворного диэлектрика методом высокотемпературного окисления. Далее осаждают слой поликристаллического кремния и формируют затвор транзистора травлением по маске. Затем формируют сильнолегированные области истока и стока транзистора посредством имплантации примеси и последующего высокотемпературного отжига. Далее формируют спейсеры транзистора путем осаждения оксида кремния с последующим реактивно-ионного травлением, на полученной структуре формируют контакты.

Изобретение поясняют следующие фигуры.

Фигуры 1-9 показывают основные этапы изготовления ЛДМОП-транзистора.

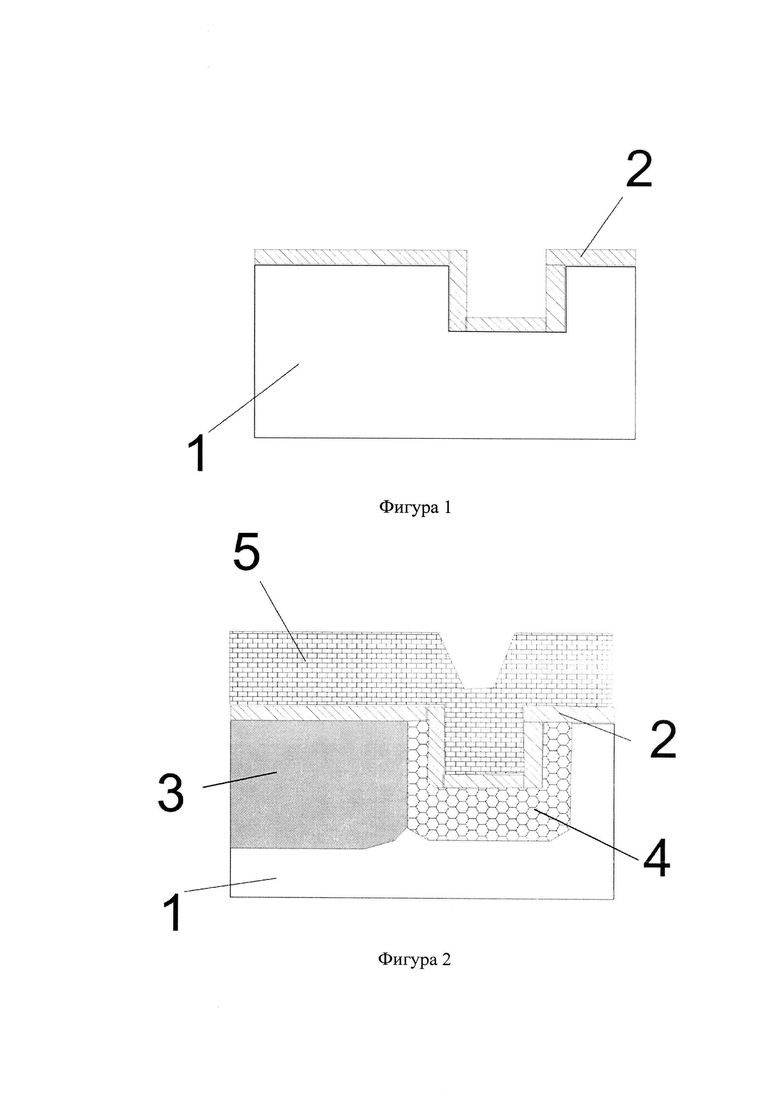

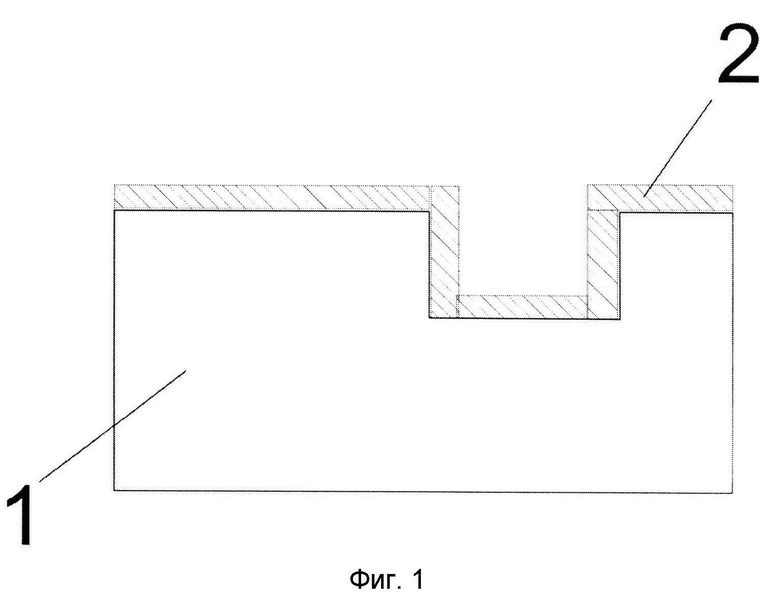

На фигуре 1 показана структура после формирования на пластине объемного кремния углубления в форме колодца и высокотемпературного окисления.

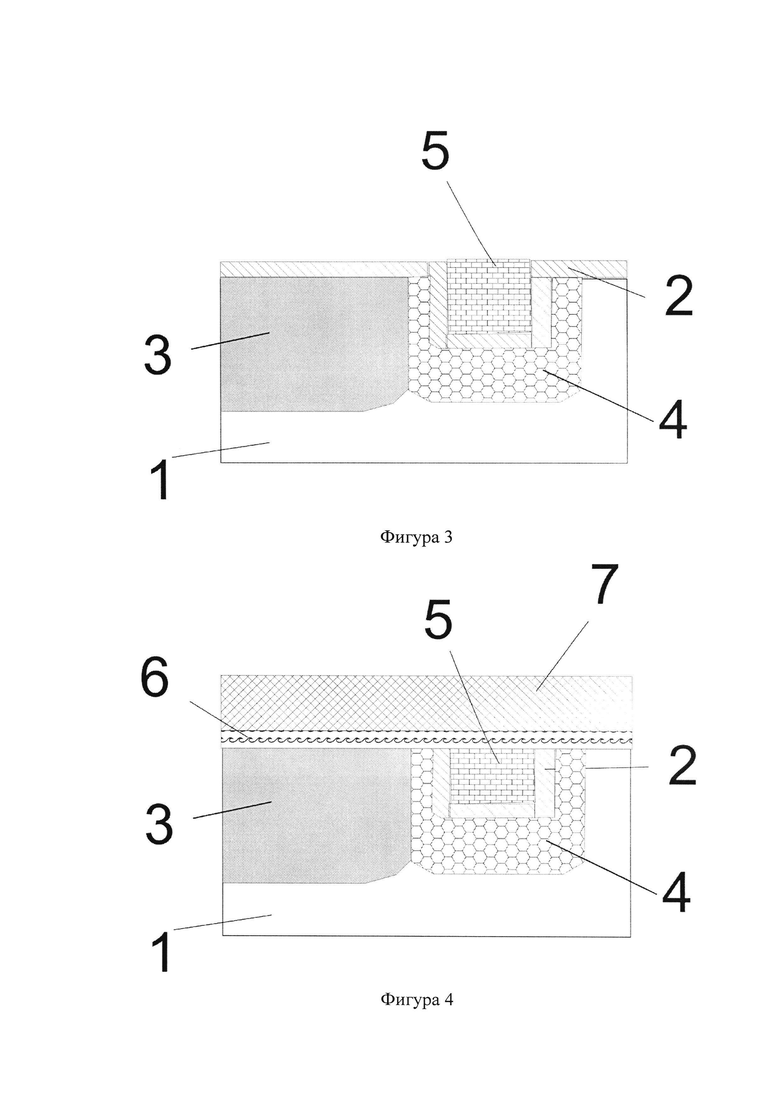

На фигуре 2 показана структура после формирования кармана транзистора, дрейфовой области и осаждения слоя оксида кремния.

На фигуре 3 показана структура после химико-механической полировки.

На фигуре 4 показана структура после формирования подзатворного диэлектрика и осаждение поликристаллического кремния.

На фигуре 5 показана структура после формирования затвора транзистора.

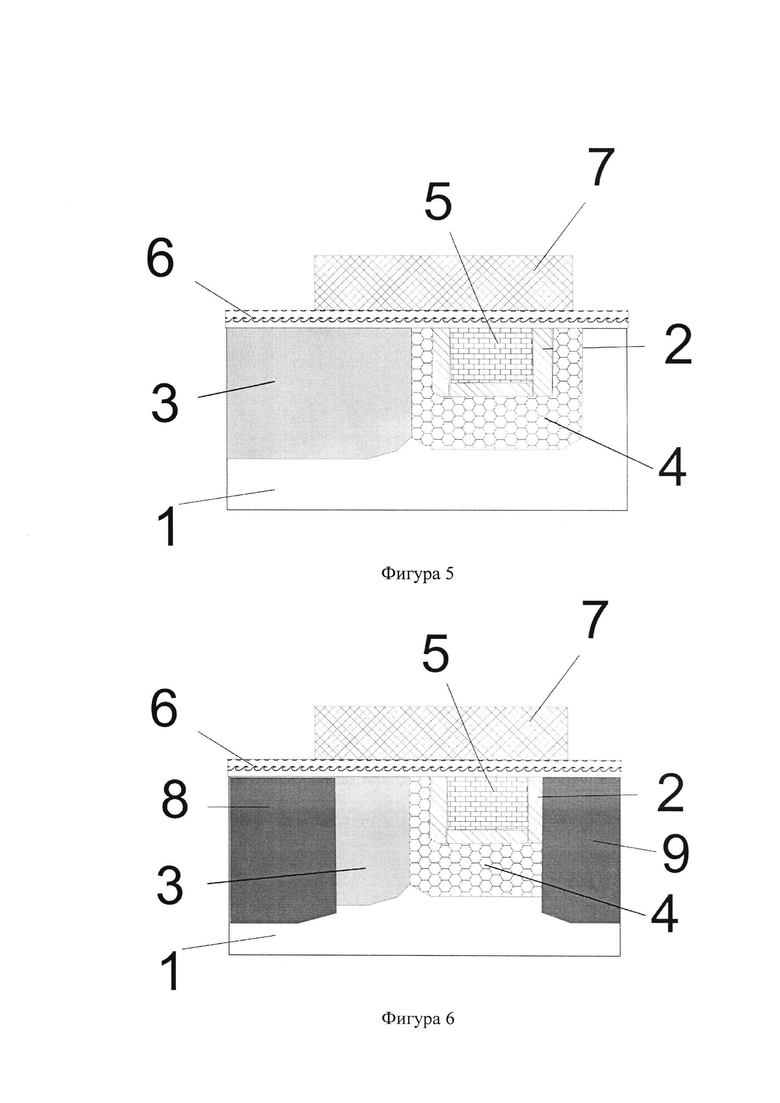

На фигуре 6 показана структура после формирования областей истока, стока транзистора.

На фигуре 7 показана структура после формирования спейсеров транзистора.

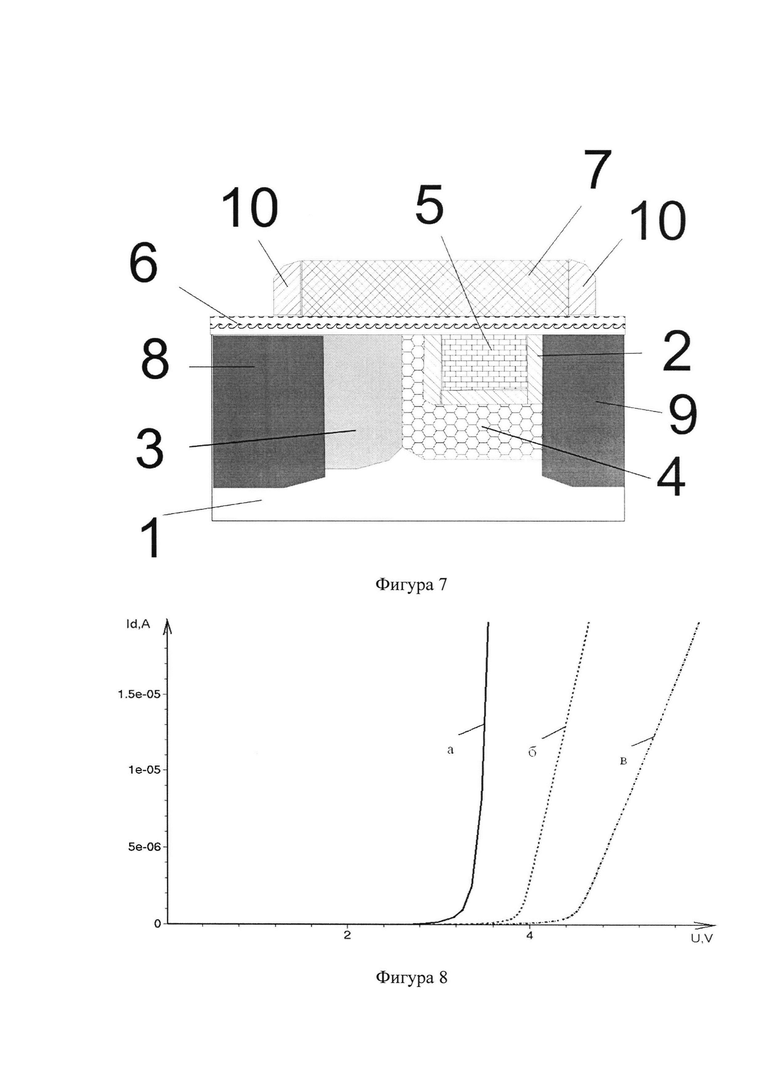

На фигуре 8 приведены вольтамперные характеристики транзисторов, изготовленных по предложенному способу, полученные посредством численного моделирования

На фигурах 1-7 приняты следующие обозначения:

1 - пластина объемного кремния;

2 - слой термического оксида кремния;

3 - легированный слой кремния (карман транзистора);

4 - легированный слой кремния (дрейфовая область);

5 - слой осажденного оксида кремния;

6 - слой подзатворного оксида кремния;

7 - слой поликристаллического кремния;

8 - сильнолегированная область кремния (исток транзистора);

9 - сильнолегированная область кремния (сток транзистора);

10 - спейсеры транзистора.

Рассмотрим реализацию предлагаемого способа на примере изготовления n - канального ЛДМОП-транзистора.

На пластине объемного кремния травят кремний по маске, соответствующей фотошаблону проектной нормы используемой технологии. Сформированное таким образом углубление в форме колодца в пластине объемного кремния будем называть колодцем. Далее посредством высокотемпературного окисления формируют термический оксид кремния 2 (фиг. 1).

Затем посредством ионной имплантации разной примеси по маскам и последующего отжига формируют область кармана транзистора 3 и дрейфовую область транзистора 4, таким образом, чтобы исключить наличие нелегированного кремния между ними. Далее осаждают слой оксида кремния 5, толщина которого должна быть не меньше глубины колодца так, чтобы колодец был заполнен оксидом кремния (фиг. 2).

Затем поверхность структуры планаризуют посредством химико-механической полировки (фиг. 3).

Далее после жидкостного травления оксида кремния проводят высокотемпературное окисление, формируя подзатворный диэлектрик 6. Затем проводят осаждение поликристаллического кремния 7 (фиг. 4).

Далее формируют затвор транзистора посредством травления поликристаллического слоя 7 по маске (фиг. 5).

Затем полученную структуру легируют посредством имплантации примеси по маске и последующего отжига, формируют сильнолегированные области истока 8 и стока 9 транзистора (фиг. 6).

Далее формируют спейсеры транзистора 10 (фиг. 7) посредством осаждения слоя оксида кремния и реактивного ионного травления.

Процесс завершается формированием контактов посредством силицидирования областей истока, стока, затвора транзистора (на фигуре не показано).

На фигуре 8 приведены вольт-амперные характеристики оригинальных n-канальных ЛДМОП-транзисторов, отличающихся только глубиной сформированного колодца. Транзисторы обладали следующими характеристиками: длина канала составляла 155 нм, концентрация фосфора в дрейфовой области 2⋅1018 см-3, пороговое напряжение 0,7 В, ширина колодца (проектные нормы) 0,35 мкм.

Рассмотрим влияние увеличения глубины формируемого колодца на напряжение пробоя «исток-сток». Кривая а на фигуре 8 соответствует конструкции транзистора с нулевой глубиной колодца, то есть без колодца. На такой конструкции напряжение пробоя «исток-сток» равно 3,5 В. При увеличении глубины колодца до 0,4 мкм (кривая б), напряжение пробоя «исток-сток» увеличивается до 4 В. При увеличении глубины колодца до 0,5 мкм (кривая в), напряжение пробоя «исток-сток» увеличивается до 4,2 В. Все остальные электрофизические характеристики таких транзисторов остаются неизменными.

При уменьшении концентрации примеси фосфора в дрейфовой области значительно увеличится не только напряжение пробоя «исток-сток», но и сдвиг напряжения пробоя при увеличении глубины формируемого колодца, вследствие увеличения сопротивления дрейфовой области (Зи.С, Физика полупроводниковых приборов:Кн.1.Пер.с англ. - 2-е перераб. и доп. Изд. - М.: Мир, 1984. - 456 с.).

Особенностью предложенного способа изготовления ЛДМОП-транзистора является возможность формирование колодца любой (более 4 мкм) глубины, за счет формирования дрейфовой области транзистора (проведения имплантации примеси) после травления в кремниевом слое колодца. При этом необходимо учитывать, что при использовании режима имплантации примеси под тремя углами (+α, 0, -α), для избежания теневого эффекта, должно выполняться следующее: tgα=W/L, где W - ширина колодца, L - высота колодца.

Таким образом, использование предложенного способа позволяет изготавливать высоковольтные ЛДМОП-транзисторы и увеличенным напряжение пробоя «исток-сток» и высокой плотностью интеграции таких транзисторов на кристалле.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МОП-ТРАНЗИСТОРА НА СТРУКТУРЕ "КРЕМНИЙ НА ИЗОЛЯТОРЕ" | 2022 |

|

RU2784405C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS-ТРАНЗИСТОРНЫХ КРИСТАЛЛОВ С МНОГОСЛОЙНОЙ ДРЕЙФОВОЙ ОБЛАСТЬЮ СТОКА | 2024 |

|

RU2819581C1 |

| Способ изготовления латерального биполярного транзистора с изолированным затвором на структуре "кремний на изоляторе" | 2023 |

|

RU2804506C1 |

| Способ изготовления быстродействующего кремниевого МОП-транзистора | 2024 |

|

RU2822006C1 |

| Способ изготовления транзистора с зависимым контактом к подложке | 2021 |

|

RU2758413C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS ТРАНЗИСТОРОВ | 2010 |

|

RU2439744C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МДП НАНОТРАНЗИСТОРА С ЛОКАЛЬНЫМ УЧАСТКОМ ЗАХОРОНЕННОГО ИЗОЛЯТОРА | 2012 |

|

RU2498447C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНОЙ СВЧ LDMOS СТРУКТУРЫ | 2012 |

|

RU2515124C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ КРЕМНИЕВЫХ СВЧ LDMOS ТРАНЗИСТОРОВ | 2013 |

|

RU2535283C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ АВТОМАСШТАБИРУЕМОЙ БИКМОП СТРУКТУРЫ | 2003 |

|

RU2234165C1 |

Изобретение относится к области микроэлектроники, а именно к полупроводниковым кремниевым транзисторам с увеличенным значением напряжения пробоя «исток-сток» и малой занимаемой площадью на кристалле. Техническим результатом предлагаемого способа является расширение области применения изготавливаемых ИС на таких транзисторах, высокая степень интеграции транзисторов на кристалле. В предлагаемом способе изготовления латерального ДМОП-транзистора на пластине объемного кремния создают колодец необходимой высоты посредством травления кремния по маске, формируют карман и дрейфовую область транзистора. Затем методом осаждения оксида кремния и дальнейшей планаризации поверхности заполняют сформированный колодец. Далее формируют подзатворный диэлектрик посредством высокотемпературного окисления и формируют затвор транзистора посредством осаждения слоя поликремния и его дальнейшего травления по маске. Затем методом ионной имплантации примеси и дальнейшего высокотемпературного отжига формируют области истока и стока. Далее формируют спейсеры транзистора посредством осаждения и дальнейшего реактивно-ионного травления оксида кремния. 8 ил.

Способ изготовления латерального ДМОП-транзистора с увеличенным значением напряжения пробоя, включающий формирование областей стока, истока, затвора, подзатворного диэлектрика, отличающийся тем, что на пластине объемного кремния создают углубление в форме колодца травлением кремния по маске, соответствующей проектной норме используемой технологии, создают карман транзистора путем легирования кремния по маске, далее создают дрейфовую область транзистора путем ионной имплантации примеси по маске таким образом, чтобы эта область смыкалась с областью кармана, далее заполняют углубление оксидом кремния путем осаждения оксида кремния из газовой фазы с последующей химико-механической полировкой, затем после химической очистки полученной структуры формируют слой подзатворного диэлектрика методом высокотемпературного окисления, далее осаждают слой поликристаллического кремния и формируют затвор транзистора травлением по маске, затем формируют сильнолегированные области истока и стока транзистора посредством имплантации примеси и последующего высокотемпературного отжига, далее формируют спейсеры транзистора путем осаждения оксида кремния с последующим реактивно-ионным травлением, на полученной структуре формируют контакты.

| ЛАТЕРАЛЬНЫЙ БИПОЛЯРНЫЙ ТРАНЗИСТОР НА СТРУКТУРАХ "КРЕМНИЙ НА ИЗОЛЯТОРЕ" И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2021 |

|

RU2767597C1 |

| СПОСОБ ПОЛУЧЕНИЯ ЛАТЕРАЛЬНЫХ НАНОСТРУКТУР | 2017 |

|

RU2676801C1 |

| CN 109887993 A, 14.06.2019 | |||

| CN 110148622 A, 20.08.2019. | |||

Авторы

Даты

2023-09-11—Публикация

2023-03-22—Подача