Техническая область

Изобретение относится к области внутричиповой связи, в частности к каналу однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками и способу его создания.

Фоновая техника

В существующих встроенных электронных продуктах как только печатная плата установлена на корпусе, становится трудно продолжать отладку и обновление других чипов, кроме основного чипа управления на печатной плате. В таких случаях пользователям часто бывает необходимо открыть закрытый корпус и подключить проводы к соответствующим паяльным точкам на печатной плате для отладки или обновления прошивки через отладчик.

Если продукт включает основной чип управления и тестовый чип, устройство внешней связи должен быть подключено к тестовому чипу продукта, но нет физического соединения между тестовым чипом и внешним интерфейсом продукта, при использовании существующих технологий соединение устройства внешней связи с тестовым чипом осуществляется путем установки электронных схем на главном чипе управления, что позволяет соединить устройство внешней связи с тестовым чипом; переключение направления передачи требует участия программного обеспечения основного чипа управления, и как только после создания канала связи, связь между устройством внешней связи и тестовым чипом создается автоматически. Программное обеспечение, работающее на основном чипе управления, не имеет возможности участвовать в процессе переключения направления связи, а аппаратная схема не может автоматически адаптироваться, поэтому реализовать настоящую однолинейную двунаправленную связь невозможно, в лучшем случае может реализоваться только однолинейная однонаправленная связь, что сильно ограничивает сферу применения.

Сущность изобретения

Чтобы преодолеть недостатки предшествующего уровня техники, настоящее изобретение предлагает канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками и способ его создания для улучшения связи между устройством внешней связи и чипом внутри продукта.

Для решения вышеуказанных проблем настоящее изобретение предлагает следующее техническое решение:

Путем построения канала однолинейной двунаправленной прямой связи между клеммами контактной площадки в чипе А клемма первой контактной площадки подключается к устройству внешней связи, клемма второй контактной площадки подключена к другому чипу В, который подключен к устройству внешней связи. Когда нет необходимости устанавливать связь между устройством внешней связи и чипом В, клеммы двух контактных площадок используются для нормальной передачи сигнала и связи в чипе А; Когда связь между устройством внешней связи и чипом В должна быть создана, клеммы двух контактных площадок образуют канал двунаправленной прямой связи в чипе A, предназначенный для передачи сигнала и связи между устройством внешней связи и чипом B.

Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками, включающий процессорный блок, блок связи, блок регистров, клемму первой контактной площадки и клемму второй контактной площадки.

Канал связи также включает первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи; первый модуль однонаправленной прямой связи используется для однонаправленной передачи сигнала первого уровня от клеммы второй контактной площадки на клемму второй контактной площадки; второй модуль однонаправленной прямой связи используется для однонаправленной передачи сигнала второго уровня от клеммы второй контактной площадки на клемму первой контактной площадки, первый модуль однонаправленной прямой связи подключен к второму модулю однонаправленной прямой связи посредством внутренних узлов; первый модуль однонаправленной прямой связи включает первую входную клемму, первую выходную клемму и первую управляющую клемму, второй модуль однонаправленной прямой связи включает вторую входную клемму, вторую выходную клемму и вторую управляющую клемму; первая входная клемма подключена ко клемме первой контактной площадки и второй выходной клемме, вторая выходная клемма подключена ко клемме второй контактной площадки и первой выходной клемме, первая управляющая клемма и вторая управляющая клемма подключены к блоку регистров.

Процессорный блок подключен к блоку связи и блоку регистров соответственно. Процессорный блок используется для управления переключением блока связи и блока регистров во время двунаправленной связи, подключен к первому модулю однонаправленной прямой связи и второму модулю однонаправленной прямой связи посредством блока связи, подключен к первой управляющей клемме и второй управляющей клемме посредством блока регистров; первая клемма блока регистров подключена к первой управляющей клемме, вторая клемма подключена ко второй управляющей клемме.

Более того, первый модуль однонаправленной прямой связи включает первый логический элемент “И”, первый резистор, первый логический элемент “ИЛИ”, первый логический элемент “НЕ”, второй логический элемент “НЕ” и первый логический элемент с тремя состояниями; первая входная клемма первого логического элемента “И” подключена ко клемме первой площадки и второй выходной клемме, вторая выходная клемма подключена к первой клемме блока регистров; первая клемма первого резистора подключен ко клемме первой контактной площадки, вторая клемма подключена к источнику питания постоянного тока; первая входная клемма первого логического элемента “ИЛИ” подключена к выходной клемме первого логического элемента “И”; входная клемма первого логического элемента “НЕ” подключена ко второму модулю однонаправленной прямой связи посредством внутренних узлов, выходная клемма подключена ко второй входной клемме первого логического элемента “ИЛИ”; входная клемма второго логического элемента “НЕ” подключена к выходной клемме первого логического элемента “ИЛИ” и входной клемме первого логического элемента с тремя состояниями; выходная клемма первого логического элемента с тремя состояниями подключена к выходной клемме второго логического элемента “НЕ” и клемме второй контактной площадки.

Второй модуль однонаправленной прямой связи включает второй логический элемент “И”, второй резистор, второй логический элемент “ИЛИ”, третий логический элемент “НЕ”, четвертый логический элемент “НЕ” и второй логический элемент с тремя состояниями; первая входная клемма второго логического элемента “И” подключена ко клемме первой контактной площадки и второй выходной клемме, его вторая выходная клемма подключена к первой клемме блока регистров; первая клемма второго резистора подключена ко клемме второй контактной площадки, вторая клемма подключена к источнику питания постоянного тока; первая входная клемма второго логического элемента “ИЛИ” подключена к выходной клемме второго логического элемента “И”; входная клемма третьего логического элемента “НЕ” подключена к первому модулю однонаправленной прямой связи посредством внутренних узлов, выходная клемма подключена ко второй входной клемме второго логического элемента “ИЛИ”; входная клемма четвертого логического элемента “НЕ” подключена к выходной клемме второго логического элемента “ИЛИ” и входной клемме второго логического элемента с тремя состояниями; выходная клемма второго логического элемента с тремя состояниями подключена к выходной клемме четвертого логического элемента “НЕ” и клемме первой контактной площадки.

Ещё более того, внутренние узлы первого модуля однонаправленной прямой связи и второго модуля однонаправленной прямой связи соединены таким образом: выходная клемма первого логического элемента “ИЛИ” подключена к входной клемме третьего логического элемента “НЕ”, выходная клемма второго логического элемента “ИЛИ” подключена к входной клемме первого логического элемента “НЕ”.

Способ однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками, включающий:

внутричиповый процессорный блок отправляет команду запуска режима двунаправленной прямой связи в блок связи и блок регистров в соответствии с протоколом связи; блок связи принимает команду запуска режима двунаправленной прямой связи и переключает первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи в режим прямой двунаправленной связи, то есть передача данных и прием данных на клемме первой контактной площадки и на клемме второй контактной площадки производятся в соответствии с протоколом связи процессорного блока; блок регистров принимает команду запуска режима двунаправленной прямой связи, первая выходная клемма блока регистров отправляет первый сигнал управления на первую управляющую клемму, и первый сигнал управления используется для управления переключением первого модуля однонаправленной прямой связи , вторая выходная клемма блока регистров отправляет второй сигнал управления на вторую управляющую клемму, второй сигнал управления используется для управления переключением второго модуля однонаправленной прямой связи.

Двунаправленная прямая связь между внутричиповыми клеммами двух контактных площадок производится в соответствии со следующими этапами:

В соответствии с протоколом связи первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи переключают клемму первой контактной площадки и клемму второй контактной площадки в режим отправки или приема в соответствии с направлением передачи сигнала;

когда клемма первой контактной площадки находится в режиме отправки, клемма второй контактной площадки находится в режиме приема: первая входная клемма первого модуля однонаправленной прямой связи принимает сигнал первого уровня, отправленный клеммой первой контактной площадки, его вторая выходная клемма принимает первый сигнал управления, отправленный первой управляющей клеммой; вторая выходная клемма второго модуля однонаправленной прямой связи принимает второй сигнал управления, отправленный второй управляющей клеммой; клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки через первый модуль однонаправленной прямой связи; в то же время сигнал первого уровня поддерживает режим отправки первого модуля однонаправленной прямой связи посредством соединительного отношения внутренних узлов и прерывает выход сигнала от первой выходной клеммы второго модуля однонаправленной прямой связи;

когда клемма второй контактной площадки находится в режиме отправки, клемма первой контактной площадки находится в режиме приема: первая входная клемма второго модуля однонаправленной прямой связи принимает сигнал второго уровня, отправленный клеммой второй контактной площадки, его вторая выходная клемма принимает второй сигнал управления, отправленный второй управляющей клеммой; вторая выходная клемма первого модуля однонаправленной прямой связи принимает первый сигнал управления, отправленный первой управляющей клеммой; клемма второй контактной площадки отправляет сигнал второго уровня на клемму второй контактной площадки посредством второго модуля однонаправленной прямой связи; в то же время сигнал второго уровня поддерживает режим отправки второго модуля однонаправленной прямой связи посредством соединительного отношения внутренних узлов и прерывает выход сигнала от первой выходной клеммы первого модуля однонаправленной прямой связи.

Ещё более того, когда клемма первой контактной площадки находится в режиме отправки, клемма второй контактной площадки находится в режиме приема:

Первая входная клемма первого логического элемента “И” принимает сигнал первого уровня, отправленный клеммой первой контактной площадки, его вторая выходная клемма принимает первый сигнал управления и выполняет логическую операцию И сигнала первого уровня и первого сигнала управления, выходит первый сигнал уровня на первый логический элемент “ИЛИ”, сигнал первого уровня и первый сигнал управления являются сигналами высокого уровня; первая входная клемма первого логического элемента “ИЛИ” принимает сигнал первого уровня, клемма второй контактной площадки по умолчанию обеспечивает высокий уровень, выходная клемма первого логического элемента “НЕ” выходит сигнал высокого уровня посредством соединительного отношения внутренних узлов, в результате этого первая выходная клемма логического элемента “ИЛИ” выходит сигнал первого уровня; входная клемма второго логического элемента “НЕ” и входная клемма первого логического элемента с тремя состояниями принимают сигнал первого уровня, отправленный выходной клеммой первого логического элемента “ИЛИ”, второй логический элемент “НЕ” инвертирует сигнал первого уровня, выходная клемма второго логического элемента “НЕ” выходит сигнал инвертированный сигнал первого уровня на управляющую клемму первого логического элемента с тремя состояниями; когда сигнал первого уровня является сигналом высокого уровня, на управляющей клемме первого логического элемента с тремя состояниями появляется сигнал низкого уровня, первый логический элемент с тремя состояниями закрыт, выходная клемма первого логического элемента с тремя состояниями не выходит сигнал высокого уровня, клемма второй контактной площадки используется для установки и увеличения сигнала высокого уровня с помощью второго резистора; когда сигнал первого уровня является сигналом низкого уровня, управляющая клемма первого логического элемента с тремя состояниями обеспечивает сигнал высокого уровня, первый логический элемент с тремя состояниями открыт, выходная клемма первого логического элемента с тремя состояниями выходит сигнал низкого уровня, на клемме второй контактной площадки появляется сигнал низкого уровня.

Когда клемма второй контактной площадки находится в режиме отправки, клемма первой контактной площадки находится в режиме приема:

первая входная клемма второго логического элемента “И” принимает сигнал второго уровня, отправленный клеммой второй контактной площадки, его вторая выходная клемма принимает второй сигнал управления и выполняет логическую операцию И сигнала второго уровня и второго сигнала управления и выходит сигнал второго уровня на второй логический элемент “ИЛИ”, сигнал второго уровня и второй сигнал управления являются сигналами высокого уровня; первая входная клемма второго логического элемента “ИЛИ” принимает сигнал второго уровня, клемма первой контактной площадки по умолчанию обеспечивает высокий уровень, посредством соединительного отношения внутренних узлов выходная клемма второго логического элемента “НЕ” выходит сигнал низкого уровня, в результате этого вторая выходная клемма логического элемента “ИЛИ” выходит сигнал первого уровня; входная клемма четвертого логического элемента “НЕ” и входная клемма второго логического элемента с тремя состояниями принимают сигнал второго уровня, отправленный выходной клеммой второго логического элемента “ИЛИ”, четвертый логический элемент “НЕ” инвертирует сигнал второго уровня, выходная клемма четвертого логического элемента “НЕ” выходит инвертированный сигнал первого уровня на управляющую клемму второго логического элемента с тремя состояниями; когда сигнал второго уровня является сигналом высокого уровня, на управляющей клемме второго логического элемента с тремя состояниями выходится сигнал низкого уровня, второй логический элемент с тремя состояниями закрыт, выходная клемма второго логического элемента с тремя состояниями не выходит сигнал высокого уровня, клемма первой контактной площадки используется для установки и увеличения сигнала высокого уровня с помощью второго резистора; когда сигнал второго уровня является сигналом низкого уровня, на управляющей клемме второго логического элемента с тремя состояниями появляется сигнал высокого уровня, второй логический элемент с тремя состояниями открыт, на выходной клемме второго логического элемента с тремя состояниями появляется сигнал низкого уровня, на клемме первой контактной площадки появляется сигнал низкого уровня.

Ещё более того, когда клемма первой контактной площадки начинает отправлять сигнал первого уровня на клемму второй контактной площадки: второй логический элемент “И” обеспечивает высокий уровень на первой выходной клемме и второй выходной клемме и выходит сигнал высокого уровня; когда клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки: третий логический элемент “НЕ” выходит сигнал инвертированный сигнал первого уровня, а первая входная клемма второго логического элемента “И” принимает сигнал уровня сигнала первого уровня, второй логический элемент “ИЛИ” выходит сигнал высокого уровня, выходная клемма первого элемента “НЕ” и выходная клемма четвертого элемента “НЕ” поддерживают низкий уровень, первый логический элемент “ИЛИ” продолжает выходить сигнал уровня сигнала первого уровня, выходная клемма второго логического элемента с тремя состояниями не выходит сигнал.

Ещё более того, когда клемма второй контактной площадки начинает отправлять сигнал второго уровня на клемму первой контактной площадки: на первую входную клемму и вторую выходную клемму первого логического элемента “И” поступает высокий уровень и выходит сигнал высокого уровня; выходная клемма первого логического элемента “ИЛИ “выходит сигнал высокого уровня, выходная клемма первого логического элемента “НЕ” поддерживает низкий уровень; когда клемма второй контактной площадки отправляет сигнал первого уровня на клемму первой контактной площадки: первый логический элемент “НЕ” выходит сигнал инвертированный сигнал первого уровня, первая входная клемма первого элемента “И” принимает сигнал первого уровня, первый логический элемент “ИЛИ” выходит сигнал высокого уровня, выходной клемме третьего логического элемента “НЕ” и выходной клемме второго логического элемента “НЕ “поддерживает низкий уровень, второй логический элемент “ИЛИ” продолжает выходить сигнал первого уровня, выходная клемма первого логического элемента с тремя состояниями не выходит сигнал.

По сравнению с предшествующим уровнем техники полезный эффект настоящего изобретения заключается в том, что: за счет построения канала двунаправленной прямой связи между внутричиповыми клеммами двух контактных площадок чипа, когда связь между устройством внешней связи и другим чипом не должна быть создана, клемма первой контактной площадки и клемма второй контактной площадки могут использоваться как обычные клеммы для передачи сигнала; когда связь между устройством внешней связи и другим чипом должна быть создана, клемма первой контактной площадки подключается к устройству внешней связи, клемма второй контактной площадки подключена к другому чипу; внутричиповый процессорный блок управляет переключением канала однолинейной двунаправленной прямой связи посредством блока регистров, режим приема или отправки клеммы первой контактной площадки и клеммы второй контактной площадки поддерживается за счет структуры канала однолинейной двунаправленной прямой связи. Передача сигналов и переключение клеммы первой контактной площадки и второй контактной площадки осуществляется по протоколу связи; таким образом достигается самоадаптация оборудования канала и управление передачей программным обеспечением, реализуется настоящая однолинейная двунаправленная прямая связь.

Ниже приведено подробное описание настоящего изобретения в сочетании с прилагаемыми чертежами и конкретными примерами осуществления.

Описание прилагаемых чертежей

Для того чтобы более наглядно проиллюстрировать технические решения примеров осуществления настоящего раскрытия, ниже приводится краткое описание прилагаемых чертежей, используемых в примерах осуществления, и будет очевидно, что прилагаемые чертежи в следующем описании являются лишь некоторыми из примеров осуществления настоящего раскрытия, и что другие чертежи могут быть получены на их основе без каких-либо творческих усилий со стороны специалиста в данной области техники.

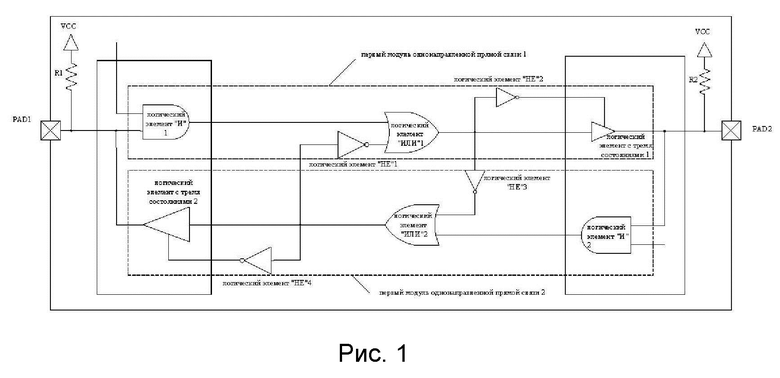

На рисунке 1 приведена принципиальная схема структуры канала одного из примеров осуществления настоящего изобретения.

Описание условных обозначений на прилагаемом рисунке: первый резистор: R1, второй резистор: R2, первый логический элемент “И”: логический элемент “И” 1, второй логический элемент “И”: логический элемент “И” 2, первый логический элемент “ИЛИ”: логический элемент “ИЛИ” 1, второй логический элемент “ИЛИ”: логический элемент “ИЛИ”2, первый логический элемент “НЕ”: логический элемент “НЕ” 1, вторые логический элемент “НЕ”: логический элемент “НЕ” 2, третий логический элемент “НЕ”: логический элемент “НЕ” 3, четвертый логический элемент “НЕ”: логический элемент “НЕ” 4, первый логический элемент с тремя состояниями: логический элемент с тремя состояниями 1, второй логический элемент с тремя состояниями : логический элемент с тремя состояниями 2.

Подробные способы осуществления

Примеры осуществления настоящего изобретения будут подробно описаны ниже в сочетании с прилагаемыми чертежами.

Воплощения настоящего раскрытия описаны ниже на конкретных примерах, и другие преимущества и выгоды настоящего раскрытия могут быть легко оценены специалистами в данной области, как раскрыто в данной спецификации. Очевидно, что описанные примеры осуществления являются лишь частью примеров осуществления настоящего раскрытия, но не всеми. Настоящее раскрытие может быть реализовано или применено различными другими конкретными способами, и различные детали спецификации могут быть модифицированы или изменены различными способами на основе различных представлений и применений без отхода от духа настоящего раскрытия. Следует отметить, что следующие примеры воплощения и признаки в примерах воплощения могут быть объединены друг с другом без противоречий. На основе воплощений, приведенных в настоящем раскрытии, все другие воплощения, полученные специалистом в данной области техники без творческого труда, попадают в объем охраны настоящего раскрытия.

Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками, включающий процессорный блок, блок связи, блок регистров, клемму первой контактной площадки и клемму второй контактной площадки;

канал связи также включает первый модуль однонаправленной прямой связи 1 и второй модуль прямой однонаправленной связи 2; первый модуль однонаправленной прямой связи 1 включает первую входную клемму, первую выходную клемму и первую управляющую клемму, второй модуль однонаправленной прямой связи 2 включает вторую входную клемму, вторую выходную клемму и вторую управляющую клемму;

первый модуль однонаправленной прямой связи используется для однонаправленной передачи сигнала первого уровня от клеммы первой контактной площадки на клемму второй контактной площадки, второй модуль однонаправленной прямой связи используется для однонаправленной передачи сигнала второго уровня от клеммы второй контактной площадки на клемму первой контактной площадки; первый модуль однонаправленной прямой связи подключен к второму модулю однонаправленной прямой связи посредством внутренних узлов; первая входная клемма подключена ко клемме первой контактной площадки и второй выходной клемме, вторая выходная клемма подключена ко клемме второй контактной площадки и первой выходной клемме, первая управляющая клемма и вторая управляющая клемма подключены к блоку регистров.

Процессорный блок подключен к блоку связи и блоку регистров соответственно, процессорный блок используется для управления переключением блока регистров и блока связи при двунаправленной связи,

блок связи подключен к первому модулю однонаправленной прямой связи 1 и второй модуль однонаправленной прямой связи 2; первая клемма блока регистров подключена к первой управляющей клемме, вторая клемма блока регистров подключена ко второй управляющей клемме; первый модуль однонаправленной прямой связи 1 используется для передачи сигнала первого уровня внутри чипа, второй модуль однонаправленной прямой связи 2 используется для передачи сигнала второго уровня внутри чипа, первый модуль однонаправленной прямой связи 1 подключен к второму модулю однонаправленной прямой связи 2 посредством внутренних узлов.

Клемма первой контактной площадки подключена к первой входной клемме первого модуля однонаправленной прямой связи 1 и первой выходной клемме второго модуля однонаправленной прямой связи 2, используется для отправки сигнала в первой модуль прямой однонаправленной связи 1 и приема сигнала от второго модуля однонаправленной прямой связи 2 во время двунаправленной связи. Клемма второй контактной площадки подключена ко второй выходной клемме второго модуля однонаправленной прямой связи 2 и первой выходной клемме первого модуля однонаправленной прямой связи 1, используется для отправки сигнала в второй модуль прямой однонаправленной связи 2 и приема сигнала от первого модуля однонаправленной прямой связи 1 во время двунаправленной связи.

В частности, как показано на рисунке 1, первый модуль однонаправленной прямой связи 1 включает первый логический элемент “И”, первый резистор R1, первый логический элемент “ИЛИ”, первый логический элемент “НЕ”, второй логический элемент “НЕ” и первый логический элемент с тремя состояниями. второй модуль однонаправленной прямой связи 2 включает второй логический элемент “И”, второй резистор R2, второй логический элемент “ИЛИ”, третий логический элемент “НЕ”, четвертый логический элемент “НЕ” и второй логический элемент с тремя состояниями.

Первая входная клемма первого логического элемента “И” подключена к выходной клемме первой контактной площадки и второй выходной клемме, вторая выходная клемма первого логического элемента “И” подключена к первой выходной клемме блока регистров, первая выходная клемма первого резистора R1 подключена к выходной клемме первой контактной площадки клемма, вторая клемма первого резистора R1 подключена к источнику питания постоянного тока, первая входная клемма первого логического элемента “ИЛИ” подключена к выходной клемме первого логического элемента “И”, входная клемма первого логического элемента “НЕ” подключена ко второму модулю однонаправленной прямой связи посредством внутренних узлов, выходная клемма первого логического элемента “НЕ” подключена ко второй выходной клемме первого логического элемента “ИЛИ, входная клемма второго логического элемента “НЕ” подключена к выходной клемме первого логического элемента “ИЛИ” и входной клемме первого логического элемента с тремя состояниями, выходная клемма первого логического элемента с тремя состояниями подключен к выходной клемме второго логического элемента “НЕ” и клемма второй контактной площадки, первая входная клемма второго логического элемента “И” подключена ко клемме первой контактной площадки и второй выходной клемме, вторая выходная клемма второго логического элемента “И” подключена к первой клемме блока регистров, а первая клемма второго резистора подключен ко клемме второй контактной площадки, вторая клемма второго резистора подключена к источнику питания постоянного тока, первая входная клемма второго логического элемента “ИЛИ “подключена к выходной клемме второго логического элемента “И”, входная клемма третьего логический элемент НЕ подключена к первому модулю однонаправленной прямой связи посредством внутренних узлов, а третья выходная клемма логического элемента “НЕ” подключена ко второй входной клемме второго логического элемента “ИЛИ”, входная клемма четвертого логического элемента “НЕ” подключена к выходной клемме второго логического элемента “ИЛИ”, входная клемма второго логического элемента с тремя состояниями; выходная клемма второго логического элемента с тремя состояниями подключена к выходной клемме четвертого логического элемента “НЕ” и клемме первой контактной площадки.

В частности, внутренние узлы первого модуля однонаправленной прямой связи и второго модуля однонаправленной прямой связи соединены таким образом: выходная клемма первого логического элемента “ИЛИ” подключена к входной клемме третьего логического элемента “НЕ”, выходная клемма второго логического элемента “ИЛИ” подключена к входной клемме первого логического элемента “НЕ”.

Способ однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками, включающий:

Когда между устройством внешней связи и другим чипом не должна быть создана двунаправленная связь, клемма первой контактной площадки и клемма второй контактной площадки используются как обычные клеммы контактной площадки, которые используются для передачи данных внутри чипа, включая ввод и вывод UART, I2C, GPIO и других сигналов; первый резистор R1 по умолчанию обеспечивает высокий уровень на клемме первой контактной площадки, второй резистор R2 обеспечивает высокий уровень на клемме второй контактной площадки, передача сигнала между первым модулем однонаправленной прямой связи 1 и вторым модулем однонаправленной прямой связи 2 не осуществляется.

Когда между устройством внешней связи и другим чипом должна быть создана двунаправленная связь, клемма первой контактной площадки подключается к устройству внешней связи, клемма второй контактной площадки подключается к другому чипу, в результате этого между первым модулем однонаправленной прямой связи 1 и вторым модулем однонаправленной прямой связи 2 образуется канал двунаправленной связи, двунаправленная прямая связь между внутричиповыми клеммами двух контактных площадок производится в соответствии со следующими этапами:

процессорный блок отправляет команду запуска режима двунаправленной прямой связи в блок связи и блок регистров в соответствии с протоколом связи; блок связи принимает команду запуска режима двунаправленной прямой связи и переключает первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи в режиме двунаправленной прямой связи, то есть передача и прием данных клеммы первой контактной площадки и клеммы второй контактной площадки производятся в соответствии с протоколом связи процессорного блока; блок регистров принимает команду запуска режима двунаправленной прямой связи, и первая выходная клемма блока регистров отправляет на первую управляющую клемму первый сигнал управления, который используется для управления переключением первого модуля однонаправленной прямой связи; вторая выходная клемма блока регистров отправляет на вторую управляющую клемму второй сигнал управления, который используется для управления переключением второго модуля однонаправленной прямой связи.

В соответствии с протоколом связи первый модуль односторонней прямой связи 1 и второй модуль однонаправленной прямой связи 2 переключают клемму первой контактной площадки и клемму второй контактной площадки в режим отправки или приема в соответствии с направлением передачи сигнала.

Когда клемма первой контактной площадки начинает отправлять сигнал первого уровня на клемму второй контактной площадки: на первую входную клемму и вторую выходную клемму второго логического элемента “И” поступает высокий уровень и выходятся сигнал высокого уровня; второй логический элемент “ИЛИ” выходит сигнал высокого уровня, на выходной клемме третьего логического элемента “НЕ” появляется низкий уровень.

Когда клемма второй контактной площадки начинает отправлять сигнал второго уровня на клемму первой контактной площадки: на первую входную клемму и вторую выходную клемму первого логического элемента “И” поступает высокий уровень и выходит сигнал высокого уровня; первый логический элемент “ИЛИ” выходит высокий уровень сигнал, выходная клемма первого логического элемента “НЕ” поддерживает низкий уровень.

Когда клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки: первая входная клемма первого модуля однонаправленной прямой связи принимает сигнал первого уровня, отправленный клеммой первой контактной площадки, вторая выходная клемма принимает первый сигнал управления, отправленный первой управляющей клеммой; вторая входная клемма второго модуля однонаправленной прямой связи принимает второй сигнал управления, отправленный второй управляющей клеммой, через первый модуль однонаправленной прямой связи клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки; в то же время сигнал первого уровня поддерживает режим отправки первого модуля однонаправленной прямой связи посредством соединительного отношения внутренних узлов прерывает выход сигнала от первой выходной клеммы первого модуля однонаправленной прямой связи; третий логический элемент “НЕ” выходит сигнал инвертированный сигнал первого уровня, а первая входная клемма второго логического элемента “И” принимает сигнал уровня сигнала первого уровня, второй логический элемент “ИЛИ” выходит сигнал высокого уровня, выходная клемма первого элемента “НЕ” и выходная клемма четвертого элемента “НЕ” поддерживают низкий уровень, а первый логический элемент “ИЛИ” продолжает выходить сигнал уровня сигнала первого уровня, выходная клемма второго логического элемента с тремя состояниями не выходит сигнал.

В частности, первый логический элемент “И”, его первая входная клемма принимает сигнал первого уровня, отправленный клеммой первой контактной площадки, его вторая выходная клемма принимает первый сигнал управления и сравнивает первый сигнал уровня с первым управляющим сигналом И, выходит сигнал первого уровня на первый логический элемент “ИЛИ”;

сигнал первого уровня и первый сигнал управления являются сигналами высокого уровня; первая входная клемма первого логического элемента “ИЛИ” принимает сигнал первого уровня, клемма второй контактной площадки по умолчанию обеспечивает высокий уровень , посредством соединительного отношения внутренних узлов первого логического элемента “НЕ” выходит сигнал высокого уровня, первая выходная клемма логического элемента “ИЛИ” выходит сигнал первого уровня; Входная клемма второго логического элемента “НЕ” и входная клемма первого логического элемента с тремя состояниями принимают сигнал первого уровня, отправленный выходной клеммой первого логического элемента “ИЛИ” , второй логический элемент “НЕ” инвертирует сигнал первого уровня, выходная клемма второго логического элемента “НЕ” выходит сигнал инвертированный сигнал первого уровня на управляющую клемму первого логического элемента с тремя состояниями; Когда сигнал первого уровня является сигналом высокого уровня, на управляющей клемме первого логического элемента с тремя состояниями появляется сигнал низкого уровня, первый логический элемент с тремя состояниями закрыт, выходная клемма первого логического элемента с тремя состояниями не выходит сигнал высокого уровня, клемма второй контактной площадки используется для установки и увеличения сигнала высокого уровня с помощью второго резистора; Когда сигнал первого уровня является сигналом низкого уровня, управляющая клемма первого логического элемента с тремя состояниями обеспечивает сигнал высокого уровня, первый логический элемент с тремя состояниями открыт, выходная клемма первого логического элемента с тремя состояниями выходит сигнал низкого уровня, на клемме второй контактной площадки появляется сигнал низкого уровня.

Когда клемма второй контактной площадки отправляет сигнал первого уровня на клемму первой контактной площадки: первая входная клемма второго модуля однонаправленной прямой связи принимает сигнал второго уровня, отправленный клеммой второй контактной площадки, его вторая входная клемма принимает сигнал второй сигнал управления, отправленный второй управляющей клеммой; вторая выходная клемма первого модуля однонаправленной прямой связи принимает первый сигнал управления, отправленный первой управляющей клеммой; клемма второй контактной площадки отправляет сигнал второго уровня на клемму второй контактной площадки через второй модуль однонаправленной прямой связи; в то же время сигнал второго уровня поддерживает режим отправки второго модуля однонаправленной прямой связи посредством соединительного отношения внутренних узлов и прерывает выход сигнала от первой выходной клеммы первого модуля однонаправленной прямой связи; первый логический элемент “НЕ” выходит сигнал инвертированный сигнал первого уровня, первая входная клемма первого логического элемента “И” принимает сигнал первого уровня, первый логический элемент “ИЛИ” выходит сигнал высокого уровня, выходная клемма третьего логического элемента “НЕ” и выходная клемма второго логического элемента “НЕ” поддерживают низкий уровень, второй логический элемент “ИЛИ” продолжает выходить сигнал первого уровня, выходная клемма первого логического элемента с тремя состояниями не выходит сигнал.

В частности, первая входная клемма второго логического элемента “И” принимает сигнал второго уровня, отправленный клеммой второй контактной площадки, его вторая выходная клемма принимает второй сигнал управления и выполняет логическую операцию И сигнала второго уровня и второго сигнала управления и выходит сигнал второго уровня на второй логический элемент “ИЛИ”; сигнал второго уровня и второй сигнал управления являются сигналами высокого уровня; первая входная клемма второго логического элемента “ИЛИ” принимает сигнал второго уровня, на клемме первой контактной площадки по умолчанию появляется высокий уровень, посредством соединительного отношения внутренних узлов выходная клемма второго логического элемента “НЕ” выходит сигнал низкого уровня, в результате вторая выходная клемма логического элемента “ИЛИ” выходит сигнал первого уровня; входная клемма четвертого логического элемента “НЕ” и входная клемма второго логического элемента с тремя состояниями принимают сигнал второго уровня, отправленный выходной клеммой второго логического элемента “ИЛИ”, а четвертый логический элемент “НЕ” инвертирует сигнал второго уровня, выходной клемме четвертого логического элемента “НЕ” выходит инвертированный сигнал первого уровня на управляющую клемму второго логического элемента с тремя состояниями; когда сигнал второго уровня является сигналом высокого уровня, на управляющей клемме второго логического элемента с тремя состояниями появляется сигнал низкого уровня, второй логический элемент с тремя состояниями закрыт, выходная клемма второго логического элемента с тремя состояниями не выходит сигнал высокого уровня, клемма первой контактной площадки используется для установки и увеличения сигнала высокого уровня с помощью второго резистора; когда сигнал второго уровня является сигналом низкого уровня, на управляющей клемме второго логического элемента с тремя состояниями появляется сигнал высокого уровня, второй логический элемент с тремя состояниями открыт, на выходной клемме второго логического элемента с тремя состояниями появляется сигнал низкого уровня, на клемме первой контактной площадки появляется сигнал низкого уровня.

В этом примере осуществления:

Клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки, и сигнал первого уровня устанавливается как цифровой сигнал высокого уровня 1:когда первая управляющая клемма и вторая управляющая клемма устанавливают цифровой сигнал высокого уровня на 1, и выходной сигнал первого логического элемента “И” на 1, выходной сигнал первого логического элемента “ИЛИ” на 1, выходной сигнал второго логического элемента “НЕ” на 0, первый логический элемент с тремя состояниями на закрытое положение, высокий уровень на клемме второй контактной площадки с помощью второго резистора R2, сигнал установки второй контактной площадки на 1, передача завершена; при этом выходной сигнал третьего логического элемента “НЕ” установлен на 0, выходной сигнал второго логического элемента “И” на 1, выходной сигнал второго логического элемента “ИЛИ” на 1, выходной сигнал логического элемента “НЕ” на 0; выходной сигнал четвертого логического элемента “НЕ” на 0, второй логический элемент с тремя состояниями на закрытое положение, тем самым первая контактная площадка продолжает отправлять данные и вторая контактная площадка продолжает принимать данные.

Клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки, и сигнал первого уровня устанавливается как цифровой сигнал низкого уровня 1: когда первая управляющая клемма и вторая управляющая клемма устанавливают цифровой сигнал высокого уровня на 1, и выходной сигнал первого логического элемента “И” на 0, выходной сигнал первого логического элемента “ИЛИ” на 0, выходной сигнал второго логического элемента “НЕ” на 1, первый логический элемент с тремя состояниями на открытое положение, выходной сигнал первого логического элемента с тремя состояниями на 0, входной сигнал клеммы второй контактной площадки на 0; при этом выходной сигнал третьего логического элемента “НЕ” установлен на 1 выходной сигнал второго логического элемента “И” на 0, выходной сигнал второго логического элемента “ИЛИ” на 1, выходной сигнал первого логического элемента “НЕ” на 0; выходной сигнал четвертого логического элемента “НЕ” на 0, второй логический элемент с тремя состояниями на закрытое положение, тем самым первая контактная площадка продолжает отправлять данные и вторая контактная площадка продолжает принимать данные.

Клемма второй контактной площадки отправляет сигнал второго уровня на клемму первой контактной площадки в соответствии со способом однолинейной двунаправленной прямой связи, который аналогичен процессу отправки клеммой первой контактной площадки сигнала первого уровня на клемму второй контактной площадки. Сигнал первого уровня включает цифровой сигнал высокого уровня 1 и цифровой сигнал низкого уровня 0.

По настоящему изобретению первый модуль однонаправленной прямой связи 1 и второй модуль однонаправленной прямой связи 2 в чипе соединены посредством внутренних узлов, в результате этого образуется канал однолинейной двунаправленной прямой связи, передача сигнала между однонаправленной прямой связи 1 и второй модуль однонаправленной прямой связи 2. Передача сигнала между первым модулем однонаправленной прямой связи 1 и вторым модулем однонаправленной прямой связи 2 осуществляется в соответствии с протоколом связи процессорного блока. Переключение канала однолинейной двунаправленной прямой связи однонаправленной прямой связи 2 управляется с помощью блока регистров.

Во время двунаправленной прямой связи клемма первой контактной площадки и клемма второй контактной площадки будут осуществлять передачу сигнала в соответствии с протоколом связи, клеммы первой контактной площадки и второй площадки находятся в режиме отправки и приема сигнала; схема подключится к устройству внешней связи с помощью клеммы первой контактной площадки и подключится к другому чипу с помощью клеммы второй контактной площадки; когда связь между схемой и устройством внешней связи должна быть создана, клеммы двух контактных площадок используются для осуществления двунаправленной прямой связи; когда связь между схемой и устройством внешней связи не должна быть создана, они используются в качестве обычных клемм для передачи сигнала.

Вышеупомянутый пример осуществления является только предпочтительным примером осуществления настоящего изобретения, не должен использоваться для ограничения объема настоящего изобретения. Все изменения, эквивалентные замены, усовершенствования и т.п., не отступающие от сущности и замысла настоящего изобретения, попадают в объем его правовой защиты.

Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками и способ его создания, канал включает процессорный блок, блок связи, блок регистров, клемму первой контактной площадки и клемму второй контактной площадки, первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи; первый модуль однонаправленной прямой связи используется для однонаправленной передачи сигнала первого уровня от клеммы первой контактной площадки на клемму второй контактной площадки; второй модуль однонаправленной прямой связи используется для однонаправленной передачи сигнала второго уровня от клеммы второй контактной площадки на клемму первой контактной площадки; первый модуль однонаправленной прямой связи подключен к второму модулю однонаправленной прямой связи посредством внутренних узлов; внутричиповый процессорный блок отправляет команду запуска режима двунаправленной прямой связи в блок связи и блок регистров в соответствии с протоколом связи; блок связи принимает команду запуска режима двунаправленной прямой связи и переключает первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи в режим двунаправленной прямой связи, то есть передача данных и прием данных на клемме первой контактной площадки и на клемме второй контактной площадки производятся в соответствии с протоколом связи процессорного блока. 2 н. и 9 з.п. ф-лы, 1 ил.

1. Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками, включающий процессорный блок, блок связи, блок регистров, клемму первой контактной площадки и клемму второй контактной площадки, отличающийся тем, что он включает первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи;

причём первый модуль однонаправленной прямой связи предназначен для однонаправленной передачи сигнала первого уровня от клеммы первой контактной площадки на клемму второй контактной площадки, второй модуль однонаправленной прямой связи предназначен для однонаправленной передачи сигнала второго уровня от клеммы второй контактной площадки на клемму первой контактной площадки; первый модуль однонаправленной прямой связи подключен ко второму модулю однонаправленной прямой связи посредством внутренних узлов;

первый модуль однонаправленной прямой связи включает первую входную клемму, первую выходную клемму и первую управляющую клемму; второй модуль однонаправленной прямой связи включает вторую входную клемму, вторую выходную клемму и вторую управляющую клемму;

первая входная клемма подключена ко клемме первой контактной площадки и второй выходной клемме, вторая выходная клемма подключена к клемме второй контактной площадки и первой выходной клемме, первая управляющая клемма и вторая управляющая клемма подключены к блоку регистров.

2. Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п. 1, отличающийся тем, что процессорный блок подключен к блоку связи и блоку регистров соответственно;

процессорный блок выполнен с возможностью управления переключением блока связи и блока регистров во время двунаправленной связи, подключен к первому модулю однонаправленной прямой связи и второму модулю однонаправленной прямой связи посредством блока связи, подключен к первой управляющей клемме и второй управляющей клемме посредством блока регистров; первая клемма блока регистров подключена к первой управляющей клемме, вторая клемма подключена ко второй управляющей клемме.

3. Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п. 1, отличающийся тем, что первый модуль однонаправленной прямой связи включает первый логический элемент “И”, первый резистор, первый логический элемент “ИЛИ”, первый логический элемент “НЕ”, второй логический элемент “НЕ” и первый логический элемент с тремя состояниями;

первая входная клемма первого логического элемента “И” подключена к клемме первой площадки и второй выходной клемме, вторая выходная клемма подключена к первой клемме блока регистров;

первая клемма первого резистора подключена к клемме первой контактной площадки, вторая клемма подключена к источнику питания постоянного тока;

первая входная клемма первого логического элемента “ИЛИ” подключена к выходной клемме первого логического элемента “И”;

входная клемма первого логического элемента “НЕ” подключена ко второму модулю однонаправленной прямой связи посредством внутренних узлов, выходная клемма подключена ко второй входной клемме первого логического элемента “ИЛИ”;

входная клемма второго логического элемента “НЕ” подключена к выходной клемме первого логического элемента “ИЛИ” и входной клемме первого логического элемента с тремя состояниями;

выходная клемма первого логического элемента с тремя состояниями подключена к выходной клемме второго логического элемента “НЕ” и клемме второй контактной площадки.

4. Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п. 1, отличающийся тем, что второй модуль однонаправленной прямой связи включает второй логический элемент “И”, второй резистор, второй логический элемент “ИЛИ”, третий логический элемент “НЕ”, четвертый логический элемент “НЕ” и второй логический элемент с тремя состояниями;

первая входная клемма второго логического элемента “И” подключена к клемме первой контактной площадки и второй выходной клемме, его вторая выходная клемма подключена к первой клемме блока регистров;

первая клемма второго резистора подключена к клемме второй контактной площадки, вторая клемма подключена к источнику питания постоянного тока;

первая входная клемма второго логического элемента “ИЛИ” подключена к выходной клемме второго логического элемента “И”;

входная клемма третьего логического элемента “НЕ” подключена к первому модулю однонаправленной прямой связи посредством внутренних узлов, выходная клемма подключена ко второй входной клемме второго логического элемента “ИЛИ”;

входная клемма четвертого логического элемента “НЕ” подключена к выходной клемме второго логического элемента “ИЛИ” и входной клемме второго логического элемента с тремя состояниями;

выходная клемма второго логического элемента с тремя состояниями подключена к выходной клемме четвертого логического элемента “НЕ” и клемме первой контактной площадки.

5. Канал однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по любому из пп. 3-4, отличающийся тем, что внутренние узлы первого модуля однонаправленной прямой связи и второго модуля однонаправленной прямой связи соединены следующим образом: выходная клемма первого логического элемента “ИЛИ” подключена к входной клемме третьего логического элемента “НЕ”, выходная клемма второго логического элемента “ИЛИ” подключена к входной клемме первого логического элемента “НЕ”.

6. Способ создания однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками, отличающийся тем, что однолинейная двунаправленная прямая связь между внутричиповыми контактными площадками с использованием канала по любому из пп. 1-5 производится следующим образом:

внутричиповый процессорный блок отправляет команду запуска режима двунаправленной прямой связи в блок связи и блок регистров в соответствии с протоколом связи;

блок связи принимает команду запуска режима двунаправленной прямой связи и переключает первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи в режим прямой двунаправленной связи, то есть передача данных и прием данных на клемме первой контактной площадки и на клемме второй контактной площадки производятся в соответствии с протоколом связи процессорного блока;

блок регистров принимает команду запуска режима двунаправленной прямой связи, и первая выходная клемма блока регистров отправляет первый сигнал управления на первую управляющую клемму, причём первый сигнал управления предназначен для управления переключением первого модуля однонаправленной прямой связи, вторая выходная клемма блока регистров отправляет второй сигнал управления на вторую управляющую клемму, причём второй сигнал управления предназначен для управления переключением второго модуля однонаправленной прямой связи.

7. Способ создания однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п. 6, отличающийся тем, что двунаправленную прямую связь между внутричиповыми клеммами двух контактных площадок обеспечивают в соответствии со следующими этапами:

первый модуль однонаправленной прямой связи и второй модуль однонаправленной прямой связи в соответствии с протоколом связи переключают клемму первой контактной площадки и клемму второй контактной площадки в режим отправки или приема в соответствии с направлением передачи сигнала;

когда клемма первой контактной площадки находится в режиме отправки, клемма второй контактной площадки находится в режиме приема: первая входная клемма первого модуля однонаправленной прямой связи принимает сигнал первого уровня, отправленный клеммой первой контактной площадки, его вторая выходная клемма принимает первый сигнал управления, отправленный первой управляющей клеммой; вторая выходная клемма второго модуля однонаправленной прямой связи принимает второй сигнал управления, отправленный второй управляющей клеммой; клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки через первый модуль однонаправленной прямой связи; одновременно сигнал первого уровня поддерживает режим отправки первого модуля однонаправленной прямой связи посредством соединительного отношения внутренних узлов и прерывает выход сигнала от первой выходной клеммы второго модуля однонаправленной прямой связи;

когда клемма второй контактной площадки находится в режиме отправки, клемма первой контактной площадки находится в режиме приема: первая входная клемма второго модуля однонаправленной прямой связи принимает сигнал второго уровня, отправленный клеммой второй контактной площадки, его вторая выходная клемма принимает второй сигнал управления, отправленный второй управляющей клеммой; вторая выходная клемма первого модуля однонаправленной прямой связи принимает первый сигнал управления, отправленный первой управляющей клеммой; клемма второй контактной площадки отправляет сигнал второго уровня на клемму второй контактной площадки посредством второго модуля однонаправленной прямой связи; одновременно сигнал второго уровня поддерживает режим отправки второго модуля однонаправленной прямой связи посредством соединительного отношения внутренних узлов и прерывает выход сигнала от первой выходной клеммы первого модуля однонаправленной прямой связи.

8. Способ создания однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п. 7, отличающийся тем, что, когда клемма первой контактной площадки находится в режиме отправки, клемма второй контактной площадки находится в режиме приема:

первая входная клемма первого логического элемента “И” принимает сигнал первого уровня, отправленный клеммой первой контактной площадки, его вторая выходная клемма принимает первый сигнал управления, и выполняет логическую операцию И сигнала первого уровня и первого сигнала управления, и выводит первый сигнал уровня на первый логический элемент “ИЛИ”, при этом сигнал первого уровня и первый сигнал управления являются сигналами высокого уровня;

первая входная клемма первого логического элемента “ИЛИ” принимает сигнал первого уровня, клемма второй контактной площадки по умолчанию обеспечивает высокий уровень, выходная клемма первого логического элемента “НЕ” выводит сигнал высокого уровня посредством соединительного отношения внутренних узлов, в результате этого первая выходная клемма логического элемента “ИЛИ” выводит сигнал первого уровня;

входная клемма второго логического элемента “НЕ” и входная клемма первого логического элемента с тремя состояниями принимают сигнал первого уровня, отправленный выходной клеммой первого логического элемента “ИЛИ”, второй логический элемент “НЕ” инвертирует сигнал первого уровня, выходная клемма второго логического элемента “НЕ” выводит инвертированный сигнал первого уровня на управляющую клемму первого логического элемента с тремя состояниями;

когда сигнал первого уровня представляет собой сигнал высокого уровня, на управляющей клемме первого логического элемента с тремя состояниями появляется сигнал низкого уровня, первый логический элемент с тремя состояниями закрыт, выходная клемма первого логического элемента с тремя состояниями не выводит сигнал высокого уровня, а клемма второй контактной площадки используется для установки и увеличения сигнала высокого уровня с помощью второго резистора;

когда сигнал первого уровня представляет собой сигнал низкого уровня, на управляющей клемме первого логического элемента с тремя состояниями обеспечивается сигнал высокого уровня, первый логический элемент с тремя состояниями открыт, выходная клемма первого логического элемента с тремя состояниями выводит сигнал низкого уровня, на клемме второй контактной площадки появляется сигнал низкого уровня.

9. Способ создания однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п. 7, отличающийся тем, что, когда клемма второй контактной площадки находится в режиме отправки, клемма первой контактной площадки находится в режиме приема:

первая входная клемма второго логического элемента “И” принимает сигнал второго уровня, отправленный клеммой второй контактной площадки, его вторая выходная клемма принимает второй сигнал управления, и выполняет логическую операцию И сигнала второго уровня и второго сигнала управления, и выводит сигнал второго уровня на второй логический элемент “ИЛИ”, при этом сигнал второго уровня и второй сигнал управления являются сигналами высокого уровня;

первая входная клемма второго логического элемента “ИЛИ” принимает сигнал второго уровня, на клемме первой контактной площадки по умолчанию появляется высокий уровень, посредством соединительного отношения внутренних узлов выходная клемма второго логического элемента “НЕ” выводит сигнал низкого уровня, в результате чего вторая выходная клемма логического элемента “ИЛИ” выводит сигнал первого уровня;

входная клемма четвертого логического элемента “НЕ” и входная клемма второго логического элемента с тремя состояниями принимают сигнал второго уровня, отправленный выходной клеммой второго логического элемента “ИЛИ”, а четвертый логический элемент “НЕ” инвертирует сигнал второго уровня, выходная клемма четвертого логического элемента “НЕ” выводит инвертированный сигнал первого уровня на управляющую клемму второго логического элемента с тремя состояниями, когда сигнал второго уровня представляет собой сигнал высокого уровня, на управляющей клемме второго логического элемента с тремя состояниями появляется сигнал низкого уровня, второй логический элемент с тремя состояниями закрыт, выходная клемма второго логического элемента с тремя состояниями не выводит сигнал высокого уровня, клемма первой контактной площадки используется для установки и увеличения сигнала высокого уровня с помощью второго резистора;

когда сигнал второго уровня представляет собой сигнал низкого уровня, на управляющей клемме второго логического элемента с тремя состояниями появляется сигнал высокого уровня, второй логический элемент с тремя состояниями открыт, на выходной клемме второго логического элемента с тремя состояниями появляется сигнал низкого уровня, на клемме первой контактной площадки появляется сигнал низкого уровня.

10. Способ создания однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п.8 или 9, отличающийся тем, что:

когда клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки, второй логический элемент “И” обеспечивает высокий уровень на первой выходной клемме и второй выходной клемме, выводит сигнал высокого уровня;

когда клемма первой контактной площадки отправляет сигнал первого уровня на клемму второй контактной площадки, третий логический элемент “НЕ” выводит инвертированный сигнал первого уровня, а первая входная клемма второго логического элемента “И” принимает сигнал первого уровня, второй логический элемент “ИЛИ” выводит сигнал высокого уровня, выходная клемма первого элемента “НЕ” и выходная клемма четвертого элемента “НЕ” поддерживают низкий уровень, первый логический элемент “ИЛИ” продолжает выводить сигнал первого уровня, а выходная клемма второго логического элемента с тремя состояниями не выводит сигнал.

11. Способ создания однолинейной двунаправленной прямой связи между внутричиповыми контактными площадками по п.8 или 9, отличающийся тем, что:

когда клемма второй контактной площадки отправляет сигнал второго уровня на клемму первой контактной площадки, первый логический элемент “И” обеспечивает высокий уровень на первой входной клемме и второй входной клемме, выводит сигнал высокого уровня; логический элемент “ИЛИ” выводит сигнал высокого уровня, на выходной клемме первого логического элемента “НЕ” появляется низкий уровень;

когда клемма второй контактной площадки отправляет сигнал первого уровня на клемму первой контактной площадки, первый логический элемент “НЕ” выводит инвертированный сигнал первого уровня, а первая входная клемма первого логического элемента “И” принимает сигнал первого уровня, первый логический элемент “ИЛИ” выводит сигнал высокого уровня, выходная клемма третьего логического элемента “НЕ” и выходная клемма второго логического элемента “НЕ” поддерживают низкий уровень, второй логический элемент “ИЛИ” продолжает выводить сигнал первого уровня, а выходная клемма первого логического элемента с тремя состояниями не выводит сигнал.

| УСТРОЙСТВО КОНТРОЛЯ АМПЛИТУДНОЙ АСИММЕТРИИ НАПРЯЖЕНИЙ | 2014 |

|

RU2561505C1 |

| УСТРОЙСТВО ДЛЯ ОТБРАКОВКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 2001 |

|

RU2187126C1 |

| МНОГОПОЗИЦИОННОЕ УСТРОЙСТВО ПЕРЕКЛЮЧЕНИЯ ИСТОЧНИКА ТОКА | 2013 |

|

RU2623494C2 |

| KR 1020050062675 A, 27.06.2005 | |||

| JP 6720532 B2, 08.07.2020 | |||

| CN 103384268 B, 24.08.2016 | |||

| CN 110245048 A, 17.09.2019. | |||

Авторы

Даты

2023-12-01—Публикация

2023-06-15—Подача