Область техники

Предлагаемое изобретение относится к области электротехники и может найти свое практическое применение в различных областях промышленности, где необходимо использование стабильных источников питания нагрузки постоянного напряжения.

Уровень техники

Получение стабильных во времени по своей величине напряжения и тока является важным условием для качественной, безопасной и долговременной работы различного оборудования, например, источников светодиодного освещения или аккумуляторных батарей, заряжаемых от таких источников.

Например, в простейшем случае получение стабилизированного тока на выходе схемы, например, для питания светодиодов, может быть обеспечено последовательным включением источника питания и резистора, имеющего высокое сопротивление. Несмотря на простоту исполнения, такое решение имеет недостатки в виде необходимости использования высоковольтного источника питания, а также, вследствие потерь мощности, которая рассеивается на высокоомном сопротивлении, низкого КПД.

Отмеченные недостатки могут быть устранены в импульсных стабилизаторах, например, таком, который известен из патентного документа US 8179110 B2, 15.05.2012 [1]. Однако в известном из [1] решении, вследствие наличия режима коммутации катушки индуктивности, неизбежны пульсации выходного тока, кроме того, для управления ключевым элементом предложено использование интегральных микросхем, что существенно усложняет конструкцию устройства и снижает надежность его работы.

Также известно решение по патентному документу RU 1155 U1, 16.11.1995 [2], лишенное недостатков отмеченного выше [1]. Данное решение основано на использовании двухполупериодного выпрямителя, на входе которого формируется двухполупериодное пульсирующее напряжение положительной полярности. При напряжении на базе первого транзистора, меньше, чем напряжение его открывания, первый транзистор заперт, т.е. напряжение на его коллекторе повторяет форму напряжения на выходе выпрямителя. Это напряжение с коллектора первого транзистора подается на базу второго транзистора, включенного по схеме эмиттерного повторителя. С эмиттера второго транзистора напряжение, по величине и форме совпадающее с напряжением на его базе, проходит через диод и заряжает выходной конденсатор. В установленных интервалах времени напряжение на базе первого транзистора превышает напряжение его открывания. В результате первый транзистор открывается и напряжение на его коллекторе резко падает, что ведет к уменьшению напряжения на эмиттере второго транзистора, приводящее к запиранию диода. Далее оба процесса периодически повторяются.

В то же время, решение по документу [2] не обеспечивает защиту ключевых элементов от перегрузки, а так же не предусматривает возможность регулирования напряжения на основании его выходного значения.

Предлагаемое изобретение направлено на преодоление недостатков предшествующего уровня техники, а также позволяет обеспечить достижение технических результатов, заключающихся в повышении быстродействия, снижении выходного сопротивления в широкой полосе частот, обеспечение масштабируемости схемы в широком диапазоне напряжений, возможность использования низковольтных ключевых элементов, имеющих лучшие характеристики по сравнению с высоковольтными, защиту управляющего элемента от случайного пробоя.

Раскрытие изобретения

Для достижения указанных выше технических результатов предложен стабилизатор напряжения, содержащий источник тока, отрицательный вывод которого соединен с положительным выводом источника входного напряжения и со стоком MOSFET транзистора, а положительный вывод которого соединен с затвором MOSFET транзистора, с катодом стабилитрона, а также с коллектором первого npn-транзистора и первым выводом первого конденсатора, второй вывод которого соединен с базой первого npn-транзистора, коллектором второго npn-транзистора и коллектором первого pnp-транзистора, анод стабилитрона соединен с истоком MOSFET транзистора, первым выводом первого резистора, который соединен с положительным выводом источника опорного напряжения, соединенным с первым выводом четвертого резистора, который соединен с первым выводом второго конденсатора, отрицательный вывод источника входного напряжения соединен с эмиттером первого npn-транзистора, соединенным с первым выводом второго резистора, который соединен с первым выводом третьего резистора, соединенного с первым выводом пятого резистора, имеющего соединение со вторым выводом второго конденсатора и с общим проводом, второй вывод первого резистора соединен с эмиттерами первого и второго pnp-транзисторов, второй вывод второго резистора соединен с эмиттером второго npn-транзистора, второй вывод третьего резистора соединен с эмиттером третьего npn-транзистора, база первого pnp-транзистора одновременно соединена со вторыми выводами четвертого и пятого резисторов, база второго npn-транзистора соединена с базой третьего npn-транзистора, а также, совместно с коллектором второго pnp-транзистора – с коллектором третьего npn-транзистора, отрицательный вывод источника опорного напряжения соединен с базой второго pnp-транзистора.

В дополнительном варианте осуществления изобретения источник входного напряжения содержит добавочный источник питания источника тока.

Далее в описании показаны варианты осуществления изобретения с подтверждением возможности достижения технического результата.

Осуществление изобретения

Для более полного понимания сущности изобретения в описании приведены отсылки на поясняющие чертежи, согласно которым представлены:

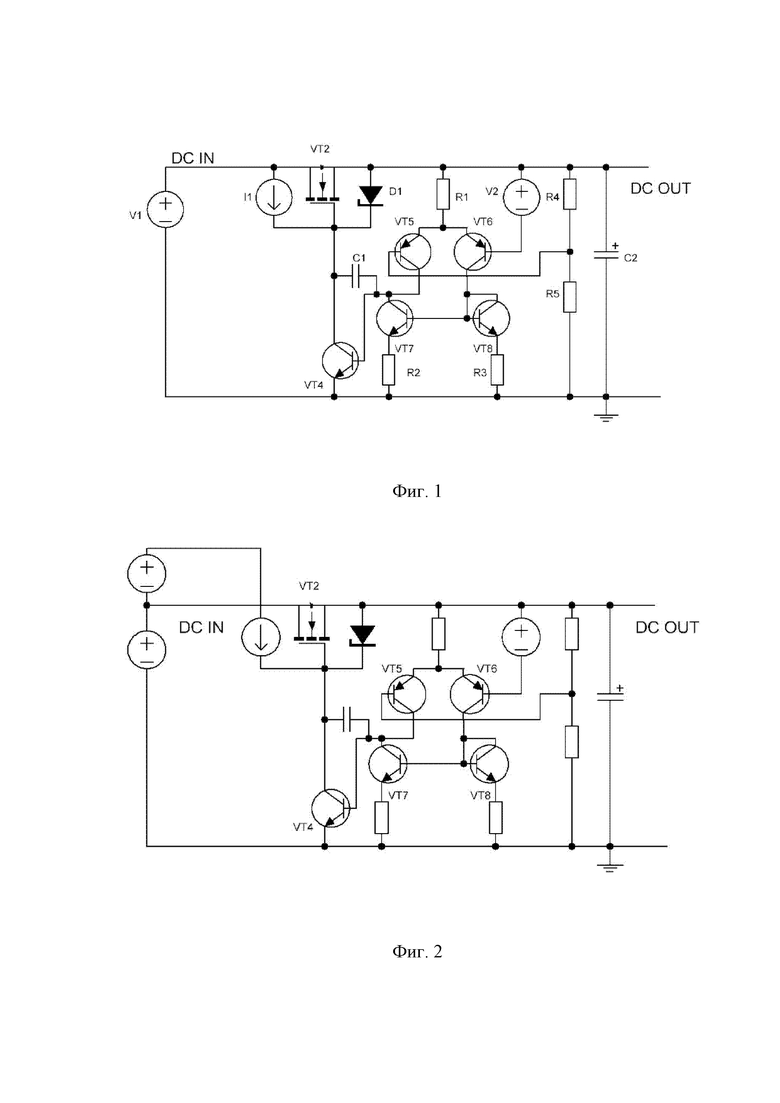

Фиг.1 – основная структурная схема предлагаемого изобретения.

Фиг. 2 – схема изобретения в дополнительном варианте осуществления.

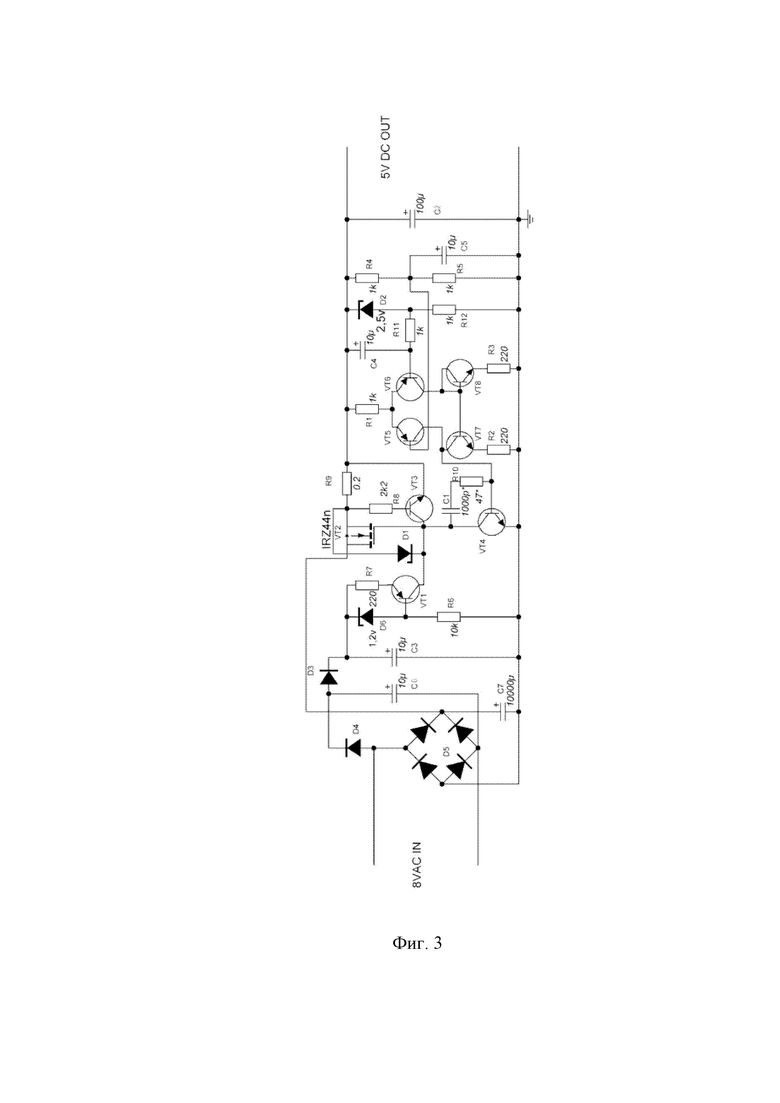

Фиг. 3 – схема варианта осуществления изобретения.

Как следует из сведений, представленных на фиг. 1, сущность предлагаемого изобретения заключается в совместном использовании полевого (MOSFET) транзистора и схемы управления, выполненной на основе дифференциального каскада, нагруженного на так называемое «токовое зеркало».

Для приведения в соответствие признаков формулы и условных обозначений, представленных на фигурах, необходимо отметить, что под первым npn-транзистором понимается транзистор VT4, под вторым npn-транзистором понимается транзистор VT7, под третьим npn-транзистором понимается транзистор VT8, под первым pnp-транзистором понимается транзистор VT5, под вторым pnp-транзистором понимается транзистор VT6.

Изобретение работает следующим образом.

Источник тока I1 подаёт ток в цепь, питающую затвор полевого транзистора VT2, этот транзистор начинает открываться и на выходе появляется напряжение, вследствие чего у схемы управления появляется питание, и она начинает работать.

Схема управления выполнена на основе дифференциального каскада на транзисторах VT5 VT6, нагруженного на «токовое зеркало» на транзисторах VT7 VT8 и резисторах R2 и R3. Каскад VT5-VT6 питается через резистор R1. Вход, образованный базой транзистора VT6, является неинвертирующим, а у транзистора VT5 - инвертирующий. На неинвертирующий вход подается опорное напряжение (V2), а на инвертирующий – напряжение обратной связи. Необходимо отметить, что все напряжения схема измеряет относительно плюса питания, а не относительно "общего" провода.

Сигнал рассогласования поступает с коллектора транзистора VT5 на транзистор VT4 и таким образом усиливается. Весь ток источника I1 стекает в транзистор VT4, и управляет потенциалом на затворе транзистора VT2. При росте напряжения на резисторе R4 выше, чем опорное напряжение источника V2, напряжение на затворе VT2 уменьшается, а напряжение на выходе схемы снижается. В противном случае, при снижении напряжения на резисторе R4, транзистор VT4 увеличивает напряжение на затворе VT2, приоткрывая его, что увеличивает напряжение на выходе схемы.

Конденсатор C1 обеспечивает частотную коррекцию каскада на транзисторе VT4, что обеспечивает стабильность работы схемы. Кроме того, конденсатор C2 использован как для стабильности работы схемы, так и для снижения ее выходного сопротивления на высоких частотах.

В предложенном изобретении стабилитрон D1 защищает затвор полевого транзистора VT2 от случайного пробоя.

Использование предложенной схемы позволяет обеспечить минимально возможное количество каскадов усиления и получить от схемы высокое быстродействие и низкое выходное сопротивление в широкой полосе частот.

Использование полевого транзистора в качестве регулирующего элемента позволяет (при добавлении добавочного источника питания входного источника тока, как показано на фиг. 2) получать минимальное падение на схеме в единицы-десятки милливольт при токах в несколько ампер.

В развивающем варианте осуществления изобретения, как показано на фиг. 3, на диодном мосту D5 собран выпрямитель, напряжение с которого сглаживает конденсатор C7.

На диодах D4 D3 и конденсаторах C6 и C3 собран удвоитель напряжения, чтобы запитать управляющую затвором транзистора VT2 цепь более высоким напряжением чем, поступает на сток этого транзистора. Это нужно для того, чтобы обеспечить напряжения на затворе VT2 как минимум на 5...6 В выше чем на его стоке, т.к. это необходимо для его полного отпирания в случае, когда разница напряжений между входом и выходом схемы становится слишком маленькой (например, для полного отпирания полевого транзистора IRFZ44n нужно, чтобы напряжение на его затворе было на 4 В выше, чем на его истоке).

Источник тока для работы каскада на транзисторе VT4 и отпирания VT2 собран на транзисторе VT1, резисторах R6 R7, и стабилитроне D6 (в частном варианте осуществления, может быть заменен на два маломощных кремниевых диода, включенных в прямом включении). В рассматриваемом случае этот источник тока выдает ток около 3 мА.

Опорное напряжение формирует стабилитрон D2 (можно использовать микросхемы источников опорного напряжения, например TL431), запитанный через резистор R12. Резистор R11 и конденсатор C4 формируют фильтр низких частот, и полученное малошумящее опорное напряжение подаётся на базу транзистора VT6.

Напряжение отрицательной обратной связи (ООС) формируется резисторами R4 R5, а конденсатор C5 на высоких частотах шунтирует R5, увеличивая глубину ООС на высоких частотах. Это напряжение подается на базу транзистора VT5. При росте напряжения на базе VT5 больше, чем подано на VT6 сигнал рассогласования подается на базу транзистора VT4, который снижает напряжение на затворе VT2, а при снижении напряжения ООС он увеличивает напряжение на затворе VT2, таким образом удерживая напряжение в заданных рамках.

Конденсатор C1 и резистор R10 обеспечивают частотную коррекцию схемы.

Транзистор VT3 формирует цепь защиты от перегрузки по току - при превышении тока примерно в 3 А на резисторе R9 напряжение вырастает выше чем 0,6...0,7 В, и это напряжение подается через резистор R8 на базу транзистора VT3, после чего он открывается, и резко снижает напряжение на затворе регулирующего транзистора VT2, что снижает напряжение на выходе схемы вплоть до нуля.

Важно отметить, что входы схемы сравнения привязаны к плюсу питания, что позволяет масштабировать ее на очень широкий диапазон напряжений, вплоть до сотен вольт.

Ограничение питания самой схемы управления позволяет использовать низковольтные транзисторы с высокими параметрами, по сравнению с высоковольтными транзисторами.

При практическом осуществлении изобретения, увеличивая количество полевых транзисторов, включенных в параллель, был собран источник напряжения 12 В с током более 40 А.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРОСТАТИЧЕСКИХ ПОТЕНЦИАЛОВ | 1993 |

|

RU2083990C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ СИЛЫ ТОКА | 1990 |

|

RU2007612C1 |

| ИСТОЧНИК ЭЛЕКТРИЧЕСКОГО СИГНАЛА, ПРОПОРЦИОНАЛЬНОГО АБСОЛЮТНОЙ ТЕМПЕРАТУРЕ | 1993 |

|

RU2115099C1 |

| Преобразователь постоянного напряжения в постоянное | 1990 |

|

SU1809513A1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2002 |

|

RU2298282C2 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2018 |

|

RU2683502C1 |

| Устройство управления газоразрядной индикаторной панелью | 1989 |

|

SU1709388A1 |

| МНОГОКАНАЛЬНЫЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2821422C1 |

| ЭЛЕКТРОННЫЙ ПРЕДОХРАНИТЕЛЬ | 2009 |

|

RU2398335C1 |

| ДОПЛЕРОВСКИЙ РАДИОВОЛНОВОЙ ИЗВЕЩАТЕЛЬ С ИСПОЛНИТЕЛЬНЫМ УСТРОЙСТВОМ ДЛЯ ОХРАННОЙ ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 2012 |

|

RU2529544C2 |

Изобретение относится к области электротехники. Технический результат заключается в повышении быстродействия, снижении выходного сопротивления в широкой полосе частот, защите управляющего элемента от случайного пробоя. Стабилизатор напряжения содержит источник тока, отрицательный вывод которого соединен с положительным выводом источника входного напряжения и со стоком MOSFET транзистора, а положительный вывод которого соединен с затвором MOSFET транзистора, с катодом стабилитрона, а также с коллектором первого npn-транзистора и первым выводом первого конденсатора, второй вывод которого соединен с базой первого npn-транзистора, коллектором второго npn-транзистора и коллектором первого pnp-транзистора. Анод стабилитрона соединен с истоком MOSFET транзистора, первым выводом первого резистора, который соединен с положительным выводом источника опорного напряжения, соединенным с первым выводом четвертого резистора, который соединен с первым выводом второго конденсатора. Отрицательный вывод источника входного напряжения соединен с эмиттером первого npn-транзистора, соединенным с первым выводом второго резистора, который соединен с первым выводом третьего резистора, соединенного с первым выводом пятого резистора, имеющего соединение со вторым выводом второго конденсатора и с общим проводом. Второй вывод первого резистора соединен с эмиттерами первого и второго pnp-транзисторов. Второй вывод второго резистора соединен с эмиттером второго npn-транзистора. Второй вывод третьего резистора соединен с эмиттером третьего npn-транзистора. База первого pnp-транзистора одновременно соединена со вторыми выводами четвертого и пятого резисторов. База второго npn-транзистора соединена с базой третьего npn-транзистора, а также совместно с коллектором второго pnp-транзистора – с коллектором третьего npn-транзистора. Отрицательный вывод источника опорного напряжения соединен с базой второго pnp-транзистора. 1 з.п. ф-лы, 3 ил.

1. Стабилизатор напряжения, содержащий источник тока, отрицательный вывод которого соединен с положительным выводом источника входного напряжения и со стоком MOSFET транзистора, а положительный вывод которого соединен с затвором MOSFET транзистора, с катодом стабилитрона, а также с коллектором первого npn-транзистора и первым выводом первого конденсатора, второй вывод которого соединен с базой первого npn-транзистора, коллектором второго npn-транзистора и коллектором первого pnp-транзистора, анод стабилитрона соединен с истоком MOSFET транзистора, первым выводом первого резистора, который соединен с положительным выводом источника опорного напряжения, соединенным с первым выводом четвертого резистора, который соединен с первым выводом второго конденсатора, отрицательный вывод источника входного напряжения соединен с эмиттером первого npn-транзистора, соединенным с первым выводом второго резистора, который соединен с первым выводом третьего резистора, соединенного с первым выводом пятого резистора, имеющего соединение со вторым выводом второго конденсатора и с общим проводом, второй вывод первого резистора соединен с эмиттерами первого и второго pnp-транзисторов, второй вывод второго резистора соединен с эмиттером второго npn-транзистора, второй вывод третьего резистора соединен с эмиттером третьего npn-транзистора, база первого pnp-транзистора одновременно соединена со вторыми выводами четвертого и пятого резисторов, база второго npn-транзистора соединена с базой третьего npn-транзистора, а также совместно с коллектором второго pnp-транзистора – с коллектором третьего npn-транзистора, отрицательный вывод источника опорного напряжения соединен с базой второго pnp-транзистора.

2. Стабилизатор напряжения по п. 1, отличающийся тем, что источник входного напряжения содержит добавочный источник питания источника тока.

| US 2020272184 A1, 27.08.2020 | |||

| US 10073476 B2, 11.09.2018 | |||

| US 6104179 A, 15.08.2000 | |||

| 1972 |

|

SU415652A1 | |

| Стабилизатор постоянного напряжения | 1977 |

|

SU838673A1 |

Авторы

Даты

2024-01-11—Публикация

2023-07-17—Подача