Изобретение относится к вычислительной технике и может применяться на этапе приемочных испытаний устройств ввода/вывода автоматизированных систем управления специализированного назначения.

Известен способ построения вычислительного процесса испытаний аппаратуры с мультиинтерфейсным взаимодействием, используя диагностические тесты, заключающийся в том, что вычислительный процесс выполняет аппаратура контроля, а именно, формирует диагностические тесты, производит вычислительный процесс испытаний и отправляет пакеты данных на устройство ввода/вывода транзитом через многофункциональный крейт, в состав которого входят модули обмена по соответствующему приборному интерфейсу и управляющее ими вычислительное устройство, которое содержит программное обеспечение, реализующее обмен между аппаратурой контроля и устройством ввода/вывода, а обмен информацией от аппаратуры контроля с устройством ввода/вывода осуществляется по определенным алгоритмам (Патент RU 2716389 С1 «Способ построения вычислительного процесса испытаний аппаратуры с мультиинтерфейсным взаимодействием»). В рассмотренном способе в качестве транзитного устройства используется многофункциональный крейт, в состав которого входят модули обмена по соответствующему приборному интерфейсу и управляющее ими вычислительное устройство. Транзитное устройство выполняет обмен данными между аппаратурой контроля и устройствами ввода/вывода. Нарушения обмена между транзитным устройством и устройствами ввода/вывода может значительно увеличить время испытаний. При чтении информации понять о нарушении обмена можно по полученным данным от устройств ввода/вывода и провести косвенную оценку с целью выявления причин нарушения обмена. При записи информации результаты обмена не доступны для аппаратуры контроля.

К недостаткам такого способа нужно отнести снижение надежности средств испытаний за счет реализации функций диагностики обмена по приборному интерфейсу средствами аппаратуры контроля, а также отсутствие оперативного контроля и своевременной реакции на ошибки обмена со стороны транзитного устройства.

Известен способ построения вычислительного процесса испытаний электронных устройств ввода/вывода с диагностикой обмена (патент RU 2750109 С1), который отличается от способа построения вычислительного процесса испытаний аппаратуры с мультиинтерфейсным взаимодействием (патент RU 2716389 С1) тем, что транзитное устройство проводит диагностику обмена с устройством ввода/вывода по критерию результата обмена - положительный или отрицательный. При отрицательном результате обмена транзитное устройство повторяет обмен несколько раз или выполняет диагностический обмен в различных режимах и формирует диагностическую информацию, включающую общий признак отрицательного результата обмена, тип отрицательного результата обмена - по характеру ошибки обмена, и признак уровня взаимодействия - транспортный или информационный. Положительным результатом обмена считают отсутствие признака отрицательного результата обмена.

Учитывая тот факт, что сроки проведения испытаний всегда ограничены, перед специалистами-испытателями стоит задача поиска путей минимизации затрат материальных, трудовых и временных ресурсов для достижения цели испытания. Поэтому при проведении испытаний необходимо учитывать два противоречивых требования: обеспечение максимальной достоверности обобщенной оценки качества устройств ввода/вывода и выполнение испытания в ограниченное время.

Недостатком способа построения вычислительного процесса испытаний электронных устройств ввода/вывода с диагностикой обмена является недостаточный уровень функциональности испытаний, ввиду отсутствия возможности определения момента остановки испытаний устройств ввода/вывода, что приводит к увеличению продолжительности испытаний.

Технической задачей заявляемого изобретения является определение момента остановки испытаний на основе полученных статистических данных о работе устройств ввода/вывода.

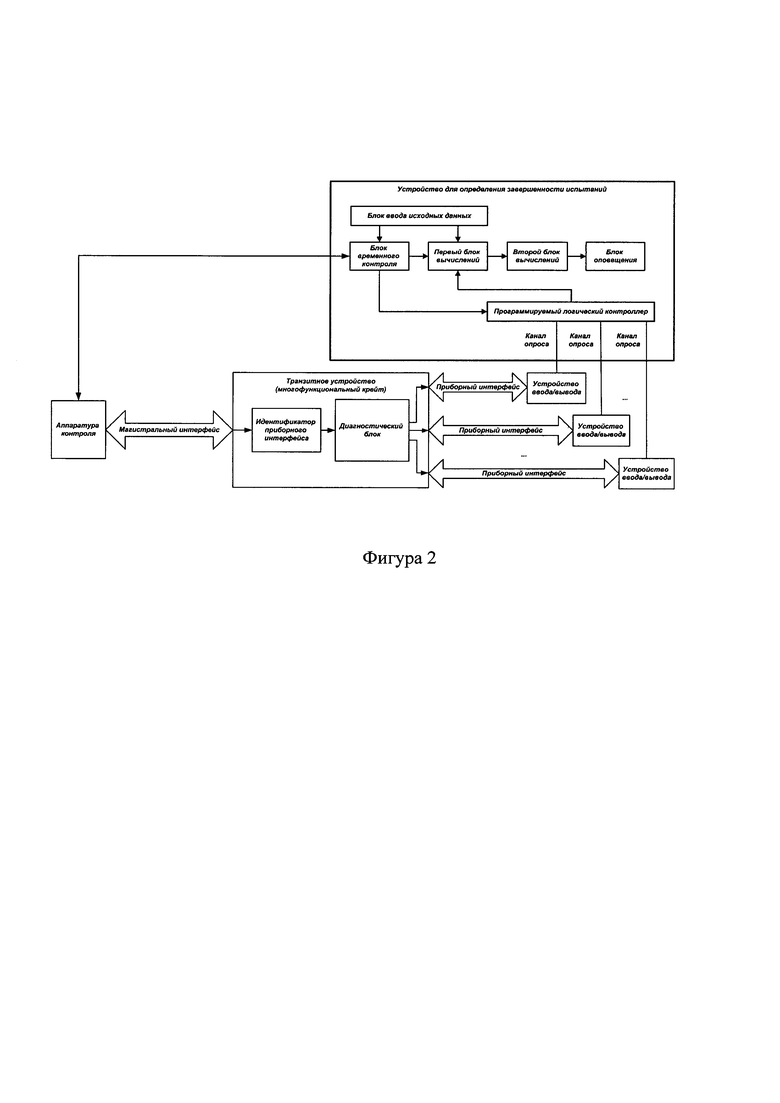

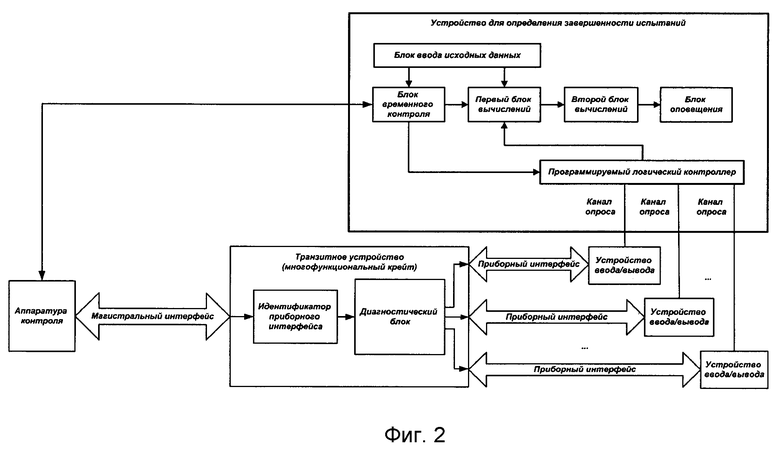

Решение технической задачи достигается за счет того, что устройство для определения завершенности испытаний содержит блок ввода исходных данных, блок временного контроля, первый блок вычислений, второй блок вычислений, программируемый логический контроллер, каналы опроса устройств ввода/вывода, блок оповещения, причем первый выход блока ввода исходных данных соединен со вторым входом блока временного контроля, первый информационный вход-выход которого является входом устройства, а второй выход блока временного контроля соединен с первым входом программируемого логического контроллера, который соединен с тестируемыми устройствами ввода/вывода при помощи каналов опроса, причем первый выход программируемого логического контроллера соединен с третьим входом первого блока вычислений, первый вход которого соединен с третьим выходом блока временного контроля, а второй вход соединен со вторым выходом блока ввода исходных данных, а первый выход соединен с первым входом второго блока вычислений, первый выход которого соединен с первым входом блока оповещения.

Технический результат, достигаемый указанной совокупностью признаков, заключается в возможности определения момента остановки (завершения) испытаний устройств ввода/вывода автоматизированных систем управления специализированного назначения.

Устройство для определения завершенности испытаний устройств ввода/вывода автоматизированных систем управления имеет взаимное соединение с аппаратурой контроля и испытываемыми устройствами ввода/вывода, на основе решающих правил нечеткого логического вывода определяет численное значение показателя завершенности испытаний, по которому делается вывод о том, что либо испытания можно остановить (завершить) или необходимо их продолжить. Поскольку АСУ функционирует, используя программное обеспечение, то предлагается формировать показатель завершенности испытаний устройств ввода/вывода на основе анализа и обработки статистических данных о работе таких средств.

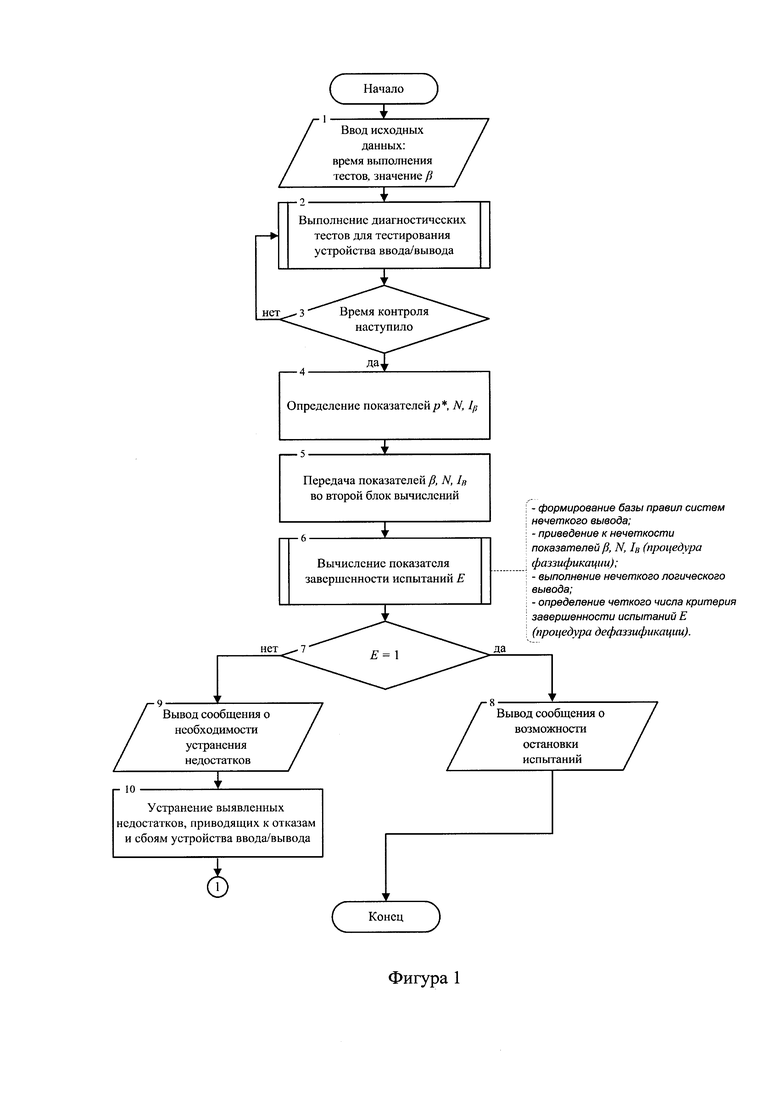

Процесс вычисления показателя завершенности испытаний (фиг. 1) состоит в непрерывном опросе состояния устройства ввода/вывода при выполнении диагностических тестов. Полученные в процессе тестирования устройства ввода/вывода, статистические данные фиксируются и обрабатываются устройством для определения завершенности испытаний для принятия решения об окончании (завершении) или продолжении испытаний.

Для проведения анализа и определения момента окончания испытаний используются три показателя [1]:

- точность оценки среднего времени наработки на отказ β;

- число аппаратных отказов за период проведения испытаний N;

- вероятность отказов и сбоев устройства ввода/вывода Iβ. Показатель β задается перед началом испытаний специалистами-испытателями, которые учитывают требования устойчивости к отказам и сбоям, и вводится в устройство для определения завершенности испытаний.

Показатель N фиксируется устройством для определения завершенности испытаний.

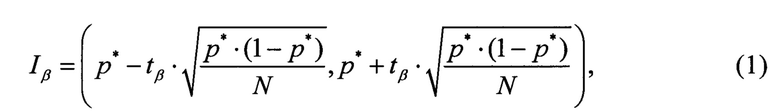

Показатель Iβ рассчитывается устройством для определения завершенности испытаний по формуле:

где р* - частота отказов и сбоев, tβ - число средних квадратических отклонений, которое нужно отложить вправо и влево от центра рассеивания среднего времени наработки на отказ; N - число аппаратных отказов устройства ввода/вывода.

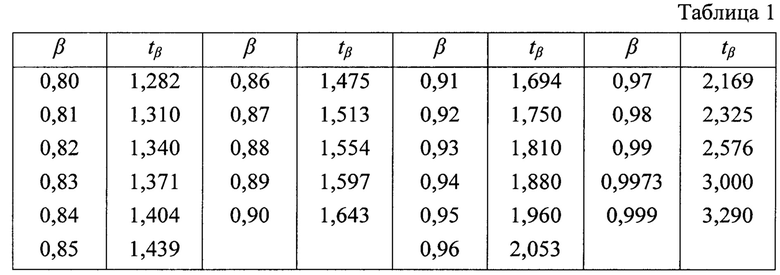

Значение величины tβ для выбранного параметра β приводится в таблице 1, согласно [1]:

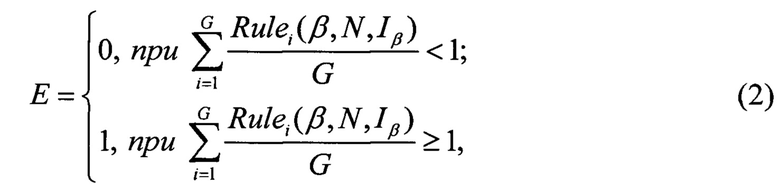

На основании выбранного специалистами-испытателями значения показателя β и полученных значений показателей N, Iβ, устройство для определения завершенности испытаний с запущенным алгоритмом нечеткого логического вывода вычисляет показатель завершенности испытаний Е по формуле:

где G - количество продукционных правил алгоритма нечеткого логического вывода;  (β, N, Iβ) - результат вычисления показателя завершенности испытания в соответствии с i-м продукционным правилом нечеткого вывода.

(β, N, Iβ) - результат вычисления показателя завершенности испытания в соответствии с i-м продукционным правилом нечеткого вывода.

В случае получения значения Е=0, испытания прерываются для устранения выявленных недостатков, приводящих к отказам и сбоям устройства ввода/вывода. В случае получения значения Е=1, выполненный объем тестирования считается достаточным для остановки (завершения) испытаний устройства ввода/вывода.

Сущность изобретения поясняется схемой (фиг. 2). На фиг. 2 представлена функциональная схема организации единой информационно-логической связи аппаратуры контроля, транзитного устройства, устройств ввода/вывода и устройства для определения завершенности испытаний.

В процессе работы с первого выхода блока ввода исходных данных на второй вход блока временного контроля поступает информация о продолжительности выполнения диагностических тестов для тестирования устройства ввода/вывода. На второй вход первого блока вычислений со второго выхода блока ввода исходных данных поступает значение точности оценки среднего времени наработки на отказ β.

В момент начала выполнения диагностических тестов от аппаратуры контроля на вход устройства для определения завершенности испытаний, являющийся первым информационным входом-выходом блока временного контроля поступает сигнал о времени начала выполнения диагностических тестов, который инициирует процесс контроля продолжительности выполнения диагностических тестов. Блок временного контроля со второго выхода выдает на первый вход ПЛК сигнал о необходимости непрерывного опроса состояния устройства ввода/вывода через канал опроса состояния устройства ввода/вывода и осуществляет контроль продолжительности выполнения диагностических тестов.

При возникновении аппаратных отказов ПЛК по каналу опроса состояния устройства ввода/вывода считывает данные с устройства ввода/вывода. Статистические данные (число аппаратных отказов N, частота отказов и сбоев р*), полученные ПЛК в процессе тестирования устройства ввода/вывода передаются с первого выхода ПЛК на третий вход первого блока вычислений. При выполнении диагностических тестов заданной продолжительности блок временного контроля с первого информационного входа-выхода посылает сигнал в аппаратуру контроля о приостановке выполнения диагностических тестов. Одновременно с третьего выхода блока временного контроля на первый вход первого блока вычислений передается управляющий сигнал о необходимости вычисления значения вероятности отказов и сбоев устройства ввода/вывода Iβ.

Первый блок вычислений определяет значение вероятности отказов и сбоев устройства ввода/вывода Iβ и с первого выхода передает на первый вход второго блока вычислений значения следующих показателей: точности оценки среднего времени наработки на отказ β, число аппаратных отказов N, вероятность отказов и сбоев устройства ввода/вывода Iβ.

Второй блок вычислений с запущенным алгоритмом нечеткого логического вывода, согласно [2], получив значения показателей β, N, Iр выполняет расчет показателя завершенности испытаний. После чего, результат вычисления с первого выхода второго блока вычислений поступает на первый вход блока оповещения. Также, во втором блоке вычислений предусмотрен механизм формирования базы продукционных правил систем нечеткого вывода. Блок оповещения на основе полученного значения показателя Е формирует информационное сообщение о том, что, либо испытания можно остановить (завершить) или необходимо их продолжить.

Реализация устройства для определения завершенности испытаний не вызывает затруднений, так как все блоки, а именно: блок ввода исходных данных, блок временного контроля, первый блок вычислений, второй блок вычислений, блок оповещения, входящие в состав устройства для определения завершенности испытаний, общеизвестны и широко описаны в технической литературе [3-8].

В частности, первый блок вычислений, второй блок вычислений, могут быть реализованы в виде специализированных изделий на микроконтроллере по методам и алгоритмам, описанным в [2, 9-11]. ПЛК может быть выполнен согласно техническому решению, изложенному в патенте на изобретение RU №2749103.

Взаимное соединение всех составных частей устройства для определения завершенности испытаний может быть осуществлено по стандартным схемам подключения устройств [12].

Соединение устройства для определения завершенности испытаний с аппаратурой контроля и испытываемыми устройствами ввода/вывода может быть осуществлено по стандартным схемам подключения устройств [13].

Сведения, раскрывающие возможность реализации предлагаемого изобретения представлены в источниках информации [1-13], опубликованных до даты приоритета этой заявки и содержащего эти сведения.

Источники информации.

1. Вентцель Е. С. Теория вероятностей / Е.С. Вентцель. - М.: Наука, 1969. - 576 с.

2. Zadeh L.A. Fuzzy sets // Information and Control, 1965, vol. 8. Pp. 338-353.

3. Нечаев И.А. Конструкции на логических элементах цифровых микросхем. - М.: Радио и связь, 1992. - 123 с.

4. Белов А.В. Создаем устройства на микроконтроллерах. - СПб.: Наука и техника, 2007. - 304 с.

5. Конструкторско-технологическое проектирование электронной аппаратуры. Учебник для вузов. Серия: Информатика в техническом университете / Под ред. Шахнова В.А. - М.: Изд-во МГТУ им. Н.Э.Баумана, 2003. - 528 с.

6. Суворова Е., Шейнин Ю. Проектирование цифровых систем на VHDL. Серия «Учебное пособие». - СПб.: БХВ-Петербург, 2003. - 576 с.

7. Овчинников В.А. Алгоритмизация комбинаторно-оптимизационных задач при проектировании ЭВМ и систем. Серия: Информатика в техническом университете. - М.: Изд-во МГТУ им. Н.Э. Баумана, 2001. - 288 с.

8. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. - М.: Мир, 2001. - 379 с.

9. Денисова Л.А. Модели и методы проектирования систем управления объектами с переменными параметрами: монография / Л.А. Денисова; Ом. гос. техн. университет.- Омск: Изд-во ОмГТУ, 2014. - 167 с.

10. Леоненков А.В. Нечеткое моделирование в среде MATLAB и fuzzyTECH. - СПб.: БХВ Петербург, 2005. - 736 с.

Дьяконов В.П. MATLAB 7. */R2006/R2007: самоучитель / В.П. Дьяконов. - М: ДМК Пресс, 2008. - 768 с.

12. Сопряжение датчиков и устройств ввода данных с компьютерами IBM PC: Пер. с англ./ Под ред. У. Томпкинса, Дж. Уэбстера. - М.: Мир, 1992. - 592 с.

13. Пей Ан. Сопряжение ПК с внешними устройствами. - М.: ДМК Пресс, 2003. - 320 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИСПЫТАНИЙ УСТРОЙСТВ ВВОДА/ВЫВОДА АВТОМАТИЗИРОВАННЫХ СИСТЕМ УПРАВЛЕНИЯ | 2023 |

|

RU2811382C1 |

| ИНТЕРФЕЙС ИНФОРМАЦИОННОГО ВЗАИМОДЕЙСТВИЯ СИСТЕМЫ ПОДДЕРЖКИ ПРИНЯТИЯ РЕШЕНИЙ С ИНФОРМАЦИОННО-АНАЛИТИЧЕСКИМ ФОНДОМ | 2022 |

|

RU2795368C1 |

| СПОСОБ ПОСТРОЕНИЯ ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА ИСПЫТАНИЙ ЭЛЕКТРОННЫХ УСТРОЙСТВ ВВОДА/ВЫВОДА С ДИАГНОСТИКОЙ ОБМЕНА | 2020 |

|

RU2750109C1 |

| СПОСОБ ОБЕСПЕЧЕНИЯ ИНФОРМАЦИОННОГО ВЗАИМОДЕЙСТВИЯ АППАРАТУРЫ ПРИ ТЕСТИРОВАНИИ УСТРОЙСТВ ВВОДА-ВЫВОДА | 2022 |

|

RU2789824C1 |

| СПОСОБ ФОРМИРОВАНИЯ 4-КАНАЛЬНОЙ ОТКАЗОУСТОЙЧИВОЙ СИСТЕМЫ БОРТОВОГО КОМПЛЕКСА УПРАВЛЕНИЯ ПОВЫШЕННОЙ ЖИВУЧЕСТИ И ЭФФЕКТИВНОГО ЭНЕРГОПОТРЕБЛЕНИЯ И ЕГО РЕАЛИЗАЦИЯ ДЛЯ КОСМИЧЕСКИХ ПРИМЕНЕНИЙ | 2011 |

|

RU2449352C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| СИСТЕМА ОХРАННО-ПОЖАРНОЙ СИГНАЛИЗАЦИИ | 2001 |

|

RU2216783C2 |

| СПОСОБ ОБЕСПЕЧЕНИЯ АСИНХРОННОГО ВЗАИМОДЕЙСТВИЯ АППАРАТУРЫ ПРИ ТЕСТИРОВАНИИ УСТРОЙСТВ ВВОДА-ВЫВОДА | 2023 |

|

RU2809047C1 |

| СПОСОБ ОБЕСПЕЧЕНИЯ МАКРОФУНКЦИОНАЛЬНОГО УПРАВЛЕНИЯ ПРИ ТЕСТИРОВАНИИ ЭЛЕКТРОННЫХ УСТРОЙСТВ ВВОДА-ВЫВОДА | 2024 |

|

RU2824053C1 |

| СПОСОБ ПОСТРОЕНИЯ ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА ИСПЫТАНИЙ АППАРАТУРЫ С МУЛЬТИИНТЕРФЕЙСНЫМ ВЗАИМОДЕЙСТВИЕМ | 2019 |

|

RU2716389C1 |

Изобретение относится к вычислительной технике и может быть использовано для приемочных испытаний устройств ввода/вывода автоматизированных систем управления. Техническим результатом является сокращение продолжительности испытаний устройств ввода/вывода за счет определения времени завершения испытаний. Устройство содержит блок ввода исходных данных, блок временного контроля, первый блок вычислений, второй блок вычислений, программируемый логический контроллер, каналы опроса устройств ввода/вывода, блок оповещения. 2 ил., 1 табл.

Устройство для определения завершенности испытаний устройств ввода/вывода автоматизированных систем управления, характеризующееся тем, что содержит блок ввода исходных данных, блок временного контроля, первый блок вычислений, второй блок вычислений, программируемый логический контроллер, каналы опроса устройств ввода/вывода, блок оповещения, причем первый выход блока ввода исходных данных соединен со вторым входом блока временного контроля, первый информационный вход-выход которого является входом устройства, а второй выход блока временного контроля соединен с первым входом программируемого логического контроллера, который соединен с тестируемыми устройствами ввода/вывода при помощи каналов опроса, причем первый выход программируемого логического контроллера соединен с третьим входом первого блока вычислений, первый вход которого соединен с третьим выходом блока временного контроля, а второй вход соединен со вторым выходом блока ввода исходных данных, а первый выход соединен с первым входом второго блока вычислений, первый выход которого соединен с первым входом блока оповещения.

| СПОСОБ ОБЕСПЕЧЕНИЯ ИНФОРМАЦИОННОГО ВЗАИМОДЕЙСТВИЯ АППАРАТУРЫ ПРИ ТЕСТИРОВАНИИ УСТРОЙСТВ ВВОДА-ВЫВОДА | 2022 |

|

RU2789824C1 |

| СПОСОБ ПОСТРОЕНИЯ ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА ИСПЫТАНИЙ ЭЛЕКТРОННЫХ УСТРОЙСТВ ВВОДА/ВЫВОДА С ДИАГНОСТИКОЙ ОБМЕНА | 2020 |

|

RU2750109C1 |

| СПОСОБ ПОСТРОЕНИЯ ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА ИСПЫТАНИЙ АППАРАТУРЫ С МУЛЬТИИНТЕРФЕЙСНЫМ ВЗАИМОДЕЙСТВИЕМ | 2019 |

|

RU2716389C1 |

| СПОСОБ ПОСТРОЕНИЯ ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА ИСПЫТАНИЙ АППАРАТУРЫ | 2011 |

|

RU2480807C2 |

| WO 2012174281 A1, 20.12.2012 | |||

| US 20170115344 A1, 27.04.2017 | |||

| US 6282681 B1, 28.08.2001. | |||

Авторы

Даты

2024-01-11—Публикация

2023-05-12—Подача