Изобретение относится к вычислительной технике, а именно к способу построения вычислительного процесса испытаний электронных устройств, имеющих в своем составе вычислительный модуль.

Известен способ построения вычислительного процесса испытаний электронных устройств в процессе производства, используя диагностические тесты, заключающийся в том, что вычислительный процесс испытаний электронных устройств реализуется в вычислительном модуле, а аппаратура контроля осуществляет его индикацию и управление. («Тестопригодный блок управления и процедуры его тестирования» / В.Б.БРОДИН, А.В.КАЛИНИН. - Научная сессия МИФИ-2007. Т.1 Автоматика. Микроэлектроника. Электроника. Электронные измерительные системы. Компьютерные медицинские системы, стр.94-96).

Известный способ работает следующим образом: при тестировании плат, в вычислительный модуль через инструментальный последовательный порт вводятся входные векторы (диагностические тесты), на основании которых вычислительный модуль формирует пакет по приборному интерфейсу в микроконтроллер устройства ввода/вывода, который собственно и задает сигналы на выходных линиях блока электронного устройства.

Однако этот способ может быть усовершенствован путем перемещения вычислительного процесса, реализующего диагностические тесты, на аппаратуру контроля и организации обмена с устройством ввода/вывода транзитом через вычислительный модуль.

Известный способ по технической сущности является наиболее близким к предлагаемому и выбран в качестве прототипа.

Недостатком прототипа является:

- недостаточная эффективность контроля выполняемых операций, данных обмена и состояний устройств ввода/вывода;

- переход между диагностическими тестами связан с перепрограммированием вычислительного устройства по инструментальному последовательному порту.

- написание диагностических тестов осуществляется в специальной среде разработки программ для вычислительного модуля.

Целью изобретения является:

- минимизация времени проведения испытаний и трудозатрат;

- упрощение процедур управления, контроля, анализа и обработки информации в ходе испытаний;

Поставленная цель достигается тем, что вычислительный процесс, реализуемый вычислительным модулем, выполняется в аппаратуре контроля, осуществляя обмен с устройством ввода/вывода транзитом через вычислительный модуль.

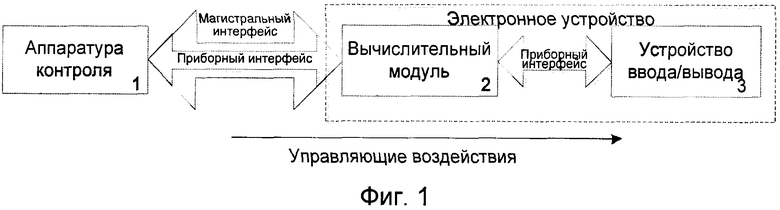

На чертеже (фиг.1) представлена функциональная схема организации единой информационно-логической связи аппаратуры контроля и устройств ввода/вывода, которая обеспечивает полный доступ вычислительного процесса, реализуемого на аппаратуре контроля, к устройствам ввода/вывода.

Аппаратура контроля подключается к вычислительному устройству с помощью протокола магистрального интерфейса. Вычислительное устройство подключается к устройству ввода/вывода по приборному интерфейсу.

Аппаратура контроля содержит программное обеспечение, осуществляющее вычислительный процесс испытаний.

Вычислительный модуль содержит универсальное программное обеспечение, реализующее поддержку единой информационно-логической связи аппаратуры контроля и устройств ввода/вывода для осуществления их двухстороннего обмена информацией.

Способ организуется следующим образом.

Вычислительный процесс испытаний, выполняющий диагностические тесты, реализуется в едином программном обеспечении, на аппаратуре контроля.

В ходе выполнения диагностических тестов происходит формирование пакетов в формате протокола приборного интерфейса, предназначенных непосредственно для устройства ввода/вывода. Для каждого из пакетов в формате протокола приборного интерфейса формируется определенное количество пакетов в формате протокола магистрального интерфейса предназначенных для передачи их в вычислительный модуль.

Количество пакетов магистрального интерфейса F, составляемое из пакета приборного интерфейса, определяется по следующей формуле:

F = (округление в меньшую сторону ((h·(N-1))/(k·(M+1))))+1

N - максимальное количество информационных слов данных (ИСД) по протоколу магистрального интерфейса;

М - требуемое количество ИСД по протоколу приборного интерфейса;

h - разрядность информационных слов данных по протоколу магистрального интерфейса;

k - разрядность информационных слов данных по протоколу приборного интерфейса.

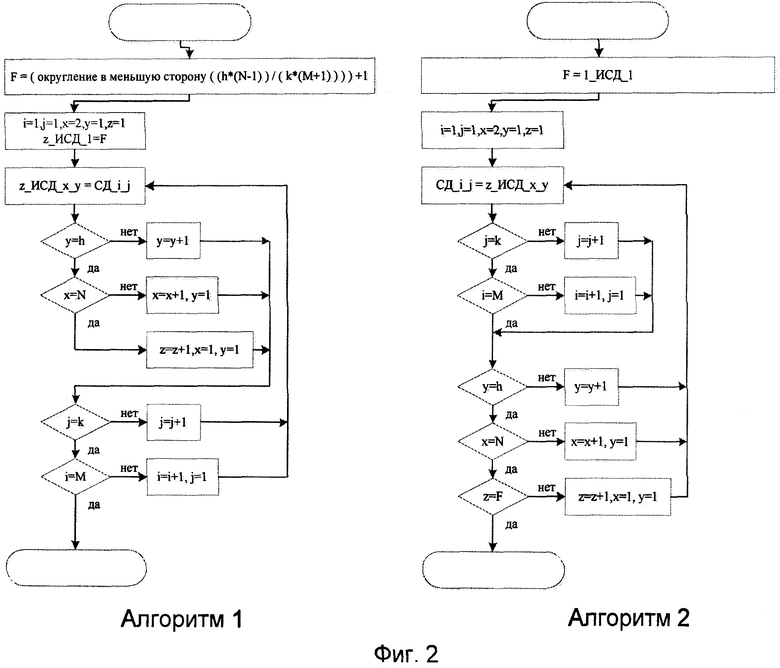

Формула используется в алгоритмах 1 и 2 фиг.2, где

i - номер ИСД по протоколу магистрального интерфейса (от 1 до N);

j - номер разряда ИСД по протоколу магистрального интерфейса (от 1 до h);

x - номер ИСД по протоколу приборного интерфейса (от 1 до М);

y - номер разряда ИСД по протоколу приборного интерфейса (от 1 до k);

z - номер посылки по протоколу магистрального интерфейса (от 1 до F).

Запись информации от аппаратуры контроля в устройство ввода/вывода реализуется путем формирования аппаратурой контроля пакета в формате протокола приборного интерфейса с признаком записи информации, из которого формируется F пакетов в формате протокола магистрального интерфейса по алгоритму 1 (фиг.2), которые передаются в вычислительный модуль. По получению F пакетов, вычислительный модуль формирует пакет в формате протокола приборного интерфейса по алгоритму 2 (фиг.2) и передает его в устройство ввода/вывода.

Чтение информации аппаратурой контроля от устройства ввода/вывода реализуется путем формирования аппаратурой контроля пакета в формате протокола приборного интерфейса с признаком чтения информации, из которого формируется 1 пакет в формате протокола магистрального интерфейса по алгоритму 1 (фиг.2), который передается в вычислительный модуль. По получению пакета, вычислительный модуль формирует пакет в формате протокола приборного интерфейса по алгоритму 2 (фиг.2) и передает его в устройство ввода/вывода, считывая информацию, которая, считывается аппаратурой контроля от вычислительного модуля, через время, определяемое как максимальное время обмена между вычислительным модулем и устройством ввода/вывода.

Минимизация времени и трудозатрат происходит за счет того, что отпадает необходимость перепрограммировать вычислительный модуль при переходе между диагностическими тестами. А их создание осуществляется в интерфейсе программного обеспечения аппаратуры контроля, без использования специальных сред программирования. Упрощение процедур управления, контроля, анализа и обработки информации достигается за счет использования единого программного интерфейса аппаратуры контроля, имеющего полный доступ к вычислительному процессу и осуществляющего его управление.

Способ был опробован на рабочем месте, состоящем из промышленного компьютера ROBO-4000-5163A, выступающего в роли аппаратуры контроля; блока управления бортового комплекса управления КА «Глонасс-К», выступающего в роли электронного устройства, содержащего центральный приборный модуль, выступающий в роли вычислительного модуля, и интерфейсных модулей сопряжения, выступающих в роли устройств ввода/вывода.

Из известных заявителю патентно-информационных материалов не обнаружены признаки, сходные с совокупностью признаков заявляемого способа.

Изобретение относится к способу организации вычислительного процесса испытаний электронных устройств, имеющих в своем составе вычислительный модуль. Техническим результатом является минимизация времени проведения испытаний и трудозатрат, упрощение процедур управления, контроля, анализа и обработки информации в ходе испытаний. При тестировании электронных устройств формируют диагностические тесты. Исполняя тесты, реализуют вычислительный процесс испытаний и формируют пакеты данных в устройство ввода/вывода. Устройство ввода/вывода формирует сигналы на выходах; аппаратура контроля осуществляет индикацию и управление вычислительным процессом. Вычислительный процесс выполняет аппаратура контроля, а именно, формирует диагностические тесты, производит вычислительный процесс испытаний и отправляет пакеты данных на устройство ввода/вывода транзитом через вычислительный модуль, который содержит программное обеспечение, реализующее обмен между аппаратурой контроля и устройством ввода/вывода. Запись информации от аппаратуры контроля в устройство ввода/вывода реализуется путем формирования аппаратурой контроля пакета в формате протокола приборного интерфейса с признаком записи информации, из которого формируется F-пакетов в формате протокола магистрального интерфейса, которые передаются в вычислительный модуль, который по получению F-пакетов формирует пакет в формате протокола приборного интерфейса и передает его в устройство ввода/вывода, осуществляя запись информации. 2 ил.

Способ построения вычислительного процесса испытаний аппаратуры, заключающийся в том, что при тестировании электронных устройств формируют диагностические тесты; исполняя тесты, реализуют вычислительный процесс испытаний и формируют пакеты данных в устройство ввода/вывода; устройство ввода/вывода формирует сигналы на выходах; аппаратура контроля осуществляет индикацию и управление вычислительным процессом, отличающийся тем, что вычислительный процесс выполняет аппаратура контроля, а именно формирует диагностические тесты, производит вычислительный процесс испытаний и отправляет пакеты данных на устройство ввода/вывода транзитом через вычислительный модуль, который содержит программное обеспечение, реализующее обмен между аппаратурой контроля и устройством ввода/вывода; запись информации от аппаратуры контроля в устройство ввода/вывода реализуется путем формирования аппаратурой контроля пакета в формате протокола приборного интерфейса с признаком записи информации, из которого формируется F-пакетов в формате протокола магистрального интерфейса, которые передаются в вычислительный модуль, который по получению F-пакетов формирует пакет в формате протокола приборного интерфейса и передает его в устройство ввода/вывода, осуществляя запись информации; чтение информации аппаратурой контроля от устройства ввода/вывода реализуется путем формирования аппаратурой контроля пакета в формате протокола приборного интерфейса с признаком чтения информации, из которой формируется 1 пакет в формате протокола магистрального интерфейса, который передается в вычислительный модуль, который по получению пакета формирует пакет в формате протокола приборного интерфейса и передает его в устройство ввода/вывода, осуществляя чтение информации, которая считывается аппаратурой контроля от вычислительного модуля, через время, определяемое как максимальное время обмена между вычислительным модулем и устройством ввода/вывода.

| КОНТРОЛЬНЫЙ ПРОЦЕССОР С ИНФОРМАЦИОННЫМ РЕЗЕРВИРОВАНИЕМ | 1999 |

|

RU2159457C1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| КОНТРОЛЬНЫЙ ПРОЦЕССОР С ИНФОРМАЦИОННЫМ РЕЗЕРВИРОВАНИЕМ | 1999 |

|

RU2159457C1 |

| Станция управления приводом машин, снабженных технологическими контактами | 1952 |

|

SU98601A1 |

Авторы

Даты

2013-04-27—Публикация

2011-07-08—Подача