ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

[0001] Настоящее раскрытие испрашивает приоритет по китайской патентной заявке 202110746053.8 под названием «ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ», поданной 1 июля 2021 г., которая полностью включена в настоящий документ посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

[0002] Настоящее раскрытие относится, без ограничения, к полупроводниковой структуре и способу ее изготовления.

УРОВЕНЬ ТЕХНИКИ

[0003] По мере повышения степени интеграции полупроводниковых устройств специалисты в соответствующей области техники начинают уделять все больше внимания изучению того, каким образом расположить транзисторы в полупроводниковых структурах и уменьшить размеры отдельных функциональных устройств в полупроводниковых структурах.

[0004] В предшествующем уровне техники ячейки памяти динамической памяти с произвольным доступом (dynamic random access memory, DRAM) на основе транзисторов с седловидными ребрами занимают площадь 6F2 (F: минимальный размер рисунка, доступный при конкретных условиях процесса). В случае дополнительного уменьшения занимаемой площади DRAM, при пропорциональном масштабировании DRAM возникает такая проблема, как эффект близости затвора, которая будет негативно влиять на электрические характеристики DRAM. Если в качестве входных транзисторов используются транзисторы с круговым затвором (gate-all-around, GAA), то площадь, занимаемая транзисторами с круговым затвором, может достигать 4F2. В принципе, может быть достигнута более высокая плотность, но имеют место такие проблемы, как трудности с травлением линии слов, или числовой шины, (word line) в пределах некоторых диапазонов размеров из-за ограничений оборудования, используемого в производственном процессе, и самого производственного процесса.

РАСКРЫТИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0005] Ниже представлен обзор объекта, подробно описанного в настоящем раскрытии, причем данный обзор не предназначен для ограничения объема защиты формулы изобретения.

[0006] В вариантах осуществления настоящего раскрытия предложены полупроводниковая структура и способ ее изготовления, которые полезны для упрощения формирования числовых шин и получения числовых шин и полупроводниковых каналов малого размера с высокой точностью.

[0007] Согласно первому аспекту вариантов осуществления настоящего раскрытия, предложен способ изготовления полупроводниковой структуры, включающий в себя: обеспечение основы; формирование линий битов, или разрядных шин, (bit line) на основе и формирование полупроводниковых каналов на поверхностях линий битов, удаленных от основы, таким образом, чтобы полупроводниковый канал включал в себя первую область легирования, канальную область и вторую область легирования, последовательно расположенные вдоль направления от основы к линии битов; формирование первого диэлектрического слоя таким образом, чтобы первый диэлектрический слой окружал боковые стенки полупроводниковых каналов, причем между участками первого диэлектрического слоя, расположенными на боковых стенках соседних полупроводниковых каналов на одной и той же линии битов, обеспечен первый зазор; формирование второго диэлектрического слоя таким образом, чтобы второй диэлектрический слой заполнял первые зазоры, причем материал второго диэлектрического слоя отличается от материала первого диэлектрического слоя; удаление участка первого диэлектрического слоя для открытия боковых стенок канальных областей; формирование изолирующего слоя таким образом, чтобы изолирующий слой покрывал по меньшей мере поверхности боковых стенок канальных областей, и между изолирующим слоем и вторым диэлектрическим слоем были обеспечены вторые зазоры; и формирование числовых шин таким образом, чтобы числовые шины заполняли вторые зазоры.

[0008] Согласно второму аспекту вариантов осуществления настоящего раскрытия, предложена полупроводниковая структура, включающая в себя: основу; линии битов, расположенные на основе; полупроводниковые каналы, расположенные на поверхностях линий битов, причем полупроводниковый канал включает в себя первую область легирования, канальную область и вторую область легирования, последовательно расположенные вдоль направления от основы к линии битов, и первая область легирования находится в контакте с линией битов; первый диэлектрический слой, окружающий первые области легирования, причем между участками первого диэлектрического слоя, покрывающими боковые стенки соседних первых областей легирования на одной и той же линии битов, обеспечен первый зазор; изолирующий слой, покрывающий по меньшей мере поверхности боковых стенок канальных областей; числовые шины, окружающие изолирующий слой, расположенный на боковых стенках канальных областей, причем между соседними числовыми шинами обеспечен второй зазор; и изоляционный слой, расположенный по меньшей мере в первых зазорах и вторых зазорах, причем верхняя поверхность изоляционного слоя, удаленная от основы, расположена не ниже, чем верхняя поверхность второй области легирования, удаленная от основы.

[0009] Другие аспекты настоящего раскрытия станут понятными после прочтения и уяснения чертежей и раздела «Осуществление изобретения».

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0010] Сопроводительные чертежи, включенные в настоящее описание и образующие часть описания, иллюстрируют варианты осуществления настоящего раскрытия и используются вместе с настоящим описанием для объяснения принципов вариантов осуществления настоящего раскрытия. На этих сопроводительных чертежах аналогичные ссылочные номера используются для представления аналогичных элементов. Сопроводительные чертежи в нижеследующем описании относятся к части вариантов осуществления настоящего раскрытия, а не ко всем из них. Специалисты в данной области техники могут создавать другие сопроводительные чертежи, основанные на этих сопроводительных чертежах, без приложения творческих усилий.

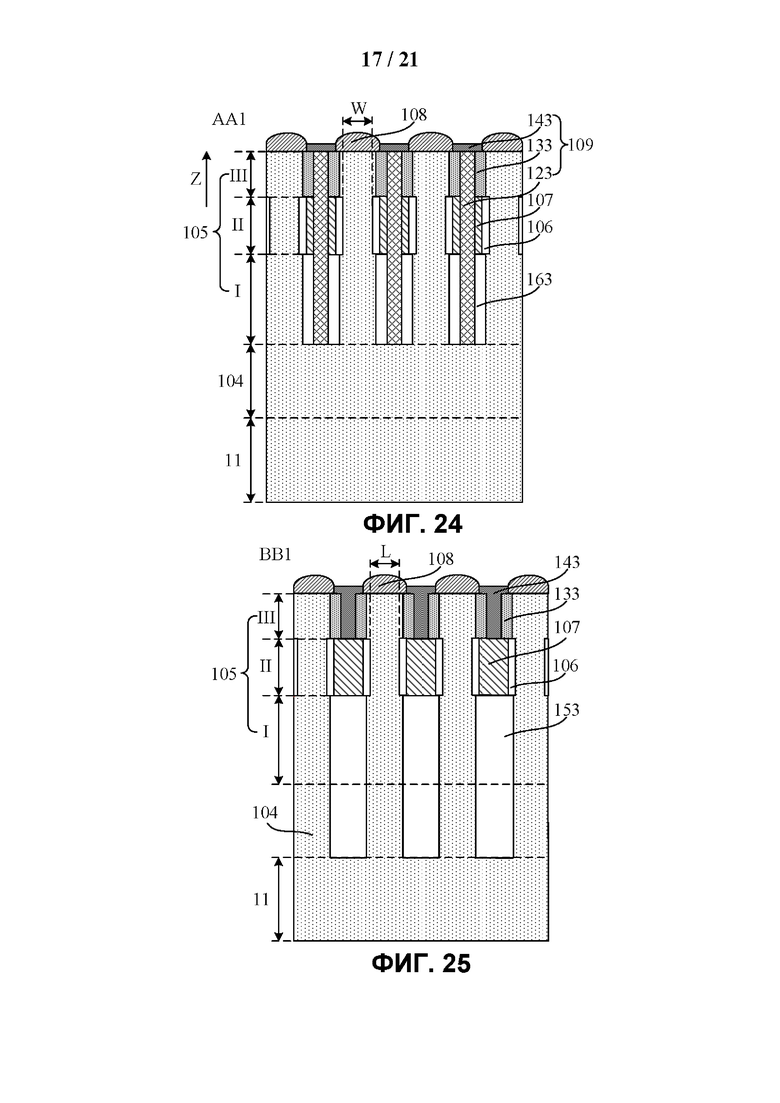

[0011] ФИГ. 1-25 представляют собой схематические структурные чертежи, соответствующие этапам способа изготовления полупроводниковой структуры согласно варианту осуществления настоящего раскрытия; и

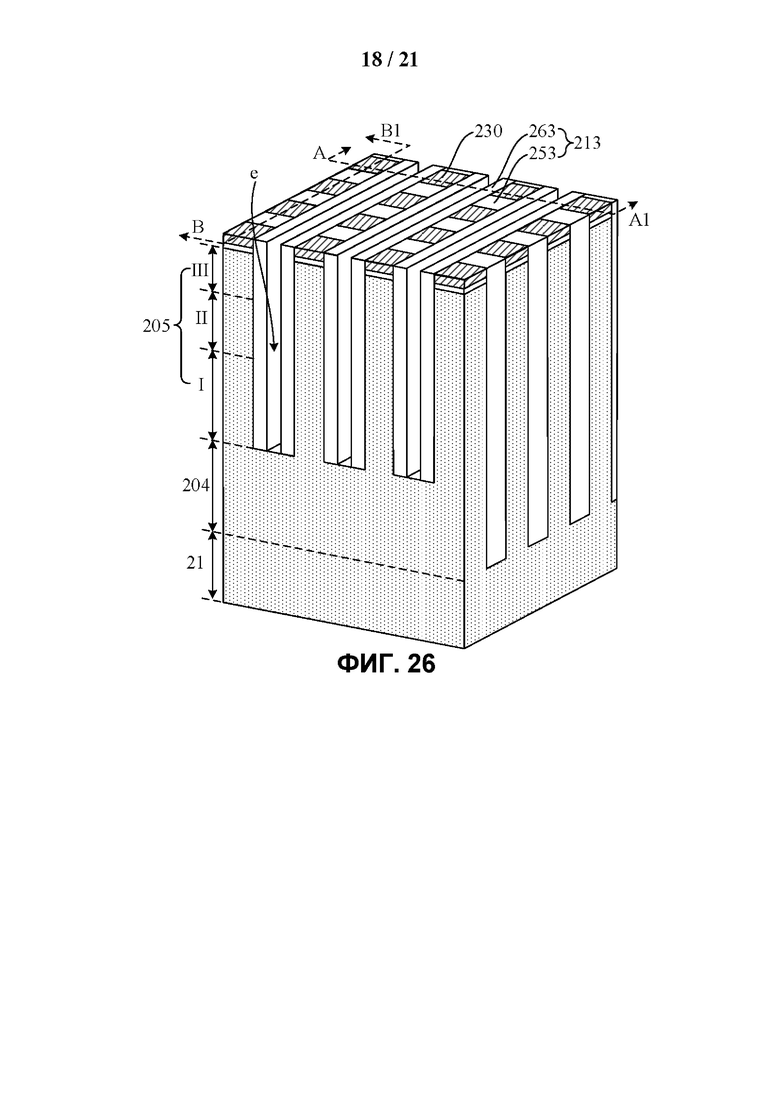

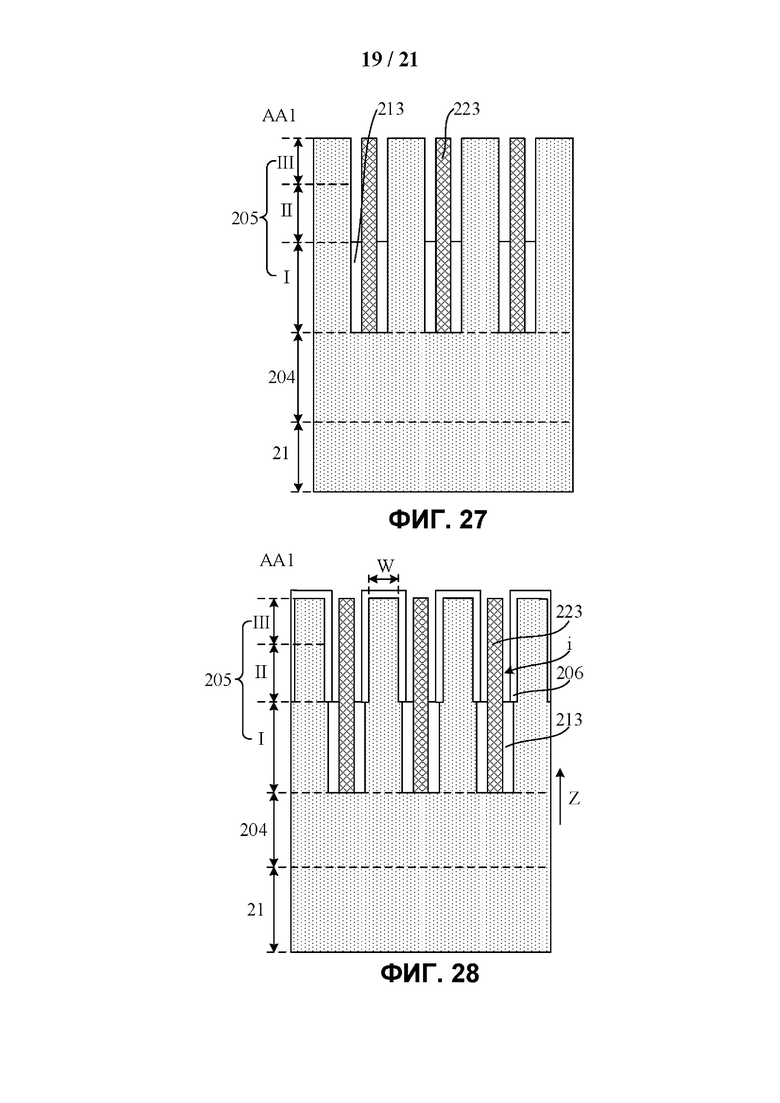

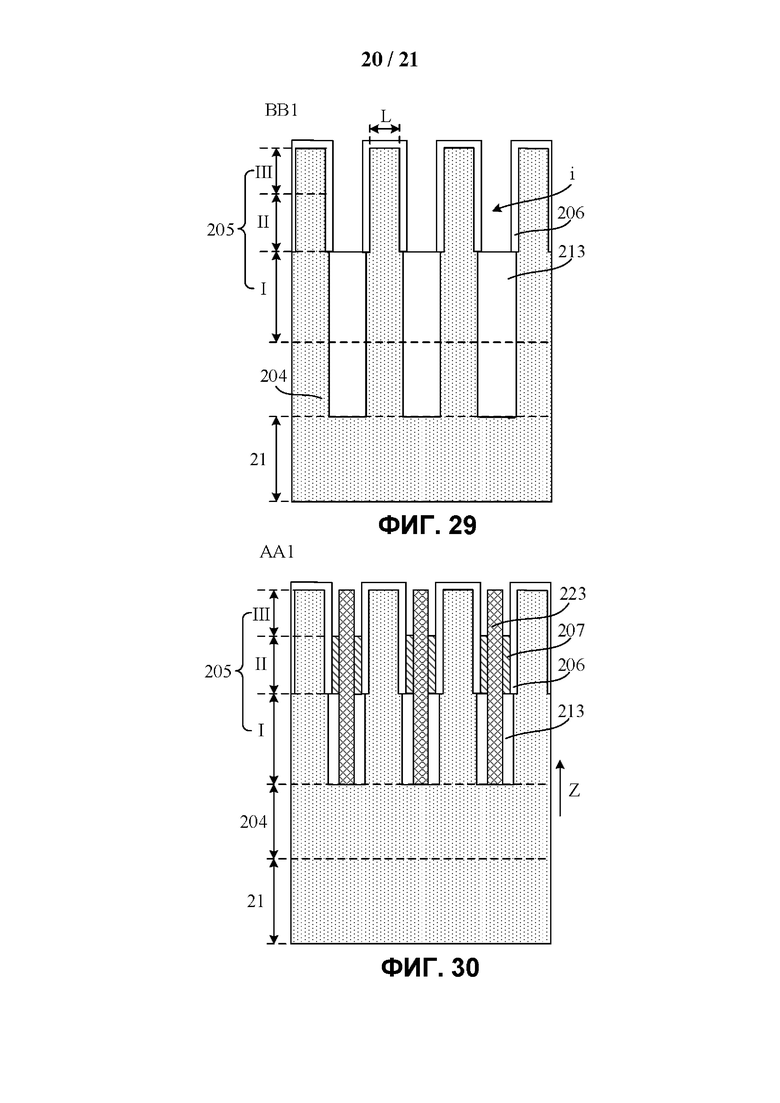

[0012] ФИГ. 26-31 представляют собой схематические структурные чертежи, соответствующие этапам способа изготовления полупроводниковой структуры согласно еще одному варианту осуществления настоящего раскрытия.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

[0013] Технические решения в вариантах осуществления настоящего раскрытия описаны ниже ясным и исчерпывающим образом со ссылкой на сопроводительные чертежи в вариантах осуществления настоящего раскрытия. Очевидно, что описанные варианты осуществления представляют собой лишь варианты осуществления настоящего раскрытия, а не все из них. Все другие варианты осуществления, создаваемые специалистами в данной области техники на основе указанных вариантов осуществления настоящего раскрытия без приложения творческих усилий, должны входить в объем защиты настоящего раскрытия. Следует отметить, что варианты осуществления в настоящем раскрытии и признаки в вариантах осуществления могут быть объединены друг с другом неконфликтным образом.

[0014] В результате исследований было обнаружено, что при формировании числовых шин, окружающих боковые стенки канальных областей полупроводниковых каналов в транзисторе с круговым затвором, требуются процессы осаждения и травления для формирования множества дискретных числовых шин. Однако вследствие сравнительно высокой плотности и сравнительно малых зазоров между соседними полупроводниковыми каналами трудно управлять точностью травления при формировании числовых шин с помощью процесса травления, и таким образом также трудно управлять точностью размеров при формировании числовых шин. Кроме того, когда размер транзистора с круговым затвором сравнительно мал, трудно управлять концентрацией легирования для каждой области полупроводникового канала при формировании транзистора с круговым затвором, имеющего вертикальную структуру, что негативно влияет на выход годных по PN-переходу, формируемому на заключительном этапе.

[0015] В вариантах осуществления настоящего раскрытия предложены полупроводниковая структура и способ ее изготовления. Согласно способу изготовления, участок первого диэлектрического слоя занимает места изолирующего слоя и числовых шин, которые должны быть сформированы впоследствии. После формирования второго диэлектрического слоя, при удалении участка первого диэлектрического слоя на боковых стенках канальных областей, оставшийся участок первого диэлектрического слоя располагается на боковых стенках первых областей легирования, так что при формировании изолирующего слоя на боковых стенках канальных областей оставшийся участок первого диэлектрического слоя может защищать первые области легирования от негативных воздействий. В дополнение, между изолирующим слоем и вторым диэлектрическим слоем сформированы вторые зазоры. Числовые шины с очень точным размером могут быть сформированы во вторых зазорах с самовыравниванием без процесса травления, что полезно для упрощения формирования числовых шин. Кроме того, регулирование размера вторых зазоров обеспечивает возможность получения числовых шин с малым размером. В дополнение, обеспечивается возможность того, чтобы концентрации легирования для легирующего иона в первой области легирования, канальной области и второй области легирования была одинакова, так что устройство, сформированное в полупроводниковом канале 105, будет представлять собой беспереходный транзистор.

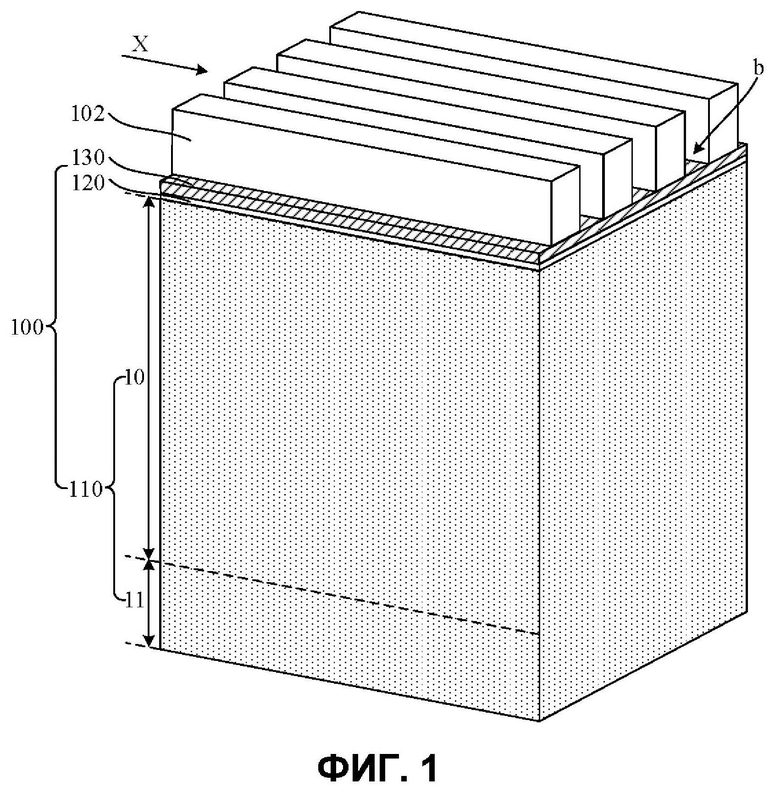

[0016] В варианте осуществления настоящего раскрытия предложен способ изготовления полупроводниковой структуры. Способ изготовления полупроводниковой структуры, предложенный в варианте осуществления настоящего раскрытия, подробно описан ниже со ссылкой на сопроводительные чертежи. ФИГ. 1-25 представляют собой схематические структурные чертежи, соответствующие этапам способа изготовления полупроводниковой структуры согласно варианту осуществления настоящего раскрытия. Следует отметить, что для удобного описания и наглядного иллюстрирования этапов способа изготовления полупроводниковой структуры, все ФИГ. 1-25 в данном варианте осуществления представляют собой частичные схематические структурные чертежи полупроводниковой структуры.

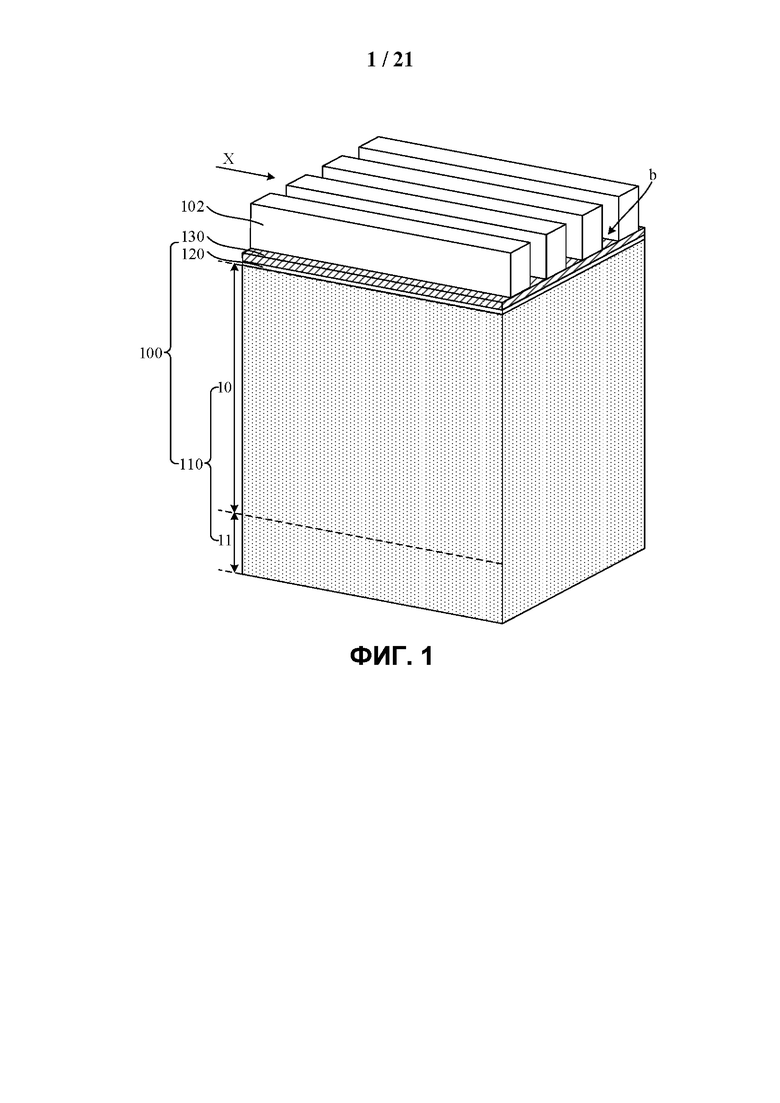

[0017] Со ссылкой на ФИГ. 1, обеспечена основа 100. В данном варианте осуществления основа 100 включает в себя подложку 110, буферный слой 120 и защитный слой 130, которые последовательно наслоены на подложку 110.

[0018] В данном варианте осуществления обеспечение основы 100 включает в себя:

[0019] Обеспечение подложки 110, которая может быть изготовлена из простого полупроводникового материала или кристаллического неорганического смешанного полупроводникового материала. Простой полупроводниковый материал может включать в себя кремний или германий, а кристаллический неорганический смешанный полупроводниковый материал может включать в себя карбид кремния, кремний-германий, арсенид галлия, арсенид индия-галлия или тому подобное.

[0020] Подложка 110 включает в себя полупроводниковый слой 11 с карманом, легированный ионами первого типа; и исходный полупроводниковый слой 10, обеспеченный на полупроводниковом слое 11 с карманом.

[0021] Исходный полупроводниковый слой 10 подвергают легированию и отжигу таким образом, чтобы исходный полупроводниковый слой 10 был легирован ионами второго типа, которые используют для последующего формирования числовых шин и полупроводниковых каналов на базе исходного полупроводникового слоя 10. Ион второго типа отличается от иона первого типа, и ион первого типа и ион второго типа соответственно представляют собой одно из иона N-типа или иона Р-типа. Ион N-типа представляет собой по меньшей мере одно из иона мышьяка, иона фосфора или иона сурьмы, а ион Р-типа представляет собой по меньшей мере одно из иона бора, иона индия или иона галлия.

[0022] Легирующая обработка может быть осуществлена путем высокотемпературной диффузии или ионной имплантации. При легировании исходного полупроводникового слоя 10 путем ионной имплантации осуществляют отжиг при 800-1000°С.

[0023] В данном варианте осуществления концентрация легирования для иона второго типа в исходном полупроводниковом слое 10 составляет от 1 × 1019 атомов/см3 до 1 × 1020 атомов/см3. В направлении от исходного полупроводникового слоя 10 к полупроводниковому слою 11 с карманом глубина легирования ионами второго типа в исходном полупроводниковом слое 10 составляет 150-250 нм. Ион первого типа представляет собой ионы Р-типа, а ион второго типа - ион N-типа. В других вариантах осуществления ион первого типа может представлять собой ион N-типа, а ион второго типа может представлять собой ион Р-типа.

[0024] Буферный слой 120 и защитный слой 130 последовательно наслоены на сторону исходного полупроводникового слоя 10, удаленную от полупроводникового слоя 11 с карманом. В некоторых примерах буферный слой 120 и защитный слой 130 могут быть сформированы посредством процесса осаждения. Буферный слой 120 изготовлен из оксида кремния, а защитный слой 130 изготовлен из нитрида кремния.

[0025] Нитрид кремния может быть осажден с помощью процесса химического осаждения из паровой фазы с образованием защитного слоя 130. Пленочный слой нитрида кремния достаточно медленно окисляется, что обеспечивает возможность защиты подложки 110, расположенной под пленочным слоем нитрида кремния, и предотвращения окисления подложки 110.

[0026] В некоторых примерах подложка 110 представляет собой кремниевую подложку. Постоянная решетки и коэффициент теплового расширения нитрида кремния имеют большое несоответствие с этими же параметрами кремниевой подложки. Если нитрид кремния осаждается непосредственно на кремниевую подложку, то вследствие высокой плотности дефектов поверхность раздела между нитридом кремния и кремнием с высокой вероятностью станет ловушкой для носителей или центром рекомбинации. Это влияет на подвижность носителей в кремнии и, таким образом, на рабочие характеристики и срок службы полупроводниковой структуры. Вследствие относительно высокого напряжения пленки нитрида кремния она подвержена растрескиванию при непосредственном осаждении на кремниевую подложку. Перед осаждением нитрида кремния на кремниевую подложку, осаждают оксид кремния в виде буферного слоя 120, таким образом улучшая рабочие характеристики и срок службы полупроводниковой структуры.

[0027] Со ссылкой на ФИГ. 1-4, на основе 100 формируют линии 104 битов, и на поверхностях линий 104 битов, удаленных от основы 100, формируют полупроводниковые каналы 105. Полупроводниковый канал 105 включает в себя первую область I легирования, канальную область II и вторую область III легирования, расположенные последовательно вдоль направления Z от основы 100 к линии 104 битов.

[0028] В данном варианте осуществления формирование линий 104 битов и полупроводниковых каналов 105 включает в себя нижеследующее.

[0029] Со ссылкой на ФИГ. 1, формируют первый маскирующий слой 102 на основе 100 таким образом, чтобы первый маскирующий слой 102 включал в себя множество первых отверстий Ь, отделенных друг от друга. Длина первого отверстия b вдоль направления X прохождения первого отверстия b является такой же, что и длина линии битов, которая будет сформирована впоследствии.

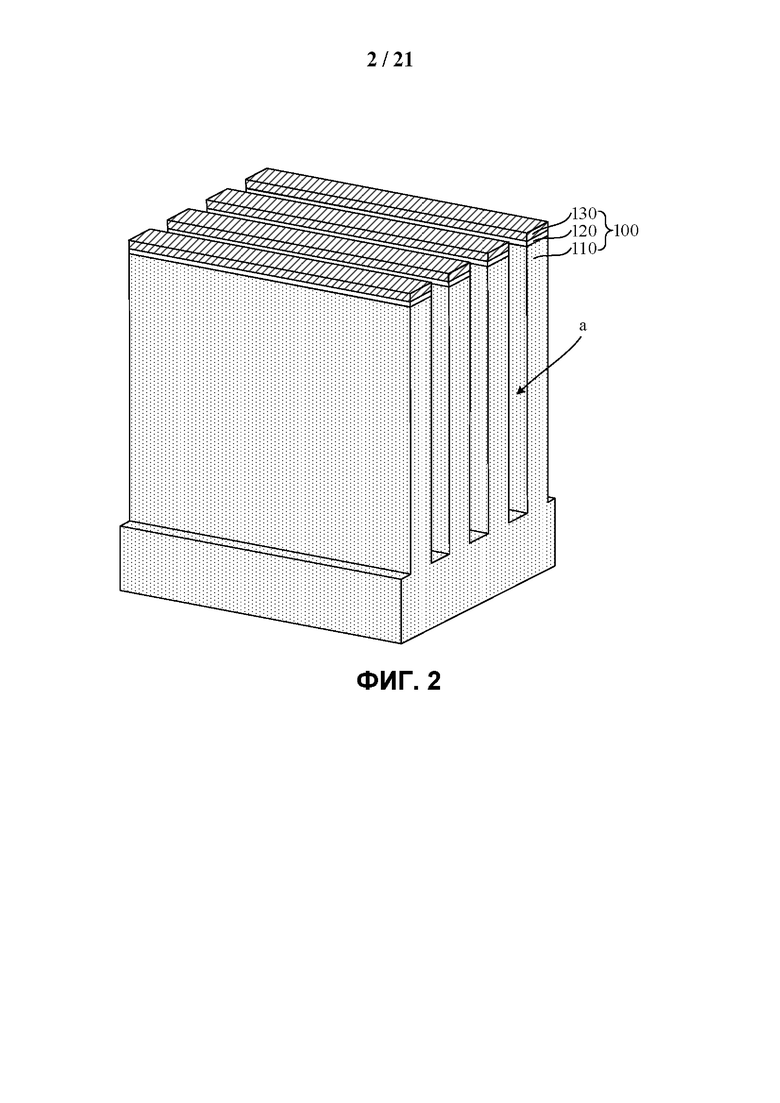

[0030] Со ссылкой на ФИГ. 2, осуществляют травление основы 100 с использованием первого маскирующего слоя 102 в качестве маски для формирования множества первых канавок а и удаляют первый маскирующий слой 102.

[0031] В данном варианте осуществления глубина первой канавки а вдоль направления Z, перпендикулярного поверхности основы 100, составляет 250-300 нм. Глубина первой канавки а больше, чем глубина легирования исходного полупроводникового слоя 10 ионами второго типа. Поэтому исходный полупроводниковый слой 10, легированный ионами второго типа, может быть подвергнут травлению для способствования последующему формированию полупроводниковых каналов и линий битов, которые легированы ионами второго типа с высокой концентрацией легирования.

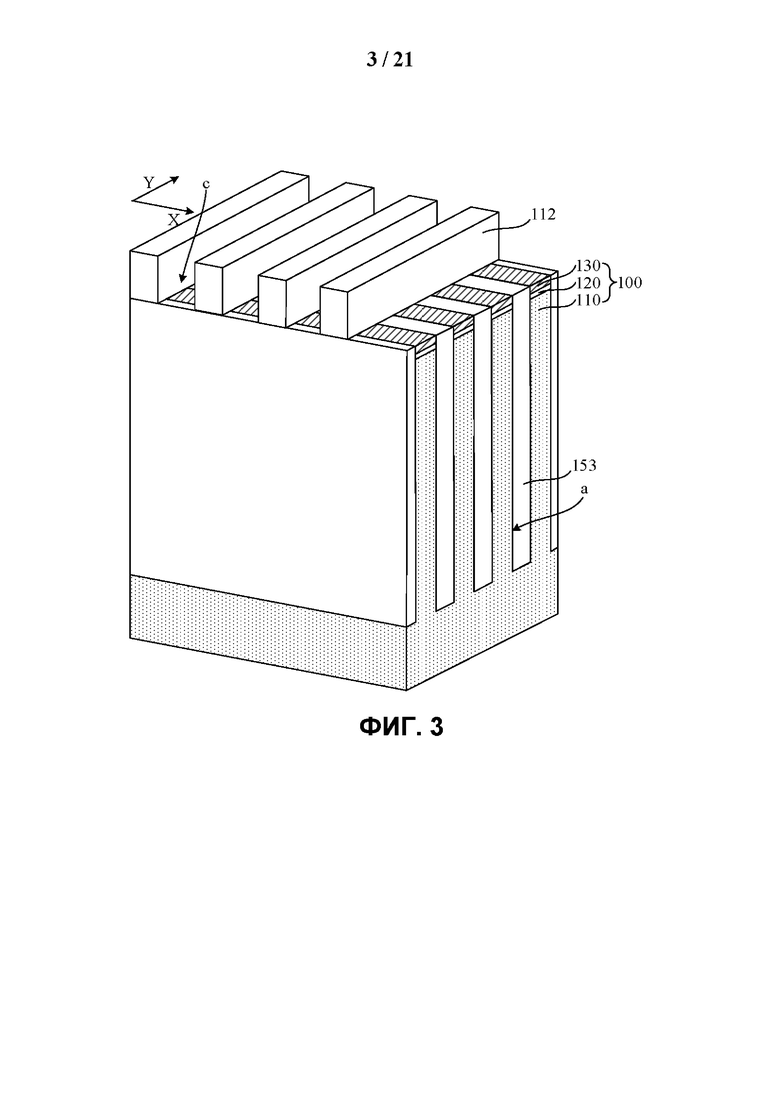

[0032] Со ссылкой на ФИГ. 3, в первых канавках а формируют пятый диэлектрический слой 153.

[0033] В данном варианте осуществления формирование пятого диэлектрического слоя 153 может включать в себя: формирование, посредством процесса осаждения, пятой диэлектрической пленки, которая покрывает верхнюю поверхность защитного слоя 130 и используется для заполнения; и осуществление процесса химико-механической планаризации на пятой диэлектрической пленке до тех пор, пока не будет открыта верхняя поверхность защитного слоя 130, при этом оставшийся участок пятой диэлектрической пленки образует пятый диэлектрический слой 153. Пятая диэлектрическая пленка включает в себя оксид кремния.

[0034] На верхней поверхности, образованной пятым диэлектрическим слоем 153 и оставшимся участком основы 100, формируют второй маскирующий слой 112 таким образом, чтобы второй маскирующий слой 112 включал в себя множество вторых отверстий с, отделенных друг от друга. Длина второго отверстия с вдоль направления Y прохождения второго отверстия с является такой же, что и длина числовые шины, которая будет сформирована впоследствии.

[0035] В данном варианте осуществления, со ссылкой на ФИГ. 1 и ФИГ. 3, направление X прохождения первого отверстия b перпендикулярно направлению Y прохождения второго отверстия с. Таким образом, полупроводниковые каналы, которые будут сформированы впоследствии, представляют собой компоновку 4F2, которая дополнительно повышает степень интеграции полупроводниковой структуры. В других вариантах осуществления направление прохождения первого отверстия и направление прохождения второго отверстия пересекаются с образованием угла, который может не составлять 90°.

[0036] Отношение ширины первого отверстия b в направлении Y к ширине второго отверстия с в направлении X равно 2 к 1, чтобы гарантировать возможность того, что впоследствии будет сформировано сквозное отверстие, открывающее участок первого диэлектрического слоя, окружающие боковую стенку канальной области II, что способствует последующему формированию второго зазора, используемого для изготовления числовые шины. В некоторых примерах ширина первого отверстия b в направлении Y равна ширине второго отверстия с в направлении X, и расстояние между соседними первыми отверстиями b равно расстоянию между соседними вторыми отверстиями с. Таким образом, множество полупроводниковых каналов, которые будут сформированы впоследствии, будут располагаться регулярным образом, что дополнительно повышает степень интеграции полупроводниковой структуры. Кроме того, обеспечивается возможность формирования первого маскирующего слоя 102 и второго маскирующего слоя 112 с использованием одной и той же маски, что снижает стоимость изготовления полупроводниковой структуры.

[0037] В данном варианте осуществления оба из первого маскирующего слоя 102 и второго маскирующего слоя 112 могут быть сформированы с помощью процесса четверного формирования рисунка с самовыравниванием (self-aligned quadruple patterning process, SAQP) или процесса двойного формирования рисунка с самовыравниванием (self-aligned double patterning process, SADP).

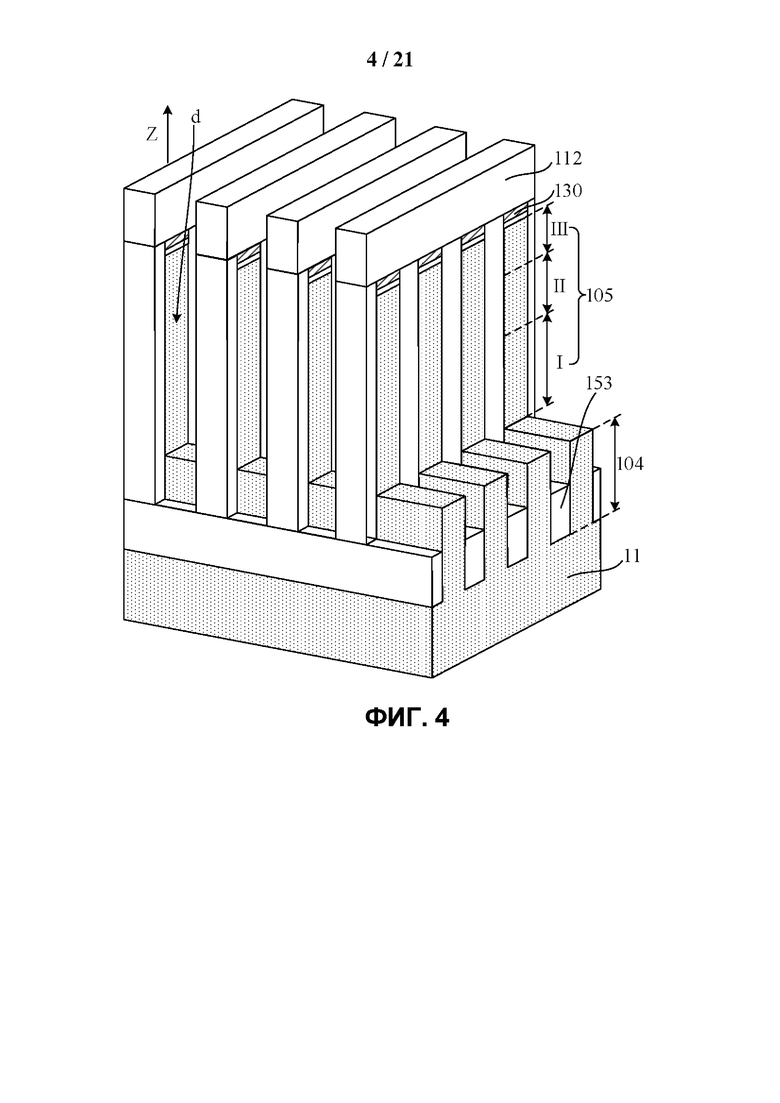

[0038] Co ссылкой на ФИГ. 4, основа 100 (см. ФИГ. 1) и пятый диэлектрический слой 153 подвергают травлению с использованием второго маскирующего слоя 112 в качестве маски для формирования множества вторых канавок d, линий 104 битов и полупроводниковых каналов 105. В направлении Z, перпендикулярном поверхности основы 100, глубина второй канавки d меньше, чем глубина первой канавки а. Таким образом, при формировании линий 104 битов, на сторонах линий 104 битов, удаленных от полупроводникового слоя 11 с карманом, формируют множество полупроводниковых каналов 105, отделенных друг от друга, причем линии 104 битов находятся в контакте с первой областью I легирования полупроводникового канала 105. Второй маскирующий слой 112 удаляют.

[0039] В некоторых примерах глубина второй канавки d составляет от 100 до 150 нм. Поскольку глубина легирования ионами второго типа в исходном полупроводниковом слое 10 (см. ФИГ. 1) составляет от 150 до 250 нм, большая часть или весь исходный полупроводниковый слой 10, легированный ионами второго типа, преобразуется в полупроводниковые каналы 105 после двух травлений.

[0040] Подложку 110 изготавливают из кремния, а пятый диэлектрический слой 153 изготавливают из оксида кремния. При травлении основы 100 и пятого диэлектрического слоя 153 с использованием второго маскирующего слоя 112 в качестве маски, скорость травления для оксида кремния больше, чем для кремния. Поэтому участок боковой стенки линии 104 битов открыт.

[0041] В данном варианте осуществления, на полупроводниковом слое 11 с карманом может быть сформировано множество линий 104 битов, отделенных друг от друга, и линии 104 битов могут находиться в контакте с по меньшей мере одной из первых областей I легирования. На ФИГ. 4 показаны четыре линии 104 битов, отделенных друг от друга, причем линии 104 битов контактируют с четырьмя первыми областями I легирования. Количество линий 104 битов и количество первых областей I легирования, контактирующих с каждой из линий 104 битов, могут быть установлены надлежащим образом в соответствии с фактическими электрическими требованиями.

[0042] После травления основы 100 и пятого диэлектрического слоя 153 с использованием второго маскирующего слоя 112 в качестве маски, оставшийся участок пятого диэлектрического слоя 153 дополнительно располагаются в зазорах между соседними линиями 104 битов и в зазорах между соседними полупроводниковыми каналами 105. Таким образом достигается электрическая изоляция между соседними исходными линиями 104 битов и соседними полупроводниковыми каналами 105.

[0043] В данном варианте осуществления, поскольку исходный полупроводниковый слой 10 (см. ФИГ. 1) легирован ионами N-типа, сформированные линия 104 битов и полупроводниковый канал 105 могут быть легированы ионами N-типа.

[0044] Линию 104 битов легируют ионами N-типа. Полупроводниковый слой 11 с карманом легируют ионами Р-типа. Линия 104 битов и полупроводниковый слой 11 с карманом образуют PN-переход для предотвращения утечки из линии 104 битов, что дополнительно улучшает электрические характеристики полупроводниковой структуры. В еще одном варианте осуществления основа может не включать в себя полупроводниковый слой с карманом, то есть основа представляет собой исходный полупроводниковый слой, и линии битов расположены на поверхности исходного полупроводникового слоя.

[0045] Устройство, образованное полупроводниковым каналом 105, представляет собой беспереходный транзистор, то есть первая область I легирования, канальная область II и вторая область III легирования легированы легирующим ионом одного и того же типа, такого как ион N-типа. Кроме того, первая область I легирования, канальная область II и вторая область III легирования могут быть легированы легирующими ионами одного и того же типа. Термин «беспереходный» в настоящем документе относится к отсутствию PN-перехода, то есть отсутствует PN-переход в транзисторе, образованном полупроводниковым каналом 105, и концентрации легирования для легирующего иона в первой области I легирования, канальной области II и второй области III легирования одинаковы. Таким образом, отсутствует необходимость в проведении дополнительного легирования первой области I легирования и второй области III легирования и в результате предотвращается проблема, состоящая в том, что процессом легирования в первой области I легирования и второй области III легирования трудно управлять. Концентрацией легирования становится особенно трудно управлять в случае дальнейшего уменьшения размера транзистора, если дополнительно легируются первая область I легирования и вторая область III легирования. В дополнение, поскольку устройство представляет собой беспереходный транзистор, оно не требует использования процесса легирования истока-стока со сверхвысоким градиентом для создания PN-перехода со сверхвысоким градиентом в наноразмерном диапазоне. В результате обеспечена возможность недопущения таких проблем, как дрейф порогового напряжения и увеличение тока утечки, вызванные резкими изменениями концентрации легирования, и возможность легкого подавления эффекта короткого канала, так что устройство по-прежнему способно работать в диапазоне нескольких нанометров. Такая конструкция дополнительно повышает степень интеграции и электрические характеристики полупроводниковой структуры. Выражение «дополнительное легирование» в настоящем документе относится к легированию, осуществляемому для обеспечения того, чтобы тип легирующего иона в первой области I легирования и второй области III легирования отличался от типа легирующего иона в канальной области II.

[0046] Полупроводниковый канал 105 образует транзистор с круговым затвором, перпендикулярный верхней поверхности линии 104 битов, удаленной от полупроводникового слоя 11 с карманом, таким образом образуя трехмерную слоистую полупроводниковую структуру. Транзисторы с круговым затвором выполнены с малым размером без негативного воздействия на электрические характеристики транзисторов с круговым затвором, что увеличивает степень интеграции полупроводниковой структуры.

[0047] В данном варианте осуществления первый маскирующий слой 102 и второй маскирующий слой 112 используют для одновременного формирования линий 104 битов и полупроводниковых каналов 105 посредством двух процессов травления. Размер полупроводникового канала 105 регулируют путем регулирования размеров первого отверстия b и второго отверстия с, так что полупроводниковые каналы 105 формируются с высокой точностью размеров. Линии 104 битов и полупроводниковые каналы 105 формируют путем травления подложки 110. Иначе говоря, линии 104 битов и полупроводниковые каналы 105 формируют с использованием одной и той же пленочной структуры, так что линии 104 битов и полупроводниковые каналы 105 объединены. Это предотвращает дефекты состояния поверхности раздела между линиями 104 битов и полупроводниковыми каналами 105 и улучшает характеристики полупроводниковой структуры. После травления основы 100 с использованием первого маскирующего слоя 102 в качестве маски, в первых канавках а дополнительно формируют пятый диэлектрический слой 153. Таким образом подготавливают последующее формирование зазора между боковой стенкой канальной области II и вторым диэлектрическим слоем и способствуют последующему формированию второго зазора для получения числовые шины.

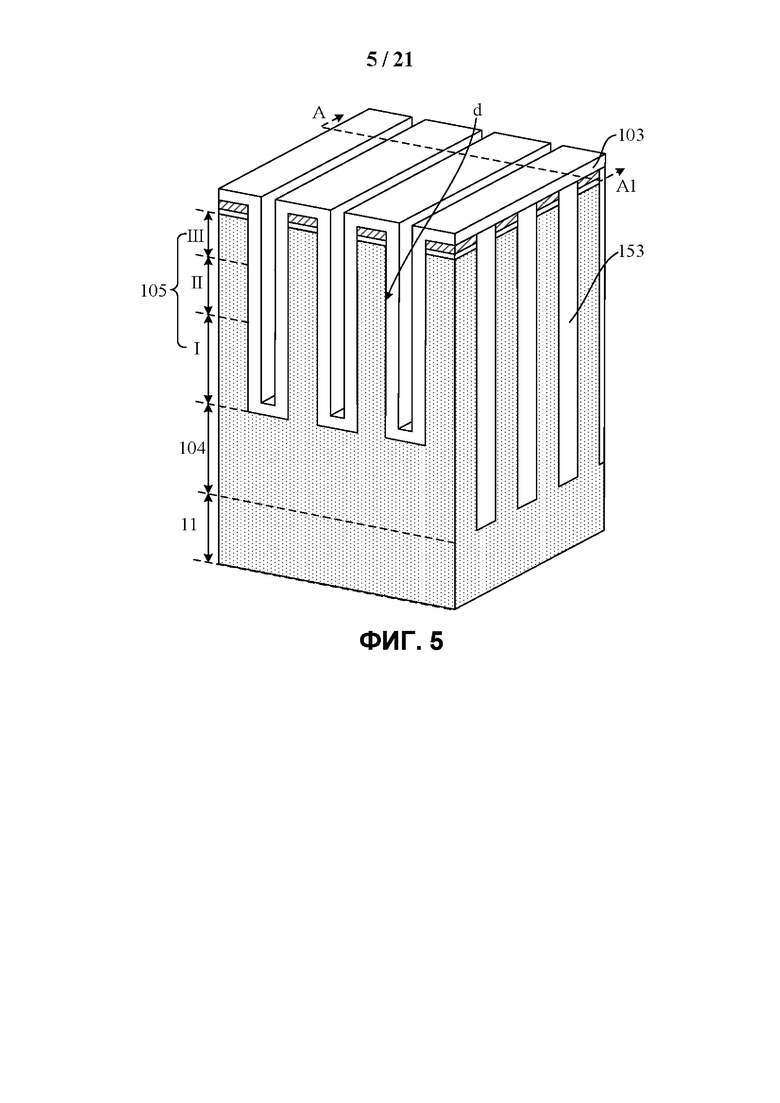

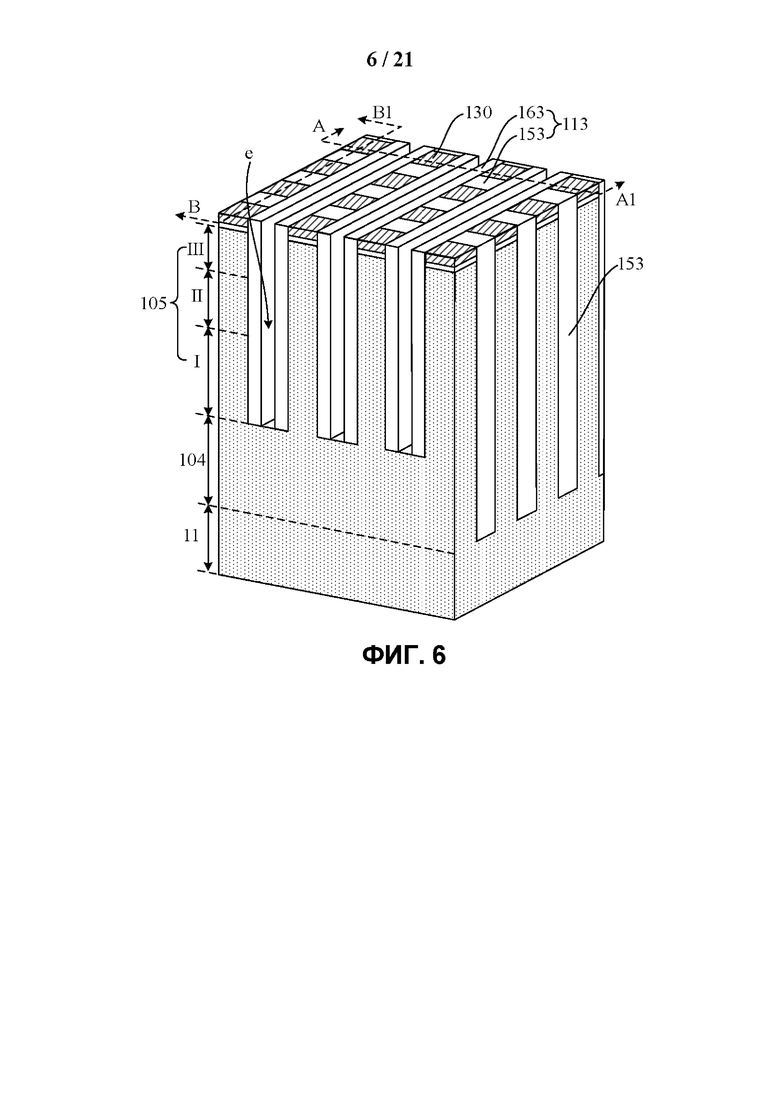

[0048] Со ссылкой на ФИГ. 5-8, формируют первый диэлектрический слой 113. Первый диэлектрический слой 113 окружает боковые стенки полупроводниковых каналов 105. Между участками первого диэлектрического слоя 113, расположенными на боковых стенках соседних полупроводниковых каналов 105 на одной и той же линии 104 битов, обеспечивают первый зазор е.

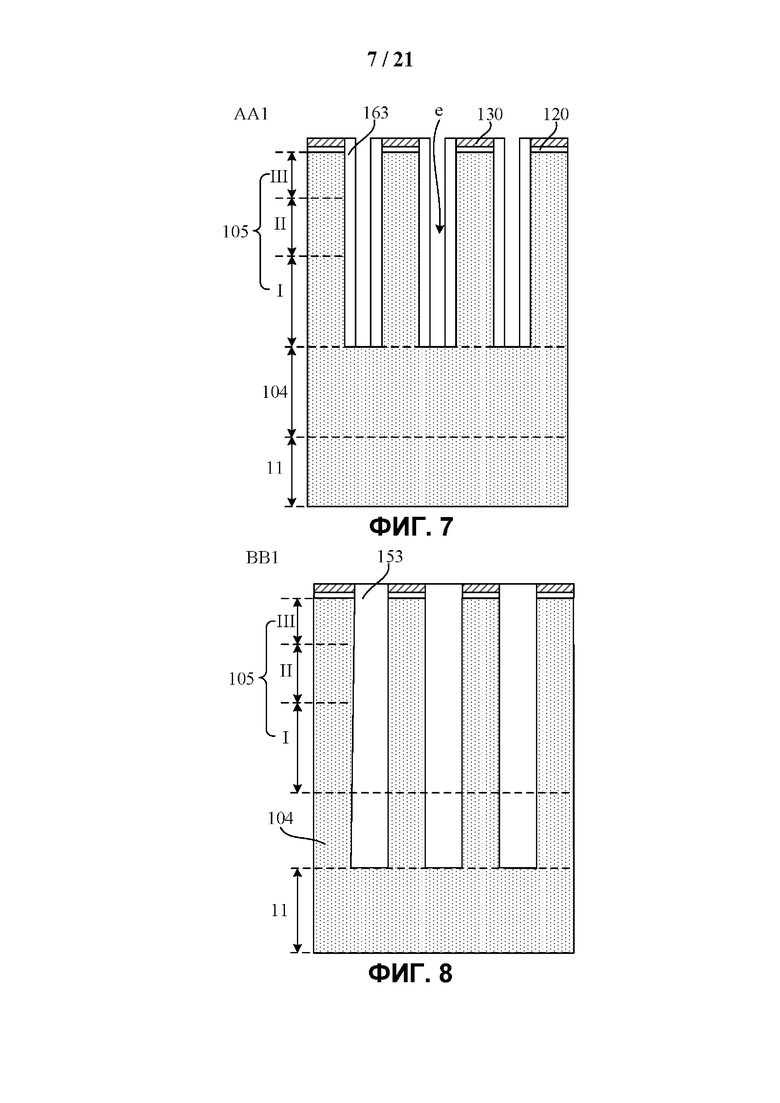

[0049] На ФИГ. 7 показан вид в сечении, выполненном вдоль первого направления АА1 сечения, структуры, показанной на ФИГ. 6, и на ФИГ. 8 показан вид в сечении, выполненном вдоль второго направления ВВ1 сечения, структуры, показанной на ФИГ. 6. Следует отметить, что один или оба из вида в сечении вдоль первого направления АА1 сечения или вида в сечении вдоль второго направления ВВ1 сечения рассмотрены ниже в соответствии с требованиями описания. При ссылке только на один сопроводительный чертеж, этот сопроводительный чертеж представляет собой вид в сечении вдоль первого направления АА1 сечения. При одновременной ссылке на два сопроводительных чертежа, первый сопроводительный чертеж представляет собой вид в сечении вдоль первого направления АА1 сечения, а второй сопроводительный чертеж представляет собой вид в сечении вдоль второго направления ВВ1 сечения.

[0050] В данном варианте осуществления формирование первого диэлектрического слоя включает в себя нижеследующее.

[0051] Со ссылкой на ФИГ. 5, формируют шестую диэлектрическую пленку 103. Шестая диэлектрическая пленка 103 конформно покрывает боковые стенки и дно вторых канавок d, и она расположена на верхних поверхностях защитного слоя 130 и пятого диэлектрического слоя 153.

[0052] Со ссылкой на ФИГ. 5 и ФИГ. 6, шестую диэлектрическую пленку 103 подвергаются процессу безмасочного сухого травления до тех пор, пока не будет открыт защитный слой 130. За одно и то же время травления происходит травление различных областей шестой диэлектрической пленки 103 таким образом, чтобы они имели одинаковую толщину, для формирования шестого диэлектрического слоя 163.

[0053] Со ссылкой на ФИГ. 6-8, шестой диэлектрический слой 163 расположен на боковых стенках вторых канавок d, и пятый диэлектрический слой 153 также расположен в зазорах между соседними полупроводниковыми каналами 105. Пятый диэлектрический слой 153 и шестой диэлектрический слой 163 образуют первый диэлектрический слой 113, и между участками шестого диэлектрического слоя 163, расположенными на боковой стенке второй канавки d, обеспечен первый зазор е.

[0054] Шестой диэлектрический слой 163 и пятый диэлектрический слой 153 изготавливают из одного и того же материала. Затем участок шестого диэлектрического слоя 163 и участок пятого диэлектрического слоя 153, соответствующие боковым стенкам канальных областей II, совместно удаляют посредством процесса травления, таким образом формируя зазоры между боковыми стенками канальных областей II и вторым диэлектрическим слоем, который будет сформирован впоследствии. Это способствует последующему формированию вторых зазоров для получения числовых шин. Шестой диэлектрический слой 163 и пятый диэлектрический слой 153 выполняют из оксида кремния.

[0055] В других вариантах осуществления шестой диэлектрический слой и пятый диэлектрический слой могут также быть изготовлены из различных материалов при условии, что материалы шестого диэлектрического слоя и пятого диэлектрического слоя обеспечивают требуемый изоляционный эффект. В этом случае участок шестого диэлектрического слоя и участок пятого диэлектрического слоя, соответствующие боковым стенкам канальных областей II, удаляют на разных этапах.

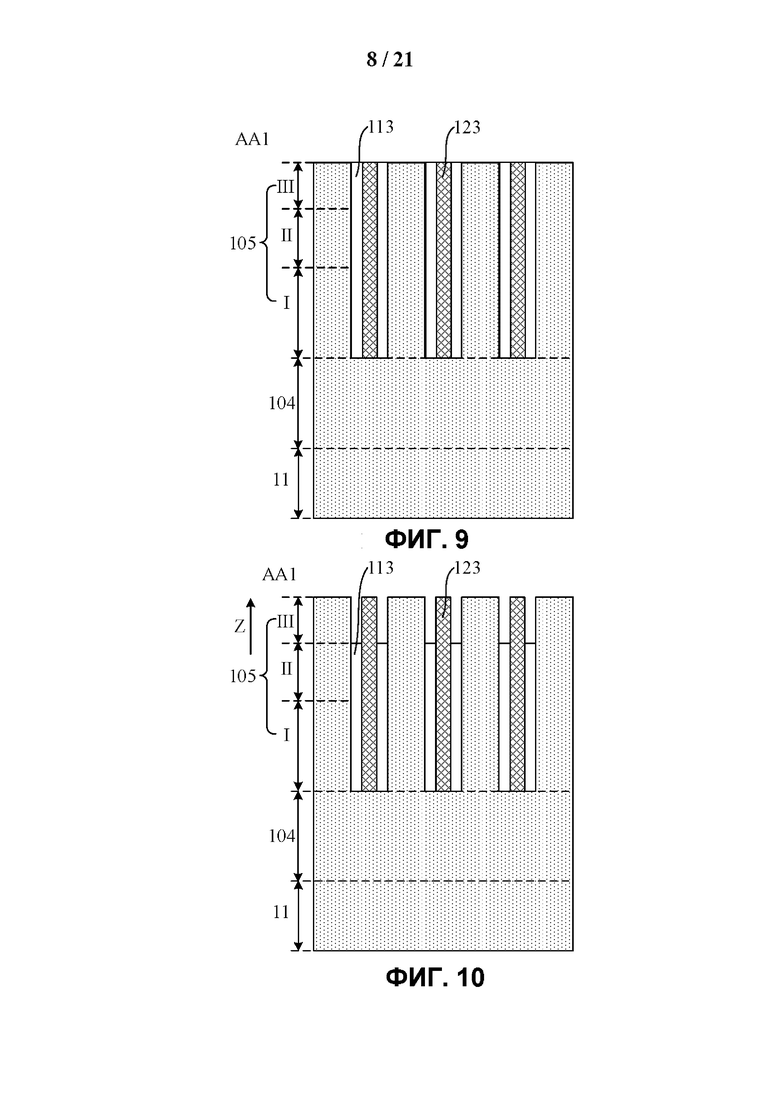

[0056] Со ссылкой на ФИГ. 7 и ФИГ. 9, второй диэлектрический слой 123 формируют для заполнения первых зазоров е. Второй диэлектрический слой 123 и первый диэлектрический слой 113 изготавливают из разных материалов.

[0057] В некоторых примерах второй диэлектрический слой 123 может быть сформирован путем формирования, посредством процесса осаждения, второй диэлектрической пленки, покрывающей верхнюю поверхность защитного слоя 130 и заполняющей первые зазоры е. Вторую диэлектрическую пленку, защитный слой 130, буферный слой 120 и первый диэлектрический слой 113 (см. ФИГ. 6) подвергают процессу химико-механической планаризации до тех пор, пока не будут открыты верхние поверхности вторых областей III легирования. Оставшийся участок второй диэлектрической пленки образуют второй диэлектрический слой 123. Вторая диэлектрическая пленка включает в себя нитрид кремния.

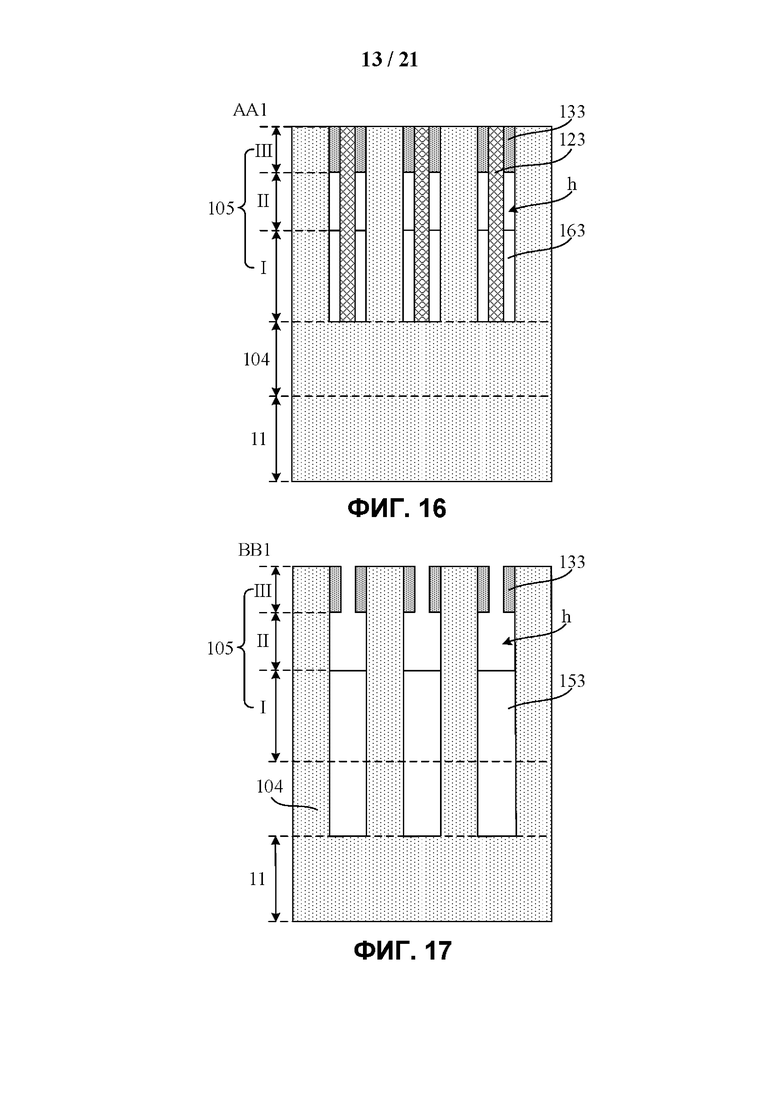

[0058] Со ссылкой на ФИГ. 10-17, участок первого диэлектрического слоя 113 подвергают травлению, чтобы открыть боковые стенки канальных областей II.

[0059] В некоторых примерах травление участка первого диэлектрического слоя 113 для открытия боковых стенок канальных областей II включает в себя нижеследующее.

[0060] Со ссылкой на ФИГ. 9 и ФИГ. 10, осуществляют травление участка первого диэлектрического слоя 113 с использованием полупроводниковых каналов 105 и второго диэлектрического слоя 123 в качестве маски для открытия боковых стенок вторых областей III легирования. В некоторых примерах вторая область III легирования имеет протяженность от 30 до 50 нм в направлении Z, которое перпендикулярно линии 104 битов и представляет собой направление на полупроводниковый канал 105.

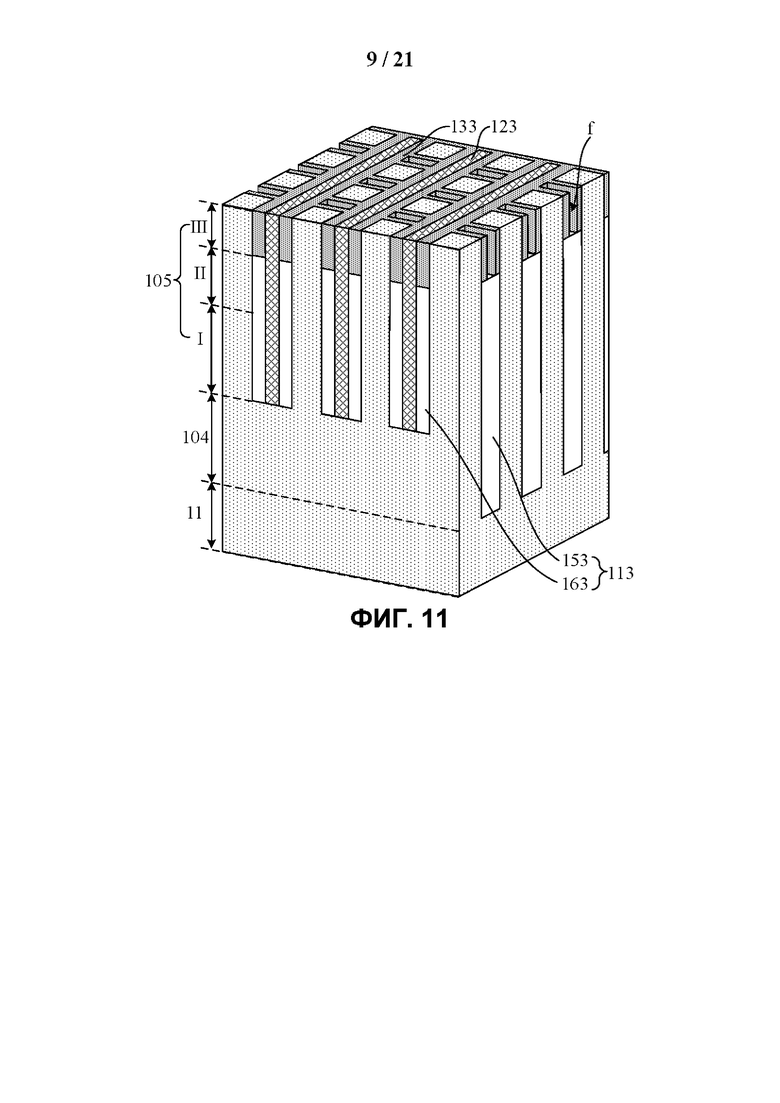

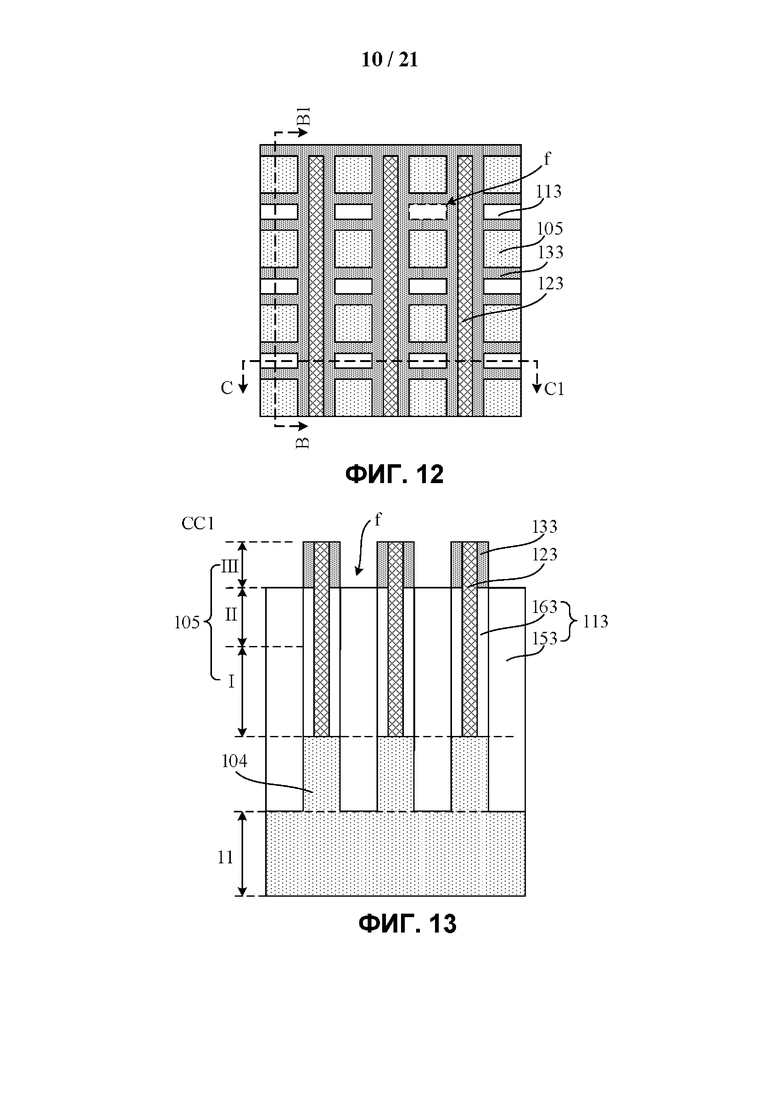

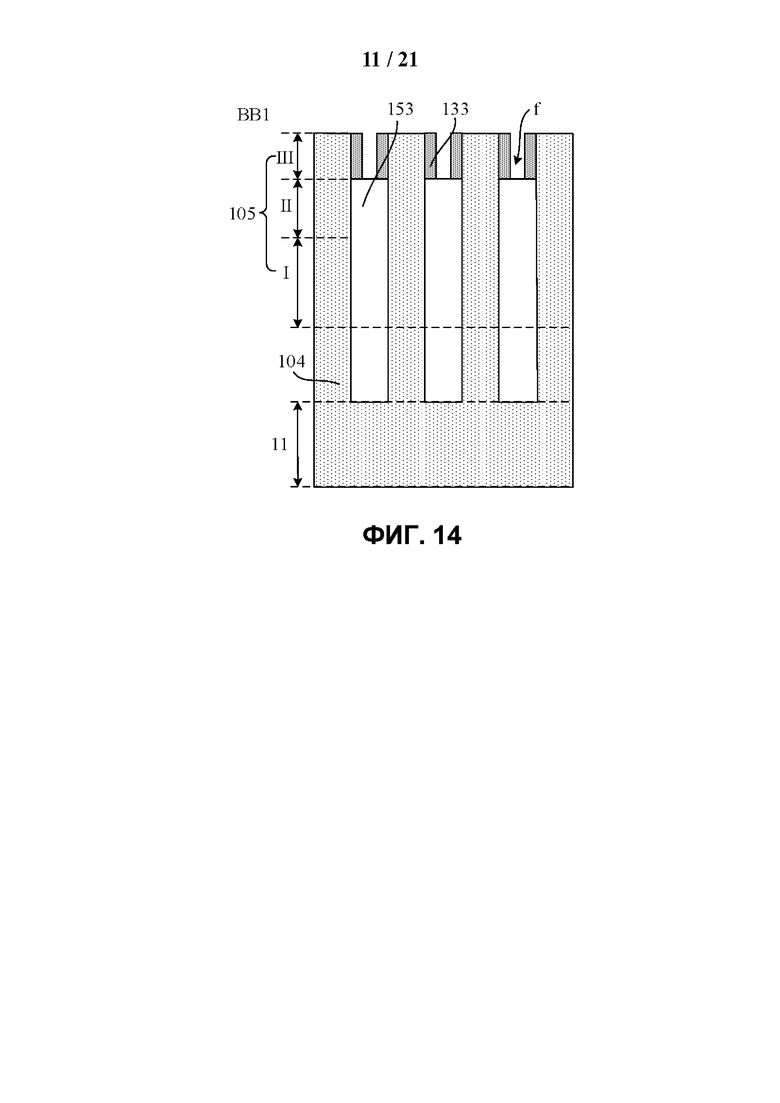

[0061] Обратимся к ФИГ. 11-14. ФИГ. 12 представляет собой вид сверху объекта по ФИГ. 11. ФИГ. 13 представляет собой вид в сечении, выполненном вдоль третьего направления СС1 сечения. ФИГ. 14 представляет собой вид в сечении, выполненном вдоль второго направления ВВ1 сечения.

[0062] Формируют третий диэлектрический слой 133. Третий диэлектрический слой 133 окружает боковые стенки вторых областей III легирования и расположен на боковой стенке второго диэлектрического слоя 123. Участок третьего диэлектрического слоя 133, расположенный на боковых стенках вторых областей III легирования, и участок третьего диэлектрического слоя 133, расположенный на боковой стенке второго диэлектрического слоя 123, образуют сквозные отверстия f. Участок первого диэлектрического слоя 113 открыт на дне сквозных отверстий f, при этом третий диэлектрический слой 133 и первый диэлектрический слой 113 изготавливают из разных материалов.

[0063] Со ссылкой на ФИГ. 13 и ФИГ. 14, третий диэлектрический слой 133 покрывает верхнюю поверхность шестого диэлектрического слоя 163 и участок верхней поверхности пятого диэлектрического слоя 153, окружая боковые стенки вторых областей III легирования. Сквозные отверстия f открывают участок верхней поверхности пятого диэлектрического слоя 153.

[0064] В данном варианте осуществления третий диэлектрический слой 133 может быть сформирован путем формирования, посредством процесса осаждения, третьей диэлектрической пленки для конформного покрытия поверхности, образованной полупроводниковыми каналами 105, первыми диэлектрическими слоями 113 и вторыми диэлектрическими слоями 123. Третью диэлектрическую пленку подвергают процессу безмасочного сухого травления до тех пор, пока не будут открыты верхние поверхности вторых областей III легирования. За одно и то же время травления происходит травление разных областей третьей диэлектрической пленки, чтобы они имели одинаковую толщину для формирования третьего диэлектрического слоя 133, открывающего участок первого диэлектрического слоя 113. Материал третьего диэлектрического слоя 133 включает в себя нитрид кремния.

[0065] В первом маскирующем слое 102 и втором маскирующем слое 112 отношение ширины первого отверстия b в направлении Y к ширине второго отверстия с в направлении X равно 2 к 1. При формировании третьего диэлектрического слоя 133 этот третий диэлектрический слой 133 заполняет зазоры между соседними полупроводниковыми каналами 105 на одной и той же линии 104 битов, но не заполняет зазоры между соседними полупроводниковыми каналами 105 на соседних линиях 104 битов. Таким образом, сформированные сквозные отверстия f способны открывать участок верхней поверхности пятого диэлектрического слоя 153, что способствует последующему удалению участка первого диэлектрического слоя 113 через сквозные отверстия f.

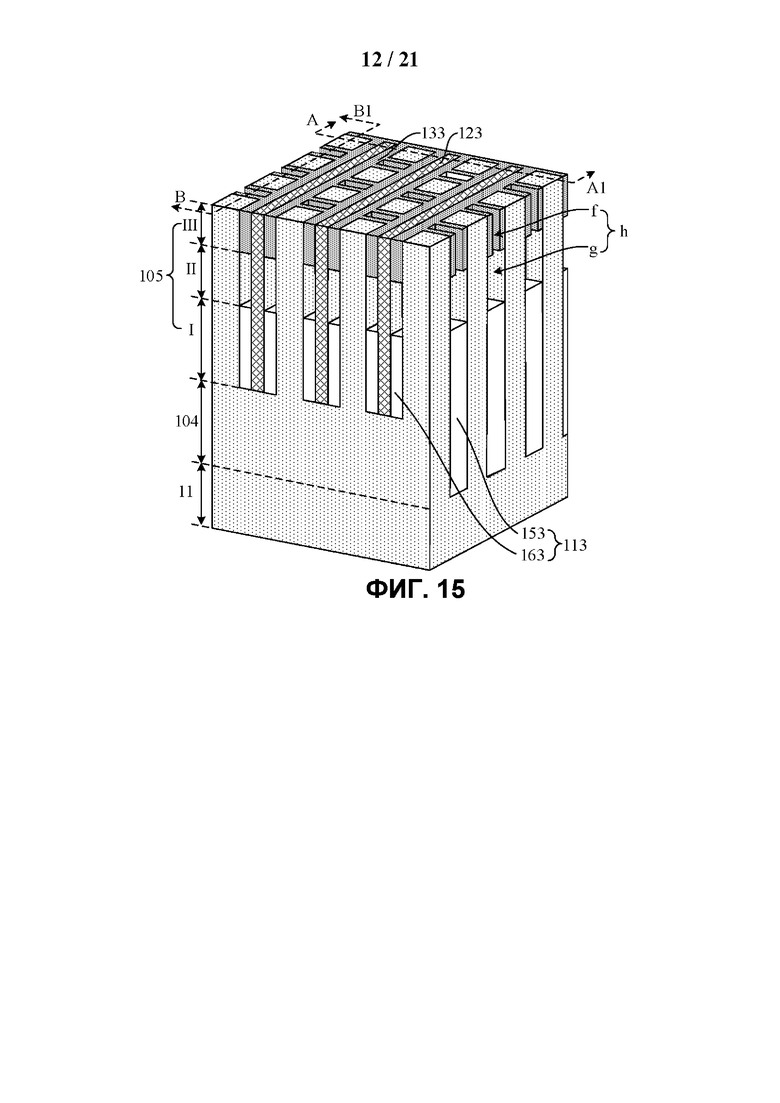

[0066] Со ссылкой на ФИГ. 15-17, удаляют участок первого диэлектрического слоя 113, расположенный на боковых стенках канальных областей II, открытых посредством сквозных отверстий f, и оставшийся участок первого диэлектрического слоя 113 окружает боковые стенки первых областей I легирования.

[0067] Сквозные отверстия f открывают участок верхней поверхности первого диэлектрического слоя 113, и первый диэлектрический слой 113, второй диэлектрический слой 123 и третий диэлектрический слой 133 выполнены из отличных друг от друга материалов. Следовательно, травильный раствор может быть впрыснут в сквозные отверстия f для травления участка первого диэлектрического слоя 113, расположенного на боковых стенках канальных областей II, посредством процесса влажного травления. Участок первого диэлектрического слоя 113, расположенный на боковых стенках первых областей I легирования, сохраняют.

[0068] Второй диэлектрический слой 123 и третий диэлектрический слой 133 вместе образуют опорную рамку. Опорная рамка находится в контакте со вторыми областями III легирования, и опорная рамка частично встроена в первый диэлектрический слой 113. При влажном травлении опорная рамка поддерживает и фиксирует полупроводниковые каналы 105. При протекании травильного раствора, на полупроводниковом канале 105 создается нажимное усилие. Опорная рамка предотвращает нажим на полупроводниковые каналы 105 с их наклоном или смещением, таким образом улучшая стабильность полупроводниковой структуры. Кроме того, опорная рамка охватывает боковые стенки вторых областей III легирования, чтобы предотвратить повреждение травильным раствором вторых областей III легирования.

[0069] После удаления участка первого диэлектрического слоя 113, расположенного на боковых стенках канальных областей II, между канальными областями II и вторым диэлектрическим слоем 123, формируют третьи зазоры g, при этом сквозное отверстие f и третий зазор g образуют полостную структуру h.

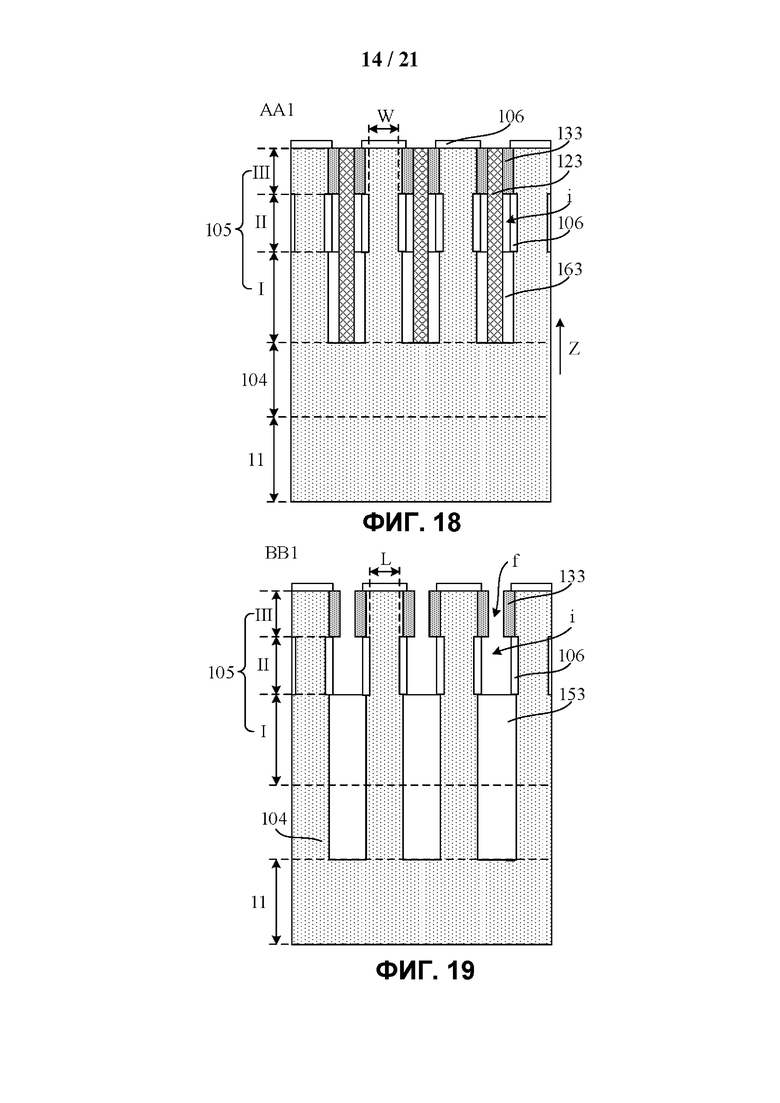

[0070] Со ссылкой на ФИГ. 18 и ФИГ. 19, формируют изолирующий слой 106. Изолирующий слой 106 покрывает по меньшей мере поверхности боковых стенок канальных областей II, и между изолирующим слоем 106 и вторым диэлектрическим слоем 123 обеспечены вторые зазоры i. Со ссылкой на ФИГ. 19, вторые зазоры I дополнительно расположены между участками изолирующего слоя 106 на боковых стенках соседних полупроводниковых каналов 105 соседних линий 104 битов.

[0071] В данном варианте осуществления, поскольку полупроводниковые каналы 105 выполнены из кремния, формирование изолирующего слоя 106 включает в себя термическое окисление открытых боковых стенок канальных областей II для формирования изолирующего слоя 106. Изолирующий слой 106 покрывает поверхности боковых стенок оставшегося участка канальных областей II. Изолирующий слой 106 выполнен из оксида кремния. В других вариантах осуществления изолирующий слой, покрывающий поверхности боковых стенок канальных областей, также может быть сформирован посредством процесса осаждения.

[0072] Путем термического окисления открытых боковых стенок канальных областей II, часть канальных областей II преобразуют в изолирующий слой 106. Ортогональная проекция канальной области II на линию 104 битов меньше, чем ортогональная проекция второй области III легирования и первой области I легирования на линию 104 битов. Таким образом обеспечена возможность формирования канальной области II с меньшей площадью сечения в сечениях, перпендикулярных направлению Z от линии 104 битов к полупроводниковому каналу 105, без использования процесса травления. В результате обеспечена возможность того, что числовые шины, которые будут сформированы впоследствии, будут лучше управлять канальными областями II, так что будет обеспечено улучшенное управление транзисторами с круговым затвором для их отпирания или запирания.

[0073] В некоторых примерах ширина W и длина L канальной области II в сечении, перпендикулярном направлению Z, не превышают 10 нм, и это гарантирует, что числовая шина, которая будет сформирована впоследствии, будет хорошо управлять канальной областью II. Высота канальной области II составляет от 30 до 50 нм в направлении Z.

[0074] Поскольку верхние поверхности вторых областей III легирования открыты наружу во время термического окисления, участок вторых областей II легирования, близкий к верхним поверхностям, преобразуется в изолирующий слой 106. В данном варианте осуществления участок изолирующего слоя 106 на верхних поверхностях оставшегося участка вторых областей III легирования удаляют на последующем этапе процесса. В других вариантах осуществления участок изолирующего слоя на верхних поверхностях оставшегося участка вторых областей легирования может быть удален после термического окисления, и сохраняется только участок изолирующего слоя, покрывающий поверхности боковых стенок оставшегося участка канальных областей.

[0075] Со ссылкой на ФИГ. 18 и 19, ортогональная проекция периферии изолирующего слоя 106 на линии 104 битов меньше, чем ортогональная проекция периферии третьего диэлектрического слоя 133 на линии 104 битов. Иначе говоря, по сравнению с наружной стенкой третьего диэлектрического слоя 133, удаленной от полупроводникового канала 105, внешняя стенка изолирующего слоя 106, удаленная от полупроводникового канала 105, находится ближе к полупроводниковому каналу 105. Таким образом обеспечена возможность формирования вторых зазоров i между изолирующим слоем 106 и вторым диэлектрическим слоем 123, так что числовая шина, которая будет сформирована впоследствии, сможет окружать участок изолирующего слоя 106, расположенный на боковой стенке канальной области II. По сравнению с внешней стенкой первого диэлектрического слоя 113 (как показано на ФИГ. 15), удаленной от полупроводникового канала 105, внешняя стенка изолирующего слоя 106, удаленная от полупроводникового канала 105, также находится ближе к полупроводниковому каналу 105.

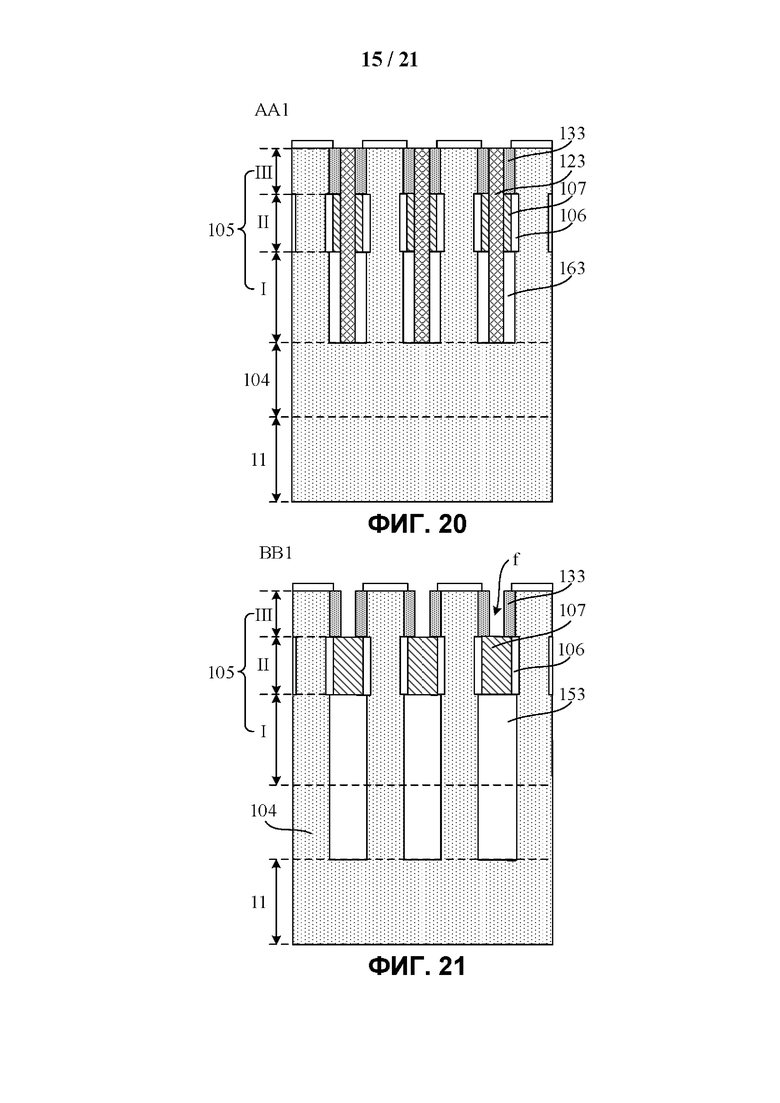

[0076] Обратимся к ФИГ. 20-22. ФИГ. 22 представляет собой вид с частичным сечением, на котором одна числовая шина 107 по ФИГ. 21, окружает четыре полупроводниковых канала 105.

[0077] Формируют числовые шины 107 таким образом, чтобы они заполняли вторые зазоры i.

[0078] В данном варианте осуществления формирование числовых шин 107 включает в себя формирование исходных числовых шин таким образом, чтобы они заполняли вторые зазоры i и сквозные отверстия f. Исходные числовые шины размещают между изолирующим слоем 106 и вторым диэлектрическим слоем 123 и между участками изолирующего слоя 106 на боковых стенках соседних канальных областей II на соседних линиях 104 битов. Участок исходных числовых шин, расположенный в сквозных отверстиях f, удаляют, и оставшийся участок исходных числовых шин образует числовые шины 107. Исходные числовые шины могут быть сформированы посредством процесса осаждения. Материал исходной числовые шины включает в себя по меньшей мере одно из поликремния, нитрида титана, нитрида тантала, меди или вольфрама.

[0079] Исходные числовые шины заполняют полые структуры h (см. ФИГ. 15) с самовыравниванием. После удаления участка исходных числовых шин, расположенных в сквозных отверстиях f, обеспечивается возможность формирования числовых шин 107 сточным размером с самовыравниванием. Отсутствует необходимость в задании размера числовые шины 107 посредством процесса травления, что упрощает изготовление числовых шин 107. В дополнение, регулирование размера второго зазора i обеспечивает получение числовые шины 107 малого размера.

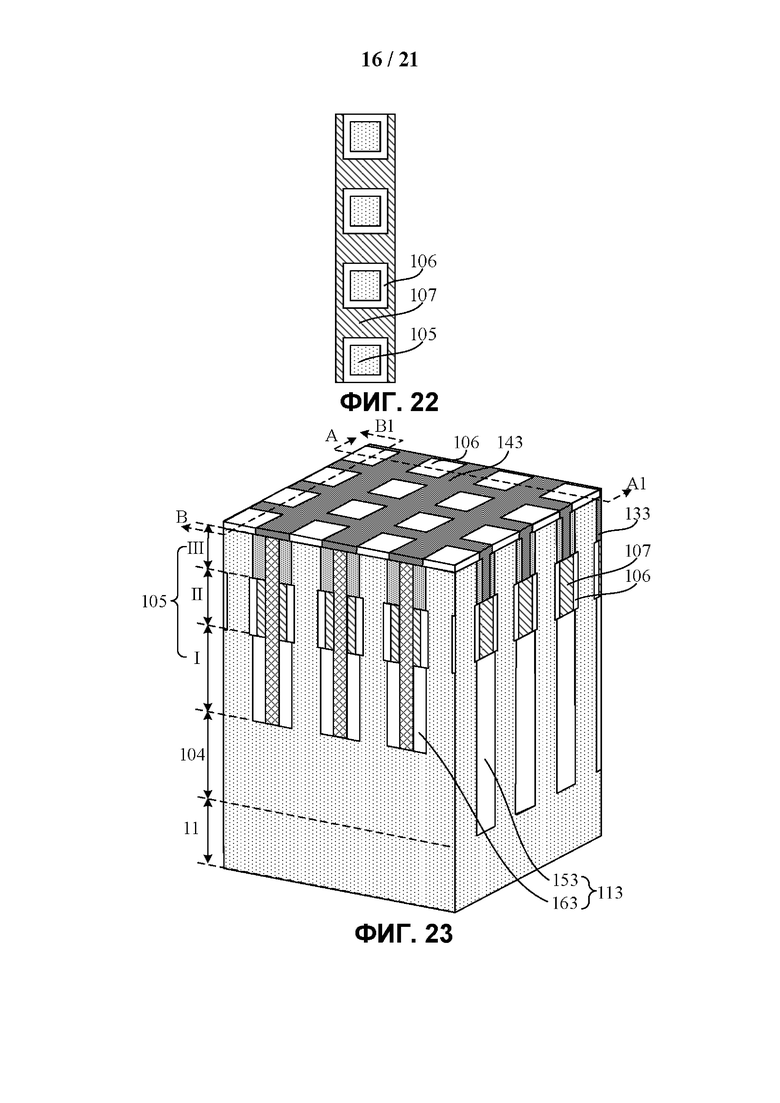

[0080] Со ссылкой на ФИГ. 23, после того как числовые шины 107 сформированы, формируют также четвертый диэлектрический слой 143 таким образом, чтобы он заполнял сквозные отверстия f (см. ФИГ. 21).

[0081] В данном варианте осуществления четвертый диэлектрический слой 143 может быть сформирован путем формирования, посредством процесса осаждения, четвертой диэлектрической пленки, покрывающей верхнюю поверхность участка изолирующего слоя 106, расположенного на верхних поверхностях вторых областей III легирования и заполняющих сквозные отверстия f. Четвертую диэлектрическую пленку подвергают процессу химико-механической планаризации до тех пор, пока не будет открыта верхняя поверхность изолирующего слоя 106, и оставшийся участок четвертой диэлектрической пленки образует четвертый диэлектрический слой 143. Четвертый диэлектрический слой, второй диэлектрический слой и третий диэлектрический слой выполняют из одного и того же материала, который включает в себя нитрид кремния. В других вариантах осуществления четвертая диэлектрическая пленка также может быть подвергнута процессу химико-механической планаризации для открытия верхних поверхностей вторых областей легирования. Иначе говоря, одновременно удаляют участок изолирующего слоя, расположенный на верхних поверхностях вторых областей легирования, и оставшийся участок четвертой диэлектрической пленки образует четвертый диэлектрический слой.

[0082] Со ссылкой на ФИГ. 23-25, удаляют участок изолирующего слоя 106, расположенный на верхних поверхностях вторых областей III легирования. На верхних поверхностях вторых областей III легирования посредством процесса эпитаксиального выращивания формируют контактный слой 108 конденсатора. Ортогональная проекция контактного слоя 108 конденсатора на линии 104 битов покрывает ортогональные проекции вторых областей III легирования на линии 104 битов.

[0083] Процесс эпитаксиального выращивания улучшает непрерывность между вторыми областями III легирования и контактным слоем 108 конденсатора. Это уменьшает контактные дефекты, обусловленные различными характеристиками решетки или дислокациями решетки, уменьшает контактное сопротивление, создаваемое контактными дефектами, и улучшает способность к переносу и скорость перемещения носителей. Таким образом улучшается проводимость между вторыми областями III легирования и контактным слоем 108 конденсатора и уменьшается количество тепла, выделяющегося во время работы полупроводниковой структуры. В дополнение, процесс эпитаксиального выращивания увеличивает ортогональную проекцию контактного слоя 108 конденсатора на линии 104 битов, так что при формировании нижнего электрода конденсаторной структуры на контактном слое 108 конденсатора это полезно для увеличения площади контакта между контактным слоем 108 конденсатора и нижним электродом и, таким образом, для уменьшения контактного сопротивления между контактным слоем 108 конденсатора и нижним электродом.

[0084] Во время эпитаксиального выращивания контактный слой 108 конденсатора дополнительно легируют легирующим ионом того же типа, что и во второй области III легирования. Концентрация легирования для легирующего иона в контактном слое 108 конденсатора больше, чем во второй области III легирования, и поэтому сопротивление контактного слоя 108 конденсатора будет меньше, чем сопротивление второй области III легирования, что дополнительно уменьшает сопротивление переносу между второй областью III легирования и нижним электродом.

[0085] Конденсаторные структуры (не показаны на чертеже) формируют на поверхности, образованной контактным слоем 108 конденсатора и четвертым диэлектрическим слоем 143.

[0086] В других вариантах осуществления после того, как сформированы числовые шины, второй диэлектрический слой и третий диэлектрический слой могут быть удалены посредством влажного процесса травления, чтобы сформировать четвертые зазоры, открывающие линии битов и всю основную поверхность первого диэлектрического слоя. С помощью процесса осаждения формируют седьмой диэлектрический слой, заполняющий четвертые зазоры. Поскольку седьмой диэлектрический слой является монолитным, этот седьмой диэлектрический слой имеет более высокую плотность и меньшее количество внутренних дефектов, что способствует усилению изоляционного эффекта седьмого диэлектрического слоя в отношении соседних полупроводниковых каналов и соседних линий битов. В некоторых примерах седьмой диэлектрический слой и второй диэлектрический слой могут быть выполнены из одного и того же материала, такого как нитрид кремния.

[0087] В других вариантах осуществления контактный слой конденсатора может не быть сформирован. После удаления участка изолирующего слоя, расположенного на верхних поверхностях вторых областей легирования, конденсаторную структуру формируют непосредственно на верхней поверхности второй области легирования.

[0088] Таким образом, формируют первый диэлектрический слой 113 и второй диэлектрический слой 123, и первый диэлектрический слой 113 повергают травлению с использованием второго диэлектрического слоя 123 в качестве маски для формирования полых структур п. Числовые шины 107 формируют с точным размером в полых структурах с самовыравниванием посредством процесса осаждения. Отсутствует необходимость в задании размера числовые шины 107 посредством процесса травления, и таким образом упрощается формирование числовых шин 107. Кроме того, обеспечивается возможность получения числовые шины 107 малого размера путем регулирования размера второго зазора i.

[0089] Далее в настоящем раскрытии представлен способ изготовления полупроводниковой структуры, который является по существу таким же, что и в предыдущем варианте осуществления, и основное различие состоит в другом процессе удаления участка первого диэлектрического слоя для открытия боковых стенок канальных областей. Способ изготовления полупроводниковой структуры, предложенный в другом варианте осуществления настоящего раскрытия, подробно описан ниже со ссылкой на сопроводительные чертежи. Части, аналогичные или соответствующие тем, которые упомянуты в предыдущем варианте осуществления, могут быть отнесены к предыдущему варианту осуществления.

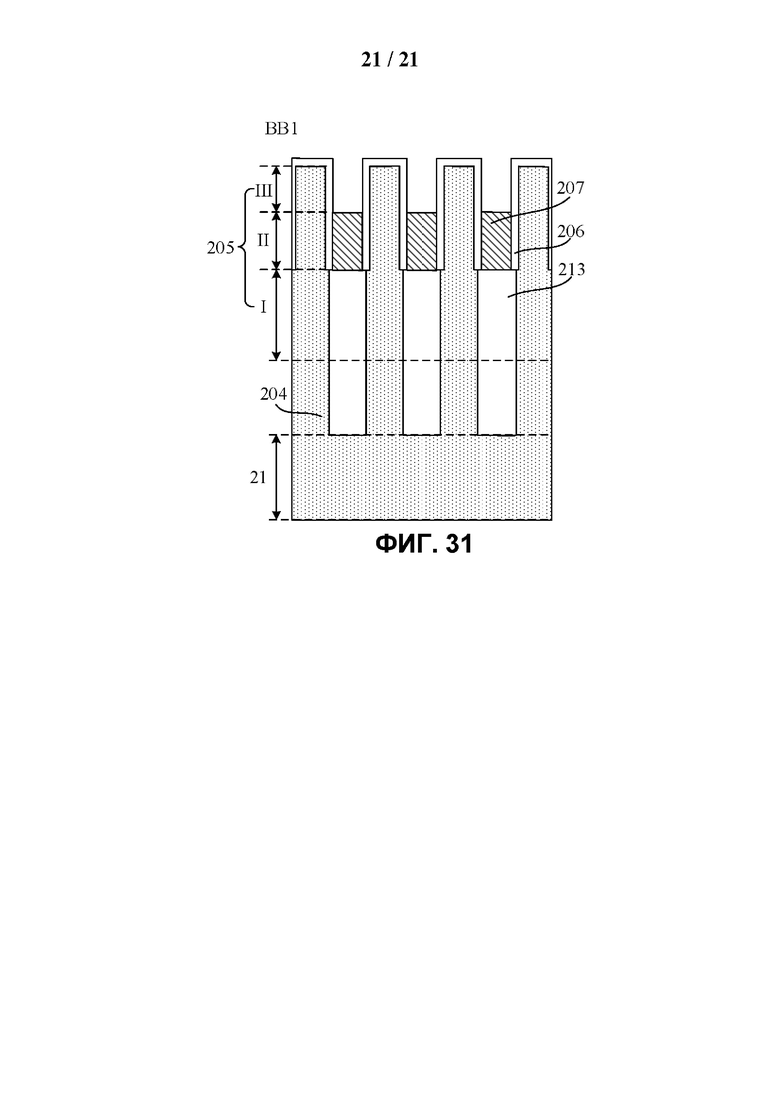

[0090] На ФИГ. 26-31 показаны схематические структурные чертежи, соответствующие этапам способа изготовления полупроводниковой структуры согласно еще одному варианту осуществления настоящего раскрытия. Следует отметить, что для упрощения описания и наглядности иллюстрирования этапов способа изготовления полупроводниковой структуры, все ФИГ. 26-31 в данном варианте осуществления представляют собой частичные схематические структурные чертежи полупроводниковой структуры. Один или оба из вида в сечении структуры вдоль первого направления АА1 сечения или вида в сечении структуры вдоль второго направления ВВ1 сечения будут рассмотрены позже в соответствии с требованиями описания. При ссылке лишь на один сопроводительный чертеж, он представляет собой вид в сечении вдоль первого направления ВВ1 сечения. При одновременной ссылке на два сопроводительных чертежа первый сопроводительный чертеж представляет собой вид в сечении вдоль первого направления АА1 сечения, а второй сопроводительный чертеж представляет собой вид в сечении вдоль второго направления ВВ1 сечения.

[0091] В данном варианте осуществления, со ссылкой на ФИГ. 26 и ФИГ. 27, на основе формируют линии 204 битов, полупроводниковые каналы 205, первый диэлектрический слой 213 и второй диэлектрический слой 223. В основе расположен полупроводниковый слой 21 с карманом. Первый диэлектрический слой 213 включает в себя пятый диэлектрический слой 253 и шестой диэлектрический слой 263. Формирование линий 204 битов, полупроводниковых каналов 205, первого диэлектрического слоя 213 и второго диэлектрического слоя 223 осуществляют аналогично предыдущим вариантам осуществления. Оно не будет повторно описано в данном документе.

[0092] Со ссылкой на ФИГ. 27, при удалении участка первого диэлектрического слоя 213 для открытия боковых стенок канальных областей II, участок первого диэлектрического слоя 213, расположенный на боковых стенках вторых областей III легирования, также удаляют, то есть оставшийся участок первого диэлектрического слоя 213 будет расположен только на поверхностях боковых стенок первых областей I легирования.

[0093] Со ссылкой на ФИГ. 28 и ФИГ. 29, формируют изолирующий слой 206. Изолирующий слой 206 не только покрывает поверхности боковых стенок канальных областей II, но он также расположен на поверхностях боковых стенок и верхних поверхностях вторых областей III легирования. Между изолирующим слоем 206 и вторым диэлектрическим слоем 223 обеспечивают вторые зазоры i.

[0094] В данном варианте осуществления полупроводниковый канал 205 выполняют из кремния, а изолирующий слой 206 формируют путем термического окисления открытых боковых стенок канальных областей II и открытых боковых стенок и верхних поверхностей вторых областей III легирования для формирования изолирующего слоя 206, который покрывает поверхности боковых стенок оставшегося участка канальных областей II и оставшегося участка вторых областей III легирования. В других вариантах осуществления изолирующий слой, покрывающий боковые стенки канальных областей и боковые стенки и верхние поверхности вторых областей легирования, также может быть сформирован посредством процесса осаждения.

[0095] В результате термического окисления открытых боковых стенок канальных областей II и вторых областей III легирования, участок канальных областей II и участок вторых областей III легирования преобразуются в изолирующий слой 206. Ортогональные проекции канальной области II и второй области III легирования на линию 204 битов меньше, чем ортогональная проекция первой области I легирования на линию 204 битов. В результате обеспечивается возможность формирования канальной области II и второй области III легирования с меньшими площадями сечения в сечениях, перпендикулярных направлению Z от линии 204 битов к полупроводниковому каналу 205, без процесса травления. Таким образом, это полезно для уменьшения порогового напряжения транзистора, образованного полупроводниковым каналом 205, так что обеспечивается возможность отпирания и запирания транзистора при более низком пороговом напряжении.

[0096] В некоторых примерах ширина W и длина канальной области II в сечении, перпендикулярном направлению Z, не превышают 10 нм, и это гарантирует, что транзисторы будут иметь меньшие пороговые напряжения. Высота канальной области II составляет от 30 до 50 нм в направлении Z.

[0097] В данном варианте осуществления участок изолирующего слоя 206 на верхних поверхностях оставшегося участка вторых областей III легирования удаляют в последующем процессе. В других вариантах осуществления участок изолирующего слоя на верхних поверхностях оставшегося участка вторых областей легирования может быть удален после термического окисления, и будет оставлен только участок изолирующего слоя, покрывающий поверхности боковых стенок оставшегося участка канальных областей и оставшегося участка вторых областей легирования.

[0098] Со ссылкой на ФИГ. 30 и ФИГ. 31, формируют числовой шины 207. Формирование числовых шин 207 осуществляют следующим образом.

[0099] Формируют исходные числовые шины таким образом, чтобы они заполняли вторые зазоры i (см. ФИГ. 29), то есть размещают исходные числовые шины между участками изолирующего слоя 206, покрывающими боковые стенки канальных областей II и вторых областей III легирования на соседних исходных линиях 204 битов. Исходные числовые шины могут быть сформированы посредством процесса осаждения.

[00100] Участок исходных числовых шин удаляют, а оставшийся участок исходных числовых шин используют в качестве числовых шин 207, которые окружают только участок изолирующего слоя 206, расположенный на боковых стенках канальных областей II.

[00101] Исходные числовые шины заполняют вторые зазоры i с самовыравниванием, так что обеспечивается возможность последующего формирования числовых шин 207 с точным размером с самовыравниванием. Отсутствует необходимость в задании размера числовой шины 207 посредством процесса травления, что упрощает изготовление числовых шин 207. Кроме того, регулирование размера второго зазора i обеспечивает возможность получения числовой шины 207 малого размера.

[00102] Формируют четвертый диэлектрический слой таким образом, чтобы он заполнял зазоры между участками изолирующего слоя 206, расположенными на боковых стенках вторых областей III легирования. Затем удаляют участок изолирующего слоя 206, расположенный на верхних поверхностях вторых областей III легирования. Формирование четвертого диэлектрического слоя и удаление участка изолирующего слоя 206 осуществляют таким же образом, что и в предыдущих вариантах осуществления. В других вариантах осуществления, перед формированием четвертого диэлектрического слоя возможно также удаление участка изолирующего слоя, расположенного на боковых стенках и верхних поверхностях вторых областей легирования, для формирования четвертого диэлектрического слоя, открывающего верхние поверхности первых областей легирования.

[00103] В данном варианте осуществления, на верхних поверхностях вторых областей III легирования на тех же самых этапах, что и в предыдущих вариантах осуществления, могут быть также сформированы контактный слой конденсатора и контактные структуры конденсатора.

[00104] Таким образом, формируют первый диэлектрический слой 213 и второй диэлектрический слой 223 и подвергают травлению первый диэлектрический слой 213 с использованием второго диэлектрического слоя 223 в качестве маски для формирования вторых зазоров i. Формируют числовой шины 207 сточным размером во вторых зазорах i с самовыравниванием посредством процесса осаждения. Отсутствует необходимость в задании размера числовой шины 207 посредством процесса травления и таким образом упрощается формирование числовых шин 207. Кроме того, регулирование размера второго зазора i обеспечивает возможность получения числовой шины 207 малого размера.

[00105] В настоящем раскрытии дополнительно предложена полупроводниковая структура, которая выполнена с использованием способа изготовления полупроводниковой структуры согласно любому из предыдущих вариантов осуществления.

[00106] Со ссылкой на ФИГ. 24 и ФИГ. 25, полупроводниковая структура включает в себя: основу, причем основа включает в себя полупроводниковый слой 11 с карманом, линии 104 битов, расположенные на полупроводниковом слое 11 с карманом; полупроводниковые каналы 105, расположенные на поверхностях линий 104 битов, причем полупроводниковый канал 105 включает в себя первую область I легирования, канальную область II и вторую область III легирования, расположенные последовательно вдоль направления Z от основы к линии 104 битов, при этом первая область I легирования находится в контакте с линией 104 битов.

[00107] В данном варианте осуществления основа, линия 104 битов и полупроводниковый канал 105 имеют один и тот же полупроводниковый элемент, и, следовательно, полупроводниковые каналы 105 и линии 104 битов сформированы с использованием одной и той же пленочной структуры. Пленочная структура образована указанным полупроводниковым элементом, так что полупроводниковые каналы 105 и линии 104 битов объединены, что предотвращает дефекты состояния поверхности раздела между полупроводниковыми каналами 105 и линиями 104 битов и улучшает характеристики полупроводниковой структуры.

[00108] Полупроводниковый элемент может включать в себя по меньшей мере одно из кремния, углерода, германия, мышьяка, галлия или индия. Основа, линия 104 битов и полупроводниковый канал 105 могут быть выполнены из простого полупроводникового материала или кристаллического неорганического смешанного полупроводникового материала. Простой полупроводниковый материал может включать в себя кремний или германий, а кристаллический неорганический смешанный полупроводниковый материал может включать в себя карбид кремния, кремний-германий, арсенид галлия или индий-галлий.

[00109] Первая область I легирования, канальная область II и вторая область III легирования легированы легирующим ионом одного и того же типа, и концентрация легирования для легирующего иона в первой области I легирования сопоставима с концентрацией легирующих ионов в канальной области II и во второй области III легирования. Кроме того, поскольку устройство, образованное полупроводниковым каналом 105, представляет собой беспереходный транзистор, это позволяет избежать использования процесса легирования стока-истока со сверхвысоким градиентом для выполнения PN-перехода со сверхвысоким градиентом в наноразмерном диапазоне. Следовательно, обеспечивается возможность устранения таких проблем, как дрейф порогового напряжения и увеличение тока утечки, вызванные резкими изменениями концентрации легирования, и возможность легкого подавления эффекта короткого канала, так что устройство способно работать в диапазоне нескольких нанометров. Такая конструкция дополнительно улучшает степень интеграции и электрические характеристики полупроводниковой структуры. Легирующий ион представляет собой одно из иона N-типа и иона Р-типа.

[00110] Ортогональная проекция канальной области II на линию 104 битов меньше, чем ортогональная проекция второй области III легирования на линию 104 битов и ортогональная проекция первой области I легирования на линию 104 битов. Канальная область II может быть сформирована без использования процесса травления, с меньшей площадью сечения в сечении, перпендикулярном направлению Z от линии 104 битов к полупроводниковому каналу 105. В результате числовая шина 107 способна лучше управлять канальной областью II, таким образом способствуя управлению отпиранием или запиранием транзистора с круговым затвором.

[00111] В некоторых примерах ширина W и длина L канальной области II в сечении, перпендикулярном направлению Z, не превышают 10 нм, и это гарантирует, что транзисторы будут иметь меньшие пороговые напряжения. Высота канальной области II составляет от 30 до 50 нм в направлении Z.

[00112] Со ссылкой на ФИГ. 6 и ФИГ. 24-25, полупроводниковая структура дополнительно включает в себя первый диэлектрический слой 113, окружающий первые области I легирования. Между участками первого диэлектрического слоя 113, покрывающими боковые стенки соседних первых областей I легирования на той же линии 104 битов, обеспечен первый зазор.

[00113] Первый диэлектрический слой 113 может включать в себя пятый диэлектрический слой 153 и шестой диэлектрический слой 163. Пятый диэлектрический слой 153 расположен в зазорах между соседними линиями 104 битов, а также в зазорах между соседними первыми областями I легирования на соседних линиях 104 битов. Шестой диэлектрический слой 163 расположен на боковых стенках соседних первых областей I легирования на той же самой линии 104 битов, а также он расположен на боковой стенке пятого диэлектрического слоя 153. Первый диэлектрический слой 113 используется для достижения электрической изоляции между соседними полупроводниковыми каналами 105 и соседними линиями 104 битов.

[00114] Полупроводниковая структура дополнительно включает в себя изолирующий слой 106, который покрывает по меньшей мере поверхности боковых стенок канальных областей II. В данном варианте осуществления изолирующий слой 106 покрывает только поверхности боковых стенок канальных областей II. В других вариантах осуществления изолирующий слой может покрывать поверхности боковых стенок обеих из канальных областей и вторых областей легирования.

[00115] Полупроводниковая структура дополнительно включает в себя числовые шины 107, окружающие изолирующие слои 106, покрывающие боковые стенки канальных областей II, при этом между соседними числовыми шинами 107 обеспечен второй зазор; изоляционный слой 109, расположенный по меньшей мере в первых зазорах и вторых зазорах, при этом верхние поверхности изоляционного слоя 109, удаленные от основы, расположены не ниже, чем поверхности второй области III легирования, удаленные от основы.

[00116] Изоляционные слои 109 могут включать в себя второй диэлектрический слой 123 и третий диэлектрический слой 133. Второй диэлектрический слой 123 расположен в первых зазорах и вторых зазорах. Верхняя поверхность второго диэлектрического слоя 123, удаленная от основы, расположена не ниже поверхности второй области III легирования, удаленной от основы. Третий диэлектрический слой 133 покрывает боковые стенки вторых областей III легирования.

[00117] В некоторых примерах верхняя поверхность второго диэлектрического слоя 123 расположена заподлицо с поверхностью второй области III легирования. Изоляционный слой 109 дополнительно включает в себя четвертый диэлектрический слой 143. Со ссылкой на ФИГ. 25, четвертый диэлектрический слой 143 расположен на верхней поверхности, образованной вторым диэлектрическим слоем 123 и третьим диэлектрическим слоем 133, и в зазорах между соседними участками третьего диэлектрического слоя 133. Второй диэлектрический слой 123, третий диэлектрический слой 133 и четвертый диэлектрический слой 143 выполнены из одного и того же материала и образуют изоляционный слой 109 для достижения электрической изоляции между соседними полупроводниковыми каналами 105 и соседними линиями 104 битов. В других вариантах осуществления второй диэлектрический слой, третий диэлектрический слой и четвертый диэлектрический слой объединены, так что изоляционный слой имеет сравнительно высокую плотность и меньшее количество внутренних дефектов, что способствует усилению изоляционного эффекта изолирующего слоя в отношении соседних полупроводниковых каналов и соседних линий битов.

[00118] В некоторых других вариантах осуществления, при покрытии поверхностей боковых стенок обеих из канальных областей и вторых областей легирования, изоляционный слой включает в себя одно из второго диэлектрического слоя и одно из четвертого диэлектрического слоя. Второй диэлектрический слой расположен в первых зазорах и вторых зазорах. Верхняя поверхность второго диэлектрического слоя, удаленная от основы, расположена не ниже поверхности второй области легирования, удаленной от основы. Четвертый диэлектрический слой расположен в зазорах, образованных вторым диэлектрическим слоем и изолирующим слоем, и в зазорах, образованных соседними участками изолирующего слоя, и четвертый диэлектрический слой покрывает верхнюю поверхность второго диэлектрического слоя.

[00119] Ортогональная проекция периферии изолирующего слоя 106 на линии 104 битов меньше, чем ортогональная проекция периферии третьего диэлектрического слоя 133 на линии 104 битов.

[00120] Полупроводниковая структура может дополнительно включать в себя контактный слой 108 конденсатора, расположенный на верхних поверхностях вторых областей III легирования. Ортогональная проекция контактного слоя 108 конденсатора на линии 104 битов покрывает ортогональные проекции вторых областей III легирования на линии 104 битов. Контактный слой 108 конденсатора легирован легирующим ионом, концентрация легирования для которого больше, чем во второй области III легирования.

[00121] Поскольку контактный слой 108 конденсатора и вторая область III легирования легированы легирующим ионом одного и того же типа и концентрация легирования для легирующего иона в контактном слое 108 конденсатора больше, чем во второй области III легирования, обеспечена возможность дополнительного улучшения проводимости контактного слоя 108 конденсатора. Ортогональная проекция контактного слоя 108 контакта конденсатора на линии 104 битов покрывает ортогональные проекции вторых областей III легирования на линии 104 битов, что полезно для увеличения площади контакта между контактным слоем 108 конденсатора и другими последующими проводящими структурами, в результате чего уменьшается контактное сопротивление между контактным слоем 108 конденсатора и другими последующими проводящими структурами.

[00122] Полупроводниковая структура может дополнительно включать в себя конденсаторную структуру (не показана на чертеже), причем конденсаторная структура расположена на поверхности, образованной контактным слоем 108 конденсатора и четвертым диэлектрическим слоем 143.

[00123] Таким образом, в сечении, перпендикулярном направлению Z от линии 104 битов к полупроводниковому каналу 105, площадь поперечного сечения канальной области II меньше, чем площадь поперечного сечения первой области I легирования и второй области II легирования, что полезно для уменьшения порогового напряжения транзистора, образованного полупроводниковым каналом 105, так что транзистор отпирается или запирается при более низком пороговом напряжении. Устройство, образованное полупроводниковым каналом 105, представляет собой беспереходный транзистор, который позволяет избежать использования процесса легирования стока-истока со сверхвысоким градиентом. Следовательно, обеспечивается возможность предотвращения таких проблем, как дрейф порогового напряжения и увеличение тока утечки, вызванные резкими изменениями концентрации легирования, и возможность легкого подавления эффекта короткого канала. Такая конструкция дополнительно повышает степень интеграции и электрические характеристики полупроводниковой структуры.

[00124] Следует понимать, что настоящее раскрытие не ограничивается его применением к конкретной структуре и расположению компонентов, раскрытых в настоящем описании. Настоящее раскрытие может включать в себя другие варианты осуществления, и оно может быть реализовано и выполнено множеством способов. Вышеупомянутые вариации и модификации входят в объем настоящего раскрытия. Можно считать, что настоящее изобретение, раскрытое и определенное в настоящем описании, распространяется на все альтернативные комбинации двух или более отдельных признаков, упомянутых или очевидных в тексте и/или на сопроводительных чертежах. Все из этих различных комбинаций составляют множество альтернативных аспектов настоящего раскрытия. Варианты осуществления, раскрытые в настоящем описании, иллюстрируют известный оптимальный способ реализации настоящего раскрытия и дают возможность специалистам в данной области техники использовать настоящее раскрытие.

[00125] Промышленная применимость

[00126] В вариантах осуществления настоящего раскрытия предложены полупроводниковая структура и способ ее изготовления, которые являются полезными для упрощения формирования числовых шин и для формирования числовых шин с малыми размерами и высокой точностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 2021 |

|

RU2807501C1 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 2021 |

|

RU2808029C1 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 2021 |

|

RU2808084C1 |

| ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 2022 |

|

RU2810689C1 |

| ВЕРТИКАЛЬНАЯ СТРУКТУРА ПОЛУПРОВОДНИКОВОГО УСТРОЙСТВА И СПОСОБ ЕЕ ФОРМИРОВАНИЯ | 2005 |

|

RU2338683C2 |

| ТВЕРДОТЕЛЬНЫЙ ДАТЧИК ИЗОБРАЖЕНИЯ, СПОСОБ ЕГО ПРОИЗВОДСТВА И СИСТЕМА ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ | 2011 |

|

RU2488190C1 |

| Способ изготовления КМОП-структур | 2015 |

|

RU2665584C2 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| ВСТРАИВАЕМАЯ С СБИС ТЕХНОЛОГИИ КМОП/КНИ ПАМЯТЬ "MRAM" И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2532589C2 |

В настоящем изобретении предложены полупроводниковая структура и способ ее изготовления. Способ изготовления включает в себя: обеспечение основы; формирование линий битов на основе и формирование полупроводниковых каналов на поверхностях линий битов, удаленных от основы, таким образом, чтобы полупроводниковый канал включал в себя первую область легирования, канальную область и вторую область легирования, расположенные последовательно; формирование первого диэлектрического слоя таким образом, чтобы первый диэлектрический слой окружал боковые стенки полупроводниковых каналов, и между участками первого диэлектрического слоя, расположенными на боковых стенках соседних полупроводниковых каналов на одной и той же линии битов, был обеспечен первый зазор; формирование второго диэлектрического слоя таким образом, чтобы второй диэлектрический слой заполнял первые зазоры, при этом материал второго диэлектрического слоя отличается от материала первого диэлектрического слоя; удаление участка первого диэлектрического слоя для открытия боковых стенок канальных областей; формирование изолирующего слоя таким образом, чтобы он покрывал, по меньшей мере, поверхности боковых стенок канальных областей, и между изолирующим слоем и вторым диэлектрическим слоем были обеспечены вторые зазоры; и формирование числовых шин таким образом, чтобы числовые шины заполняли вторые зазоры. 2 н. и 9 з.п. ф-лы, 31 ил.

1. Способ изготовления полупроводниковой структуры, включающий:

обеспечение основы;

формирование линий битов на основе и формирование полупроводниковых каналов на поверхностях линий битов, удаленных от основы, причем полупроводниковый канал содержит первую область легирования, канальную область и вторую область легирования, последовательно расположенные вдоль направления от основы к линии битов;

формирование первого диэлектрического слоя таким образом, чтобы первый диэлектрический слой окружал боковые стенки полупроводниковых каналов, и между участками первого диэлектрического слоя, расположенными на боковых стенках соседних полупроводниковых каналов на одной и той же линии битов, был обеспечен первый зазор;

формирование второго диэлектрического слоя таким образом, чтобы второй диэлектрический слой заполнял первые зазоры, при этом материал второго диэлектрического слоя отличается от материала первого диэлектрического слоя;

удаление участка первого диэлектрического слоя для открытия боковых стенок канальных областей;

формирование изолирующего слоя таким образом, чтобы изолирующий слой покрывал, по меньшей мере, поверхности боковых стенок канальных областей, и между изолирующим слоем и вторым диэлектрическим слоем были обеспечены вторые зазоры; и

формирование числовых шин таким образом, чтобы они заполняли вторые зазоры.

2. Способ изготовления полупроводниковой структуры по п. 1, согласно которому удаление участка первого диэлектрического слоя для открытия боковых стенок канальных областей включает:

травление участка первого диэлектрического слоя для открытия боковых стенок вторых областей легирования;

формирование третьего диэлектрического слоя таким образом, чтобы: третий диэлектрический слой окружал боковые стенки вторых областей легирования и был расположен на участке боковой стенки второго диэлектрического слоя; участок третьего диэлектрического слоя, расположенный на боковых стенках вторых областей легирования, и участок третьего диэлектрического слоя, расположенный на участке боковой стенки второго диэлектрического слоя, образовывали сквозные отверстия; и участок первого диэлектрического слоя был открыт на дне сквозных отверстий, при этом материал третьего диэлектрического слоя отличается от материала первого диэлектрического слоя; и

удаление участка первого диэлектрического слоя, расположенного на боковых стенках канальных областей и открытого посредством сквозных отверстий, таким образом, чтобы оставшийся участок первого диэлектрического слоя окружал боковые стенки первых областей легирования,

причем формирование изолирующего слоя включает:

термическое окисление боковых стенок открытых канальных областей для формирования изолирующего слоя таким образом, чтобы изолирующий слой покрывал поверхности боковых стенок оставшегося участка канальных областей,

причем формирование числовых шин включает:

формирование исходных числовых шин таким образом, чтобы исходные числовые шины заполняли вторые зазоры и сквозные отверстия, и исходные числовые шины также были расположены между участками изолирующего слоя, покрывающими боковые стенки канальных областей на соседних линиях битов; и

удаление участка исходных числовых шин, расположенных в сквозных отверстиях, при этом оставшийся участок исходных числовых шин используют в качестве числовых шин,

причем после формирования числовых шин способ дополнительно включает: формирование четвертого диэлектрического слоя таким образом, чтобы четвертый диэлектрический слой заполнял сквозные отверстия.

3. Способ изготовления полупроводниковой структуры по п. 1, согласно которому удаление участка первого диэлектрического слоя для открытия боковых стенок канальных областей дополнительно включает удаление участка первого диэлектрического слоя, расположенного на боковых стенках вторых областей легирования, и при формировании изолирующего слоя этот изолирующий слой дополнительно покрывает боковые стенки вторых областей легирования,

причем формирование числовых шин включает:

формирование исходных числовых шин таким образом, чтобы исходные числовые шины заполняли вторые зазоры, и исходные числовые шины были также расположены между участками изолирующего слоя, покрывающими участок боковых стенок полупроводниковых каналов на соседних линиях битов; и

удаление участка исходных числовых шин, при этом оставшийся участок исходных числовых шин используют в качестве числовых шин, и числовые шины окружают лишь участок изолирующего слоя, расположенный на боковых стенках канальных областей.

4. Способ изготовления полупроводниковой структуры по п. 1, согласно которому формирование линий битов и формирование полупроводниковых каналов включает:

формирование первого маскирующего слоя на основе;

травление основы с использованием первого маскирующего слоя в качестве маски и формирование множества первых канавок;

удаление первого маскирующего слоя и формирование пятого диэлектрического слоя в первых канавках;

формирование второго маскирующего слоя на верхней поверхности, образованной пятым диэлектрическим слоем и оставшимся участком основы;

травление основы и пятого диэлектрического слоя с использованием второго маскирующего слоя в качестве маски и формирование множества вторых канавок, линий битов и полупроводниковых каналов таким образом, чтобы глубина второй канавки была меньше глубины первой канавки в направлении, перпендикулярном поверхности основы; и

удаление второго маскирующего слоя,

причем первый маскирующий слой содержит множество первых отверстий, отделенных друг от друга, второй маскирующий слой содержит множество вторых отверстий, отделенных друг от друга, и направление прохождения первого отверстия перпендикулярно направлению прохождения второго отверстия,

причем в направлении, перпендикулярном боковой стенке полупроводникового канала, отношение ширины первого отверстия к ширине второго отверстия составляет 2 к 1, и расстояние между соседними первыми отверстиями равно расстоянию между соседними вторыми отверстиями,

причем формирование первого диэлектрического слоя включает:

формирование шестого диэлектрического слоя таким образом, чтобы шестой диэлектрический слой был расположен на боковых стенках вторых канавок, оставшийся участок пятого диэлектрического слоя и шестого диэлектрического слоя образовывали первый диэлектрический слой, и участок шестого диэлектрического слоя, расположенный на боковой стенке второй канавки, был обеспечен первым зазором.

5. Способ изготовления полупроводниковой структуры по п. 1, дополнительно включающий:

формирование контактного слоя конденсатора на верхних поверхностях вторых областей легирования посредством процесса эпитаксиального выращивания таким образом, чтобы ортогональная проекция контактного слоя конденсатора на линии битов покрывала ортогональные проекции вторых областей легирования на линии битов.

6. Полупроводниковая структура, содержащая:

основу;

линии битов, расположенные на основе;

полупроводниковые каналы, расположенные на поверхностях линий битов, причем полупроводниковый канал содержит первую область легирования, канальную область и вторую область легирования, последовательно расположенные вдоль направления от основы к линии битов, при этом первая область легирования находится в контакте с линией битов;

первый диэлектрический слой, окружающий первые области легирования, причем между участками первого диэлектрического слоя, покрывающими боковые стенки соседних первых областей легирования на одной и той же линии битов, обеспечен первый зазор;

изолирующий слой, покрывающий, по меньшей мере, поверхности боковых стенок канальных областей;

числовые шины, окружающие изолирующий слой, расположенный на боковых стенках канальных областей, причем между соседними числовыми шинами обеспечен второй зазор; и

изоляционный слой, расположенный, по меньшей мере, в первых зазорах и вторых зазорах, причем верхняя поверхность изоляционного слоя, удаленная от основы, расположена не ниже, чем верхняя поверхность второй области легирования, удаленная от основы.

7. Полупроводниковая структура по п. 6, в которой основа, линия битов и полупроводниковый канал содержат один и тот же полупроводниковый элемент.