ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

Данное раскрытие основано на заявке на патент Китая № 202110777160.7, поданной 9 июля 2021 и поименованной "ПОЛУПРОВОДНИКОВАЯ СТРУКТУРА И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ", и испрашивает приоритет по данной заявке на патент Китая, раскрытие которой посредством ссылки полностью включено в настоящий документ.

ОБЛАСТЬ ТЕХНИКИ

[0002] Варианты реализации данного раскрытия относятся к полупроводниковой структуре и способу ее изготовления.

УРОВЕНЬ ТЕХНИКИ

[0003] В архитектуре фон Неймана логическое управляющее устройство и запоминающее устройство являются отдельными блоками. Логическое управляющее устройство считывает данные из запоминающего устройства, выполняет соответствующую обработку этих данных и сохраняет обработанные данные в запоминающем устройстве. В частности, данные передаются туда и обратно между логическим управляющим устройством и запоминающим устройством. Запоминающее устройство и логическое управляющее устройство соответственно расположены в различных чипах. Передача данных между различными чипами приводит к высокому энергопотреблению и низкой производительности.

[0004] Таким образом, существует потребность в полупроводниковом устройстве, которое может осуществлять вычисление в запоминающем устройстве (In-Memory Computing, IMC).

РАСКРЫТИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0005] В вариантах реализации этого раскрытия предложена полупроводниковая структура, включающая в себя: полупроводниковую основу, включающую в себя область логического устройства и область памяти; линию битов и слой электрического контакта, расположенный в том же самом слое, что и линия битов, при этом линия битов расположена на полупроводниковой основе в области памяти, а слой электрического контакта расположен на полупроводниковой основе в области логического устройства; первый полупроводниковый канал, расположенный на поверхности линии битов в направлении от полупроводниковой основы к линии битов, при этом первый полупроводниковый канал включает в себя первую область легирования, первую канальную область и вторую область легирования, которые расположены последовательно, при этом первая область легирования находится в контакте с линией битов; второй полупроводниковый канал, расположенный в том же самом слое, что и первый полупроводниковый канал, и на поверхности слоя электрического контакта в направлении от полупроводниковой основы к слою электрического контакта, при этом второй полупроводниковый канал включает в себя третью область легирования, вторую канальную область и четвертую область легирования, которые расположены последовательно, причем третья область легирования находится в контакте со слоем электрического контакта; линию слов и затвор, расположенный в том же самом слое, что и линия слов, при этом линия слов расположена вокруг первой канальной области, а затвор расположен вокруг второй канальной области; емкостную структуру, расположенную на стороне второй области легирования на удалении от первой канальной области и находящуюся в контакте со второй областью легирования; структуру электрического соединения, расположенную на стороне четвертой области легирования на удалении от второй канальной области и находящуюся в контакте с четвертой областью легирования; и диэлектрический слой, расположенный между линией битов и линией слов, а также расположенный на стороне линии слов на удалении от полупроводниковой основы.

[0006] Соответственно, варианты реализации раскрытия также обеспечивают способ изготовления полупроводниковой структуры, включающий: обеспечение полупроводниковой основы, при этом полупроводниковая основа включает в себя область логического устройства и область памяти; формирование линии битов и слоя электрического контакта, расположенного в том же самом слое, что и линия битов, при этом линия битов расположена на полупроводниковой основе в области памяти, а слой электрического контакта расположен на полупроводниковой основе в области логического устройства; формирование первого полупроводникового канала и второго полупроводникового канала, расположенного в том же самом слое, что и первый полупроводниковый канал, при этом первый полупроводниковый канал расположен на поверхности линии битов в направлении от полупроводниковой основы к линии битов, причем первый полупроводниковый канал включает в себя первую область легирования, первую канальную область и вторую область легирования, которые расположены последовательно, при этом первая область легирования находится в контакте с линией битов, а второй полупроводниковый канал расположен на поверхности слоя электрического контакта в направлении от полупроводниковой основы к слою электрического контакта, при этом второй полупроводниковый канал включает в себя третью область легирования, вторую канальную область и четвертую область легирования, которые расположены последовательно, причем третья область легирования находится в контакте со слоем электрического контакта; формирование линии слов и затвора, расположенного в том же самом слое, что и линия слов, при этом линия слов расположена вокруг первой канальной области, а затвор расположен вокруг второй канальной области; формирование емкостной структуры, при этом емкостная структура расположена на стороне второй области легирования на удалении от первой канальной области и находится в контакте со второй областью легирования; формирование структуры электрического соединения, причем структура электрического соединения расположена на стороне четвертой области легирования на удалении от второй канальной области, при этом структура электрического соединения находится в контакте с четвертой областью легирования; и формирование диэлектрического слоя, причем диэлектрический слой расположен между линией битов и линией слов, а также расположен на стороне линии слов на удалении от полупроводниковой основы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0007] Один или более вариантов реализации для примера описаны с использованием изображений, которые соответствуют одному или более вариантам реализации на сопроводительных чертежах. Если специально не указано иное, изображения на сопроводительных чертежах не составляют каких-либо ограничений в отношении пропорций.

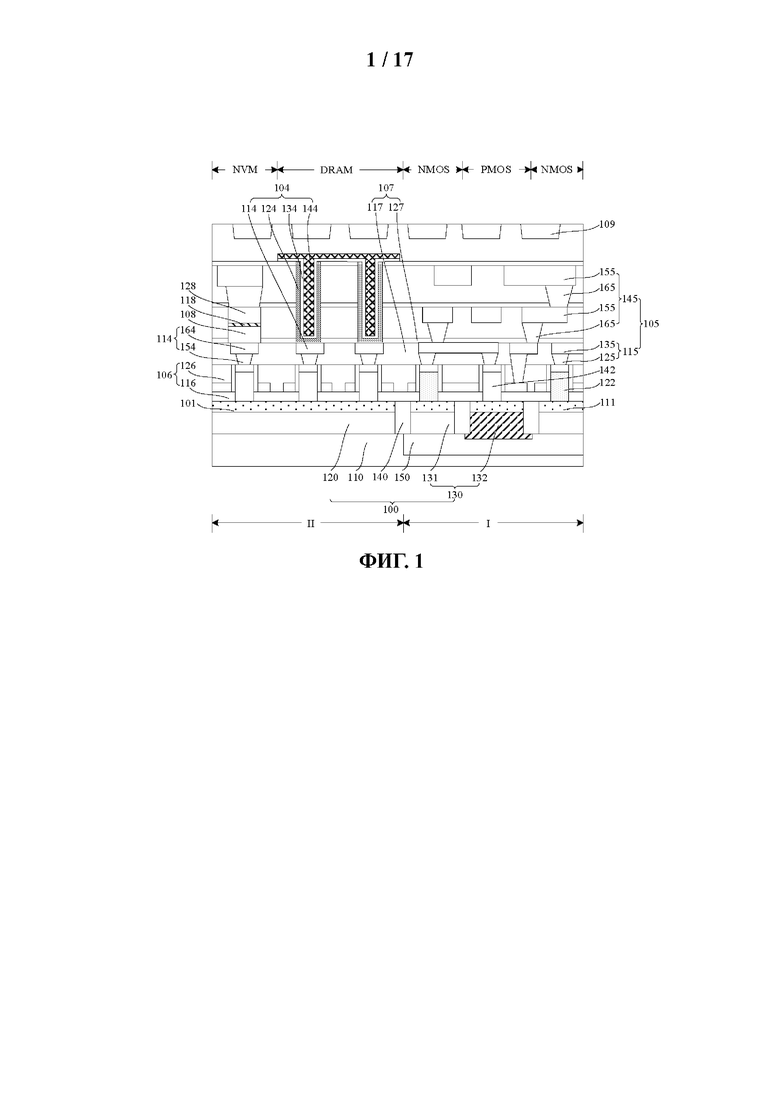

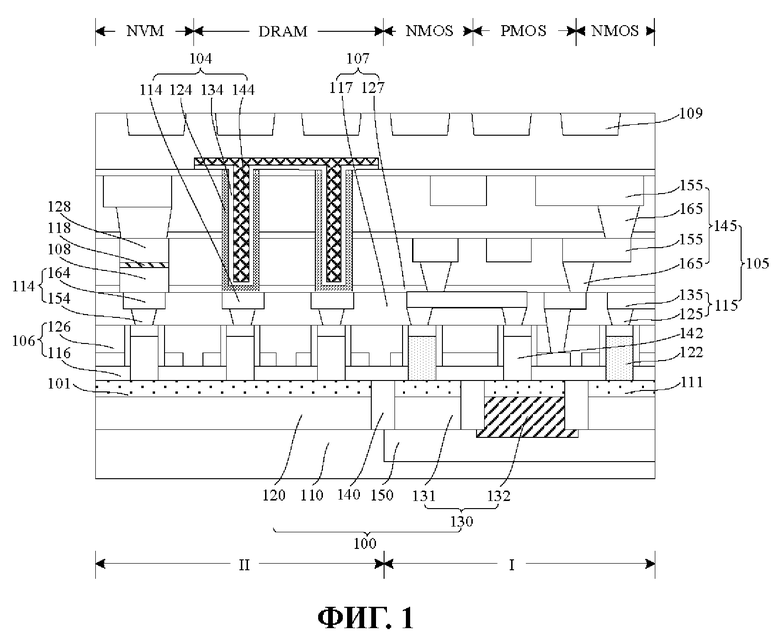

[0008] На ФИГ. 1 приведен схематический вид в разрезе, представляющий структурную схему, соответствующую полупроводниковой структуре согласно одному варианту реализации раскрытия;

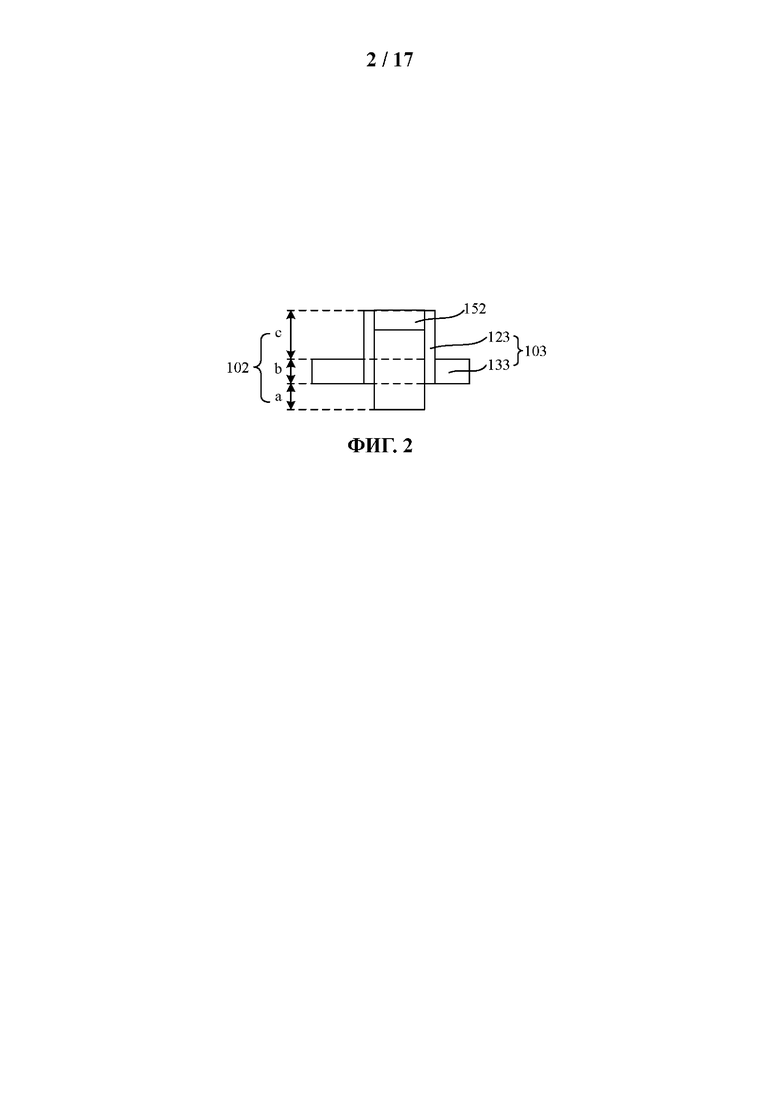

[0009] На ФИГ. 2 приведен увеличенный схематический вид, представляющий структурную схему первого полупроводникового канала и линии слов в полупроводниковой структуре, показанной на ФИГ. 1.

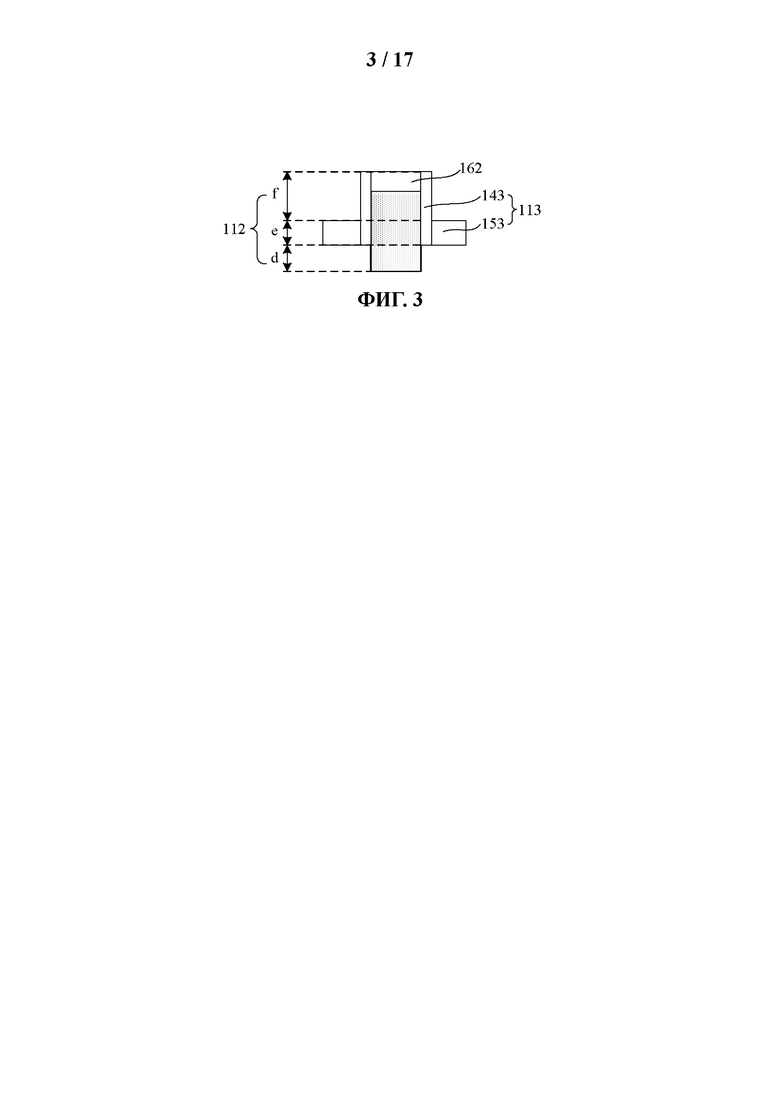

[0010] На ФИГ. 3 приведен увеличенный схематический вид, представляющий структурную схему второго полупроводникового канала и затвора в полупроводниковой структуре, показанной на ФИГ. 1; и

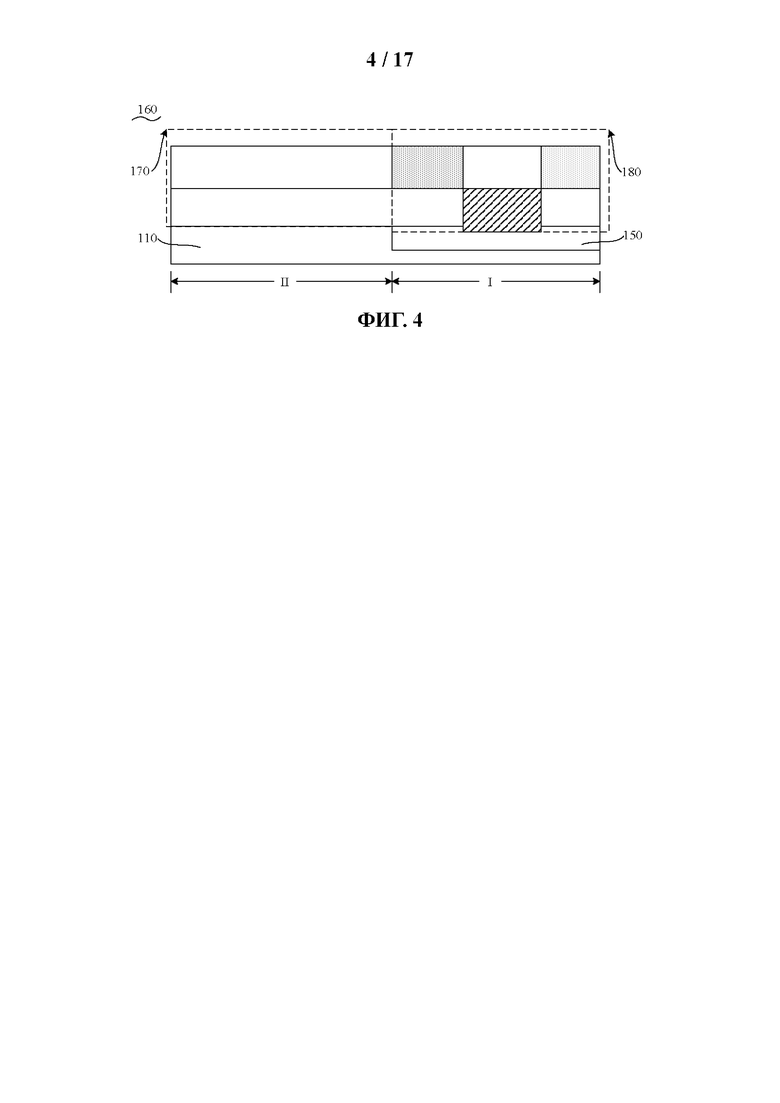

[0011] На ФИГ. 4-17 приведены схематические виды в разрезе, представляющие структурные схемы, соответствующие операциям способа изготовления полупроводниковой структуры в соответствии с еще одним вариантом реализации данного раскрытия.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

[0012] На основании раздела "УРОВЕНЬ ТЕХНИКИ", из соответствующей области техники видно, что хотя степень интеграции полупроводниковых устройств должна быть увеличена, производственные затраты должны быть снижены.

[0013] На основании анализа, в традиционном компьютере используется архитектура фон Неймана. В такой архитектуре функции вычисления и функции хранения разделены. Центральный процессор (central processing unit, CPU) и запоминающее устройство связаны друг с другом с возможностью передачи данных посредством шины. Центральный процессор считывает данные из запоминающего устройства, выполняет вычисление и затем сохраняет результат в запоминающем устройстве. Все данные хранятся в запоминающем устройстве и затем передаются центральному процессору. Затем результат вычисления из центрального процессора сохраняется в запоминающем устройстве. Как может быть замечено, при использовании традиционной архитектуры фон Неймана запоминающее устройство должно часто выполнять операции считывания и записи, при этом интенсивный обмен данными приводит к существенному энергопотреблению и снижению производительности устройства.

[0014] Для решения указанной выше проблемы варианты реализации этого раскрытия обеспечивают полупроводниковую структуру и способ ее изготовления. В полупроводниковой структуре проектируют полупроводниковую основу, включающую в себя область логического устройства и область памяти. Структура в области памяти используется для осуществления хранения данных, а структура в области логического устройства используется для осуществления вычисления данных, так что одна и та же полупроводниковая структура снабжена как процессорным блоком, так и запоминающим устройством, для реализации интегральной микросхемы (IMC), таким образом обеспечивая выполнение процесса ввода/вывода и процесса вычисления данных в различных областях полупроводниковой структуры. Это способствует сокращению расстояния между процессорным блоком и запоминающим устройством, таким образом повышая эффективность передачи данных и снижая энергопотребление, требуемое для передачи данных. Это способствует повышению производительности полупроводниковой структуры и снижению потребления энергии полупроводниковой структурой во время работы.

[0015] Для более ясного описания задач, технических решений и преимуществ вариантов реализации этого раскрытия, варианты реализации этого раскрытия ниже подробно описаны со ссылкой на сопроводительные чертежи. Однако специалистам в данной области техники понятно, что для читателя представлено множество технических подробностей для лучшего понимания этого раскрытия в вариантах его реализации. Однако даже в отсутствие этих технических подробностей и различных изменений и модификаций на основании следующих вариантов реализации может быть осуществлено техническое решение, заявленное в этом раскрытии.

[0016] Вариант реализации этого раскрытия обеспечивает полупроводниковую структуру. Полупроводниковая структура, обеспеченная в варианте реализации этого раскрытия, подробно описана ниже со ссылкой на сопроводительные чертежи. На ФИГ. 1 приведен схематический вид в разрезе, представляющий структурную схему, соответствующую полупроводниковой структуре согласно одному варианту реализации этого раскрытия. На ФИГ. 2 приведен увеличенный схематический вид, представляющий структурную схему первого полупроводникового канала и линии слов в полупроводниковой структуре, показанной на ФИГ. 1. На ФИГ. 3 приведен увеличенный схематический вид, представляющий структурную схему второго полупроводникового канала и затвора в полупроводниковой структуре, показанной на ФИГ. 1.

[0017] Со ссылкой на ФИГ. 1-3, полупроводниковая структура включает в себя: полупроводниковую основу 100, включающую в себя область I логического устройства и область II памяти; линию 101 битов и слой 111 электрического контакта, расположенный в том же самом слое, что и линия 101 битов, при этом линия 101 битов расположена на полупроводниковой основе 100 в области II памяти, а слой 111 электрического контакта расположен на полупроводниковой основе 100 в области I логического устройства; первый полупроводниковый канал 102, расположенный на поверхности линии 101 битов и проходящий в направлении от полупроводниковой основы 100 к линии 101 битов, при этом первый полупроводниковый канал 102 включает в себя первую область а легирования, первую канальную область b и вторую область c легирования, которые расположены последовательно, при этом первая область легирования а находится в контакте с линией 101 битов; второй полупроводниковый канал 112, расположенный в том же самом слое, что и первый полупроводниковый канал 102, на поверхности слоя 111 электрического контакта и проходит в направлении от полупроводниковой основы 100 к слою 111 электрического контакта, при этом второй полупроводниковый канал 112 включает в себя третью область d легирования, вторую канальную область e и четвертую область f легирования, которые расположены последовательно, при этом третья область d легирования находится в контакте со слоем 111 электрического контакта; линию 103 слов и затвор 113, расположенный в том же самом слое, что и линия 103 слов, при этом линия 103 слов расположена таким образом, что окружает первую канальную область b, а затвор 113 расположен таким образом, что окружает вторую канальную область e; емкостную структуру 104, расположенную на стороне второй области c легирования на удалении от первой канальной области b и в контакте со второй областью c легирования; структуру 105 электрического соединения, расположенную на стороне четвертой области f легирования на удалении от второй канальной области e и в контакте с четвертой областью f легирования; и диэлектрический слой 106, расположенный между линией 101 битов и линией 103 слов, а также расположенный на стороне линии 103 слов на удалении от полупроводниковой основы 100. Полупроводниковая структура включает в себя вертикальные транзисторы с круговым затвором (Gate-All-Around, GAA), а линия 101 битов расположена между полупроводниковой основой 100 и вертикальными транзисторами с круговым затвором (GAA), так что может быть формировано запоминающее устройство с объемной (3D) сложенной послойно структурой. Это способствует увеличению степени интеграции ИС в полупроводниковой структуре. Кроме того, полупроводниковая основа 100 включает в себя область I логического устройства и область II памяти, при этом структура в области II памяти используется для осуществления хранения данных, а структура в области I логического устройства используется для осуществления вычисления данных, так что одна и та же полупроводниковая структура оснащена как процессорным блоком, так и запоминающим устройством, для реализации интегральной микросхемы (IMC).

[0018] Ниже со ссылкой на ФИГ. 1-3 указанная полупроводниковая структура описана более подробно.

[0019] В этом варианте реализации тип материала полупроводниковой основы 100 может быть одноэлементным полупроводниковым материалом или кристаллическим неорганическим смешанным полупроводниковым материалом. Одноэлементный полупроводниковый материал может быть кремнием или германием. Кристаллический неорганический смешанный полупроводниковый материал может быть карбидом кремния, кремний-германиевым материалом, арсенидом галлия, индий-галлиевым материалом или тому подобным.

[0020] В частности, тип материала первого полупроводникового канала 102 и тип материала второго полупроводникового канала 112 могут быть теми же самыми, что и тип материала полупроводниковой основы 100, т.е. оба являются одноэлементным полупроводниковым материалом или кристаллическим неорганическим смешанным полупроводниковым материалом.

[0021] Кроме того, линия 101 битов и первый полупроводниковый канал 102 имеют один и тот же полупроводниковый элемент. Удельное сопротивление линии 101 битов меньше, чем удельное сопротивление первой области a легирования. Слой 111 электрического контакта и второй полупроводниковый канал 112 имеют один и тот же полупроводниковый элемент. Удельное сопротивление слоя 111 электрического контакта меньше, чем удельное сопротивление третьей области d легирования.

[0022] Поскольку первый полупроводниковый канал 102 и линия 101 битов имеют один и тот же полупроводниковый элемент, первый полупроводниковый канал 102 и линия 101 битов сформированы с использованием одной и той же пленочной слоевой структуры, а пленочная слоевая структура сформирована полупроводниковым элементом, так что линия 101 битов и первый полупроводниковый канал 102 являются единой структурой, таким образом смягчая дефект состояния межфазной границы между линией 101 битов и первым полупроводниковым каналом 102. Слой 111 электрического контакта и второй полупроводниковый канал 112 имеют один и тот же полупроводниковый элемент. Второй полупроводниковый канал 112 и слой 111 электрического контакта сформированы с использованием одной и той же пленочной слоевой структуры, а пленочная слоевая структура сформирована полупроводниковым элементом, так что слой 111 электрического контакта и второй полупроводниковый канал 112 являются единой структурой, таким образом смягчая дефект состояния межфазной границы между слоем 111 электрического контакта и вторым полупроводниковым каналом 112. Оба указанные выше фактора способствуют улучшению характеристики полупроводниковой структуры.

[0023] В этом варианте реализации первый полупроводниковый канал 102, линия 101 битов, слой 111 электрического контакта и второй полупроводниковый канал 112 имеют один и тот же полупроводниковый элемент, т.е. все они могут быть сформированы с использованием одной и той же пленочной слоевой структуры, т.е. все они могут быть сформированы с использованием одной и той же исходной полупроводниковой основы. Линия 101 битов, первый полупроводниковый канал 102, слой 111 электрического контакта, второй полупроводниковый канал 112 и полупроводниковая основа 100 являются единой структурой, таким образом улучшая характеристики межфазной границы между полупроводниковой основой 100 и линией 101 битов и слоем 111 электрического контакта, между линией 101 битов и первым полупроводниковым каналом 102, а также между слоем 111 электрического контакта и вторым полупроводниковым каналом 112 для смягчения дефектов состояния межфазной границы между этими четырьмя компонентами, таким образом дополнительно улучшая электрические характеристики полупроводниковой структуры.

[0024] Еще в одних вариантах реализации материалом линии битов может быть металл, например, медь, алюминий или вольфрам. Материалом слоя электрического контакта может быть металл, например, медь, алюминий или вольфрам.

[0025] В этом варианте реализации полупроводниковая основа 100 может включать в себя: полупроводниковую подложку 110; первый полупроводниковый захватный слой 120, расположенный на полупроводниковой подложке 110 в области II памяти, при этом линия 101 битов расположена на поверхности первого полупроводникового захватного слоя 120 на удалении от полупроводниковой подложки 110; и второй полупроводниковый захватный слой 130, расположенный на полупроводниковой подложке 110 в области I логического устройства, при этом слой 111 электрического контакта расположен на поверхности второго полупроводникового захватного слоя 130 на удалении от полупроводниковой подложки 110.

[0026] Первый полупроводниковый захватный слой 120 расположен между линией 101 битов и полупроводниковой подложкой 110 для способствования предотвращению электрической утечки из линии 101 битов, а второй полупроводниковый захватный слой 130 расположен между слоем 111 электрического контакта и полупроводниковой подложкой 110 для способствования предотвращению электрической утечки из слоя 111 электрического контакта.

[0027] В этом варианте реализации полупроводниковая подложка 110 является кремниевой подложкой, ионы первого типа являются ионами N-типа, а ионы второго типа являются ионами P-типа. В частности, ионы N-типа представляют собой по меньшей мере один тип ионов из ионов мышьяка, ионов фосфора или ионов сурьмы. Ионы P-типа представляют собой по меньшей мере один тип ионов из ионов бора, ионов индия или ионов галлия. Еще в одних вариантах реализации полупроводниковой подложкой является германиевая подложка, германиево-кремниевая подложка или подложка из полупроводникового соединения III-V групп. Материал подложки из полупроводникового соединения III-V групп включает в себя по меньшей мере одно из арсенида галлия, фосфида индия или нитрида галлия.

[0028] Кроме того, ортогональная проекция первого полупроводникового захватного слоя 120 на полупроводниковую подложку 110 может совпадать с ортогональной проекцией линии 101 битов на полупроводниковую подложку 110. Это способствует увеличению площади контакта между первым полупроводниковым захватным слоем 120 и линией 101 битов, таким образом уменьшая контактное сопротивление между первым полупроводниковым захватным слоем 120 и линией 101 битов. Кроме того, это дополнительно способствует увеличению объема линии 101 битов, так что активное сопротивление линии 101 битов уменьшается, эффект резистивно-емкостной (RC) задержки смягчается, а быстродействие полупроводниковой структуры увеличивается.

[0029] Логическое устройство, соответствующее области I логического устройства, может включать в себя по меньшей мере одно из процессора цифровых сигналов (digital signal processor, DSP), программируемой пользователем вентильной матрицы (field-programmable gate array, FPGA), центрального процессора (CPU), графического процессора (graphics processing unit, GPU) или встроенного процессора нейронной сети (neural-network processing unit, NPU). Запоминающее устройство, соответствующее области II памяти, может включать в себя по меньшей мере одно из статического запоминающего устройства произвольного доступа (static random access memory, SRAM), динамического запоминающего устройства произвольного доступа (dynamic random access memory, DRAM), резистивного запоминающего устройства произвольного доступа (resistive random access memory, RRAM), магниторезистивного запоминающего устройства произвольного доступа (magnetoresistive random access memory, MRAM) или запоминающего устройства произвольного доступа с фазовым переходом (Phase Change Random Access Memory, PCRAM). В этом случае в вариантах реализации этого раскрытия логическое устройство и запоминающее устройство могут быть целиком изготовлены в одном и том же чипе для осуществления реальных вычислений в памяти (in-memory computing, IMC).

[0030] В этом варианте реализации область I логического устройства может включать в себя области n-канальной МОП-структуры (n-channel metal-oxide-semiconductor, NMOS) и области p-канальной МОП-структуры (p-channel metal-oxide-semiconductor, PMOS). Полупроводниковая основа 100 в области I логического устройства дополнительно включает в себя: изолирующую структуру 140, расположенную между двумя смежными вторыми полупроводниковыми захватными слоями 130, а также между двумя смежными слоями 111 электрического контакта.

[0031] Изолирующая структура 140 расположена между двумя смежными вторыми полупроводниковыми захватными слоями 130 и двумя смежными слоями 111 электрического контакта для достижения изоляции между смежными вторыми полупроводниковыми захватными слоями 130 и между смежными слоями 111 электрического контакта. Это способствует устранению электрических взаимных помех между смежными вторыми полупроводниковыми захватными слоями 130 и между смежными слоями 111 электрического контакта. Кроме того, изолирующие структуры 140 дополнительно расположены между первым полупроводниковым захватным слоем 120 и вторым полупроводниковым захватным слоем 130 для осуществления изоляции между первым полупроводниковым захватным слоем 120 и вторым полупроводниковым захватным слоем 130. Материалом изолирующей структуры 140 является по меньшей мере одно из нитрида кремния, карбонитрида кремния или карбооксинитрида кремния.

[0032] Кроме того, вторые полупроводниковые захватные слои 130 включают в себя третьи полупроводниковые захватные слои 131 и четвертые полупроводниковые захватные слои 132. Третьи полупроводниковые захватные слои 131 и четвертые полупроводниковые захватные слои 132 расположены с интервалами относительно друг друга. Третьи полупроводниковые захватные слои 131 легированы ионами первого типа. Четвертые полупроводниковые захватные слои 132 легированы ионами второго типа. Ионы второго типа отличаются от ионов первого типа. Первый полупроводниковый захватный слой 120 также легирован ионами первого типа. Как ионы первого типа, так и ионы второго типа являются одним из ионов N-типа или ионов P-типа. В этом варианте реализации ионы первого типа являются ионами N-типа. Ионы второго типа являются ионами P-типа. Область I логического устройства, соответствующая третьим полупроводниковым захватным слоям 131, является областями n-канальной МОП-структуры (NMOS). Область I логического устройства, соответствующая четвертым полупроводниковым захватным слоям 132, является областями p-канальной МОП-структуры (PMOS). Еще в одних вариантах реализации ионы первого типа могут быть ионами P-типа, а ионы второго типа могут быть ионами N-типа.

[0033] Следует отметить, что на ФИГ. 1 в качестве примера показано, что второй полупроводниковый захватный слой 130 включает в себя два третьих полупроводниковых захватных слоя 131 и один четвертый полупроводниковый захватный слой 132, расположенный между двумя третьими полупроводниковыми захватными слоями 131, а второй полупроводниковый захватный слой 130, ближайший к первому полупроводниковому захватному слою 120, является одним из третьих полупроводниковых захватных слоев 131. Фактически, количество вторых полупроводниковых захватных слоев 130 не ограничивается в этом варианте реализации, и тип второго полупроводникового захватного слоя 130, ближайшего к первому полупроводниковому захватному слою 120, также не ограничивается. Количество вторых полупроводниковых захватных слоев может быть задано надлежащим образом в соответствии с фактическими электрическими требованиями при условии, что третьи полупроводниковые захватные слои и четвертый полупроводниковый захватный слой (слои) последовательно распределены чередующимся способом. Кроме того, второй полупроводниковый захватный слой, ближайший к первому полупроводниковому захватному слою, также может быть четвертым полупроводниковым захватным слоем.

[0034] Полупроводниковая основа 100 также может включать в себя глубокий захватный слой 150. Ортогональная проекция второго полупроводникового захватного слоя 130 на полупроводниковую подложку 110 расположена в ортогональной проекции глубокого захватного слоя 150 на полупроводниковую подложку 110. В этом варианте реализации глубокий захватный слой 150 легирован ионами первого типа. Еще в одних вариантах реализации глубокий захватный слой может быть легирован ионами второго типа.

[0035] Еще в одних вариантах реализации полупроводниковая основа может не включать в себя первый полупроводниковый захватный слой и вторые полупроводниковые захватные слои. Линия битов и слой электрического контакта вместе непосредственно расположены на полупроводниковой подложке. Линия 101 битов, первый полупроводниковый канал 102, слой 111 электрического контакта и второй полупроводниковый канал 112 включают в себя один и тот же полупроводниковый элемент и структурно представляют собой одно целое. В одном примере линия 101 битов, первый полупроводниковый канал 102, слой 111 электрического контакта и второй полупроводниковый канал 112 соответственно включают в себя кремний. Еще в одном примере линия битов, первый полупроводниковый канал, слой электрического контакта и второй полупроводниковый канал могут соответственно включать в себя германий. Альтернативно линия битов, первый полупроводниковый канал, слой электрического контакта и второй полупроводниковый канал соответственно включают в себя кремний и германий. Альтернативно линия битов, первый полупроводниковый канал, слой электрического контакта и второй полупроводниковый канал соответственно включают в себя кремний и углерод. Альтернативно линия битов, первый полупроводниковый канал, слой электрического контакта и второй полупроводниковый канал соответственно включают в себя мышьяк и галлий. Альтернативно линия битов, первый полупроводниковый канал, слой электрического контакта и второй полупроводниковый канал соответственно включают в себя галлий и индий.

[0036] В частности, материал линии 101 битов может включать в себя химическое соединение металла с полупроводником. По сравнению с неметаллизированным полупроводниковым материалом химическое соединение металла с полупроводником имеет относительно небольшое удельное сопротивление. Таким образом, по сравнению с первым полупроводниковым каналом 102 удельное сопротивление линии 101 битов меньше. Это способствует уменьшению активного сопротивления линии 101 битов и контактного сопротивления между линией 101 битов и первой областью a легирования, таким образом дополнительно улучшая электрические характеристики полупроводниковой структуры.

[0037] Кроме того, удельное сопротивление линии 101 битов меньше, чем удельное сопротивление первого полупроводникового захватного слоя 120. По сравнению со случаем использования полупроводникового материала в качестве материала линии 101 битов, химическое соединение металла с полупроводником используется в качестве материала линии 101 битов, таким образом способствуя уменьшению активного сопротивления линии 101 битов.

[0038] В некоторых примерах материал всей линии 101 битов является химическим соединением металла с полупроводником. В некоторых других примерах материал области линии 101 битов, расположенный непосредственно под первой областью а легирования, является полупроводниковым материалом, а материал области линии 101 битов, не покрытый первой областью а легирования, является химическим соединением металла с полупроводником. Понятно, что при постепенном уменьшении размеров устройства или регулировке параметров производственного процесса материал в частичной области линии 101 битов, расположенный непосредственно под первой областью а легирования, является полупроводниковым материалом, а материал в другой области линии 101 битов, расположенной непосредственно под первой областью а легирования, может быть химическим соединением металла с полупроводником. "Другие области" в настоящем документе расположены на периферии "частичной области".

[0039] Кроме того, материал слоя 111 электрического контакта является тем же самым, что и материал линии 101 битов. Таким образом, по сравнению со вторым полупроводниковым каналом 112 удельное сопротивление слоя 111 электрического контакта меньше. Это способствует уменьшению активного сопротивления слоя 111 электрического контакта и контактного сопротивления между каждым слоем 111 электрического контакта и каждой третьей областью d легирования, таким образом также улучшая электрические характеристики полупроводниковой структуры.

[0040] Кроме того, удельное сопротивление слоя 111 электрического контакта меньше, чем удельное сопротивление второго полупроводникового захватного слоя 130. По сравнению со случаем использования полупроводникового материала в качестве материала слоя 111 электрического контакта, когда химическое соединение металла с полупроводником используется в качестве материала слоев 111 электрического контакта, удельное сопротивление слоя 111 электрического контакта меньше. Это способствует уменьшению активного сопротивления слоя 111 электрического контакта.

[0041] В некоторых примерах материал каждого полного слоя 111 электрического контакта является химическим соединением металла с полупроводником. В некоторых других примерах материал в области слоя 111 электрического контакта, расположенный непосредственно под третьей областью d легирования, является полупроводниковым материалом, а материал в области слоя 111 электрического контакта, не покрытого третьей областью d легирования, является химическим соединением металла с полупроводником. Понятно, что с непрерывным уменьшением размеров устройства или регулировкой параметров производственного процесса материал в частичной области слоя 111 электрического контакта, расположенной непосредственно под третьей областью d легирования, является полупроводниковым материалом, а материал в другой области слоя 111 электрического контакта, расположенной непосредственно под третьей областью d легирования, может быть химическим соединением металла с полупроводником. "Другие области" в настоящем документе расположены на периферии "частичной области".

[0042] Еще в одних вариантах реализации материал линии битов и материал слоя электрического контакта могут быть полупроводниковыми материалами. Полупроводниковая основа не включает в себя первый полупроводниковый захватный слой и второй полупроводниковый захватный слой. Линия битов и слой электрического контакта вместе расположены непосредственно на полупроводниковой подложке.

[0043] Еще в одних вариантах реализации материал линии битов и/или материал слоя электрического контакта могут быть металлическим материалом.

[0044] Полупроводниковый элемент может включать в себя по меньшей мере одно из кремния, углерода, германия, мышьяка, галлия или индия. Металлический элемент в химическом соединении металла с полупроводником включает в себя по меньшей мере одно из кобальта, никеля, молибдена, титана, вольфрама, тантала или платины.

[0045] При использовании кремния, являющегося полупроводниковым элементом, в качестве примера, химическое соединение металла с полупроводником включает в себя по меньшей мере одно из силицида кобальта, силицида никеля, силицида молибдена, силицида титана, силицида вольфрама, силицида тантала или силицида платины. Кроме того, химическое соединение металла с полупроводником может быть дополнительно легировано азотом.

[0046] Полупроводниковая структура может включать в себя множество линий 101 битов, расположенных с интервалами. Каждая линия 101 битов может находиться в контакте по меньшей мере с одной первой областью a легирования. На ФИГ. 1 в качестве примера показано, что каждая линия 101 битов находится в контакте с тремя первыми областями a легирования. Количество первых областей а легирования в контакте с каждой линией 101 битов может быть надлежащим образом задано в соответствии с фактическими электрическими требованиями.

[0047] Материал первого полупроводникового канала 102 и материал второго полупроводникового канала 112 включают в себя одноэлементный полупроводниковый материал или кристаллический неорганический смешанный полупроводниковый материал. В этом варианте реализации материал первого полупроводникового канала 102 и материал второго полупроводникового канала 112 являются кремнием. Еще в одних вариантах реализации материал первого полупроводникового канала и/или материал второго полупроводникового канала могут быть германием, кремний-германиевым материалом, карбидом кремния, арсенидом галлия или индий-галлиевым материалом.

[0048] Кроме того, первый полупроводниковый канал 102 и линия 101 битов имеют один и тот же тип легирующих ионов. Легирующие ионы могут быть ионами N-типа или ионами P-типа. Второй полупроводниковый канал 112 включает в себя третий полупроводниковый канал 122 и четвертый полупроводниковый канал 142. Третий полупроводниковый канал 122 расположен на стороне одного из третьих полупроводниковых захватных слоев 131 на удалении от полупроводниковой подложки 110. Четвертый полупроводниковый канал 142 расположен на стороне четвертого полупроводникового захватного слоя 132 на удалении от полупроводниковой подложки 110. Тип легирующих ионов, легированных в третьем полупроводниковом канале 122, отличается от типа легирующих ионов, легированных в третьем полупроводниковом захватном слое 131. Тип легирующих ионов, легированных в четвертом полупроводниковом канале 142, отличается от типа легирующих ионов, легированных в четвертом полупроводниковом захватном слое 132.

[0049] В этом варианте реализации первый полупроводниковый канал 102 и второй полупроводниковый канал 112 соответственно имеют цилиндрическую форму. Боковые стенки первого полупроводникового канала 102 и второго полупроводникового канала 112 обе являются гладкими переходными поверхностями. Это способствует предотвращению возникновения явления точечного разряда или электрической утечки в первом полупроводниковом канале 102 и втором полупроводниковом канале 112, таким образом дополнительно улучшая электрические характеристики полупроводниковой структуры. Следует отметить, что еще в одних вариантах реализации первый полупроводниковый канал и/или второй полупроводниковый канал могут иметь конструкцию эллиптической колонки, конструкцию квадратной колонки или другую нерегулярную конструкцию. Следует понимать, что когда конструкция первого полупроводникового канала и/или конструкция второго полупроводникового канала представляют собой конструкцию квадратной колонки, углы, сформированные смежными поверхностями боковых стенок конструкции квадратной колонки, могут быть закругленными углами, так что проблемы точечного разряда также могут быть устранены. Конструкция квадратной колонки может быть конструкцией кубической колонки или конструкцией прямоугольной колонки.

[0050] Первая область a легирования образует одно из истока и стока транзисторного устройства, а вторая область c легирования образует другое одно из истока и стока транзисторного устройства. Третья область d легирования образует одно из истока и стока другого транзисторного устройства, а вторая область c легирования образует другое одно из истока и стока транзисторного устройства.

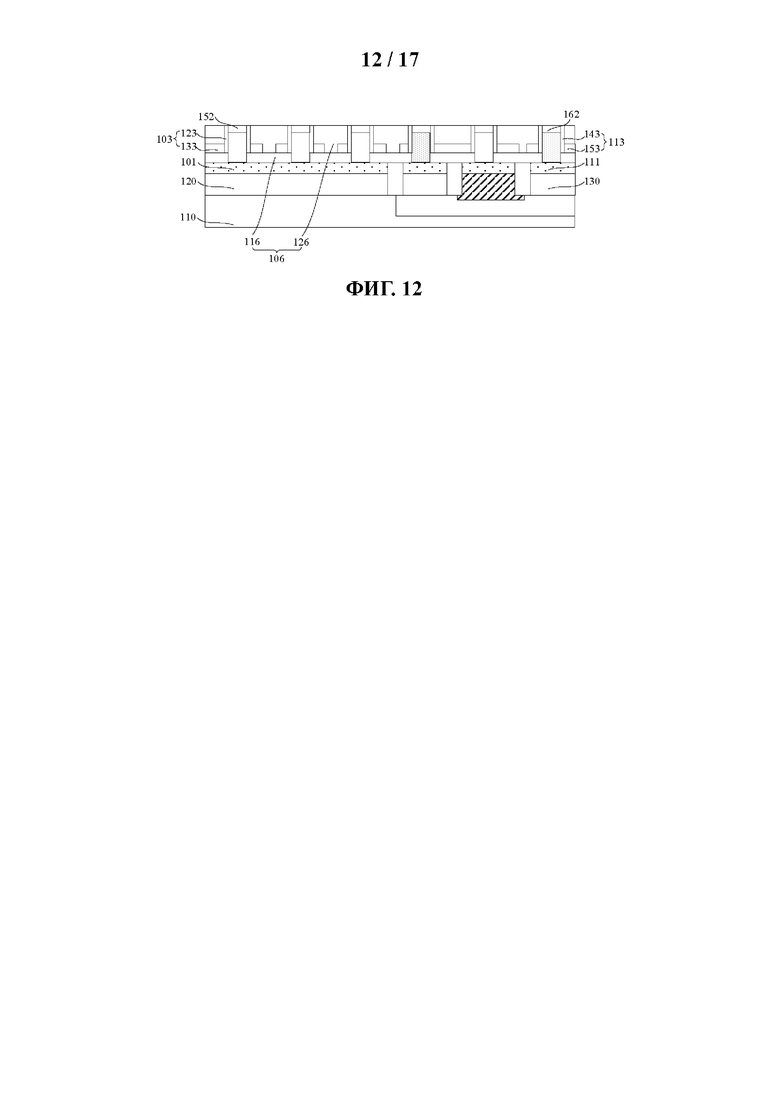

[0051] Вторая область c легирования также может включать в себя первый металлический контактный слой 152. Первый металлический контактный слой 152 находится в контакте с емкостной структурой 104. Материал первого металлического контактного слоя 152 также является химическим соединением металла с полупроводником. Таким образом, материал первого металлического контактного слоя 152 может быть тем же самым, что и материал линии 101 битов. Удельное сопротивление первого металлического контактного слоя 152 меньше, чем удельное сопротивление второй области c легирования, отличающейся от первого металлического контактного слоя 152. Это способствует уменьшению удельного сопротивления второй области c легирования. Кроме того, первый металлический контактный слой 152 способствует уменьшению контактного сопротивления между второй областью c легирования и емкостной структурой 104. Следует отметить, что выражение "материалы являются теми же самыми" в настоящем документе фактически означает, что указанные материалы, если не принимать во внимание легирующие ионы N-типа или легирующие ионы P-типа, являются одинаковыми. Например, материал первого металлического контактного слоя 152 и материал линии 101 битов оба являются силицидом никеля.

[0052] Четвертая область f легирования также может включать в себя второй металлический контактный слой 162. Второй металлический контактный слой 162 расположен в том же самом слое, что и первый металлический контактный слой 152, и находится в контакте со структурой 105 электрического соединения. Материал второго металлического контактного слоя 162 также является химическим соединением металла с полупроводником. Таким образом, материал второго металлического контактного слоя 162 может быть тем же самым, что и материал слоя 111 электрического контакта. Удельное сопротивление второго металлического контактного слоя 162 меньше, чем удельное сопротивление четвертой области f легирования, отличающейся от второго металлического контактного слоя 162. Это способствует уменьшению удельного сопротивления четвертой области f легирования. Кроме того, второй металлический контактный слой 162 способствует уменьшению контактного сопротивления между четвертой областью f легирования и структурой 105 электрического соединения. Следует отметить, что выражение "материалы являются теми же самыми" в настоящем документе фактически означает, что указанные материалы, если не принимать во внимание легирующие ионы N-типа или легирующие ионы P-типа, являются одинаковыми. Например, материал второго металлического контактного слоя 162 и материал слоя 111 электрического контакта оба являются силицидом никеля.

[0053] Первый полупроводниковый канал 102 и второй полупроводниковый канал 112 могут составлять канал беспереходного транзистора соответственно. Таким образом, первая область a легирования, первая канальная область b и вторая область c легирования имеют один и тот же тип легирующих ионов. Третья область d легирования, вторая канальная область e и четвертая область f легирования также имеют один и тот же тип легирующих ионов. Например, легирующие ионы все являются ионами N-типа или ионами P-типа. Кроме того, первая область a легирования, первая канальная область b и вторая область c легирования могут иметь одни и те же легирующие ионы. Третья область d легирования, вторая канальная область e и четвертая область f легирования могут иметь одни и те же легирующие ионы. Кроме того, легирующие ионы в областях первого полупроводникового канала 102 и второго полупроводникового канала 112 могут быть одного и того же типа. Это способствует формированию первого полупроводникового канала 102 и второго полупроводникового канала 112 с использованием одного и того же этапов процесса.

[0054] "Беспереходный" в настоящем документе означает, что переход PN отсутствует. Таким образом, переход PN отсутствует в устройствах, состоящих из первого полупроводникового канала 102 и второго полупроводникового канала 112. Это дает следующие преимущества. В одном аспекте первая область a легирования, вторая область c легирования, третья область d легирования и четвертая область f легирования не нуждаются в дополнительном легировании, что позволяет устранить проблему, заключающуюся в том, что трудно управлять процессами легирования первой области a легирования, второй области c легирования, третьей области d легирования и четвертой области f легирования. В частности, по мере дальнейшего уменьшения размера транзистора, когда первая область a легирования, вторая область c легирования, третья область d легирования и четвертая область f легирования должны быть дополнительно легированы, управлять концентрацией легирования значительно труднее. В другом аспекте, поскольку устройство является беспереходным транзистором, можно обойтись без изготовления гиперрезкого перехода PN в наноразмерном диапазоне с использованием процесса легирования перехода сток-исток с гиперрезким градиентом концентрации. Таким образом, могут быть устранены проблемы, такие как дрейф порогового напряжения и увеличение тока утечки, вызванное резким изменением легирования. Это также способствует подавлению эффекта короткого канала, и устройство по-прежнему может работать в размерном диапазоне нескольких нанометров. Таким образом, это способствует дополнительному повышению плотности упаковки ИС и улучшению электрических характеристик полупроводниковой структуры. Дополнительное легирование в настоящем документе означает легирование для того, чтобы тип легирующих ионов в первой области a легирования и второй области c легирования отличался от типа легирующих ионов в первой канальной области b, и для того, чтобы тип легирующих ионов в третьей области d легирования и четвертой области f легирования отличался от типа легирующих ионов во второй канальной области e.

[0055] Каждая линия 103 слов включает в себя: первый диэлектрический слой 123 затвора, расположенный вокруг первой канальной области b на поверхности боковой стенки первого полупроводникового канала 102, в котором расположена первая канальная область b, и дополнительно расположенный на поверхности боковой стенки первого полупроводникового канала 102, в котором расположена вторая область c легирования; и первый проводящий слой 133 затвора, расположенный вокруг первой канальной области b на поверхности боковой стенки первого диэлектрического слоя 123 затвора, соответствующей первой канальной области b.

[0056] Первый диэлектрический слой 123 затвора используется для изоляции первого проводящего слоя 133 затвора от первого полупроводникового канала 102. Кроме того, первый диэлектрический слой 123 затвора расположен на поверхности боковой стенки первого полупроводникового канала 102, в котором расположена вторая область c легирования, защищая поверхность второй области c легирования и предотвращая технологическое повреждение поверхности второй области c легирования в производственном процессе. Это способствует дополнительному улучшению электрических характеристик полупроводниковой структуры. Еще в одних вариантах реализации первый диэлектрический слой затвора может быть расположен только на поверхности боковой стенки первого полупроводникового канала, в котором расположена первая канальная область.

[0057] Затвор 113 включает в себя: второй диэлектрический слой 143 затвора, расположенный в том же слое, что и первый диэлектрический слой 123 затвора, вокруг второй канальной области e на поверхности боковой стенки второго полупроводникового канала 112, в котором расположена вторая канальная область e, а также на поверхности боковой стенки второго полупроводникового канала 112, в котором расположена четвертая область f легирования; и второй проводящий слой 153 затвора, расположенный в том же слое, что и первый проводящий слой 133 затвора, вокруг второй канальной области e, а также на поверхности боковой стенки второго диэлектрического слоя 143 затвора, соответствующей второй канальной области e.

[0058] Второй диэлектрический слой 143 затвора используется для изоляции второго проводящего слоя 153 затвора от второго полупроводникового канала 112. Кроме того, второй диэлектрический слой 143 затвора расположен на поверхности боковой стенки второго полупроводникового канала 112, в котором расположена четвертая область f легирования, защищая поверхность четвертой области f легирования и предотвращая технологическое повреждение поверхности четвертой области f легирования в производственном процессе. Это способствует дополнительному улучшению электрических характеристик полупроводниковой структуры. В других вариантах реализации второй диэлектрический слой затвора может быть расположен только на поверхности боковой стенки второго полупроводникового канала, в котором расположена вторая канальная область.

[0059] Материал первого диэлектрического слоя 123 затвора и материал второго диэлектрического слоя 143 затвора оба включают в себя по меньшей мере одно из диоксида кремния, нитрида кремния или оксинитрида кремния. Материал первого проводящего слоя 133 затвора и материал второго проводящего слоя 153 затвора оба включают в себя по меньшей мере одно из поликристаллического кремния, нитрида титана, нитрида тантала, меди, вольфрама или алюминия. В некоторых примерах материал первого диэлектрического слоя 123 затвора и материал второго диэлектрического слоя 143 затвора являются одним и тем же материалом. Это способствует формированию первого диэлектрического слоя 123 затвора и второго диэлектрического слоя 143 затвора на одном и том же этапе процесса. Материал первого проводящего слоя 133 затвора и материал второго проводящего слоя 153 затвора являются одним и тем же материалом. Это способствует формированию первого проводящего слоя 133 затвора и второго проводящего слоя 153 затвора на одном и том же этапе процесса.

[0060] В этом варианте реализации полупроводниковая структура включает в себя множество линий 101 битов, расположенных с интервалами, и множество слоев 111 электрического контакта, расположенных с интервалами. Каждая линия 101 битов и каждый слой 111 электрического контакта проходят в первом направлении. Соответственно, полупроводниковая структура включает в себя множество линий 103 слов, расположенных с интервалами, и множество затворов 113, расположенных с интервалами. Каждая линия 103 слов и каждый затвор 113 проходят во втором направлении. Второе направление отличается от первого направления. Например, первое направление может быть перпендикулярным второму направлению. Кроме того, каждая линия 103 слов может быть расположена вокруг первой канальной области b по меньшей мере одного первого полупроводникового канала 102. Каждый затвор 113 может быть расположен вокруг второй канальной области e по меньшей мере одного второго полупроводникового канала 112. Количество первых полупроводниковых каналов 102, окруженных каждой линией 103 слов, и количество вторых полупроводниковых каналов 112, окруженных каждым затвором 113, может быть задано надлежащим образом в соответствии с фактическими электрическими требованиями.

[0061] На ФИГ. 1 показано, что второй проводящий слой 153 затвора окружает как третий полупроводниковый канал 122 в области n-канальной МОП-структуры (NMOS), так и четвертый полупроводниковый канал 142 в области p-канальной МОП-структуры (PMOS), смежной с областью n-канальной МОП-структуры (NMOS). В другом примере один второй проводящий слой затвора может окружать только третий полупроводниковый канал в области n-канальной МОП-структуры (NMOS), а другой второй проводящий слой затвора может окружать только четвертый полупроводниковый канал в области p-канальной МОП-структуры (PMOS).

[0062] Диэлектрический слой 106 используется для изоляции линии 101 битов от первого проводящего слоя 133 затвора, а также используется для изоляции слоя 111 электрического контакта от второго проводящего слоя 153 затвора, и дополнительно используется для изоляции смежных линий 103 слов и смежных затворов 113. Таким образом, диэлектрический слой 106 расположен между линиями 101 битов и линиями 103 слов, а также расположен в интервалах между смежными линиями 103 слов, и кроме того расположен между слоями 111 электрического контакта и затворами 113, а также расположен в интервалах между смежными затворами 113.

[0063] Диэлектрический слой 106 может включать в себя: первый диэлектрический слой 116, расположенный между линиями 101 битов и линиями 103 слов и между слоями 111 электрического контакта и затворами 113 для осуществления изоляции между линиями 101 битов и линиями 103 слов и изоляции между слоями 111 электрического контакта и затворами 113, таким образом предотвращая электрические взаимные помехи между линиями 101 битов и линиями 103 слов и между слоями 111 электрического контакта и затворами 113; и второй диэлектрический слой 126, который расположен между смежными линиями 103 слов и между смежными затворами 113, находится в контакте с первым диэлектрическим слоем 116 и используется для осуществления изоляции между смежными линиями 103 слов и между смежными затворами 113, таким образом предотвращая электрические взаимные помехи между смежными линиями 103 слов и между смежными затворами 113. Второй диэлектрический слой 126 также расположен на поверхностях линий 103 слов и затворов 113 на удалении от полупроводниковой основы 100 и используется для поддержки других проводящих структур, расположенных на поверхности второго диэлектрического слоя 126 на удалении от полупроводниковой основы 100, и изоляции линий 103 слов и затворов 113 от других проводящих структур.

[0064] В этом варианте реализации материал первого диэлектрического слоя 116 и материал второго диэлектрического слоя 126 являются одними и теми же и оба могут быть по меньшей мере одним из диоксида кремния, нитрида кремния, карбооксинитрида кремния или оксинитрида кремния. Еще в одних вариантах реализации материал первого диэлектрического слоя и материал второго диэлектрического слоя могут быть различными.

[0065] Понятно, что еще в одних вариантах реализации диэлектрический слой может иметь другую сложенную послойно пленочную слоевую структуру. Конкретная структура сложенной послойно пленочной слоевой структуры зависит от процессов способа изготовления при условии, что диэлектрический слой может обеспечивать изоляцию.

[0066] В этом варианте реализации область II памяти включает в себя область динамического запоминающего устройства произвольного доступа (DRAM). Емкостная структура 104 области DRAM включает в себя: первую проводящую структуру 114, находящуюся в контакте со второй областью c легирования; нижний электродный слой 124, находящийся в контакте с первой проводящей структурой 114; емкостной диэлектрический слой 134, расположенный на поверхности нижнего электродного слоя 124; и верхний электродный слой 144, расположенный на поверхности емкостного диэлектрического слоя 134.

[0067] В частности, первая проводящая структура 114 включает в себя первую проводящую колонку 154 и первый проводящий слой 164. В плоскости, перпендикулярной поверхности полупроводниковой основы 100, форма поперечного сечения первой проводящей колонки 154 является перевернутой трапецией с уменьшением ширины в направлении сверху вниз. Ортогональная проекция первого проводящего слоя 164 на полупроводниковую основу 100 покрывает ортогональную проекцию первой проводящей колонки 154 на полупроводниковую основу 100. Это является преимуществом, которое состоит в обеспечении относительно большой площади контакта между первой проводящей колонкой 154 и второй областью c легирования и относительно большой площади контакта между первым проводящим слоем 164 и нижним электродным слоем 124. В то же время это является преимуществом, которое состоит в увеличении объема первой проводящей структуры 114 и уменьшении активного сопротивления первой проводящей структуры 114. В некоторых примерах материал первой проводящей колонки 154 и материал первого проводящего слоя 164 являются одним и тем же, и оба являются по меньшей мере одним из проводящих материалов, таких как никель-платина, титан, тантал, кобальт, поликристаллический кремний, медь, вольфрам, нитрид тантала, нитрид титана или рутений. Еще в одних вариантах реализации материал первой проводящей колонки может отличаться от материала первого проводящего слоя.

[0068] Материал нижнего электродного слоя 124 может быть тем же самым, что и материал верхнего электродного слоя 144. Оба материала нижнего электродного слоя 124 и верхнего электродного слоя 144 могут быть по меньшей мере одним из никель-платины, титана, тантала, кобальта, поликристаллического кремния, меди, вольфрама, нитрида тантала, нитрида титана или рутения. Еще в одних вариантах реализации материал нижнего электродного слоя может отличаться от материала верхнего электродного слоя. Материал емкостного диэлектрического слоя 134 включает в себя материал с высокой диэлектрической проницаемостью, такой как диоксид кремния, оксид тантала, оксид гафния, оксид циркония, оксид ниобия, оксид титана, оксид бария, оксид стронция, оксид иттрия, оксид лантана, оксид празеодима, титанат бария-стронция или тому подобное.

[0069] В этом варианте реализации в плоскости, перпендикулярной поверхности полупроводниковой основы 100, форма поперечного сечения нижнего электродного слоя 124 является U-образной. Емкостной диэлектрический слой 134, расположенный на поверхности нижнего электродного слоя 124, образует одно сквозное отверстие. Верхний электродный слой 144 заполняет это сквозное отверстие. Верхние электродные слои 144, расположенные между смежными сквозными отверстиями, находятся в контакте и электрически соединены друг с другом. Таким образом, верхние электродные слои 144 имеют единую структуру. Еще в одних вариантах реализации имеется интервал между двумя верхними электродными слоями, расположенными соответственно в двух смежных сквозных отверстиях, так что смежные верхние электродные слои могут быть соединены с различными потенциалами. Это способствует достижению индивидуального управления смежными емкостными структурами.

[0070] Еще в одних вариантах реализации емкостная структура может быть плоским конденсатором. Нижний электродный слой находится в контакте со стороной второй области легирования, расположенной на удалении от первой канальной области. Емкостной диэлектрический слой находится в контакте со стороной нижнего электродного слоя на удалении от второй области легирования. Верхний электродный слой находится в контакте со стороной емкостного диэлектрического слоя на удалении от нижнего электродного слоя.

[0071] В этом варианте реализации каждый первый полупроводниковый канал 102 имеет цилиндрическую структуру. Торцевая поверхность цилиндрической структуры, т.е. торцевая поверхность первой области a легирования находится в контакте с линией 101 битов. Другая торцевая поверхность цилиндрической структуры, т.е. вторая область c легирования находится в контакте с емкостной структурой 104. Кроме того, вторая область c легирования включает в себя первый металлический контактный слой 152. Первый металлический контактный слой 152 находится в контакте с нижним электродным слоем 124, что способствует уменьшению контактного сопротивления между второй областью c легирования и нижним электродным слоем 124, таким образом улучшая электрические характеристики полупроводниковой структуры.

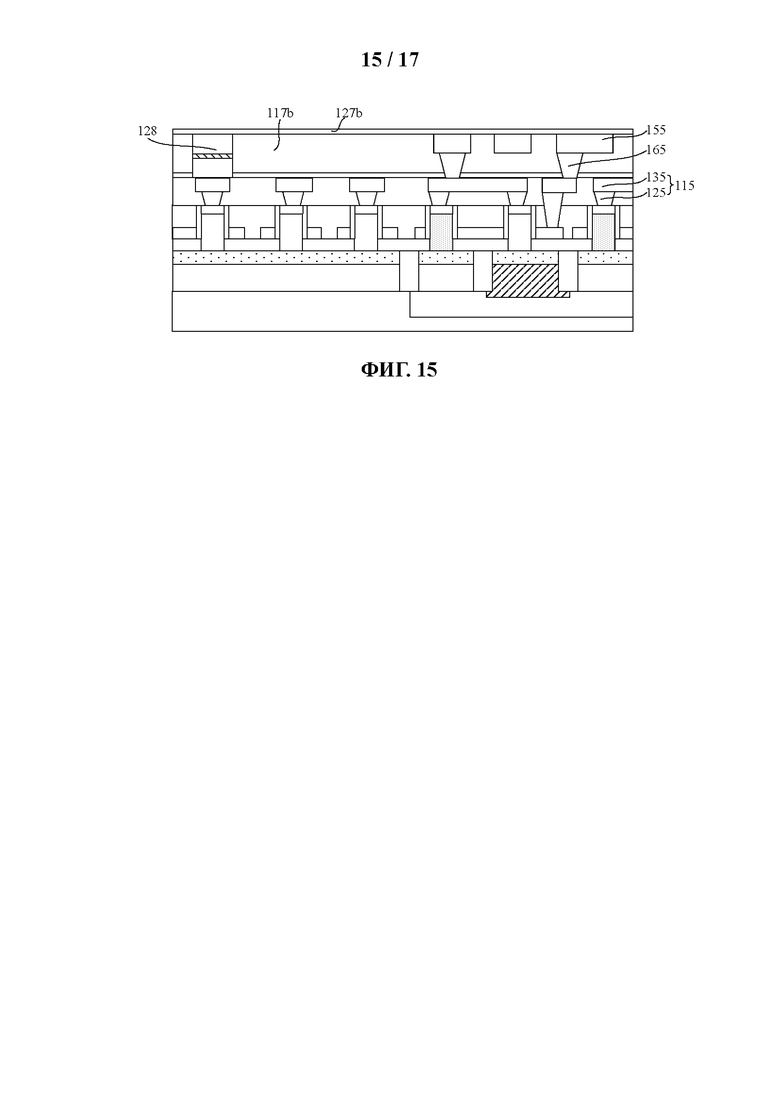

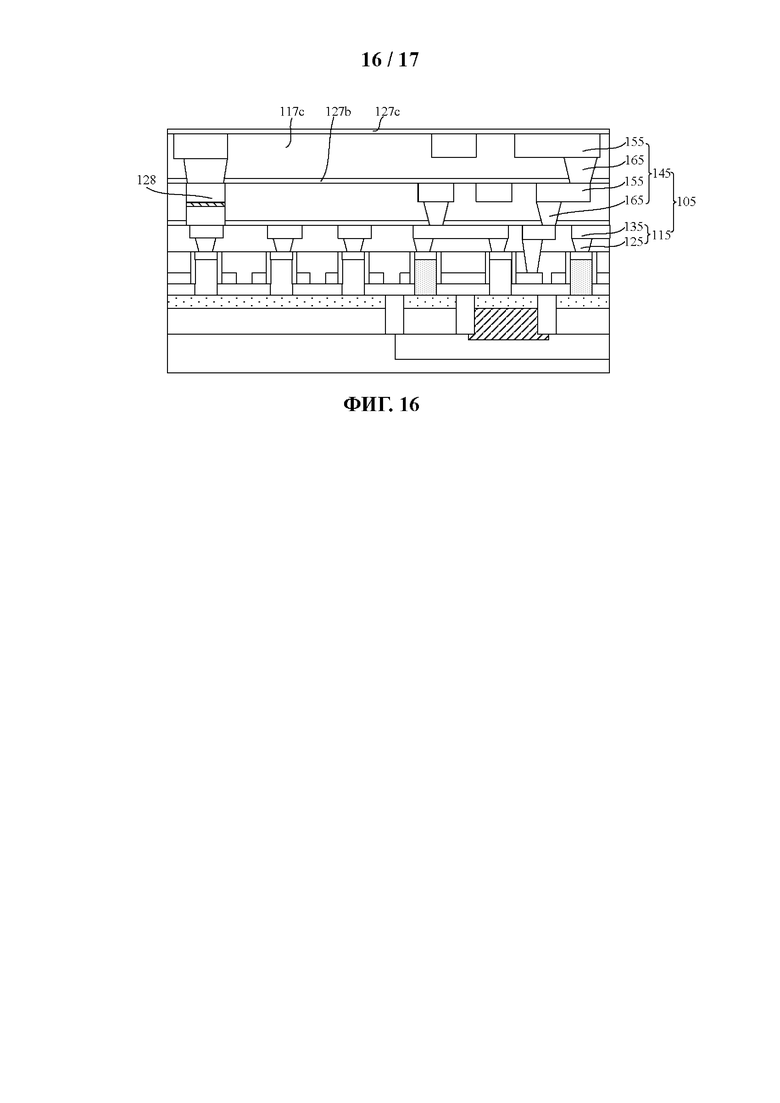

[0072] Структура 105 электрического соединения включает в себя: вторую проводящую структуру 115, расположенную в том же самом слое, что и первая проводящая структура 114, и находящуюся в контакте с четвертой областью f легирования; и третью проводящую структуру 145, находящуюся в контакте со стороной второй проводящей структуры 115 и на удалении от четвертой области f легирования.

[0073] В частности, вторая проводящая структура 115 включает в себя вторую проводящую колонку 125 и второй проводящий слой 135. На ФИГ. 1 показано, что одна вторая проводящая структура 115 может включать в себя один второй проводящий слой 135 и две вторые проводящие колонки 125. Две вторые проводящие колонки 125 находятся в контакте с двумя смежными четвертыми областями f легирования соответственно. Таким образом, одна вторая проводящая структура 115 может быть электрически соединена с двумя смежными четвертыми областями f легирования. Другая вторая проводящая структура 115 может включать в себя один второй проводящий слой 135 и одну вторую проводящую колонку 125, при этом вторая проводящая колонка 125 электрически соединена с одной четвертой областью f легирования. Еще одна другая вторая проводящая структура 115 может включать в себя один второй проводящий слой 135 и одну вторую проводящую колонку 125, при этом вторая проводящая колонка 125 электрически соединена со вторым проводящим слоем 153 затвора. В этом варианте реализации количество вторых проводящих колонок 125 и количество вторых проводящих слоев 135, включенных в одиночную вторую проводящую структуру 115, и конкретный режим электрического соединения второй проводящей колонки 125 могут быть заданы надлежащим образом в соответствии с фактическими электрическими требованиями.

[0074] Кроме того, топологические характеристики и свойства материала второй проводящей колонки 125 и второго проводящего слоя 135 во второй проводящей структуре 115 могут быть определены по ссылке на представленную выше первую проводящую структуру 114, подробности которой в данном случае не будут описаны повторно.

[0075] Третья проводящая структура 145 включает в себя по меньшей мере два третьих проводящих слоя 155, третью проводящую колонку 165, электрически соединяющую смежные третьи проводящие слои 155, и другую третью проводящую колонку 165, также электрически соединяющую вторую проводящую структуру 115 и третий проводящий слой 155, ближайший к второй проводящей структуре 115. На ФИГ. 1 в качестве примера показано, что третья проводящая структура 145 включает в себя два третьих проводящих слоя 155 и две третьих проводящих колонки 165. Количество третьих проводящих слоев 155 и третьих проводящих колонок 165, включенных в третью проводящую структуру 145, может быть задано надлежащим образом в соответствии с фактическими электрическими требованиями.

[0076] Кроме того, топологические характеристики и свойства материала третьего проводящего слоя 155 и третьей проводящей колонки 165 в третьей проводящей структуре 145 могут быть определены по ссылке на представленную выше первую проводящую структуру 114, подробности которой в данном случае не будут описаны повторно.

[0077] В этом варианте реализации в направлении, перпендикулярном поверхности полупроводниковой основы 100, глубина нижнего электродного слоя 124 является той же самой, что и глубина третьей проводящей структуры 145. На ФИГ. 1, в качестве примера показано, что глубина нижнего электродного слоя 124 проходит через два третьих проводящих слоя 155. Количество третьих проводящих слоев 155, проходящих на глубину нижнего электродного слоя 124, может быть задано надлежащим образом в соответствии с фактическими электрическими требованиями.

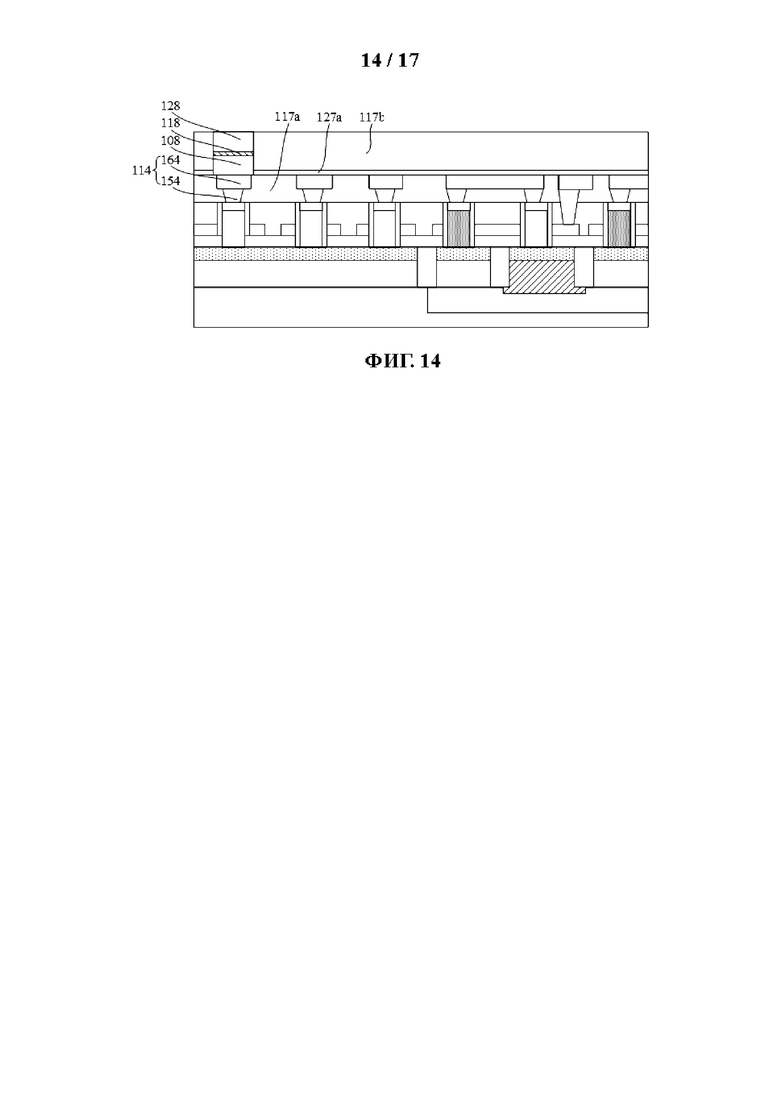

[0078] Область II памяти дополнительно может включать в себя область энергонезависимой памяти (nonvolatile memory, NVM). Таким образом, полупроводниковая структура может дополнительно включать в себя: свободный слой 108, туннельный слой 118 и фиксированный слой 128, сложенные послойно на второй области c легирования в области энергонезависимой памяти (NVM). Свободный слой 108 электрически соединен со второй областью c легирования, расположенной в области энергонезависимой памяти (NVM).

[0079] В частности, первая проводящая структура 114 дополнительно обеспечена между свободным слоем 108 и второй областью c легирования в области энергонезависимой памяти (NVM), при этом свободный слой 108 электрически соединен со второй областью c легирования посредством первой проводящей структуры 114.

[0080] Различные проводящие структуры, расположенные в области энергонезависимой памяти (NVM), образуют энергонезависимую память (NVM), а различные проводящие структуры, расположенные в области динамического запоминающего устройства произвольного доступа (DRAM), образуют динамическое запоминающее устройство произвольного доступа (DRAM). Область энергонезависимой памяти (NVM) и область динамического запоминающего устройства произвольного доступа (DRAM) образуют область II запоминающего устройства, используемую для хранения данных. Различные проводящие структуры, расположенные в области n-канальной МОП-структуры (NMOS) и области p-канальной МОП-структуры (PMOS) в области I логического устройства, образуют процессорный блок, используемый для выполнения логических операций с данными. Таким образом, одна и та же полупроводниковая структура обеспечена как процессорным блоком, так и запоминающим устройством, для осуществления реальных вычислений в памяти (in-memory computing, IMC), обеспечения процесса ввода-вывода и процесса вычисления данных, выполняемых в различных областях полупроводниковой структуры. Это способствует сокращению расстояния между процессорным блоком и запоминающим устройством, таким образом повышая эффективность передачи данных и уменьшая энергопотребление, требуемое для передачи данных. Таким образом, это способствует повышению эффективности работы полупроводниковой структуры и уменьшению потребления энергии полупроводниковой структурой во время ее работы.

[0081] Полупроводниковая структура дополнительно включает в себя: изолирующий слой 107, расположенный на поверхности диэлектрического слоя 106. В изолирующем слое 107 расположены емкостная структура 104 и структура 105 электрического соединения. Относительная диэлектрическая постоянная материала изолирующего слоя 107 меньше, чем относительная диэлектрическая постоянная материала диэлектрического слоя 106.

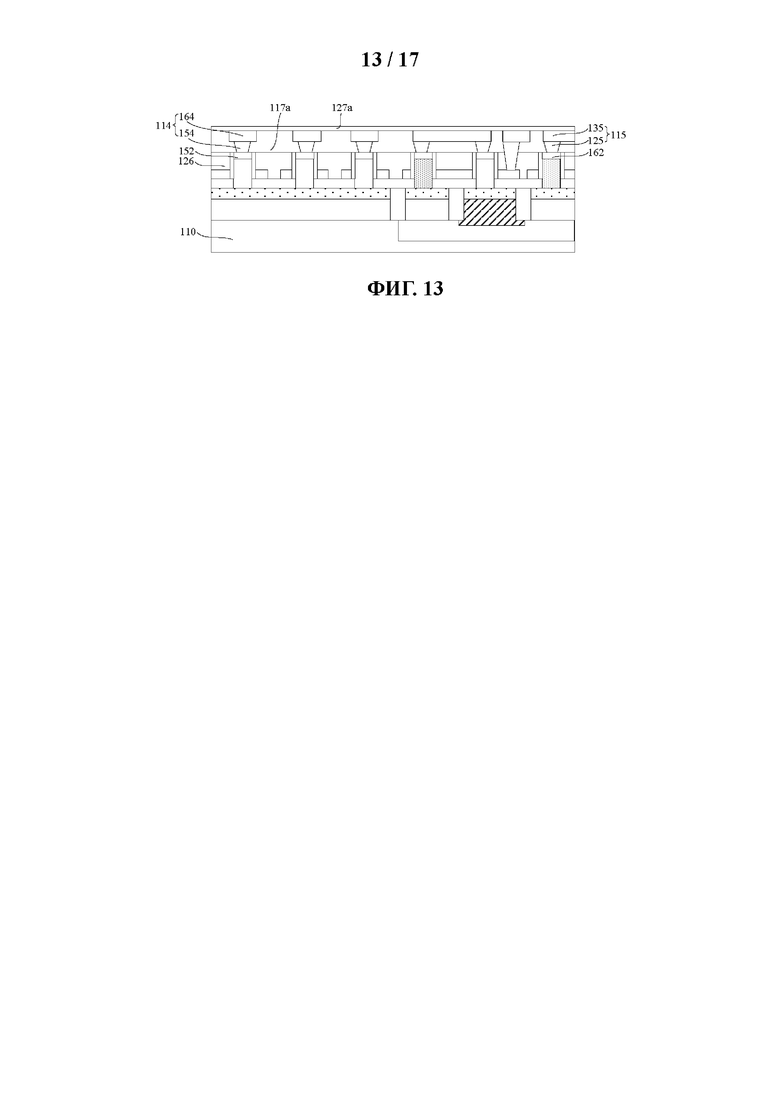

[0082] В частности, изолирующий слой 107 может включать в себя множество межслойных диэлектрических слоев 117 и множество препятствующих травлению слоев 127. Межслойный диэлектрический слой 117 и препятствующий травлению слой 127 последовательно уложены послойно. Часть изолирующего слоя 107, находящаяся в контакте с поверхностью диэлектрического слоя 106, является межслойным диэлектрическим слоем 117. Понятно, что еще в одних вариантах реализации изолирующий слой может иметь другую сложенную послойно пленочную слоевую структуру. Конкретная конфигурация сложенной послойно пленочной слоевой структуры определяется операциями производственного процесса при том условии, что изолирующий слой может обеспечивать изоляцию.

[0083] В этом варианте реализации полупроводниковая структура может дополнительно включать в себя множество четвертых проводящих слоев 109, которые расположены на самом верхнем слое и разнесены друг от друга. Четвертые проводящие слои 109 используются для электрического соединения с соответствующим проводящим слоем или внешним устройством. В этом варианте реализации в качестве примера показано, что имеются четыре проводящих слоя. Могут быть использованы три, пять или любое количество проводящих слоев в соответствии с фактическим требованием схемы.

[0084] В итоге, полупроводниковая основа 100 включает в себя область I логического устройства и область II запоминающего устройства. Структура в области II запоминающего устройства используется для осуществления хранения данных, а структура в области I логического устройства используется для осуществления вычисления данных, так что одна и та же полупроводниковая структура снабжена как процессорным блоком, так и запоминающим устройством для реализации интегральной микросхемы (IMC), таким образом обеспечивая процесс ввода/вывода и процесс вычисления данных, подлежащие выполнению в различных областях полупроводниковой структуры. Это способствует сокращению расстояния между процессорным блоком и запоминающим устройством, таким образом повышая эффективность передачи данных и уменьшая энергопотребление, требуемое для передачи данных. Это способствует повышению эффективности работы полупроводниковой структуры и снижению энергопотребления полупроводниковой структуры при работе.

[0085] Кроме того, полупроводниковая структура, предложенная в этом варианте реализации, может быть применена к запоминающему устройству 4F2. В данном случае F означает размер элемента. Запоминающее устройство может быть динамическим запоминающим устройством произвольного доступа (DRAM) или статическим запоминающим устройством произвольного доступа (SRAM).

[0086] Соответственно, еще в одном варианте реализации этого раскрытия обеспечен способ изготовления полупроводниковой структуры, который может использоваться для формирования приведенной выше полупроводниковой структуры.

[0087] На ФИГ. 4-17 представлены схематические виды в разрезе структур, соответствующие операциям способа изготовления полупроводниковой структуры согласно еще одному варианту реализации этого раскрытия. Способ изготовления полупроводниковой структуры, обеспеченной в этом варианте реализации, описан ниже подробно со ссылкой на сопроводительные чертежи. Части, которые являются теми же самыми или соответствующими приведенным выше вариантам реализации, не описаны ниже подробно повторно.

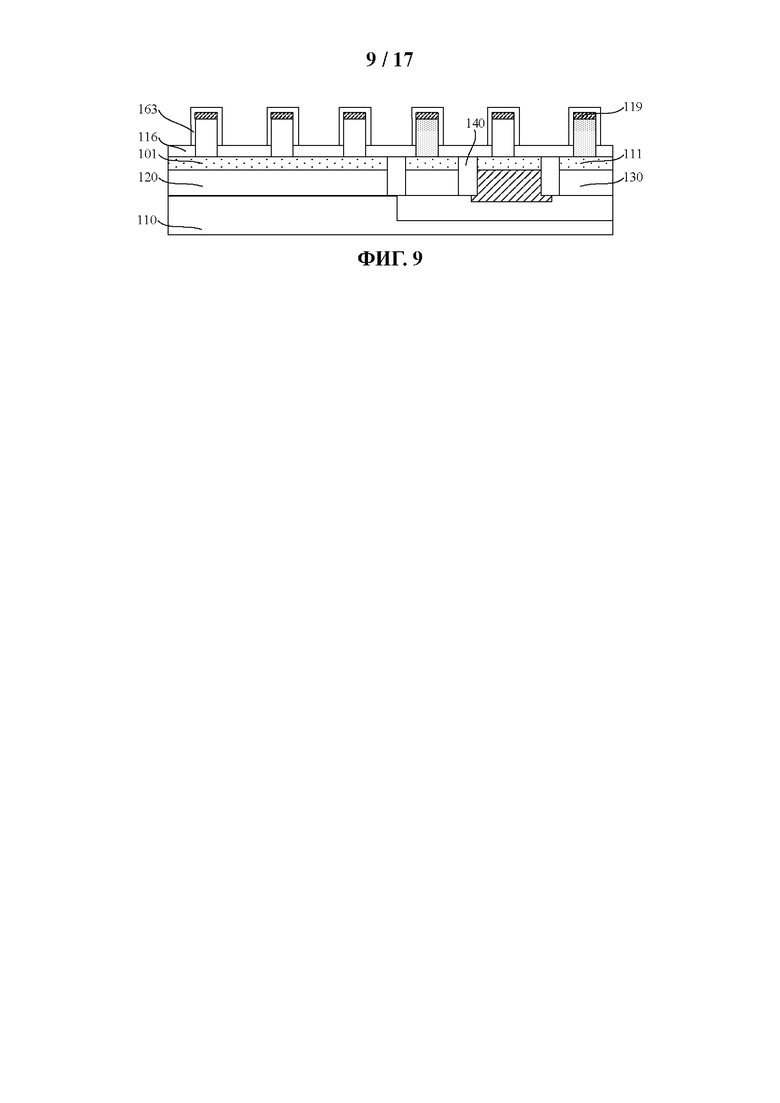

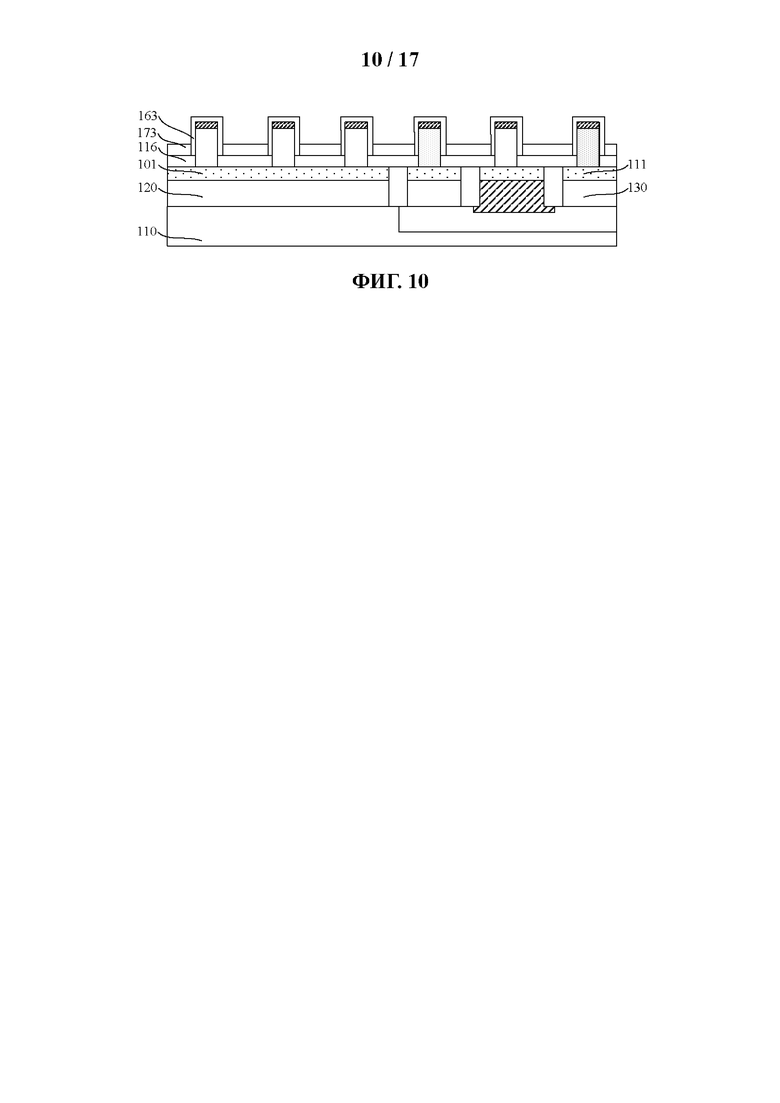

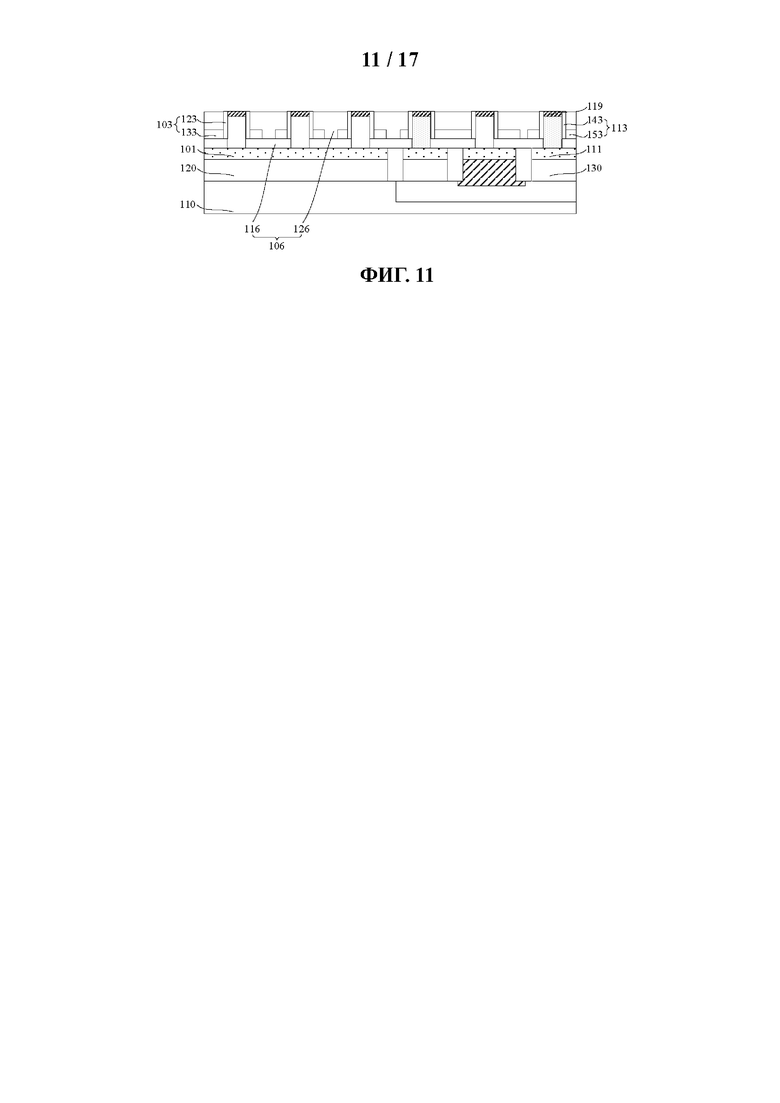

[0088] Со ссылкой на ФИГ. 4-9, обеспечивают полупроводниковую основу 100. Полупроводниковая основа 100 включает в себя область I логического устройства и область II памяти. Образуют линию 101 битов и слой 111 электрического контакта, расположенный в том же самом слое, что и линия 101 битов. Линия 101 битов расположена на полупроводниковой основе 100 в области II памяти. Слой 111 электрического контакта расположен на полупроводниковой основе 100 в области I логического устройства. Образуют первый полупроводниковый канал 102 и второй полупроводниковый канал 112, расположенный в том же самом слое, что и первый полупроводниковый канал 102. Первый полупроводниковый канал 102 расположен на поверхности линии 101 битов. С перечислением в направлении от полупроводниковой основы 100 к линии 101 битов, первый полупроводниковый канал 102 включает в себя первую область а легирования, первую канальную область b и вторую область c легирования, которые расположены последовательно. Первая область a легирования находится в контакте с линией 101 битов. Второй полупроводниковый канал 112 расположен на поверхности слоя 111 электрического контакта. С перечислением в направлении от полупроводниковой основы 100 к слою 111 электрического контакта, второй полупроводниковый канал 112 включает в себя третью область d легирования, вторую канальную область e и четвертую область f легирования, которые расположены последовательно. Третья область d легирования находится в контакте со слоем 111 электрического контакта.

[0089] В частности, обеспечение полупроводниковой основы 100 и формирование линии 101 битов, слоя 111 электрического контакта, первого полупроводникового канала 102 и второго полупроводникового канала 112 включает в себя следующие операции процесса.

[0090] Со ссылкой на ФИГ. 4, обеспечивают исходную полупроводниковую основу 160.

[0091] Исходную полупроводниковую основу 160 используют в качестве основы для формирования полупроводниковой основы 100, линии 101 битов, слоя 111 электрического контакта, первого полупроводникового канала 102 и второго полупроводникового канала 112.

[0092] В некоторых вариантах реализации исходная полупроводниковая основа 160 включает в себя полупроводниковую подложку 110, исходный первый полупроводниковый захватный слой 170 и исходный второй полупроводниковый захватный слой 180. Исходный первый полупроводниковый захватный слой 170 расположен на полупроводниковой подложке 110 в области II памяти. Исходный второй полупроводниковый захватный слой 180 расположен на полупроводниковой подложке 110 в области I логического устройства.

[0093] В частности, исходный первый полупроводниковый захватный слой 170 является двухслойной структурой. Исходный первый полупроводниковый захватный слой 170 легирован ионами первого типа. Концентрации легирования ионами первого типа в различных слоях являются различными. Зависимость между концентрациями легирования ионами первого типа в различных слоях не ограничивается в этом варианте реализации.

[0094] Исходный второй полупроводниковый захватный слой 180 также имеет двухслойную структуру. Частичные области исходного второго полупроводникового захватного слоя 180, расположенные в одном и том же слое, легированы ионами первого типа. Частичные области легированы ионами второго типа. Области, легированные ионами первого типа, и области, легированные ионами второго типа, распределены ступенчатым образом. В направлении, перпендикулярном поверхности полупроводниковой подложки 110, типы легирующих ионов в исходном втором полупроводниковом захватном слое 180 в смежных слоях являются различными.

[0095] Кроме того, исходная полупроводниковая основа 160 дополнительно может включать в себя глубокий захватный слой 150. Ортогональная проекция исходного второго полупроводникового захватного слоя 180 на полупроводниковую подложку 110 расположена в ортогональной проекции глубокого захватного слоя 150 на полупроводниковую подложку 110. В этом варианте реализации глубокий захватный слой 150 легирован ионами первого типа. Еще в одних вариантах реализации глубокий захватный слой может быть легирован ионами второго типа.

[0096] В этом варианте реализации полупроводниковая подложка 110 является кремниевой подложкой. Ионы первого типа являются ионами N-типа. Ионы второго типа являются ионами P-типа. Еще в одних вариантах реализации полупроводниковая подложка может быть германиевой подложкой, германиево-кремниевой подложкой или подложкой из полупроводникового соединения III-V групп. Ионы первого типа могут быть ионами P-типа. Ионы второго типа могут быть ионами N-типа.

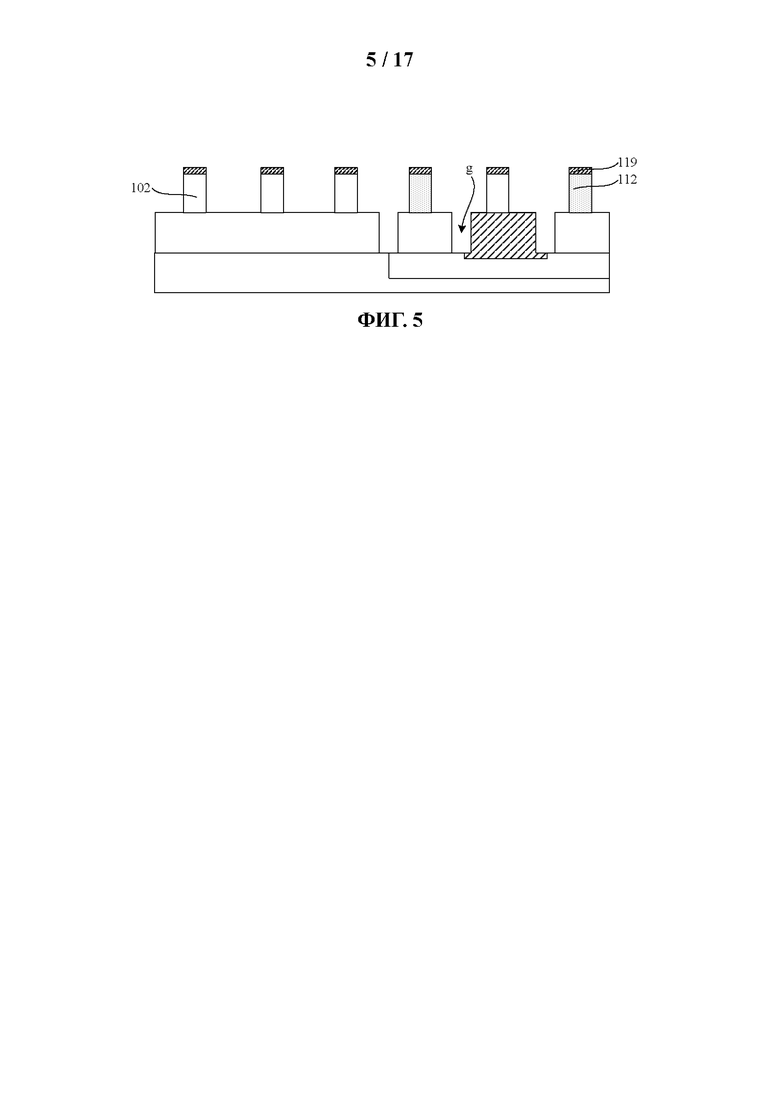

[0097] Со ссылкой на ФИГ. 4 и ФИГ. 5 в сочетании, для частичной толщины исходной полупроводниковой основы 160 получают рисунок с использованием маскирующего слоя 119 в качестве маски для формирования первого полупроводникового канала 102 и второго полупроводникового канала 112.

[0098] В этом варианте реализации для частичной толщины исходного первого полупроводникового захватного слоя 170 и частичной толщины исходного второго полупроводникового захватного слоя 180 получают рисунок для формирования первого полупроводникового канала 102 и второго полупроводникового канала 112. Оставшаяся частичная толщина исходного первого полупроводникового захватного слоя 170 используется для последующего формирования линии 101 битов. Оставшаяся частичная толщина исходного второго полупроводникового захватного слоя 180 используется для последующего формирования слоя 111 электрического контакта. Способ получения рисунка включает в себя технологию самовыравнивающейся четырехкратной экспозиции или технологию самовыравнивающейся четырехкратной визуализации.

[0099] Со ссылкой на ФИГ. 2, первый полупроводниковый канал 102 включает в себя первую область а легирования, первую канальную область b и вторую область c легирования, которые расположены последовательно. Со ссылкой на ФИГ. 3, второй полупроводниковый канал 112 включает в себя третью область d легирования, вторую канальную область e и четвертую область f легирования, которые расположены последовательно.

[00100] Таким образом, первая область a легирования, первая канальная область b и вторая область c легирования имеют один и тот же тип легирующих ионов. Третья область d легирования, вторая канальная область e и четвертая область f легирования имеют один и тот же тип легирующих ионов. Первый полупроводниковый канал 102 и второй полупроводниковый канал 112 оба используются для формирования каналов беспереходных транзисторов. Это позволяет устранить проблемы, такие как дрейф порогового напряжения и увеличение тока утечки, вызванное резким изменением легирования. Это также способствует подавлению эффекта короткого канала.

[00101] Исходная полупроводниковая основа 160 может быть легирована в соответствующих областях заранее перед получением рисунка. Легирование может быть легированием ионами N-типа или ионами P-типа. Частичная толщина исходной полупроводниковой основы 160 может быть легирована после получения рисунка для формирования первого полупроводникового канала 102 и второго полупроводникового канала 112 с соответствующим распределением ионов. В этом варианте реализации скругление углов может быть выполнено на первом полупроводниковом канале 102 и/или втором полупроводниковом канале 112 термическим оксидированием, травлением и/или отжигом в водороде для формирования первого полупроводникового канала 102 и/или второго полупроводникового канала 112 с цилиндрической структурой. Во время работы полупроводниковой структуры это способствует предотвращению возникновения явления точечного разряда или электрической утечки в первом полупроводниковом канале 102 и/или втором полупроводниковом канале 112.

[00102] С продолжением ссылки на ФИГ. 5, для оставшегося исходного второго полупроводникового захватного слой 180 снова получают рисунок (см. ФИГ. 4) для формирования канавки g на границе между двумя смежными областями, легированными ионами различных типов в исходном втором полупроводниковом захватном слое 180. Канавка g проникает в толщину оставшегося исходного второго полупроводникового захватного слоя 180.

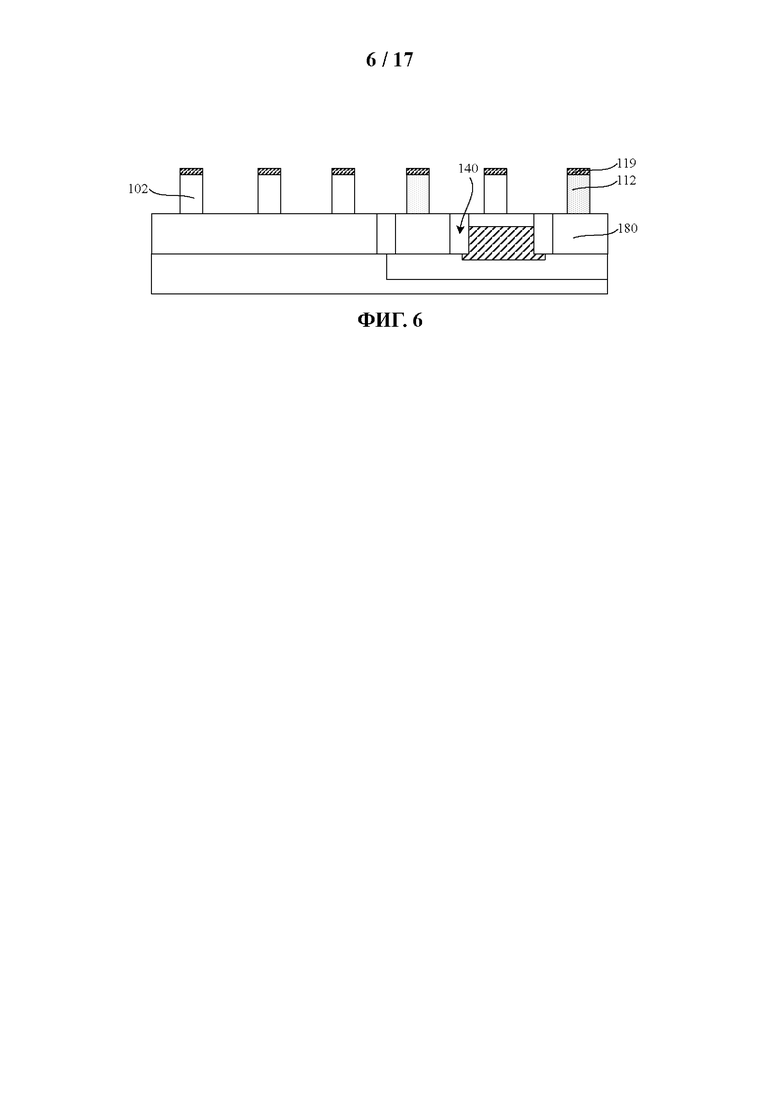

[00103] Со ссылкой на ФИГ. 6, в канавке g образуется изолирующая структура 140 (см. ФИГ. 5). Впоследствии, когда металлические контактные слои и вторые полупроводниковые захватные слои будут сформированы на основе оставшегося исходного второго полупроводникового захватного слоя 180, изолирующая структура 140 будет способствовать изоляции смежных металлических контактных слоев и изоляции смежных вторых полупроводниковых захватных слоев.

[00104] Верхняя поверхность изолирующей структуры 140 может быть расположена вровень с верхней поверхностью оставшегося исходного второго полупроводникового захватного слоя 180.

[00105] Со ссылкой на ФИГ. 7-9, оставшуюся частичную толщину исходной полупроводниковой основы 160 (см. ФИГ. 4) металлизируют для преобразования частичной толщины исходной полупроводниковой основы 160, расположенной ниже первого полупроводникового канала 102, в линию 101 битов и преобразования частичной толщины исходной полупроводниковой основы 160, расположенной ниже второго полупроводникового канала 112, в слой 111 электрического контакта, а оставшуюся исходную полупроводниковую основу 160 используют в качестве полупроводниковой основы 100.

[00106] В частности, оставшуюся частичную толщину исходного первого полупроводникового захватного слоя 170 и частичную толщину исходного второго полупроводникового захватного слоя 180 металлизируют для преобразования частичной толщины исходного первого полупроводникового захватного слоя 170, расположенного ниже первого полупроводникового канала 102, в линию 101 битов и преобразования частичной толщины исходного второго полупроводникового захватного слоя 180, расположенного ниже второго полупроводникового канала 112, в слой 111 электрического контакта. После металлизации оставшийся исходный первый полупроводниковый захватный слой 170 используют в качестве первого полупроводникового захватного слоя 120, а оставшийся исходный второй полупроводниковый захватный слой 180 используют в качестве второго полупроводникового захватного слоя 130.

[00107] Еще в одних вариантах реализации металлизируют оставшуюся частичную толщину исходного первого полупроводникового захватного слоя и частичную толщину исходного второго полупроводникового захватного слоя. Полная толщина исходного первого полупроводникового захватного слоя, расположенного ниже первого полупроводникового канала, может быть преобразована в линию битов, а полная толщина исходного второго полупроводникового захватного слоя, расположенного ниже второго полупроводникового канала, может быть преобразована в слой электрического контакта.

[00108] В частности, металлизация включает следующие операции.

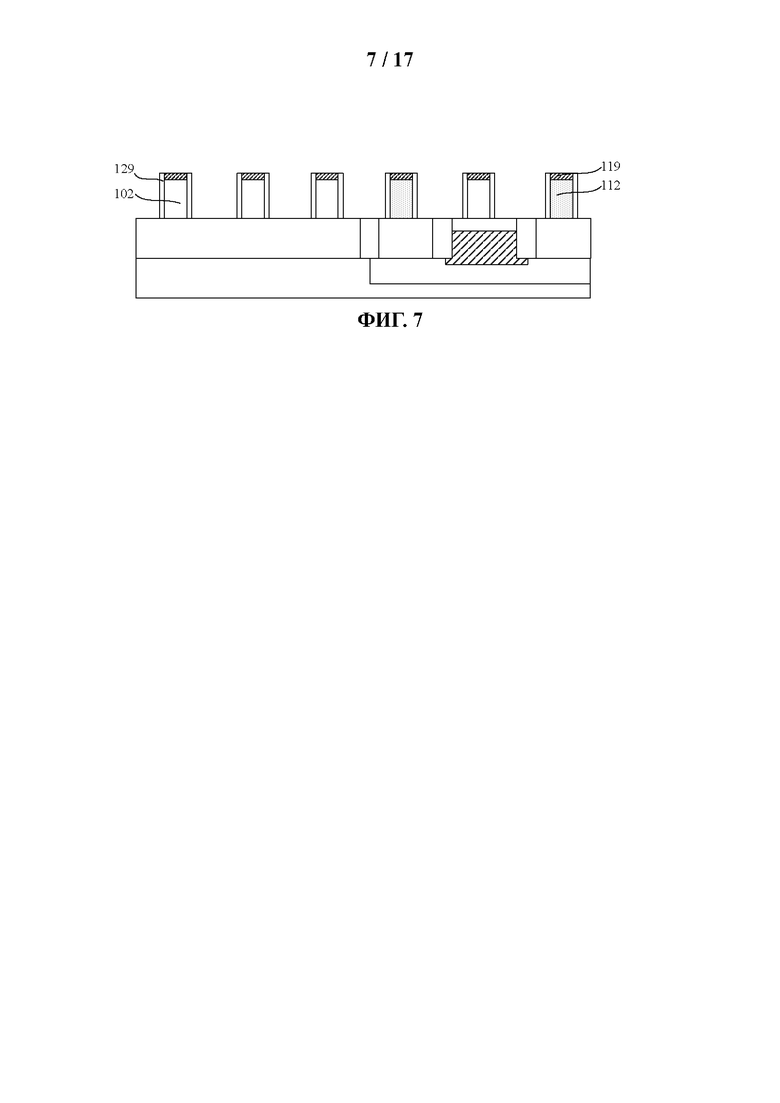

[00109] Со ссылкой на ФИГ. 7, образуют барьерный слой 129. Барьерный слой 129 покрывает поверхности боковых стенок первого полупроводникового канала 102 и второго полупроводникового канала 112.

[00110] Барьерный слой 129 обнажает поверхность исходного первого полупроводникового захватного слоя 170, отличающуюся от позиции непосредственно под первым полупроводниковым каналом 102, и обнажает поверхность исходного второго полупроводникового захватного слоя 180, отличающуюся от позиции непосредственно под вторым полупроводниковым каналом 112. В этом варианте реализации во время получения рисунка для формирования первого полупроводникового канала 102 и второго полупроводникового канала 112 маскирующий слой 119, расположенный поверх поверхности первого полупроводникового канала 102 и второго полупроводникового канала 112, не удаляют. Таким образом, маскирующий слой 119 и барьерный слой 129 могут совместно использоваться для защиты первого полупроводникового канала 102 и второго полупроводникового канала 112 при последующем процессе отжига для предотвращения материалов первого полупроводникового канала 102 и второго полупроводникового канала 112 от реакции с металлическим материалом.

[00111] Еще в одних вариантах реализации в этой операции маскирующий слой, расположенный на верхних поверхностях первого полупроводникового канала и второго полупроводникового канала, может быть удален для обнажения верхних поверхностей первого полупроводникового канала и второго полупроводникового канала, так что в последующих операциях формирования линии битов и слоя электрического контакта первый металлический контактный слой образуется на торцевой поверхности второй области легирования на удалении от полупроводниковой основы, а второй металлический контактный слой образуется на торцевой поверхности четвертой области легирования на удалении от полупроводниковой основы.

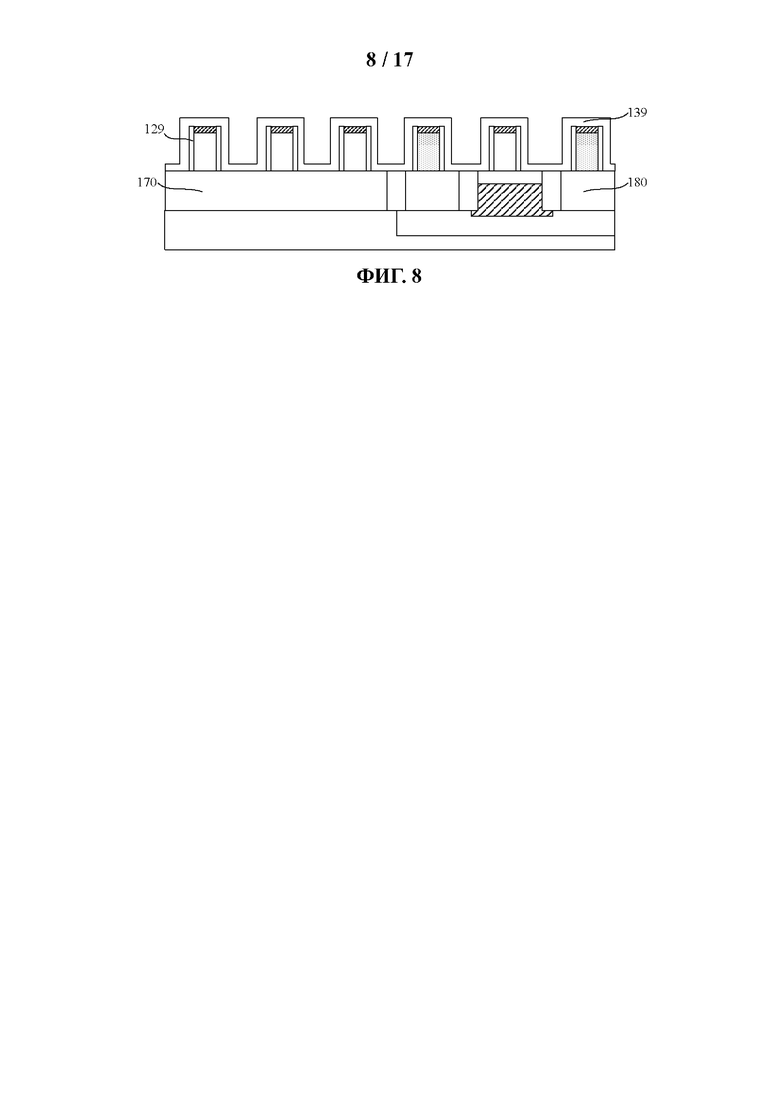

[00112] Со ссылкой на ФИГ. 8, образуют металлический слой 139 на поверхностях исходного первого полупроводникового захватного слоя 170 и исходного второго полупроводникового захватного слоя 180.

[00113] Металлический слой 139 обеспечивает металлический элемент для последующего формирования линии 101 битов. Металлический слой 139 расположен на поверхности исходного первого полупроводникового захватного слоя 170, отличающейся от позиции непосредственно под первыми полупроводниковыми каналами 102, т.е. расположен на поверхности исходного второго полупроводникового захватного слоя 180, отличающейся от позиции непосредственно под вторыми полупроводниковыми каналами 112, а также расположен на поверхности барьерного слоя 129. Материал металлического слоя 139 включает в себя по меньшей мере одно из кобальта, никеля, молибдена, титана, вольфрама, тантала или платины.