ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности, к реконфигурируемым вычислительным устройствам, предназначенным для решения сложных, трудоемких задач и высокоскоростной обработки больших информационных массивов в многозадачных и многопользовательских вычислительных системах с использованием различных ускорителей вычислений.

Ускорителями вычислений в реконфигурируемых вычислительных системах являются аппаратные ускорители, синтезированные на ресурсах вычислительных ПЛИС, и программно-аппаратные ускорители, реализуемые на различного типа совычислителях, представляющих собой заказные СБИС.

В связи с появлением мощных вычислительных компонент, таких как заказные многоядерные СБИС, и развитием технологии создания мощных ПЛИС, в которых размещаются несколько вычислительных устройств, предназначенных для функционирования в различных задачах, актуальным становится гибкое, динамическое распределение вычислительных ресурсов в зависимости от текущего потока задач.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известен вычислительный модуль для многозадачных вычислительных систем (RU №2780169 С1, МПК G06F 15/16, заявлен 29.11.2021, опубликовано 20.09.2022 Бюл. №26), содержащий входной порт 1 интерфейса PCI-Express, выходной порт 2 интерфейса PCI-Express, коммутатор 3 PCI-Express, блок 4 управления коммутатором PCI-Express, память 5 стартовой конфигурации системной ПЛИС 7, память 6 стартовой конфигурации рабочих ПЛИС, системная ПЛИС 7, порт 8 контроля и управления системной ПЛИС 7, блок 10 конфигурирования рабочих ПЛИС, блок 11 мониторинга, порт 12 мониторинга, блок 13 управления питанием и охлаждением, порт 14 управления питанием и охлаждением и группу из М вычислительных каналов 91, …, 9М, каждый из которых содержит рабочую ПЛИС 15 и совычислитель 26, причем рабочая ПЛИС 15 содержит контроллер 16 PCI-Express, память 17 конфигурации, блок 18 управления коммутатором 23 рабочей ПЛИС 15, адаптер 19 совычислителя 26, буферную память 20 данных, буферную память 21 результата, контроллер 22 прямого доступа в память, коммутатор 23 рабочей ПЛИС 15, группу из К адаптеров 241, …, 24K исполнительных устройств, группу из К исполнительных устройств 251, …, 25K, а совычислитель 26 содержит интерфейсный блок 27, коммутатор 28 совычислителя и группу из N вычислительных ядер 291, …, 24N, каждое из которых содержит память 30 программы и параметров, блок 31 управления, память 32 данных, операционный блок 33 и память 34 результата.

Недостатком данного вычислительного модуля является отсутствие возможности динамического перераспределения вычислительных ресурсов в зависимости от текущего потока задач.

Причинами, препятствующими достижению технического результата, является отсутствие возможности оперативного реконфигурирования вычислительных ПЛИС исполнительными устройствами в соответствие с текущим потоком задач, так как требуется завершение работы всех исполнительных устройств 251, …, 25K рабочих ПЛИС.

Наиболее близким устройством того же назначения, к заявленному изобретению, по совокупности признаков, принятым за прототип, является вычислительный модуль 11 из реконфигурируемой вычислительной системы (RU №2798443 С1, МПК G06F 15/16, G06F 15/177, заявлен 09.12.2022, опубликовано 22.06.2023 Бюл. №18), содержащий входной порт высокоскоростного интерфейса PCI-Express, выходной порт высокоскоростного интерфейса PCI-Express, порт управления охлаждением и питанием вычислительного модуля, порт мониторинга и управления вычислительного модуля, коммутатор PCI-Express 12 вычислительного модуля, системную ПЛИС 38 вычислительного модуля, блок 34 управления режимом коммутатора PCI-Express 12 вычислительного модуля, память 36 стартовой конфигурации системной ПЛИС 38 вычислительного модуля, блок 35 конфигурирования вычислительных ПЛИС, блок 39 мониторинга и управления вычислительного модуля, блок 40 автоматического управления вычислительного модуля, блок 41 управления охлаждением и питанием вычислительного модуля, память 37 базовой стартовой конфигурации вычислительных ПЛИС 131, …, 13М с индивидуальным питанием и группа из М блоков 261, …, 26М индивидуального управления режимом совычислителей, группу из М совычислителей 271, …, 27М с индивидуальным питанием, каждый из которых содержит интерфейсный блок 28, коммутатор 29 совычислителя и группа из L вычислительных ядер 301, …,30L, и группу из М вычислительных ПЛИС 131, …, 13М с индивидуальным питанием, каждая из которых содержит, объединенные в статическом регионе 14 частичной реконфигурации вычислительной ПЛИС, контроллер 16 PCI-Express, память 17 конфигурации коммутатора, блок 18 управления коммутатором, блок 19 автоматического управления, буферную память 20 данных, буферную память 21 результата, контроллер 22 прямого доступа в память, коммутатор 23 вычислительной ПЛИС, адаптер 24 совычислителя и, объединенные в динамическом регионе 31 частичной реконфигурации вычислительной ПЛИС, группу из Q исполнительных устройств 331, …, 33Q и группу из Q адаптеров исполнительных устройств 321, …,32Q.

Недостатком данного вычислительного модуля является не эффективное перераспределение вычислительных ресурсов между задачами пользователей.

Причиной, препятствующей достижению технического результата, является то, что у данного вычислительного модуля имеется возможность оперативно (динамически) перераспределять вычислительные ресурсы между задачами, включающими только однотипные исполнительные устройства.

Под однотипными исполнительными устройствами следует понимать такие, для реализации которых требуется одно и тоже количество виртуальных областей динамического региона и конфигурационные последовательности для которых получены для одного и того же коммутатора 23 статического региона.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании вычислительного модуля с динамическим перераспределением вычислительных ресурсов в зависимости от текущего потока задач.

Техническим результатом предлагаемого изобретения является расширение функциональных возможностей и повышение производительности за счет одновременного решения различных задач на исполнительных устройствах разного типа в одной вычислительной ПЛИС и совмещения процессов решения текущих задач и реконфигурирования виртуальных областей динамического региона.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что вычислительный модуль с динамическим перераспределением вычислительных ресурсов содержит входной порт 1 высокоскоростного интерфейса PCI-Express, выходной порт 2 высокоскоростного интерфейса PCI-Express, коммутатор 3 PCI-Express, блок 23 управления режимом коммутатора 3 PCI-Express, генератор 4 опорной частоты вычислительных ПЛИС, генератор 5 опорной частоты совычислителей, блок 6 формирования синхронизации совычислителей, блок 31 конфигурирования вычислительных ПЛИС, системную ПЛИС 32, блок 33 мониторинга и управления, блок 34 автоматического управления, память 35 стартовой конфигурации системной ПЛИС, память 36 базовой стартовой конфигурации вычислительных ПЛИС, порт 37 контроля и управления JTAG, порт 38 мониторинга и управления, порт 39 управления охлаждением и питанием, блок 40 управления охлаждением и питанием, а также содержит группу из М блоков 261, …, 26М индивидуального управления режимом совычислителей, группу из М вычислительных ПЛИС 71, …, 7М с индивидуальным питанием и группу из М совычислителей 271, …, 27М с индивидуальным питанием, каждый из которых содержит интерфейсный блок 28, коммутатор 29 совычислителя и группу из L вычислительных ядер 301, …, 30L.

причем каждая из М вычислительных ПЛИС 71, …, 7М содержит, объединенные в статический регион 8, блок 9 автореконфигурации, контроллер 10 PCI-Express, память 11 конфигурации коммутаторов, блок 12 управления автоблокировкой, блок 13 управления коммутатором, блок 14 индивидуального автоматического управления, буферную память 15 данных, буферную память 16 результата, контроллер 17 прямого доступа в память, коммутатор 18 статического региона, адаптер 19 совычислителя, блок 20 формирования синхронизации, и, объединенные в динамический регион группу из N виртуальных областей 211, …, 21N, каждая из которых состоит из группы из К исполнительных устройств 251, …, 25К, группы из К адаптеров 241, …, 24К исполнительных устройств и коммутатора 22,

причем коммутатор 3 PCI-Express соединен с входным портом 1, с выходным портом 2, с системной ПЛИС 32 и с контроллерами 10 PCI-Express вычислительных ПЛИС 71, …, 7М по высокоскоростному интерфейсу PCI-Express, а также с блоком 23 управления режимом коммутатора 3 PCI-Express, который соединен с системной ПЛИС 32, которая соединена с памятью 35 стартовой конфигурации системной ПЛИС, с памятью 36 базовой стартовой конфигурации вычислительных ПЛИС, с блоком 31 конфигурирования вычислительных ПЛИС, с блоком 33 мониторинга и управления, который соединен с портом 38 мониторинга и управления, с вычислительными ПЛИС 71, …, 7М, с совычислителями 271, …, 27М и с блоком 34 автоматического управления, который соединен с блоками 14 индивидуального автоматического управления вычислительных ПЛИС, с блоками 261, …, 26М индивидуального управления режимом совычислителей и с блоком 40 управления охлаждением и питанием, который соединен с портом 39 управления охлаждением и питанием, с вычислительными ПЛИС 71, …, 7М и с совычислителями 271, …, 27М, которые соединены с соответствующими одноименными блоками 261, …, 26М индивидуального управления режимом совычислителей, которые соединены с блоками 14 индивидуального автоматического управления в соответствующих одноименных вычислительных ПЛИС 71, …, 7М, в которых соединены с соответствующим адаптером 19 совычислителя, который соединен с интерфейсным блоком 28 в соответствующих одноименных совычислителях, в которых соединен с коммутатором 29 одноименного совычислителя, который соединен с вычислительными ядрами 301, …, 30L одноименного совычислителя,

кроме того порт 37 контроля и управления JTAG соединен с вычислительными ПЛИС 71, …, 7М и системной ПЛИС 32, которая соединена с генератором 4 опорной частоты вычислительных ПЛИС и генератором 5 опорной частоты совычислителей, который соединен с блоком 6 формирования синхронизации совычислителей, который соединен с совычислителями 271, …, 27М, а генератор 4 опорной частоты вычислительных ПЛИС соединен с блоками 20 формирования синхронизации, при этом блок 31 конфигурирования вычислительных ПЛИС соединен с вычислительными ПЛИС 71, …, 7М,

при этом в каждой из вычислительных ПЛИС 71, …, 7М адаптер 19 совычислителя соединен с коммутатором 18 статического региона, который соединен с блоком 13 управления коммутатором и с контроллером 17 прямого доступа в память, который соединен с буферной памятью 15 данных, с буферной памятью 16 результата, с контроллером 10 PCI-Express и с памятью 11 конфигурации коммутаторов, которая соединена с блоком 13 управления коммутатором и с контроллером 10 PCI-Express, блок 20 формирования синхронизации соединен с виртуальными областями 211, …, 21N, в которых коммутаторы 22 соединены с коммутатором 18 статического региона 8 и адаптерами 241, …, 24К исполнительных устройств, которые соединены с соответствующими исполнительными устройствами 251, …, 25К, а блок 9 автореконфигурации соединен с контроллером 10 PCI-Express и блоком 12 управления автоблокировкой, который соединен с блоком 13 управления коммутатором и блоком 20 формирования синхронизации.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

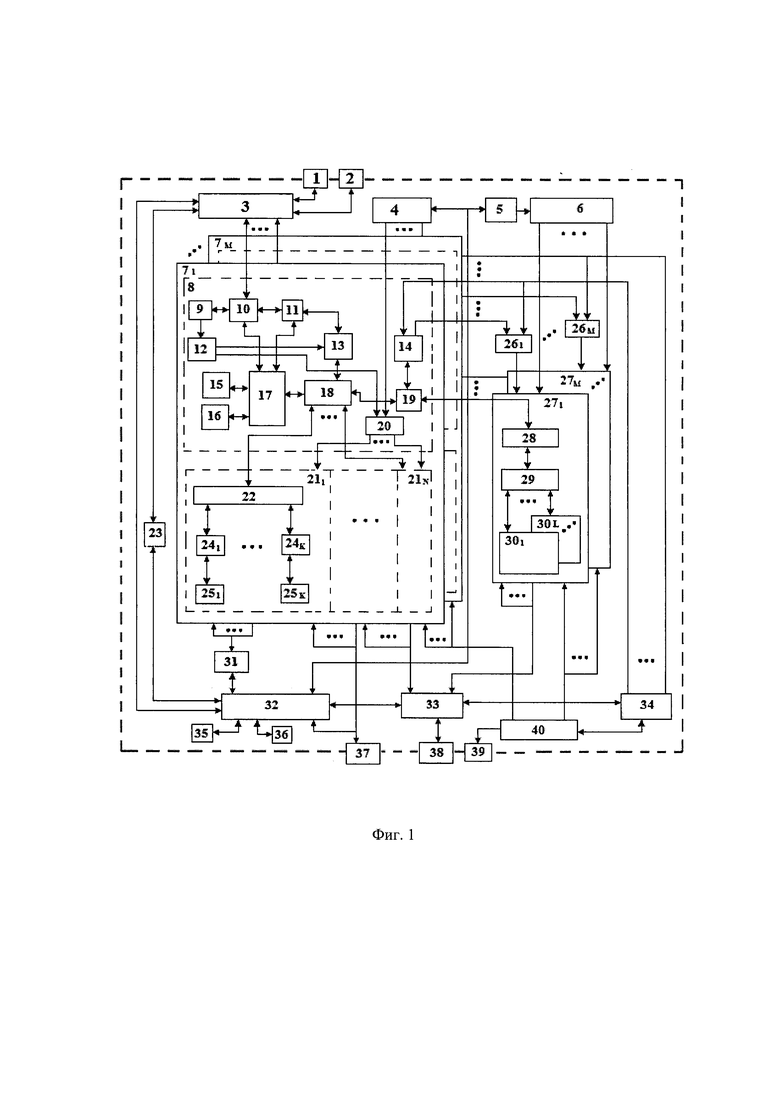

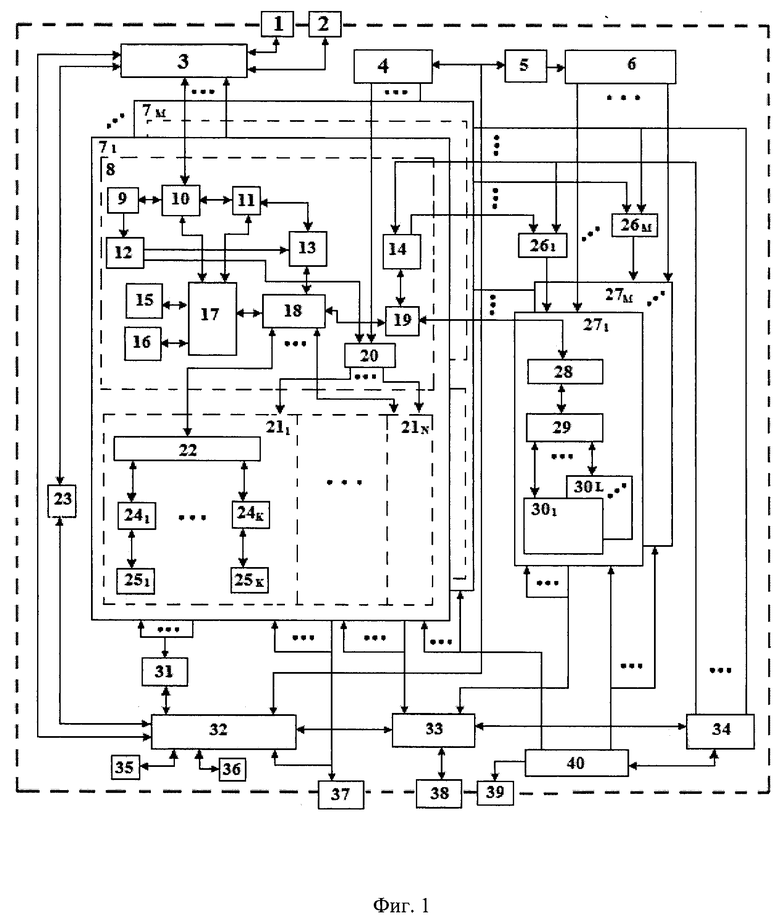

На фиг. 1 приведена функциональная схема вычислительного модуля с динамическим перераспределением вычислительных ресурсов.

На фиг. 1 и в тексте приняты следующие сокращения и обозначения:

РВС - реконфигурируемая вычислительная система;

М - количество вычислительных ПЛИС и совычислителей в вычислительном модуле;

L - количество вычислительных ядер в совычислителе;

N - количество виртуальных областей;

K - количество виртуальных зон в виртуальной области;

1 - входной порт высокоскоростного интерфейса PCI-Express;

2 - выходной порт высокоскоростного интерфейса PCI-Express;

3 - коммутатор PCI-Express;

4 - генератор опорной частоты вычислительных ПЛИС;

5 - генератор опорной частоты совычислителей;

6 - блок формирования синхронизации совычислителей;

71, …, 7М - группа из М вычислительных ПЛИС с индивидуальным питанием;

8 - статический регион;

9 - блок автореконфигурации;

10 - контроллер PCI-Express;

11 - память конфигурации коммутаторов;

12 - блок управления автоблокировкой;

13 - блок управления коммутатором;

14 - блок индивидуального автоматического управления;

15 - буферная память данных;

16 - буферная память результата;

17 - контроллер прямого доступа в память;

18 - коммутатор статического региона;

19 - адаптер совычислителя;

20 - блок формирования синхронизации;

211, …, 21N - группа из N виртуальных областей;

22 - коммутатор;

23 - блок управления режимом коммутатора 3 PCI-Express;

241, …, 24К - группа из К адаптеров исполнительных устройств;

251, …, 25К - группа из К исполнительных устройств;

261, …, 26М - группа из М блоков индивидуального управления режимом совычислителей;

271, …, 27М - группа из М совычислителей с индивидуальным питанием;

28 - интерфейсный блок совычислителя;

29 - коммутатор совычислителя;

301, …, 30L - группа из L вычислительных ядер совычислителя;

31 - блок конфигурирования вычислительных ПЛИС;

32 - системная ПЛИС;

33 - блок мониторинга и управления;

34 - блок автоматического управления;

35 - память стартовой конфигурации системной ПЛИС;

36 - память базовой стартовой конфигурации вычислительных ПЛИС;

37 - порт контроля и управления JTAG;

38 - порт мониторинга и управления;

39 - порт управления охлаждением и питанием;

40 - блок управления охлаждением и питанием.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Под динамическим регионом следует понимать совокупность виртуальных областей 211, …, 21N, которые могут быть корректно переконфигурированы в режиме частичной реконфигурации без нарушения работы исполнительных устройств и соответствующих совычислителей.

Статический регион 8 вычислительной ПЛИС является неизменяемой частью программы вычислительных ПЛИС 71, …, 7М, которая предназначена для организации взаимодействия исполнительных устройств 251, …, 25К виртуальных областей 211, …, 21N динамического региона и вычислительных ядер 301, …, 30L совычислителей 271, …, 27М с программами пользователей, организации формирования синхронизации динамического региона и автореконфигурирования требуемых компонент виртуальных областей 211, …, 21N.

Под виртуальной областью 211, …, 21N динамического региона понимается такая его часть, в которой имеет место единая синхронизация, независимая от синхронизации других виртуальных областей, и которая может быть корректно переконфигурирована независимо от других виртуальных областей в режиме частичной реконфигурации без нарушения их работы.

Под виртуальной зоной виртуальной области 211, …, 21N понимается такая ее часть, которая может быть корректно переконфигурирована независимо от других виртуальных зон данной виртуальной области в режиме частичной реконфигурации при условии блокировки синхронизации во всей виртуальной области, что предполагает ожидание завершения очередных интервалов работы всех исполнительных устройств данной виртуальной области.

Коммуникационная среда - это система, предназначенная для обмена информацией между компонентами вычислительного модуля и его внешними портами. В предлагаемом вычислительном модуле с динамическим перераспределением вычислительных ресурсов реализована трехуровневая коммуникационная среда, обеспечивающая взаимодействие программы пользователя (задачи) с исполнительными устройствами и вычислительными ядрами.

Первый уровень коммуникационной среды реализован на коммутаторе 3 PCI-Express, основан на использовании стандартного протокола PCI-Express, обеспечивает унифицированное объединение контроллеров 10 PCI-Express вычислительных ПЛИС 71, …, 7М и простое подключение предлагаемого вычислительного модуля к внешней управляющей ЭВМ реконфигурируемой вычислительной системы.

Второй уровень коммуникационной среды реализован на коммутаторе 18 статического региона 8 вычислительных ПЛИС 71, …, 7М, который использует как стандартные, так и специализированные протоколы.

Третий уровень коммуникационной среды реализован на коммутаторах 22 виртуальных областей 211, …, 21N динамического региона вычислительных ПЛИС 71, …, 7М для подключения конкретных исполнительных устройств 251, …, 25К и коммутаторах 28 совычислителей 271, …, 27М для подключения конкретных вычислительных ядер, которые также использует как стандартные, так и специализированные протоколы.

Состав и назначение компонент.

Входной порт 1 интерфейса PCI-Express предназначен для связи с управляющей ЭВМ в составе РВС.

Выходной порт 2 интерфейса PCI-Express предназначен для подключения аналогичных вычислительных модулей к управляющей ЭВМ в составе РВС и объединения с другой управляющей ЭВМ.

Блок 23 управления коммутатором PCI-Express предназначен для управления режимами работы коммутатора 3 PCI-Express по входному 1 и выходному 2 портам при подключении дополнительных вычислительных модулей или объединении с другой управляющей ЭВМ.

Память 35 стартовой конфигурации системной ПЛИС 32 предназначена для хранения стартовой программы системной ПЛИС 32, загружающейся в нее по включению питания.

Системная ПЛИС 32 взаимодействует со служебными программами управляющей ЭВМ посредством коммутатора 3 PCI-Express и предназначена для управления коммутатором 3 PCI-Express, посредством блока управления 23, для записи памяти 36 базовой стартовой конфигурации вычислительных ПЛИС 71, …, 7М и для записи памяти 35 стартовой конфигурации, и обеспечивает управление блоком 31 конфигурирования вычислительных ПЛИС, блоком 33 мониторинга и блоком 34 автоматического управления.

Порт 37 контроля и управления JTAG предназначен для работы в режиме настройки и начального конфигурирования программными средствами САПР системной ПЛИС 32, вычислительных ПЛИС 71, …, 7М, а также памяти 35 стартовой конфигурации системной ПЛИС.

Блок 31 конфигурирования вычислительных ПЛИС 71, …, 7М предназначен для организации конфигурирования как из памяти 36 базовой стартовой конфигурации, так и независимого конфигурирования отдельных вычислительных ПЛИС рабочими программами, включающими программы статического региона 8 и программы виртуальных областей 211, …, 21N с использованием и без режима частичной реконфигурации под управлением системной ПЛИС 32.

Блок 33 мониторинга предназначен для сбора и обработки информации о состоянии (температура, напряжение питания) вычислительных ПЛИС 71, …, 7М и совычислителей 271, …, 27М, организации взаимодействия с внешней системой мониторинга по порту 38 мониторинга, с блоком 34 автоматического управления и с блоком 40 управления охлаждением и питанием.

Контроллер 10 PCI-Express и контроллер 17 прямого доступа в память с буферными памятями данных 15 и результатов 16 вычислительных ПЛИС 71, …, 7М предназначены для организации высокоскоростного обмена с управляющей ЭВМ через коммутатор 3 PCI-Express по входному 1 и выходному 2 портам высокоскоростного интерфейса PCI-Express.

Память 11 конфигурации коммутаторов предназначена для хранения характеристик исполнительных устройств 251, …, 25К виртуальных областей 211, …, 21N динамического региона вычислительных ПЛИС 71, …, 7М и совычислителей 271, …, 27М, а также параметров их взаимодействия с задачами пользователя, имеет максимальный формат для данного типа вычислительных ПЛИС с учетом коммутатора 18 статического региона 8 и коммутаторов 22 виртуальных областей 211, …, 21N.

Исполнительные устройства 251, …, 25К виртуальных областей 211, …, 21N - это ускорители вычислений, аппаратно реализующие трудоемкие фрагменты задач пользователей и реализованные на ресурсах вычислительных ПЛИС 71, …, 7М с индивидуальным питанием.

Адаптеры 241, …, 24К исполнительных устройств пользователей предназначены для согласования протокола коммутатора 22 виртуальных областей 211, …, 21М с протоколами конкретных исполнительных устройств 251, …,25К-

Адаптеры 19 совычислителей предназначены для согласования протокола совычислителей 271, …, 27М с протоколом коммутатора 18 статического региона вычислительных ПЛИС 71, …, 7М.

Интерфейсные блоки 28 совычислителей 271, …, 27М предназначены для согласования протокола адаптера 19 с протоколом коммутатора 29 совычислителей 271, …, 27М.

Вычислительные ядра 301, …, 30L - это ускорители вычислений, предназначенные для программно-аппаратной реализации трудоемких фрагментов задач пользователей и реализованные на ресурсах совычислителей 271, …, 27М.

Блок 40 управления питанием и охлаждением предназначен для организации индивидуального управления питанием вычислительных ПЛИС 71, …, 7М и совычислителей 271, …, 27М (включить/выключить питание) и организации взаимодействия с системой управления скоростью вращения вентиляторов охлаждения по порту 39.

Для снижения энергопотребления включение питания на совычислителях 271, …, 27М осуществляется посредством блоков 261, …, 26М индивидуального управления режимом совычислителей блоком 14 индивидуального автоматического управления по команде от адаптера 19 совычислителя только во время его использования для вычислений.

Кроме этого блок 14 индивидуального автоматического управления совместно с блоками 261, …, 26М индивидуального управления режимом совычислителей 271, …, 27М и блоком 34 автоматического управления осуществляет автоматическую регулировку интенсивности потока задач, выполняемых на совычислителях 271, …, 27М в зависимости от их текущего температурного режима, путем замедления выполнения очередных заданий с целью охлаждения совычислителей 271, …, 27М для уменьшения вероятности превышения аварийного температурного порога.

Генератор 4 опорной частоты вычислительных ПЛИС 71, …, 7М совместно с блоком 20 формирования синхронизации предназначенные для обеспечения независимой рабочей синхронизацией виртуальных областей 211, …, 21N, позволяют осуществлять программирование параметров синхронизации от системной ПЛИС 32, независимую блокировку синхронизации в виртуальных областях подлежащих конфигурированию в режиме частичной реконфигурации и функционировать при этом исполнительным устройствам других виртуальных областей.

Генератор 5 опорной частоты совычислителей 271, …, 27М совместно с блоком 6 формирования синхронизации работы ядер 301, …, 30L, предназначенные для обеспечения независимой рабочей синхронизацией ядер 301, …, 30L совычислителей 271, …, 27М, позволяют осуществлять программирование параметров синхронизации от системной ПЛИС 32 и функционировать при реконфигурации любых виртуальных областей 211, …, 21N вычислительных ПЛИС 71, …, 7М.

Блок 9 автореконфигурации предназначен для выполнения конфигурирования как исполнительных устройств с адаптерами в отдельных виртуальных зонах, так и виртуальных областей 211, …, 21N в целом в режиме частичной реконфигурации.

Блок 12 управления автоблокировкой предназначен для выполнения автоматической блокировки синхронизации виртуальной области и соответствующего ей канала коммутатора 18 через блок 13 управления коммутатором при конфигурировании в режиме частичной реконфигурации данной виртуальной области.

Базовая стартовая программа вычислительных ПЛИС 71, …, 7М находится в памяти 36 базовой стартовой конфигурации и содержит программу статического региона 8 с максимально возможными форматами коммутатора 18 статического региона и коммутатора 22 виртуальных областей 211, …, 21N для данного типа вычислительной ПЛИС. Это необходимо для того, чтобы формат памяти 11 конфигурации коммутаторов был в дальнейшем фиксированным, для обеспечения возможности описания реальных коммутаторов 22 виртуальных областей 211, …, 21N динамического региона. При этом сам коммутатор 18 выполнен в виде N-конечной «звезды» с возможностью блокировки любого луча для выполнения корректного реконфигурирования сопряженной с ним виртуальной области.

Условия синтеза исполнительных устройств.

Предлагаемый вычислительный модуль с динамическим перераспределением вычислительных ресурсов позволяет использовать в работе исполнительные устройства, требующие для своей реализации как несколько виртуальных зон одной виртуальной области, так и из нескольких виртуальных областей 211, …, 21N динамического региона без переконфигурирования статического региона.

Синтез конфигурационных последовательностей исполнительных устройств 251, …, 25К с соответствующими адаптерами 241, …, 24К для режима частичной реконфигурации должен осуществляться совместно с заданным статическим регионом 8 и коммутаторами 18 и 22 максимального формата для данного типа вычислительной ПЛИС.

При синтезе «крупных» исполнительных устройств выполняется последовательное объединение ресурсов смежных виртуальных зон виртуальных областей 211, …, 21N, причем к неиспользуемым портам коммутаторов 22 должны быть подключены только адаптеры, возвращающие на любую команду по этому порту код неиспользуемого порта, а в памяти 11 конфигурации коммутаторов по этим портам должен быть также прописан код неиспользуемого порта с нулевым размером обслуживаемого буфера. По такому же принципу должно осуществляться объединение ресурсов смежных виртуальных областей 211, …, 21N при синтезе более «крупных» исполнительных устройств.

Данный принцип позволяет пользователям единожды синтезировать конфигурационные последовательности исполнительных устройств для всех доступных случаев подключения, с возможностью их последующего объединения с другими как внутри виртуальных областей, так и между виртуальными областями 211, …, 21N, и формирования корректных суммарных конфигурационных последовательностей для режима частичной автореконфигурации.

Смежными виртуальными зонами виртуальных областей и смежными виртуальными областями следует считать такие, которые можно объединить (соединить) логическими связями для реализации «крупных» исполнительных устройств, которые не будут использовать ресурсы других (несмежных) зон и областей, чтобы не реконфигурировать последние.

Предлагаемый вычислительный модуль с динамическим перераспределением вычислительных ресурсов в составе реконфигурируемой вычислительной системы с управляющей ЭВМ работает следующим образом.

После подключения вычислительного модуля к портам 1 и 2 интерфейса PCI-Express, к подсистеме мониторинга по порту 38 и к порту 39 управления питанием и охлаждением, осуществляется централизованное включение питания на вычислительном модуле и выполняется загрузка стартовой конфигурации системной ПЛИС 32 из памяти 35. После этого системная ПЛИС 32 включает питание на вычислительных ПЛИС 71, …, 7М и осуществляет загрузку в них базовых стартовых конфигураций из памяти 36, а также установку начальных порогов температурной защиты вычислительных ПЛИС 71, …, 7М и совычислителей 271, …, 27М в блоке 33 мониторинга.

Включение питания совычислителей 271, …, 27М осуществляется соответствующей вычислительной ПЛИС 71, …, 7М только в случае использования их вычислительных ресурсов задачами пользователей.

По окончании начальной подготовки предлагаемого вычислительного модуля к работе осуществляется загрузка операционной системы управляющей ЭВМ и выполняется привязка контроллеров 10 PCI-Express вычислительных ПЛИС 71, …, 7М к адресному пространству управляющей ЭВМ (номер вычислительного модуля в вычислительной системе и номер контроллера 10 PCI-Express в коммуникационной среде первого уровня коммутатора 3 вычислительного модуля).

После этого осуществляется считывание содержания памяти 11 конфигурации коммутаторов, выделение требуемых буферов в памяти управляющей ЭВМ и привязка последних к вычислительным ресурсам исполнительных устройств 251, …, 25К виртуальных областей 211, …, 21N вычислительных ПЛИС 71, …, 7М и вычислительных ядер 301, …, 30L совычислителей 271, …, 27М. Привязка осуществляется путем записи в память 11 конфигурации коммутаторов прямых (физических) адресов буферов обмена, выделенных для них вычислительной системой.

На каждое исполнительное устройство 251, …, 25К виртуальных областей 211, …, 21N и каждое вычислительное ядро 301, …, 30L совычислителей 271, …, 27М в памяти управляющей ЭВМ выделяются:

- буфер для обрабатываемых данных;

- буфер для результатов обработки;

- буфер для выполняемой программы, параметров и текущего состояния исполнительного устройства и вычислительного ядра.

Для каждого исполнительного устройства 251, …, 25К виртуальных областей 211, …, 21N и каждого вычислительного ядра 301, …, 30L совычислителей 271, …, 27М память 11 конфигурации коммутаторов содержит следующую информацию:

- признак исполнительного устройства (0) или номер адаптера 19 (не равен 0) совычислителя 27 (содержится в памяти 11 конфигурации коммутаторов);

- номер (тип) задачи выполняемой исполнительным устройством 251, …, 25К виртуальных областей 211, …, 21N или вычислительным ядром 301, …, 30L из общего списка задач (содержится в памяти 11 конфигурации коммутаторов);

- номер (адрес) адаптера исполнительного устройства 241, …, 24К виртуальных областей 211, …, 21N или вычислительного ядра 301, …, 30L (содержится в памяти 11 конфигурации коммутаторов);

- начальные (физические) адреса буферов в адресном пространстве управляющей ЭВМ (записываются в память 11 конфигурации коммутаторов после привязки);

- объемы буферов необходимые для выполнения задачи в исполнительных устройствах 251, …, 25К виртуальных областей 211, …, 21N или ядрах 301, …, 30L (содержится в памяти 11 конфигурации коммутаторов).

Исполнительные устройства 251, …, 25К виртуальных областей 211, …, 21N или ядра 301, …, 30L могут быть как однотипные, так и разные. Загрузка тех или иных осуществляется в процессе обработки текущего потока задач пользователей, в режиме частичной реконфигурации, которая может выполняться как системной ПЛИС 32, так и непосредственно самими вычислительными ПЛИС 71, …, 7М в режиме частичной реконфигурации блоком 9 автореконфигурации.

Память 11 конфигурации коммутаторов по всем исполнительным устройствам и вычислительным ядрам содержит следующую информацию:

{(X)(ZJ)(J)(F)(nJ)(I)(nI)(A)(B)(C)(Na)(Nb)(Nc)},

где X - признак исполнительного устройства (0) или совычислителя (1);

ZJ - номер (тип) задачи из общего списка задач исполнительных устройств и вычислительных ядер;

J - номер порта коммутатора 18 (0, …, N) - соответствует виртуальной области;

F - рабочая частота виртуальной области;

nJ - признак неиспользуемого порта коммутатора 18 (0);

I- номер порта коммутатора 22 (0, …, K) или вычислительного ядра (0, …, L);

nI - признак неиспользуемого порта коммутатора 22 (0);

А, В, С - начальные (физические) адреса буферов в памяти управляющей ЭВМ;

Na, Nb, Nc - объем буферов в памяти управляющей ЭВМ.

Алгоритм взаимодействия задачи пользователя с операционной системой управляющей ЭВМ реализует:

- выделение массивов под переменные задачи;

- выделение выполняемой задаче исполнительных устройств и вычислительных ядер совычислителей из имеющихся в наличие и свободных на текущий момент;

- привязка адресов массивов логических переменных обрабатываемых данных и результатов выполняемой программы, параметров и текущего состояния к буферам, выделенным исполнительным устройствам и соответствующим вычислительным ядрам;

- загрузку программ и параметров в выделенные исполнительные устройства и вычислительные ядра, и их активация, после которой ими выставляются запросы на получения данных для обработки или новых программ и параметров.

В процессе выполнения задачи осуществляется следующее:

- загрузка данных в соответствующие буфера выделенных задаче исполнительных устройств и вычислительных ядер из массива данных задачи;

- старт и анализ завершения обработки данных выделенными задаче исполнительными устройствами и вычислительными ядрами;

- выгрузка результатов из соответствующих буферов, выделенных задаче исполнительных устройств и вычислительных ядер в массив результатов;

- анализ на продолжение или окончание задачи, освобождение в последнем случае выделенных задаче исполнительных устройств, вычислительных ядер и массивов переменных.

После освобождения выделенных задаче исполнительных устройств и вычислительных ядер они остаются активными и, после перезагрузки в них программ и параметров от другой задачи могут принимать участие в ее решении.

Порядок динамической замены исполнительных устройств.

Если в текущем потоке задач требуются другие исполнительные устройства, то в предлагаемом вычислительном модуле предусмотрена возможность их динамической замены в режиме частичной реконфигурации на фоне работы исполнительных устройств остальных виртуальных областей.

Реконфигурация исполнительных устройств в зависимости от необходимости может осуществляться как внутри виртуальных областей 211, …, 21N, так и с объединением последних, причем внутри виртуальных областей может происходить объединение, как в пределах отдельных зон, так и области целиком. В любом случае предварительно осуществляется обнуление памяти 11 конфигурации коммутаторов соответствующей реконфигурируемым областям, и соответственно обнуляются и рабочие частоты данных виртуальных областей.

После этого выполняется реконфигурация заданных виртуальных зон и областей системной ПЛИС 32 или блоком 9 автореконфигурации вычислительных ПЛИС. В обоих случаях осуществляется блокировка рабочей синхронизации требуемой виртуальной области и блокировка соответствующего ей канала коммутатора 18 блоком 12 управления автоблокировкой, причем в первом случае она осуществляется программно, а во втором аппаратно на время реконфигурации.

По окончании реконфигурации (автореконфигурации) осуществляется запись соответствующей информации в память 11 конфигурации коммутаторов, устанавливаются рабочие частоты заданных виртуальных областей, снимаются блокировки рабочих частот и каналов коммутатора 18 и формируется сигнал сброса.

Так как коммутатор 18 выполнен в виде N-конечной «звезды» с возможностью блокировки только необходимых лучей и формирование рабочей синхронизации осуществляется блоком 20 из опорной частоты генератора 4 независимо по виртуальным областям, то исполнительные устройства остальных виртуальных областей имеют возможность продолжать выполнение своих задач на фоне реконфигурации, что уменьшает простои и увеличивает производительность предлагаемого вычислительного модуля.

Перераспределение вычислительных ресурсов.

Перераспределение вычислительных ресурсов между задачами осуществляется на основании анализа состояния исполнительных устройств и характеристик текущего потока задач по принципу максимального использования вычислительных ресурсов, а именно минимизации количества неиспользуемого оборудования, что обеспечивает увеличение производительности вычислительного модуля с динамическим перераспределением вычислительных ресурсов.

При занятости всех имеющихся вычислительных ресурсов, вновь поступающие задачи (фрагменты задач) также анализируются, но переводятся в режим ожидания освобождения требуемых вычислительных ресурсов.

В случае, когда освобождающиеся вычислительные ресурсы остаются незатребованными для вновь поступающих задач, осуществляется концентрация решаемых текущих задач в отдельных виртуальных областях 211, …, 21N вычислительных ПЛИС, с целью полного освобождения некоторых виртуальных областей и автореконфигурации их в режиме частичной реконфигурации для выполнения вновь поступающих задач.

Задачи с одинаковым приоритетом выполнения запускаются в порядке поступления на свободных вычислительных ресурсах. При поступлении задач более высокого приоритета к текущим задачам осуществляется высвобождение ресурсов от текущих задач (фактическое замедление исполнения задач с более низким приоритетом) и передача их вычислительных ресурсов в распоряжение приоритетных, по мере выполнения которых они возвращаются к прерванным задачам обратно. Высвобождение вычислительных ресурсов от текущих задач низкого приоритета осуществляется, для минимизации потерь при перезапуске, только после полного завершения обработки очередного конечного блока данных, чтобы не производить сохранение промежуточных результатов, что бывает к тому же не всегда возможно.

В случае поступления задач, имеющих более высокий приоритет к текущим задачам и требующих для своего выполнения реконфигурации не только исполнительных устройств с соответствующими адаптерами, а и статического региона 8 в целом, осуществляется высвобождение вычислительных ПЛИС 71, …, 7М от текущих задач целиком и передача их в распоряжение приоритетных задач. Реконфигурация статического региона 8 осуществляется системной ПЛИС 32.

ПРИМЕР ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Предлагаемый вычислительный модуль с динамическим перераспределением вычислительных ресурсов может быть реализован на следующих элементах:

системная ПЛИС 32 - на микросхеме XC6VLX75T-1FFG784C фирмы Xilinx;

вычислительные ПЛИС 71, …, 7М - на микросхемах XCKUP15P-FFVA1156C фирмы Xilinx;

коммутатор 3 PCI-Express - на микросхеме PEX8748-CA80BCG фирмы PLX Technology;

блок 31 конфигурирования вычислительных ПЛИС 71, …, 7М - на микросхемах CPLD ХС2С64А;

память 35 стартовой конфигурации системной ПЛИС 32 - на микросхеме MT25QU128 ABA1EW9-0SIT;

память 36 базовой стартовой конфигурации вычислительных ПЛИС 71, …, 7М - на микросхеме MT25QU512ABA1EW9-0SIT;

блок 33 мониторинга и управления - на микросхемах TMP461AIRUNT, МАХ6656 и CPLD ХС2С64А;

программируемые генераторы опорных частот вычислительных ПЛИС 71, …, 7М и совычислителей 5 - на микросхемах 570FCA000133DG.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый вычислительный модуль с динамическим перераспределением вычислительных ресурсов решает поставленную задачу и соответствует заявляемому техническому результату -расширение функциональных возможностей и повышение производительности за счет одновременного решения различных задач на исполнительных устройствах разного типа в одной вычислительной ПЛИС и совмещения процессов решения текущих задач и реконфигурирования виртуальных областей динамического региона.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2022 |

|

RU2798443C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОЗАДАЧНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2021 |

|

RU2780169C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И УПРАВЛЕНИЯ | 2018 |

|

RU2699254C1 |

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2019 |

|

RU2720556C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И АВТОМАТИЧЕСКИМ УПРАВЛЕНИЕМ | 2020 |

|

RU2748454C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2019 |

|

RU2713757C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2017 |

|

RU2677363C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2018 |

|

RU2686004C1 |

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ С СУБМОДУЛЯМИ | 2020 |

|

RU2748299C1 |

| Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой | 2016 |

|

RU2635896C1 |

Изобретение относится к области вычислительной техники. Техническим результатом является повышение производительности устройства. Устройство содержит входной и выходной порты, коммутатор интерфейса PCI-Express, генераторы опорной частоты вычислительных ПЛИС и совычислителей, блок формирования синхронизации совычислителей, блок конфигурирования вычислительных ПЛИС, системную ПЛИС, памяти стартовой конфигурации системной ПЛИС и базовой конфигурации вычислительных ПЛИС, порты контроля и управления JTAG, мониторинга и управления, управления охлаждением и питанием, группу из М вычислительных ПЛИС с индивидуальным питанием, каждая из которых содержит, объединенные в статический регион, блок автореконфигурации, контроллер PCI-Express, память конфигурации коммутаторов, блок управления автоблокировкой, коммутатор статического региона, адаптер совычислителя, блок формирования синхронизации, и, объединенные в динамический регион, группу из N виртуальных областей, каждая из которых состоит из К исполнительных устройств, К адаптеров и коммутатора, и группу из М совычислителей с индивидуальным питанием, каждый из которых содержит интерфейсный блок, коммутатор совычислителя и группу из L вычислительных ядер. 1 ил.

Вычислительный модуль с динамическим перераспределением вычислительных ресурсов содержит входной порт 1 высокоскоростного интерфейса PCI-Express, выходной порт 2 высокоскоростного интерфейса PCI-Express, коммутатор 3 PCI-Express, блок 23 управления режимом коммутатора 3 PCI-Express, генератор 4 опорной частоты вычислительных ПЛИС, генератор 5 опорной частоты совычислителей, блок 6 формирования синхронизации совычислителей, блок 31 конфигурирования вычислительных ПЛИС, системную ПЛИС 32, блок 33 мониторинга и управления, блок 34 автоматического управления, память 35 стартовой конфигурации системной ПЛИС, память 36 базовой стартовой конфигурации вычислительных ПЛИС, порт 37 контроля и управления JTAG, порт 38 мониторинга и управления, порт 39 управления охлаждением и питанием, блок 40 управления охлаждением и питанием, а также содержит группу из М блоков 261, …, 26М индивидуального управления режимом совычислителей, группу из М вычислительных ПЛИС 71, …, 7М с индивидуальным питанием и группу из М совычислителей 271, …, 27М с индивидуальным питанием, каждый из которых содержит интерфейсный блок 28, коммутатор 29 совычислителя и группу из L вычислительных ядер 301, …, 30L,

причем каждая из М вычислительных ПЛИС 71, …, 7М содержит, объединенные в статический регион 8, блок 9 автореконфигурации, контроллер 10 PCI-Express, память 11 конфигурации коммутаторов, блок 12 управления автоблокировкой, блок 13 управления коммутатором, блок 14 индивидуального автоматического управления, буферную память 15 данных, буферную память 16 результата, контроллер 17 прямого доступа в память, коммутатор 18 статического региона, адаптер 19 совычислителя, блок 20 формирования синхронизации, и, объединенные в динамический регион, группу из N виртуальных областей 211, …, 21N, каждая из которых состоит из группы из К исполнительных устройств 251, …, 25К, группы из К адаптеров 241, …, 24К исполнительных устройств и коммутатора 22,

причем коммутатор 3 PCI-Express соединен с входным портом 1, с выходным портом 2, с системной ПЛИС 32 и с контроллерами 10 PCI-Express вычислительных ПЛИС 71, …, 7М по высокоскоростному интерфейсу PCI-Express, а также с блоком 23 управления режимом коммутатора 3 PCI-Express, который соединен с системной ПЛИС 32, которая соединена с памятью 35 стартовой конфигурации системной ПЛИС, с памятью 36 базовой стартовой конфигурации вычислительных ПЛИС, с блоком 31 конфигурирования вычислительных ПЛИС, с блоком 33 мониторинга и управления, который соединен с портом 38 мониторинга и управления, с вычислительными ПЛИС 71, …, 7М, с совычислителями 271, …, 27М и с блоком 34 автоматического управления, который соединен с блоками 14 индивидуального автоматического управления вычислительных ПЛИС, с блоками 261, …, 26М индивидуального управления режимом совычислителей и с блоком 40 управления охлаждением и питанием, который соединен с портом 39 управления охлаждением и питанием, с вычислительными ПЛИС 71, …, 7М и с совычислителями 271, …, 27М, которые соединены с соответствующими одноименными блоками 261, …, 26М индивидуального управления режимом совычислителей, которые соединены с блоками 14 индивидуального автоматического управления в соответствующих одноименных вычислительных ПЛИС 71, …, 7М, в которых соединены с соответствующим адаптером 19 совычислителя, который соединен с интерфейсным блоком 28 в соответствующих одноименных совычислителях, в которых соединен с коммутатором 29 одноименного совычислителя, который соединен с вычислительными ядрами 301, …, 30L одноименного совычислителя,

кроме того порт 37 контроля и управления JTAG соединен с вычислительными ПЛИС 71, …, 7М и системной ПЛИС 32, которая соединена с генератором 4 опорной частоты вычислительных ПЛИС и генератором 5 опорной частоты совычислителей, который соединен с блоком 6 формирования синхронизации совычислителей, который соединен с совычислителями 271, …, 27М, а генератор 4 опорной частоты вычислительных ПЛИС соединен с блоками 20 формирования синхронизации, при этом блок 31 конфигурирования вычислительных ПЛИС соединен с вычислительными ПЛИС 71, …, 7М,

при этом в каждой из вычислительных ПЛИС 71, …, 7М адаптер 19 совычислителя соединен с коммутатором 18 статического региона, который соединен с блоком 13 управления коммутатором и с контроллером 17 прямого доступа в память, который соединен с буферной памятью 15 данных, с буферной памятью 16 результата, с контроллером 10 PCI-Express и с памятью 11 конфигурации коммутаторов, которая соединена с блоком 13 управления коммутатором и с контроллером 10 PCI-Express, блок 20 формирования синхронизации соединен с виртуальными областями 211, …, 21N, в которых коммутаторы 22 соединены с коммутатором 18 статического региона 8 и адаптерами 241, …, 24К исполнительных устройств, которые соединены с соответствующими исполнительными устройствами 251, …, 25К, а блок 9 автореконфигурации соединен с контроллером 10 PCI-Express и блоком 12 управления автоблокировкой, который соединен с блоком 13 управления коммутатором и блоком 20 формирования синхронизации.

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2022 |

|

RU2798443C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОЗАДАЧНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2021 |

|

RU2780169C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И АВТОМАТИЧЕСКИМ УПРАВЛЕНИЕМ | 2020 |

|

RU2748454C1 |

| US 9898345 B2, 20.02.2018 | |||

| US 20140149715 A1, 29.05.2014 | |||

| KR 101393237 B1, 08.05.2014 | |||

| US 7051188 B1, 23.05.2006. | |||

Авторы

Даты

2024-07-18—Публикация

2023-11-14—Подача