Изобретение относится к области вычислительной техники, в частности, к реконфигурируемым вычислительным системам, предназначенным для решения вычислительно сложных, трудоемких задач с динамическим перераспределением вычислительных ресурсов в зависимости от текущего потока задач.

При решении вычислительно сложных задач осуществляется их декомпозиция на отдельные фрагменты, наиболее трудоемкие из которых выполняются при помощи ускорителей вычислений. К ускорителям вычислений в реконфигурируемых вычислительных системах относятся аппаратные ускорители, синтезированные на ресурсах вычислительных ПЛИС, и программно-аппаратные ускорители, реализуемые на различного типа совычислителях, представляющих собой заказные СБИС.

В настоящее время в реконфигурируемых вычислительных системах, использующих для обмена с управляющей ЭВМ интерфейс PCI-Express, распределение вычислительных ресурсов между пользователями (задачами) осуществляется с точностью до одной вычислительной ПЛИС.

С появлением более мощных вычислительных компонент, заказных СБИС, и развитием технологии создания мощных ПЛИС, когда их вычислительных ресурсов становится достаточно для размещения в них нескольких вычислительных устройств (как одинаковых, так и в общем случае разных), актуальным становится дифференцированное распределение вычислительных ресурсов между задачами

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известен вычислительный модуль для многозадачных вычислительных систем (RU №2780169 С1, МПК G06F 15/16, заявлена 29.11.2021, опубликовано 20.09.2022 Бюл. №26), содержащий входной порт 1 интерфейса PCI-Express, выходной порт 2 интерфейса PCI-Express, коммутатор 3 PCI-Express, блок 4 управления коммутатором PCI-Express, память 5 стартовой конфигурации системной ПЛИС 7, память 6 стартовой конфигурации рабочих ПЛИС, системная ПЛИС 7, порт 8 контроля и управления системной ПЛИС 7, блок 10 конфигурирования рабочих ПЛИС, блок 11 мониторинга, порт 12 мониторинга, блок 13 управления питанием и охлаждением, порт 14 управления питанием и охлаждением и группу из М вычислительных каналов 91, …, 9M, каждый из которых содержит рабочую ПЛИС 15 и совычислитель 26, причем рабочая ПЛИС 15 содержит контроллер 16 PCI-Express, память 17 конфигурации, блок 18 управления коммутатором 23 рабочей ПЛИС 15, адаптер 19 совычислителя 26, буферную память 20 данных, буферную память 21 результата, контроллер 22 прямого доступа в память, коммутатор 23 рабочей ПЛИС 15, группу из К адаптеров 241, …, 24K исполнительных устройств, группу из К исполнительных устройств 251, …, 25K, а совычислитель 26 содержит интерфейсный блок 27, коммутатор 28 совычислителя и группу из N вычислительных ядер 291, …, 24N, каждое из которых содержит память 30 программы и параметров, блок 31 управления, память 32 данных, операционный блок 33 и память 34 результата.

Недостатком данного вычислительного модуля является отсутствие возможности динамического (гибкого) перераспределения вычислительных ресурсов по потоку текущих задач.

Причинами, препятствующими достижению технического результата, является отсутствие возможности оперативного реконфигурирования вычислительных ПЛИС исполнительными устройствами в соответствие с текущим потоком задач.

Известна реконфигурируемая вычислительная система (RU №2713757 С1, МПК G06F 15/16, заявлено 29.04.2019, опубликовано 07.02.2020 Бюл. №4), содержащая коммутатор EtherNet 1 управления вычислительной системой, ведущий сервер 2, двухпортовую интерфейсную плату 5, сервер 3 управления задачами, оперативную память 6, группу из K ведомых вычислительных узлов 41, …, 4K и коммутатор PCI-Express 31, причем каждый из K ведомых вычислительных узлов 41, …, 4K содержит вычислительное устройство общего назначения 10 с оперативной памятью 12, группу из N реконфигурируемых вычислительных устройств 131, …, 13N, коммутатор PCI-Express 11, компьютер 8 и группу из N памятей состояния 91, …, 9K, а каждое из N реконфигурируемых вычислительных устройств 131, …, 13N содержит коммутатор PCI-Express 19, группу из М унифицированных посадочных мест 171, …, 17M с установленными соответствующими вычислительными ПЛИС 201, …, 20M, интерфейсную ПЛИС 22, группа из М унифицированных посадочных мест 181, …, 18M с установленными соответствующими вычислительными СБИС 331, …, 33M, с установленным над ними единым радиатором прямоугольной формы 27, блок конфигурирования и мониторинга 23, блок управления режимом 30 коммутатора PCI-Express 19, память 24 конфигураций ПЛИС, группу из М блоков индивидуального мониторинга и управления 151, …, 15M и группу из М памятей стартовых конфигураций 351, …, 35M, группу из М буферных памятей 371, …, 37M и группу из М контроллеров 381, …, 38M прямого доступа в память реконфигурируемых вычислительных устройств 131, …, 13N.

Недостатком данной реконфигурируемой вычислительной системы является не эффективное распределение вычислительных ресурсов между задачами пользователей.

Причинами, препятствующими достижению технического результата, является возможность распределения вычислительных ресурсов между задачами пользователей только с точностью до одной вычислительной ПЛИС.

Наиболее близким устройством того же назначения, к заявленному изобретению, по совокупности признаков, принятой за прототип, является реконфигурируемая вычислительная система с многоуровневой подсистемой мониторинга и автоматическим управлением (RU №2748454 С1, МПК G06F15/16, G06F15/80, заявлено 02.10.2020, опубликовано 25.05.2021 Бюл. №15), содержащая сетевой коммутатор 1 управления, ведущий сервер 2, сетевой коммутатор 31 мониторинга, коммутатор PCI-Express 3, блок 32 контроля и управления питанием, группу из K памятей 41, …, 4K и группу из K вычислительных узлов 51, …, 5K,

каждый из которых содержит вычислитель общего назначения 8, коммутатор 9 PCI-Express, коммутатор 10 PCI-Express, блок 29 мониторинга и управления, блок 28 контроля и управления вентиляторами охлаждения, блок 30 контроля и управления питанием, группу из N памятей 71, …, 7N состояния, блок 27 автоматического управления охлаждением и питанием вычислительного узла, группу из N памятей 61, …, 6N выполняемых задач и группу из N вычислительных модулей 111, …, 11N,

каждый из которых содержит коммутатор PCI-Express 12, группу из М вычислительных ПЛИС 161, …, 16M, системную ПЛИС 25, блок 20 управления режимом коммутатора 12 PCI-Express, память 24 стартовой конфигураций системной ПЛИС 25, группу из М памятей 131, …, 13M стартовых конфигураций вычислительных ПЛИС 161, …, 16M, группу из М совычислителей 191, …, 19M с индивидуальным питанием, группу из М блоков 181, …, 18M управления режимом совычислителей 191, …, 19M, блок 21 мониторинга и управления и блок 26 конфигурирования вычислительных ПЛИС 161, …, 16M и их памятей 131, …, 13M стартовых конфигураций, блок 23 автоматического управления охлаждением и питанием вычислительного модуля, блок 22 автоматического управления, группы из М блоков 171, …, 17M автоматического управления вычислительными ПЛИС и совычислителями, буферных памятей 141, …, 14M и контроллеров 151, …, 15M прямого доступа в память выполняемых задач.

Недостатком данной реконфигурируемой вычислительной системы с многоуровневой подсистемой мониторинга и автоматическим управлением является не эффективное распределение вычислительных ресурсов между задачами пользователей.

Причиной, препятствующей достижению технического результата, является то, что у данной реконфигурируемой вычислительной системы с многоуровневой подсистемой мониторинга и автоматическим управлением имеется возможность распределять вычислительные ресурсы между задачами только с точностью до одной вычислительной ПЛИС с совычислителем.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании реконфигурируемой вычислительной системы с динамическим перераспределением вычислительных ресурсов в зависимости от текущего потока задач.

Техническим результатом предлагаемого изобретения является повышение производительности и расширение функциональных возможностей за счет одновременного решения различных задач на исполнительных устройствах одной вычислительной ПЛИС и совычислителе.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что в реконфигурируемую вычислительную систему, содержащую сетевой коммутатор Ethernet 1 управления, ведущий сервер 2, коммутатор PCI-Express 3 вычислительных узлов, сетевой коммутатор Ethernet 46 мониторинга, блок 47 контроля и управления питанием вычислительных узлов, группу из К памятей 41, …, 4K выполняемых задач вычислительных узлов и группу из К вычислительных узлов 51, …, 5K,

каждый из которых содержит вычислитель общего назначения 8 вычислительного узла, коммутатор PCI-Express 9 вычислительного узла, коммутатор PCI-Express 10 вычислительных модулей вычислительного узла, блок 42 управления охлаждением и питанием вычислительного узла, блок 43 контроля и управления вентиляторами охлаждения вычислительного узла, блок 44 мониторинга и управления вычислительного узла, блок 45 контроля и управления питанием вычислительных модулей, группу из N памятей 61, …, 6N выполняемых задач вычислительных модулей, группу из N памятей 71, …, 7N состояния вычислительных модулей и группу из N вычислительных модулей 111, …, 11N,

каждый из которых содержит коммутатор PCI-Express 12 вычислительного модуля, системную ПЛИС 38 вычислительного модуля, блок 34 управления режимом коммутатора PCI-Express 12 вычислительного модуля, память 36 стартовой конфигурации системной ПЛИС 38 вычислительного модуля, блок 35 конфигурирования вычислительных ПЛИС, блок 39 мониторинга и управления вычислительного модуля, блок 40 автоматического управления вычислительного модуля, блок 41 управления охлаждением и питанием вычислительного модуля, группу из М совычислителей 271, …, 27M с индивидуальным питанием и группу из М вычислительных ПЛИС 131, …, 13M с индивидуальным питанием,

причем ведущий сервер 2 соединен с сетевым коммутатором Ethernet 46 мониторинга и с сетевым коммутатором Ethernet 1 управления, который соединен с вычислителями общего назначения 8 вычислительных узлов 51, …, 5K, а сетевой коммутатор Ethernet 46 мониторинга соединен с блоками 44 мониторинга и управления вычислительных узлов и с блоком 47 контроля и управления питанием вычислительных узлов, кроме того ведущий сервер 2 соединен с памятями 41, …, 4K выполняемых задач вычислительных узлов, с коммутатором PCI-Express 3 вычислительных узлов, который соединен с коммутаторами PCI-Express 10 вычислительных модулей вычислительных узлов 51, …, 5K,

в которых коммутаторы PCI-Express 9 вычислительного узла и PCI-Express 10 вычислительных модулей вычислительного узла соединены с коммутаторами PCI-Express 12 вычислительных модулей 111, …, 11N, кроме того коммутатор PCI-Express 9 вычислительного узла также соединен с вычислителем 8 общего назначения, который соединен с памятями 71, …, 7N состояния вычислительных модулей и с памятями 61, …, 6N выполняемых задач вычислительных модулей, блок 42 управления охлаждением и питанием вычислительного узла соединен с блоком 43 контроля и управления вентиляторами охлаждения вычислительного узла, с блоком 45 контроля и управления питанием вычислительных модулей и блоками 41 управления охлаждением и питанием вычислительных модулей, а блок 44 мониторинга и управления вычислительного узла соединен с блоком 45 контроля и управления питанием вычислительных модулей, с блоком 43 контроля и управления вентиляторами охлаждения вычислительного узла и с блоками 39 мониторинга и управления вычислительных модулей 111, …, 11N,

в каждом из которых системная ПЛИС 38 вычислительного модуля соединена с блоком 39 мониторинга и управления вычислительного модуля, с памятью 36 стартовой конфигурации системной ПЛИС вычислительного модуля и с блоком 35 конфигурирования вычислительных ПЛИС, кроме того коммутатор PCI-Express 12 вычислительного модуля соединен с системной ПЛИС 38 вычислительного модуля и с блоком 34 управления режимом коммутатора PCI-Express 12 вычислительного модуля, который соединен с системной ПЛИС 38 вычислительного модуля, а блок 39 мониторинга и управления вычислительного модуля соединен с вычислительными ПЛИС 131, …, 13M с индивидуальным питанием, с совычислителями 271, …, 27M с индивидуальным питанием и с блоком 40 автоматического управления вычислительного модуля, который соединен с блоком 41 управления охлаждением и питанием вычислительного модуля, а блок 35 конфигурирования вычислительных ПЛИС соединен с вычислительными ПЛИС 131, …, 13M с индивидуальным питанием,

дополнительно введены в каждый из вычислительных узлов 51, …, 5K память 15 состояния исполнительных устройств и память 25 частичной реконфигурации исполнительных устройств, в каждый из вычислительных модулей 111, …, 11K дополнительно введены память 37 базовой стартовой конфигурации вычислительных ПЛИС 131, …, 13M с индивидуальным питанием и группа из М блоков 261, …, 26M индивидуального управления режимом совычислителей, в каждую из вычислительных ПЛИС 131, …, 13M индивидуальным питанием дополнительно введены, объединенные в статическом регионе 14 частичной реконфигурации вычислительной ПЛИС, контроллер 16 PCI-Express, память 17 конфигурации коммутатора, блок 18 управления коммутатором, блок 19 автоматического управления, буферная память 20 данных, буферная память 21 результата, контроллер 22 прямого доступа в память, коммутатор 23 вычислительной ПЛИС, адаптер 24 совычислителя и, объединенные в динамическом регионе 31 частичной реконфигурации вычислительной ПЛИС, группа из Q исполнительных устройств 331, …, 33Q и группа из Q адаптеров исполнительных устройств 321, …, 32Q, а в каждый из совычислителей 271, … 27M дополнительно введены интерфейсный блок 28, коммутатор 29 совычислителя и группа из L вычислительных ядер 301, …, 30L,

причем в каждом из вычислительных узлов 51, …, 5K вычислитель 8 общего назначения вычислительного узла соединен с памятью 15 состояния исполнительных устройств и памятью 25 частичной реконфигурации исполнительных устройств,

а в каждом из вычислительных модулей 111, …, 11N память 37 базовой стартовой конфигурации вычислительных ПЛИС соединена с системной ПЛИС 38 вычислительного модуля, коммутатор 12 PCI-Express вычислительного модуля соединен с контроллерами 16 PCI-Express вычислительных ПЛИС 131, …, 13M с индивидуальным питанием, блок 40 автоматического управления вычислительного модуля соединен с блоками 19 автоматического управления и блоками 261, …, 26M индивидуального управления режимом совычислителей, которые соединены с совычислителями 271, …, 27M и блоками 19 автоматического управления, адаптеры 24 совычислителя соединены с интерфейсными блоками 28 совычислителей, которые соединены с коммутаторами 29 совычислителей, с которыми соединены вычислительные ядра 301, …, 30L,

а в каждой из вычислительных ПЛИС 131, …, 13M с индивидуальным питанием контроллер 16 PCI-Express соединен с памятью 17 конфигурации коммутатора и контроллером 22 прямого доступа в память, который соединен с памятью 17 конфигурации коммутатора, с буферной памятью 20 данных, с буферной памятью 21 результата и с коммутатором 23 вычислительной ПЛИС, который соединен с адаптером 24 совычислителя и с блоком 18 управления коммутатором, который соединен с памятью 17 конфигурации коммутатора,

кроме того в каждой из вычислительных ПЛИС 131, …, 13M с индивидуальным питанием адаптер 24 совычислителя соединен с блоком 19 автоматического управления, коммутатор 23 вычислительной ПЛИС соединен с адаптерами 321, …, 32Q исполнительных устройств, которые соединены с соответствующими исполнительными устройствами 331, …, 33Q.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

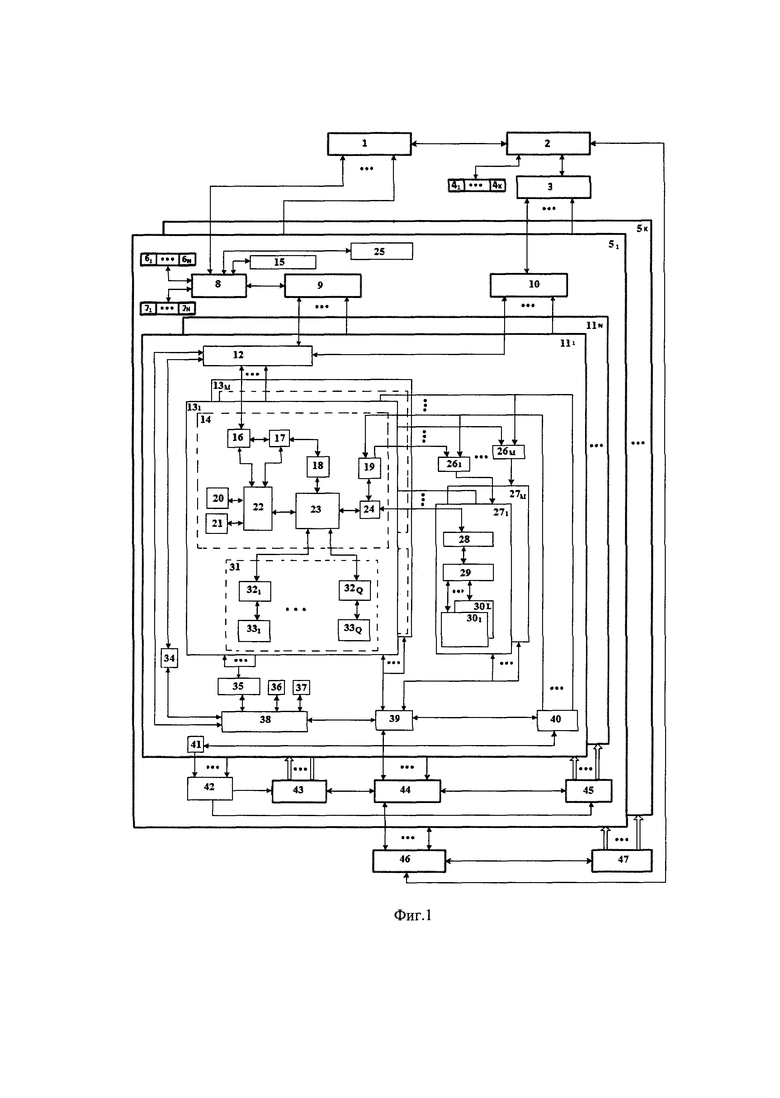

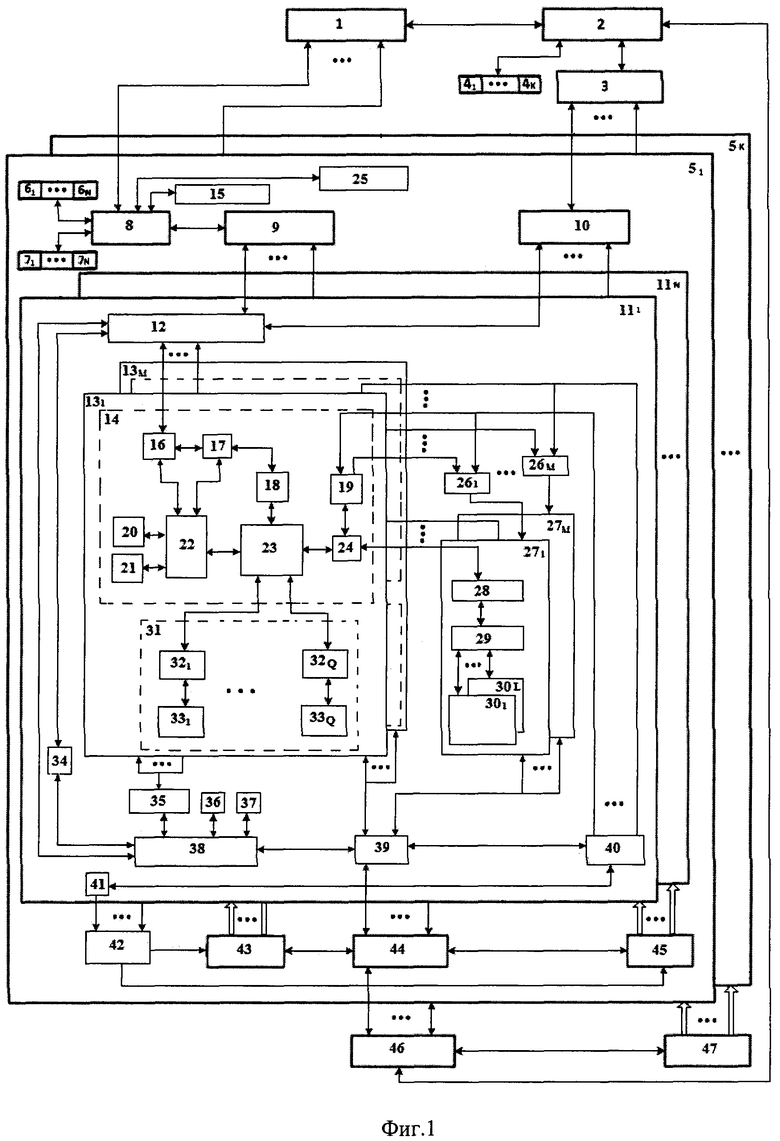

На фиг. 1 приведена функциональная схема предлагаемой реконфигурируемой вычислительной системы.

На фиг. 1 и в тексте приняты следующие сокращения и обозначения:

РВС - реконфигурируемая вычислительная система;

ВУ - вычислительный узел;

ВМ - вычислительный модуль;

ВЯ - вычислительное ядро;

СВ - совычислитель;

ИУ - исполнительное устройство;

КС - коммуникационная среда;

K - количество вычислительных узлов в реконфигурируемой вычислительной системе;

N - количество вычислительных модулей в вычислительном узле;

М - количество вычислительных ПЛИС и совычислителей в вычислительном модуле;

L - количество вычислительных ядер в совычислителе;

Q - количество ИУ в динамическом регионе вычислительных ПЛИС;

1 - сетевой коммутатор Ethernet управления;

2 - ведущий сервер;

3 - коммутатор PCI-Express вычислительных узлов;

41, …, 4K - группа из К памятей выполняемых задач вычислительных узлов;

51, …, 5K - группа из K вычислительных узлов;

61, …, 6N - группа из N памятей выполняемых задач вычислительных модулей;

71, …, 7N - группа из N памятей состояния вычислительных модулей;

8 - вычислитель общего назначения вычислительного узла;

9 - коммутатор PCI-Express вычислительного узла;

10 - коммутатор PCI-Express вычислительных модулей вычислительного узла;

111, …, 11N - группа из N вычислительных модулей;

12 - коммутатор PCI-Express вычислительного модуля;

131, …, 13M - группа из М вычислительных ПЛИС с индивидуальным питанием;

14 - статический регион частичной реконфигурации вычислительной ПЛИС;

15 - память состояния исполнительных устройств;

16 - контроллер PCI-Express;

17 - память конфигурации коммутатора;

18 - блок управления коммутатором;

19 - блок автоматического управления;

20 - буферная память данных;

21 - буферная память результата;

22 - контроллер прямого доступа в память;

23 - коммутатор вычислительной ПЛИС;

24 - адаптер совычислителя;

25 - память частичной реконфигурации исполнительных устройств;

261, …, 26M - группа из М блоков индивидуального управления режимом совычислителей;

271, …, 27M - группа из М совычислителей с индивидуальным питанием;

28 - интерфейсный блок;

29 - коммутатор совычислителя;

301, …, 30L - группа из L вычислительных ядер;

31 - динамический регион частичной реконфигурации вычислительной ПЛИС;

321, …, 32Q - группа из Q адаптеров исполнительных устройств;

331, …, 33MQ - группа из Q исполнительных устройств;

34 - блок управления режимом коммутатора PCI-Express 12 вычислительного модуля;

35 - блок конфигурирования вычислительных ПЛИС;

36 - память стартовой конфигурации системной ПЛИС вычислительного модуля;

37 - память базовой стартовой конфигурации вычислительных ПЛИС;

38 - системная ПЛИС вычислительного модуля;

39 - блок мониторинга и управления вычислительного модуля;

40 - блок автоматического управления вычислительного модуля;

41 - блок управления охлаждением и питанием вычислительного модуля;

42 - блок управления охлаждением и питанием вычислительного узла;

43 - блок контроля и управления вентиляторами охлаждения вычислительного узла;

44 - блок мониторинга и управления вычислительного узла;

45 - блок контроля и управления питанием вычислительных модулей;

46 - сетевой коммутатор Ethernet мониторинга;

47 - блок контроля и управления питанием вычислительных узлов.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

В предлагаемой реконфигурируемой вычислительной системе реализована четырехуровневая подсистема мониторинга и управления с использованием автоматического управления параметрами работы вычислительной системы: оперативное изменение скорости вращения вентиляторов охлаждения, оперативная остановка обработки данных вычислительными ПЛИС и СВ и оперативное отключение питания вычислительных ПЛИС и СВ в зависимости от их текущей температуры.

На первом уровне осуществляется локальное управление индивидуальными питаниями СВ 271, …, 27M, которое предполагает, как автоматическое «Аварийное» отключение вычислительными ПЛИС 131, …, 13M индивидуальных питаний от соответствующих СВ, так и отключение от них питания в период простоя для сокращения общей мощности потребления и, следовательно, тепловыделения.

На втором уровне также осуществляется локальный мониторинг и управление состоянием отдельных ВМ 111, …, 11N соответствующими системными ПЛИС 38, которые осуществляют сбор данных о текущем состоянии компонент ВМ, задействованных в процессе выполнения вычислений, а именно вычислительных ПЛИС 131, …, 13M и соответствующих СВ 271, …, 27M, управление их питанием, рабочими частотами, а также формирование кадров состояния вычислительных модулей в соответствующих памятях состояния 71, …, 7N.

На третьем уровне осуществляется мониторинг и управление состоянием ВУ 5ь 5n соответствующими блоками 44 мониторинга и управления вычислительных узлов, которые осуществляют включение питания на вычислительных узлах, а также управление скоростью вращения вентиляторов охлаждения.

Ведущий сервер 2 на четвертом уровне осуществляет централизованный сбор информации о состоянии всех компонент РВС и распределение заданий между ВУ 5ь 5n с учетом обеспечения их равномерного энергопотребления, а также в перераспределении заданий между ВУ 51, …, 5N в зависимости от их текущего энергопотребления и температурного режима для обеспечения максимально возможного уровня производительности РВС.

В случае обработки потока энергоемких вычислительных задач, выполнение которых приводит к необходимости работы системы охлаждения в экстремальном режиме, а именно с максимальной скоростью вращения вентиляторов при минимальной температуре воздушного потока, которых может быть недостаточно для нормального охлаждения вычислительных компонент, в предлагаемой РВС используются дополнительные меры, снижающие вероятность ошибок вычислений. К таким мерам, прежде всего, относятся уменьшение рабочей частоты выполнения вычислений и пропуск некоторых интервалов обработки с целью охлаждения вычислительных компонент. Это снижает фактическую производительность РВС, но оставляет вероятность ошибок вычислений на допустимом уровне и не делает необходимым проведение перепроверки результатов, что снижало бы производительность РВС еще больше.

В предлагаемой РВС используется автоматическое, то есть без программой обработки и непосредственного участия ведущего сервера 2, управление параметрами работы вычислительной системы: оперативное изменение скорости вращения вентиляторов охлаждения, оперативная остановка обработки данных вычислительными ПЛИС 131, …, 13M и СВ 271, …, 27M и оперативное отключение питания вычислительных ПЛИС и СВ в соответствии с трех пороговой системой автоматического управления, в зависимости от порогов текущей температуры: «Авария», «Внимание» или «Работа».

Порог «Авария» характеризуется температурой вычислительных ПЛИС и СВ близкой к температуре выхода из строя данных компонент, при котором выполняется отключение питания.

Порог «Внимание» характеризуется температурой вычислительных ПЛИС 131, …, 13M и 271, …, 27M близкой к температуре не достоверной работы (вероятные ошибки вычислений, ошибки при передаче), при котором выполняется повышение, если это еще возможно, скорости вращения вентиляторов охлаждения, остановка и повторение вычислений для повышения достоверности результатов.

Порог «Работа» характеризуется рабочей температурой вычислительных ПЛИС 131, …, 13M и СВ 271, …, 27M на задаче пользователя с заданной рабочей частотой в течение одного интервала обработки, при котором выполняется инициализация вычислений.

Интервал обработки - это время обработки для фиксированного набора входных данных по заданному алгоритму до получения результатов на заданной частоте обработки, которое характеризуется возможностью изменения частоты работы, выключения питания вычислительных ПЛИС 131, …, 13M и СВ 271, …, 27M без потери результатов и корректного перехода к следующему интервалу. По интервалу обработки, рабочей частоте, энергоемкости задачи пользователя и мощности системы охлаждения РВС вычисляется величина порога «Работа».

В предлагаемой РВС эффект снижения производительности в экстремальном режиме работы системы охлаждения уменьшается в связи с оперативной адаптацией системы управления к текущему температурному состоянию вычислительных ПЛИС 131, …, 13M и СВ 271, …, 27M.

Блок 40 автоматического управления в вычислительных модулях 111, …, 11N предназначен для анализа текущего температурного режима ВМ по информации от блока 39 мониторинга и управления вычислительного модуля и оперативного управления (без участия ведущего сервера 2) блоком 41 управления охлаждением и питанием вычислительного модуля и блоком 42 управления охлаждением и питанием вычислительного узла, предназначенных как для управления изменением текущей скорости вращения вентиляторов охлаждения, так и для управления аварийным отключением питания вычислительных модулей, в случаях, когда температура вычислительных ПЛИС 131, …, 13M и СВ 271, …, 27M превышает аварийный температурный порог «Авария».

Блок 40 автоматического управления вычислительного модуля осуществляет подготовку информации для формирования кадра текущего состояния системной ПЛИС 38, который передается в памяти 71, …, 7N состояния вычислительных модулей, и предназначен для принятия решения по управлению ведущим сервером 2 и вычислителями общего назначения 8 по аварийному отключению питания от вычислительных ПЛИС и СВ в ВМ и возврата в работу вычислительных ПЛИС и СВ после перехода их рабочей температуры к порогу «Работа».

Кроме того, блок 40 автоматического управления вычислительного модуля через блоки 261, … 26M индивидуального управления режимом совычислителей разрешает вычислительным ПЛИС 131, … 13M обработку очередных данных, при значении текущей температуры меньше или равной рабочему порогу «Работа», и предупреждает, при значении температуры больше или равной «Внимание», для остановки обработки очередных данных с целью охлаждения вычислительных ПЛИС 131, … 13M и СВ 271, …, 27M.

При наличии разрешения перехода к обработке очередных данных от блоков 261, … 26M индивидуального управления режимом совычислителей посредством соответствующих блоков 19 автоматического управления разрешают адаптерам 24 совычислителей выполнять запись очередных данных в буферную память 20, используя контроллеры прямого доступа 22, из памятей 61, …, 6N выполняемых задач вычислительного модуля, причем данная операция осуществляется только при условии обработки предыдущих данных при температуре меньше или равной «Внимание», иначе, после охлаждения соответствующих вычислительных ПЛИС 131, … 13M и СВ 271, …, 27M обработка данных должна повториться.

Для снижения энергопотребления РВС включение питания на СВ 271, …, 27M осуществляется посредством блоков 261 …, 26M индивидуального управления режимом совычислителей блоком 19 автоматического управления по команде от адаптера 24 совычислителя только во время его использования для вычислений.

Предлагаемая реконфигурируемая вычислительная система работает следующим образом.

При включении питания первыми включаются сетевой коммутатор Ethernet 1 управления РВС, сетевой коммутатор Ethernet 46 мониторинга РВС и ведущий сервер 2.

После этого ведущий сервер 2, как и в прототипе, осуществляет включение питания на вычислительных узлах 51, …, 5K уже и вычислительных модулях 111, …, 11N После загрузки вычислителей общего назначения 8 ведущий сервер 2 осуществляет размещение заданий в памяти выполняемых задач 41, …, 4K вычислительных узлов, которые содержат не только рабочие конфигурации вычислительных ПЛИС, исполнительные модули для вычислителей общего назначения 8, блоки исходных данных и рабочие частоты вычислительных ПЛИС и СВ, но и характеристики ожидаемой мощности потребления на рабочих частотах. Память выполняемых задач 41, …, 4K вычислительных узлов доступна вычислителям общего назначения 8, которые осуществляют считывание из них очередных заданий и запись их в память выполняемых задач 61, …, 6N вычислительных модулей.

Для обеспечения технического результата в предлагаемой реконфигурируемой вычислительной системе, а именно повышение производительности и расширение функциональных возможностей за счет одновременного решения различных задач на одной вычислительной ПЛИС и совычислителе, в вычислительных узлах 51, …, 5K, в отличие от прототипа, введены память 15 состояния исполнительных устройств, память 25 частичной реконфигурации исполнительных устройств и реализована трехуровневая коммуникационная среда, обеспечивающая взаимодействие программы пользователя (задачи) с исполнительными устройствами 331, …, 33Q вычислительных ПЛИС и вычислительными ядрами 301, …, 30L совычислителей, позволяющая осуществлять динамическое перераспределения вычислительных ресурсов в зависимости от текущего потока задач.

Первой и второй уровень коммуникационной среды реализуется на коммутаторах PCI_Express вычислительных узлов 51, …, 5K и вычислительных модулей 111, …, 11N, а третий реализуется на коммутаторах 23 вычислительных ПЛИС 131, …, 13M и коммутаторах 29 совычислителей 271, …, 27M

Каждому ИУ 331, …, 33Q вычислительных ПЛИС и ВЯ 301, …, 30L совычислителя ставится в соответствие область памяти вычислителя общего назначения 8 соответствующего вычислительного узла, обмен с которой реализует контроллер прямого доступа 22 посредством контроллера PCI_Express 16. При декомпозиции задач пользователей для выполнения на отдельных ИУ и ВЯ, взаимодействие программ осуществляется уже не с вычислительными ПЛИС, а с областями памяти, соответствующими выделенным для данной задачи ИУ 331, …, 33Q и ВЯ 301, …, 30L. В связи с этим на одной и той же ПЛИС, но различных ИУ того же типа могут выполняться трудоемкие фрагменты различных задач пользователей, при этом, для обеспечения максимальной производительности РВС, выполняемые текущие задачи распределяются на максимально возможное количество свободных в данный момент ИУ 331, …, 33Q.

Для обеспечения возможности динамической замены ИУ одного типа на другой, в зависимости от требований текущего потока задач, в составе каждой вычислительной ПЛИС 131, …, 13M имеются, объединенные в статический (не изменяемый) регион 14 контроллер 16 PCI-Express, память 17 конфигурации коммутатора, блок 18 управления коммутатором, блок 19 автоматического управления, буферная память 20 данных, буферная память 21 результата, контроллер 22 прямого доступа в память, коммутатор 23 вычислительной ПЛИС, адаптер 24 совычислителя, а также, объединенные в динамический регион 31, ИУ 331, …, 33Q с адаптерами 321, …, 32Q, которые предназначены для согласования интерфейса коммутатора 23 вычислительной ПЛИС с интерфейсами ИУ.

В зависимости от мощности используемых в РВС вычислительных ПЛИС и вычислительной мощности реализуемых на них ИУ, количество которых в одном ПЛИС может быть различное (Q=l, 2, …, Qmax). Qmax - это максимальное возможное число виртуальных областей, на которые может быть разбит динамический регион 31 вычислительных ПЛИС, которые могут независимо друг от друга конфигурироваться в режиме частичной реконфигурации.

Память 25 частичной реконфигурации исполнительных устройств предназначена для хранения библиотеки вариантов конфигураций статического региона 14 и конфигурационные последовательности для частичной конфигурации ИУ, использующихся при решении трудоемких задач.

Частичные конфигурации ИУ, хранящиеся в памяти 25, представляют собой наборы фрагментов конфигурации вычислительных ПЛИС и имеют следующие характеристики:

- выполняемая трудоемкая операция (ОП1, ОП2, …);

- рабочая частота;

- тип ИУ (T1, Т2, …), где Ti - число виртуальных областей динамического региона 31, необходимых для его реализации;

- порт (П1, П2, …), где Пj номер порта коммутатора 23, к которому подключается ИУ.

При появлении в реконфигурируемой вычислительной системе задач с новыми ИУ, текущая библиотека в памяти 25 может расширяться для обеспечения возможности более гибкого реагирования на поток задач в вычислительной системе.

Стартовое конфигурирование осуществляется системной ПЛИС 38 из памяти 37 базовой стартовой конфигурации по включению питания. Рабочее конфигурирование также осуществляется системной ПЛИС 38, но из памяти 25 частичной реконфигурации исполнительных устройств, в соответствии с потоком обрабатываемых задач. Размерность коммутатора 23 вычислительной ПЛИС и состав подключенных к нему ИУ по типам, фиксируется в памяти 17 конфигурации коммутатора и изменяется только при изменении состава ИУ по типам.

Реконфигурирование освобождающихся ИУ одного типа на ИУ другого типа без переконфигурирования всей вычислительной ПЛИС возможно только при наличии фрагмента конфигурационной последовательности, реализованной для данного типа ИУ при аналогичном коммутаторе 23 вычислительной ПЛИС (аналогичной конфигураций статического региона), с таким же количеством подключаемых ИУ, и осуществляется также системной ПЛИС 38.

Блок 18 управления коммутатором реализован в статическом 14 регионе частичной реконфигурации и предназначен для управления потоками данных и результатов для ИУ в соответствии с памятью 17 конфигурации коммутатора.

Контроллер 22 прямого доступа в память предназначен для организации взаимодействия ИУ 331, …, 33Q посредством коммутатора 23 вычислительной ПЛИС, контроллера 16 PCI-Express, буферных памятей данных 20 и результата 21, а также ВЯ 301, …, 30L совычислителя 27 посредством адаптера 24, интерфейсного блока 28 и коммутатора 29 совычислителя с выделенными им массивами памяти вычислителя общего назначения 8.

Память 15 состояния исполнительных устройств в вычислительных узлах 51, …, 5K предназначена для отображения содержания памятей 17 конфигурации коммутаторов 23 вычислительных ПЛИС 131, …, 13M соответствующих вычислительных модулей 11, …, 11N. Память 15 разделена на N*M секторов, где N соответствует числу вычислительных модулей в вычислительном узле, а М соответствует числу вычислительных ПЛИС в вычислительном модуле. Каждый сектор содержит информацию о текущем состоянии соответствующего коммутатора 23 вычислительной ПЛИС, к которой, прежде всего, относится тип используемого коммутатора (число портов). Каждый из портов характеризуется параметрами:

- выполняемая операция;

- рабочая частота;

- признак «Занято» или «Свободно»;

- распределенный адрес в системе;

- ожидаемое время завершения работы или процент выполнения задачи (или интервала обработки).

Задачи, поступающие для выполнения в вычислительные узлы, сопровождаются следующими характеристиками:

- число параллельно выполняемых одинаковых процессов;

- исходные данные и параметры для этих процессов;

- используемые трудоемкие операции в процессах (какие и их количество);

- конфигурационные последовательности для вычислительных ПЛИС, реализованные с учетом обеспечения частичной реконфигурации ИУ.

Распределение вычислительных ресурсов между задачами осуществляется вычислителем общего назначения 8 на основании анализа памяти 15 состояния исполнительных устройств и характеристик текущего потока задач по принципу максимального использования вычислительных ресурсов, а именно минимизации количества неиспользуемого оборудования, что обеспечивает увеличение производительности РВС.

После заполнения всех имеющихся вычислительных ресурсов, вновь поступающие задачи (фрагменты задач) также анализируются вычислителем общего назначения 8, но переводятся в режим ожидания освобождения требуемых вычислительных ресурсов.

В случае, когда освобождающиеся вычислительные ресурсы остаются незатребованными для вновь поступающих задач, осуществляется перемещение решаемых текущих задач и концентрация их в отдельных вычислительных ПЛИС, с целью полного освобождения некоторых ПЛИС и реконфигурации их для выполнения новых задач.

Задачи с одинаковым приоритетом выполнения запускаются параллельно в порядке поступления на освобождающихся вычислительных ресурсах. При поступлении задач более высокого приоритета к текущим задачам осуществляется высвобождение ресурсов от текущих задач (фактическое замедление исполнения задач с более низким приоритетом) и передача их вычислительных ресурсов в распоряжение приоритетных, по мере выполнения которых они возвращаются к прерванным задачам обратно.

ПРИМЕР ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Предлагаемая реконфигурируемая вычислительная система может быть реализована на следующих элементах:

В качестве ведущего сервера 2 РВС может быть использован сервер фирмы Kraftway на базе платформы Kraftway Express 200: процессор Intel(R) Xeon(R) E2620V4 2.10 GHz 8 cores; оперативная память 64 Gbyte; жесткий диск 1 Tbyte.

Вычислители общего назначения 8 ВУ: процессор Intel(R) Xeon(R) E2620V4 2.10 GHz 8 cores; оперативная память 64 Gbyte; жесткий диск 1 Tbyte; восемь ВМ 111, …, 118, содержащих по четыре вычислительных ПЛИС 131, …, 134 и четыре заказных СБИС в качестве СВ 271, …, 274, установленные на унифицированные посадочные места под типовой корпус HSBGA-400.

Вычислительные модули 11: системная ПЛИС 38 и вычислительные ПЛИС 131, …, 134 - на микросхемах фирмы Xilinx типа XC7A100T-FGG484; коммутатор PCI-Express 12 - на микросхеме коммутатора РЕХ8732 фирмы PLX Technology; блок 39 мониторинга и управления вычислительного модуля - на микросхемах МАХ6656 фирмы Maxim Integrated, TMP461AIRUNT фирмы Texas Instruments; блоки 26 управления режимом СВ - с использованием микросхем SI570; блок 35 конфигурирования вычислительных ПЛИС - на микросхеме CPLD ХС2С64А фирмы Xilinx; памяти стартовых конфигураций 36, 37 вычислительных ПЛИС и системной ПЛИС - на микросхемах SPI-памяти М25Р64 фирмы Micron Technology.

Блок 44 мониторинга и управления ВУ - на микросхеме фирмы Xilinx типа XC7Z007S-1CLG400C.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемая реконфигурируемая вычислительная система решает поставленную задачу и соответствует заявляемому техническому результату - повышение производительности и расширение функциональных возможностей за счет одновременного решения различных задач на исполнительных устройствах одной вычислительной ПЛИС и совычислителе.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И АВТОМАТИЧЕСКИМ УПРАВЛЕНИЕМ | 2020 |

|

RU2748454C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И УПРАВЛЕНИЯ | 2018 |

|

RU2699254C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ С ДИНАМИЧЕСКИМ ПЕРЕРАСПРЕДЕЛЕНИЕМ ВЫЧИСЛИТЕЛЬНЫХ РЕСУРСОВ | 2023 |

|

RU2823113C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОЗАДАЧНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2021 |

|

RU2780169C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2017 |

|

RU2677363C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2019 |

|

RU2713757C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2018 |

|

RU2686004C1 |

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ С СУБМОДУЛЯМИ | 2020 |

|

RU2748299C1 |

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2019 |

|

RU2720556C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2023 |

|

RU2815706C1 |

Изобретение относится к области вычислительной техники, в частности к реконфигурируемым вычислительным системам. Технический результат заключается в повышении производительности системы. Технический результат достигается за счет того, что система содержит ведущий сервер, сетевые коммутаторы, коммутаторы PCI-Express и К вычислительных узлов, каждый из которых содержит вычислитель общего назначения, коммутаторы PCI-Express и N вычислительных модулей. Каждый из вычислительных модулей содержит системную ПЛИС, коммутатор PCI-Express, М вычислительных ПЛИС и М совычислителей с индивидуальным питанием, а также памяти стартовой конфигурации ПЛИС, каждая из М вычислительных ПЛИС содержит контроллер PCI-Express, буферные памяти данных и результата, контроллер прямого доступа в память, коммутатор с памятью конфигурации и Q исполнительных устройств с адаптерами, а каждый из совычислителей содержит интерфейсный блок, коммутатор и L вычислительных ядер, для вычислительных ПЛИС используется принцип частичной реконфигурации, а каждый из К вычислительных узлов содержит память состояния и память частичной реконфигурации исполнительных устройств. 1 ил.

Реконфигурируемая вычислительная система, содержащая сетевой коммутатор Ethernet 1 управления, ведущий сервер 2, коммутатор PCI-Express 3 вычислительных узлов, сетевой коммутатор Ethernet 46 мониторинга, блок 47 контроля и управления питанием вычислительных узлов, группу из К памятей 41, …, 4K выполняемых задач вычислительных узлов и группу из К вычислительных узлов 51, …, 5K,

каждый из которых содержит вычислитель общего назначения 8 вычислительного узла, коммутатор PCI-Express 9 вычислительного узла, коммутатор PCI-Express 10 вычислительных модулей вычислительного узла, блок 42 управления охлаждением и питанием вычислительного узла, блок 43 контроля и управления вентиляторами охлаждения вычислительного узла, блок 44 мониторинга и управления вычислительного узла, блок 45 контроля и управления питанием вычислительных модулей, группу из N памятей 61, …, 6N выполняемых задач вычислительных модулей, группу из N памятей 71, …, 7N состояния вычислительных модулей и группу из N вычислительных модулей 111, …, 11N,

каждый из которых содержит коммутатор PCI-Express 12 вычислительного модуля, системную ПЛИС 38 вычислительного модуля, блок 34 управления режимом коммутатора PCI-Express 12 вычислительного модуля, память 36 стартовой конфигурации системной ПЛИС 38 вычислительного модуля, блок 35 конфигурирования вычислительных ПЛИС, блок 39 мониторинга и управления вычислительного модуля, блок 40 автоматического управления вычислительного модуля, блок 41 управления охлаждением и питанием вычислительного модуля, группу из М совычислителей 271,…, 27M с индивидуальным питанием и группу из М вычислительных ПЛИС 131, …, 13M с индивидуальным питанием,

причем ведущий сервер 2 соединен с сетевым коммутатором Ethernet 46 мониторинга и с сетевым коммутатором Ethernet 1 управления, который соединен с вычислителями общего назначения 8 вычислительных узлов 51, …, 5K, а сетевой коммутатор Ethernet 46 мониторинга соединен с блоками 44 мониторинга и управления вычислительных узлов и с блоком 47 контроля и управления питанием вычислительных узлов, кроме того, ведущий сервер 2 соединен с памятями 41, …, 4K выполняемых задач вычислительных узлов, с коммутатором PCI-Express 3 вычислительных узлов, который соединен с коммутаторами PCI-Express 10 вычислительных модулей вычислительных узлов 51, …, 5K,

в которых коммутаторы PCI-Express 9 вычислительного узла и PCI-Express 10 вычислительных модулей вычислительного узла соединены с коммутаторами PCI-Express 12 вычислительных модулей 111, …, 11N, кроме того, коммутатор PCI-Express 9 вычислительного узла также соединен с вычислителем 8 общего назначения, который соединен с памятями 71, …, 7N состояния вычислительных модулей и с памятями 61, …, 6N выполняемых задач вычислительных модулей, блок 42 соединен с блоком 43 контроля и управления вентиляторами охлаждения вычислительного узла, с блоком 45 контроля и управления питанием вычислительных модулей и блоками 41 управления охлаждением и питанием вычислительных модулей, а блок 44 мониторинга и управления вычислительного узла соединен с блоком 45 контроля и управления питанием вычислительных модулей, с блоком 43 контроля и управления вентиляторами охлаждения вычислительного узла и с блоками 39 мониторинга и управления вычислительных модулей 111, …, 11N,

в каждом из которых системная ПЛИС 38 вычислительного модуля соединена с блоком 39 мониторинга и управления вычислительного модуля, с памятью 36 стартовой конфигурации системной ПЛИС вычислительного модуля и с блоком 35 конфигурирования вычислительных ПЛИС, кроме того, коммутатор PCI-Express 12 вычислительного модуля соединен с системной ПЛИС 38 вычислительного модуля и с блоком 34 управления режимом коммутатора PCI-Express 12 вычислительного модуля, который соединен с системной ПЛИС 38 вычислительного модуля, а блок 39 мониторинга и управления вычислительного модуля соединен с вычислительными ПЛИС 131, …, 13M с индивидуальным питанием, с совычислителями 131, …, 13M с индивидуальным питанием и с блоком 40 автоматического управления вычислительного модуля, который соединен с блоком 41 управления охлаждением и питанием вычислительного модуля, а блок 35 конфигурирования вычислительных ПЛИС соединен с вычислительными ПЛИС 131, …, 13M с индивидуальным питанием,

дополнительно введены в каждый из вычислительных узлов 51, …, 5K память 15 состояния исполнительных устройств и память 25 частичной реконфигурации исполнительных устройств, в каждый из вычислительных модулей 111, …, 11K дополнительно введены память 37 базовой стартовой конфигурации вычислительных ПЛИС 131, …, 13M с индивидуальным питанием и группа из М блоков 261, …, 26M индивидуального управления режимом совычислителей, в каждую из вычислительных ПЛИС 131, …, 13M с индивидуальным питанием дополнительно введены, объединенные в статическом регионе 14 частичной реконфигурации вычислительной ПЛИС, контроллер 16 PCI-Express, память 17 конфигурации коммутатора, блок 18 управления коммутатором, блок 19 автоматического управления, буферная память 20 данных, буферная память 21 результата, контроллер 22 прямого доступа в память, коммутатор 23 вычислительной ПЛИС, адаптер 24 совычислителя и, объединенные в динамическом регионе 31 частичной реконфигурации вычислительной ПЛИС, группа из Q исполнительных устройств 331, …, 33Q и группа из Q адаптеров исполнительных устройств 331, …, 33Q, а в каждый из совычислителей 271, …, 27M дополнительно введены интерфейсный блок 28, коммутатор 29 совычислителя и группа из L вычислительных ядер 331, …, 30L,

причем в каждом из вычислительных узлов 51, …, 5K вычислитель 8 общего назначения вычислительного узла соединен с памятью 15 состояния исполнительных устройств и памятью 25 частичной реконфигурации исполнительных устройств,

а в каждом из вычислительных модулей 111, …, 11N память 37 базовой стартовой конфигурации вычислительных ПЛИС соединена с системной ПЛИС 38 вычислительного модуля, коммутатор 12 PCI-Express вычислительного модуля соединен с контроллерами 16 PCI-Express вычислительных ПЛИС 131, …, 13M с индивидуальным питанием, блок 40 автоматического управления вычислительного модуля соединен с блоками 19 автоматического управления и блоками 261, …, 26M индивидуального управления режимом совычислителей, которые соединены с совычислителями 271, …, 27M и блоками 19 автоматического управления, адаптеры 24 совычислителя соединены с интерфейсными блоками 28 совычислителей, которые соединены с коммутаторами 29 совычислителей, с которыми соединены вычислительные ядра 301, …, 30L,

а в каждой из вычислительных ПЛИС 131, …, 13M с индивидуальным питанием контроллер 16 PCI-Express соединен с памятью 17 конфигурации коммутатора и контроллером 22 прямого доступа в память, который соединен с памятью 17 конфигурации коммутатора, с буферной памятью 20 данных, с буферной памятью 21 результата и с коммутатором 23 вычислительной ПЛИС, который соединен с адаптером 24 совычислителя и с блоком 18 управления коммутатором, который соединен с памятью 17 конфигурации коммутатора,

кроме того, в каждой из вычислительных ПЛИС 131, …, 13M с индивидуальным питанием адаптер 24 совычислителя соединен с блоком 19 автоматического управления, коммутатор 23 вычислительной ПЛИС соединен с адаптерами 321, …, 32Q исполнительных устройств, которые соединены с соответствующими исполнительными устройствами 331, …, 33Q.

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2019 |

|

RU2713757C1 |

| US 20190205271 A1, 04.07.2019 | |||

| Бортовая литая алюминиевая шина для цинкоэлектролитных ванн | 1961 |

|

SU144357A1 |

| CN 111737941 A, 02.10.2020 | |||

| CN 101630305 A, 20.01.2010. | |||

Авторы

Даты

2023-06-22—Публикация

2022-12-09—Подача