Изобретение относится к системам передачи дискретной информации и может быть использовано в системах помехоустойчивой защиты информации.

При разработке декодирующих устройств актуальной задачей является повышение достоверности принимаемой информации в каналах связи с высоким уровнем помех.

Применение мягких решений дает дополнительную информацию для увеличения достоверности принимаемой информации для помехоустойчивого кода.

В основе мягкого декодирования лежит правило, которое состоит в выборе кодового слова с минимальным расстоянием до принятой последовательности. Это правило минимальной вероятности ошибки в последовательности. Реализующий его декодер является декодером максимального правдоподобия.

Такое правило может быть точно реализовано только для очень коротких кодов. В настоящее время методы мягкого декодирования более длинных кодов представляют собой попытки аппроксимировать это правило.

Известен способ устойчивой кодовой цикловой синхронизации при применении жестких и мягких решений и модуляции по типу стыка С1-ФЛ [Патент РФ №2812964, МПК H04L 7/08. Забабурин А.Н., Трушин С.А. Приор. 03.07.2023, опубл. 06.02.2023], заключающийся в том, что принятую входную последовательность и последовательности, полученные в результате суммирования входной последовательности с ненулевыми векторами ошибок, параллельно умножают на проверочный полином помехоустойчивого циклического кода БЧХ(31,16,7) и в результате умножения получают суммы синдромов помехоустойчивого циклического кода, нумерующей последовательности и фазирующей последовательности, затем полученные суммы умножают на проверочный полином нумерующей последовательности и получают суммы синдромов помехоустойчивого циклического кода и фазирующей последовательности, из каждой этой суммы вычитают синдром фазирующей последовательности и получают синдромы помехоустойчивого циклического кода БЧХ(31,21,5), при жестких решениях и нулевом векторе при мягких решениях синхронизацию проводят по кодовым словам БЧХ(31,21,5) с числом ошибок в них не более исправляющей способности кодовых слов БЧХ(31,16,7), равной (d-1)/2, где d есть минимальное кодовое расстояние слов БЧХ(31,16,7), при мягких решениях синхронизацию проводят по кодовым словам БЧХ(31,21,5), число ошибок в которых соответствует не более (d-1) ошибке для кодовых слов БЧХ(31,16,7), для исправления ошибок мягкими решениями в кодовых словах формируют векторы ошибок, количество которых зависит от выбора варианта схемы векторов ошибок, вариант схемы векторов ошибок характеризуется его максимальным числом различных векторов ошибок, при этом максимальное число различных векторов ошибок для каждого варианта равно 2Z, где z есть максимальное число ненадежных разрядов в слове, для которых формируют различные вектора ошибок данного варианта, для ненадежных разрядов в слове, превышающих число z, вектора ошибок не формируются, если после исправления мягкими решениями в кодовых словах БЧХ(31,21,5) останется не более двух ошибок, то эти ошибки исправляют жесткими решениями по синдромам кодовых слов БЧХ(31,21,5), для варианта, формирующего при мягких решениях шестнадцать векторов ошибок при четырех и более ненадежных разрядах в слове, все шестнадцать векторов ошибок различные, и при синхронизации для данного варианта максимальное количество исправляемых ошибок в слове БЧХ(31,21,5) может составить шесть, каждому биту в непрерывной последовательности, равной числу бит в кодовом слове циклического помехоустойчивого кода, присваивают свою метку, повторяющуюся постоянно через промежуток времени, соответствующий передаче одного кодового слова, поэтому такие метки определяют границы слов циклического помехоустойчивого кода и слов, образованных на стыке двух соседних слов циклического помехоустойчивого кода, пороговое значение числа кодовых слов в синхронизирующей последовательности равно минимальному набору кодовых слов, требуемому для декодирования блока, и синхронизацию проводят по кодовым словам с числом ошибок в них не более исправляющей способности кодовых слов, получаемых после снятия с входной последовательности синхронизирующих символов, для каждого слова блоков, соответствующего своей метке, синхронизированными счетчиками параллельно формируют полный набор нумерующих последовательностей, значения этих синхронизированных счетчиков параллельно увеличивают на единицу через промежуток времени, соответствующий передаче одного кодового слова, при достижении синхронизированными счетчиками их максимального значения следующее значение счетчиков соответствует их начальному значению и время цикла синхронизированного счетчика равно длительности нумерующей последовательности, для каждого синхронизированного счетчика одной определенной нумерующей последовательности есть свой набор счетчиков совпадений для всех разных меток, значения каждого синхронизированного счетчика из полного набора нумерующих последовательностей для каждой метки аппаратным способом параллельно сравнивают с номерами нумерующих последовательностей для соответствующего слова входной последовательности, которое анализируют в данный момент, при совпадении номера слова входной последовательности со значением синхронизированного счетчика нумерующей последовательности значение их счетчика совпадений увеличивают на единицу, если по окончании синхронизирующей последовательности в ее счетчике совпадений, соответствующем метке определенных слов входной последовательности, значение не достигло порогового значения, то только этот счетчик совпадений сбрасывают в исходное состояние, с целью исключения возможных срабатываний ложной синхронизации блоков по окончании каждой нумерующей последовательности проводят сравнение значения ее счетчика совпадений со значениями всех счетчиков совпадений остальных меток, в случае превышения или равенства числу, записанному в этом анализируемым счетчике совпадений, порогового значения и если в каком - либо из этих счетчиков меток значение равно или больше значения анализируемого счетчика совпадений или если значение анализируемого счетчика совпадения не достигло порогового значения по окончании этой нумерующей последовательности, тогда не принимают решение о кодовой цикловой синхронизации входной последовательности, при этом сбрасывают в исходное состояние только счетчик совпадений этой нумерующей последовательности и продолжают операцию определения правильной синхронизации блока, если по окончании каждой нумерующей последовательности значение ее счетчика совпадений превышает или становится равным пороговому значению и превышает значение любого счетчика совпадений всех меток, то принимают решение о кодовой цикловой синхронизации входной последовательности, при этом сбрасывают в исходное состояние все счетчики совпадений, с целью максимального исключения срабатываний ложной синхронизации блоков после определения правильной синхронизации запускают счетчик на промежуток времени, соответствующий длительности передачи одного блока, и если по окончании счета приходит подтверждение правильной синхронизации блока, то при дальнейшей передаче блоков все возможные срабатывания ложной синхронизации игнорируют внутри истинных блоков из кодовых слов, при этом в каждой очередной передаче блока идет подтверждение правильной синхронизации блока, если не приходит очередное подтверждение правильной синхронизации блока, то это означает либо окончание передачи сообщения, либо, в худшем случае, потерю блока, в таком случае алгоритм синхронизации переходит на поиск правильной синхронизации блока и нового подтверждения правильной синхронизации блока, в коррекционное устройство из канала поступает модулированная информация типа стыка С1-ФЛ, коррекционное устройство для каждого бита модулированной информации вычисляет его качество, по которому формируют признаки наименее достоверных битов, а для этих наименее достоверных битов формируют векторы ошибок, векторы ошибок, суммированные по модулю два с входной биимпульсной информацией, поступают в блок демодуляторов, на выходах которых формируют разряды слов БЧХ и слов, образованных на стыках слов БЧХ, далее эти слова поступают в блок фильтров Хаффмена, из коррекционного устройства биимпульсную последовательность, соответствующую модулированной информации по типу стыка С1-ФЛ, качество ее битов, и признаки наименее достоверных битов, чтобы не было потери, записывают в накопитель информации через регистр, учитывающий задержки обработки в демодуляторе, схеме формирования векторов ошибок и блоке фильтров Хаффмена.

Этот способ устойчивой кодовой цикловой синхронизации при применении жестких и мягких решений и модуляции по типу стыка С1-ФЛ обеспечивает достоверность принимаемой информации за счет высокой вероятности правильной синхронизации при применении жестких и мягких решений и простую схемотехническую реализацию. При этом алгоритм обработки информации реализован параллельно аппаратными решениями, что обеспечивает высокую скорость передачи информации.

Однако в этом способе устойчивой кодовой цикловой синхронизации при применении жестких и мягких решений и модуляции по типу стыка С1-ФЛ нет реализации декодирования кодов БЧХ и PC для восстановления искаженной переданной информации.

Наиболее близким к предлагаемому устройству (прототип) является устройство декодирования с мягкими решениями для двухступенчатого каскадного кода [Патент РФ №2485683, МПК Н03М 13/45. Забабурин А.Н., Квашенников В.В., Ромачева И.А., Третьяков А.Н., Трушин С.А. Приор. 02.04.2012, опубл. 20.06.2013], содержащее коррекционное устройство, вход INF которого является информационным входом устройства, а вход С которого является тактовым входом устройства, один из выходов коррекционного устройства соединен с входом схемы определения качества бита, другой выход коррекционного устройства соединен с входом демодулятора, один из выходов демодулятора соединен с одним из входов схемы определения качества символов и выбора наименее достоверных символов, другой вход которой соединен с выходом схемы определения качества бита, в устройство введены схема кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями, схема формирования векторов ошибок для наименее достоверных символов, блок сумматоров по модулю два, блок декодеров кода БЧХ, схема определения наименьшего веса, схема контроллера PC, при этом выход схемы определения качества символов и выбора наименее достоверных символов соединен с одним из входов схемы кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями, другой вход которой соединен с выходом демодулятора, выходы Q1QU, CDCH, SR схемы кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями соединены с входами схемы формирования векторов ошибок для наименее достоверных символов, выход схемы формирования векторов ошибок для наименее достоверных символов соединен с одним из входов блока сумматоров по модулю два, а другой вход блока сумматоров по модулю два соединен с выходом DBCH схемы кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями, а выходы блока сумматоров по модулю два соединены с входами D1-D8 блока декодеров кода БЧХ, который содержит восемь декодеров кода БЧХ, другие входы блока декодеров кода БЧХ соединены шиной BUS CL с выходами схемы кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями, выходы WBCH0-WBCH8 декодеров кода БЧХ соединены с входами схемы определения наименьшего веса, вход признаков наименее достоверных символов Q1QU и вход качества символов Q0QU которой соединены с выходами схемы кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями, выходы для управляющих сигналов СВСН и WRRG которой соединены по шине BUS CL с входами схемы определения наименьшего веса, а выходы разрешения Е1-Е8 которой соединены с входами блока декодеров кода БЧХ, выходы WZBCH0-WBZCH8 и QZER-QZER8 которого соединены с входами IN Ports контроллера PC, входы прерываний INT1, INT2, INT3 которого по шине BUS CL соединены с выходами для сигналов МО и SR схемы кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями, выходы d0-d4 которой соединены с входами контроллера PC, выход которого OUT Ports является информационным выходом устройства.

Недостатком этого устройства декодирования с мягкими решениями для двухступенчатого каскадного кода, является недостаточная достоверность принимаемой информации в каналах с высоким уровнем помех, так как не исключаются многие варианты ложной синхронизации блоков и не регистрируются многие варианты правильной синхронизации блоков.

Недостатком также является неточный алгоритм определения декодированного слова БЧХ с наименьшим весом к слову, поступившему из канала.

Цель изобретения - повышение достоверности принимаемой информации в каналах с высоким уровнем помех.

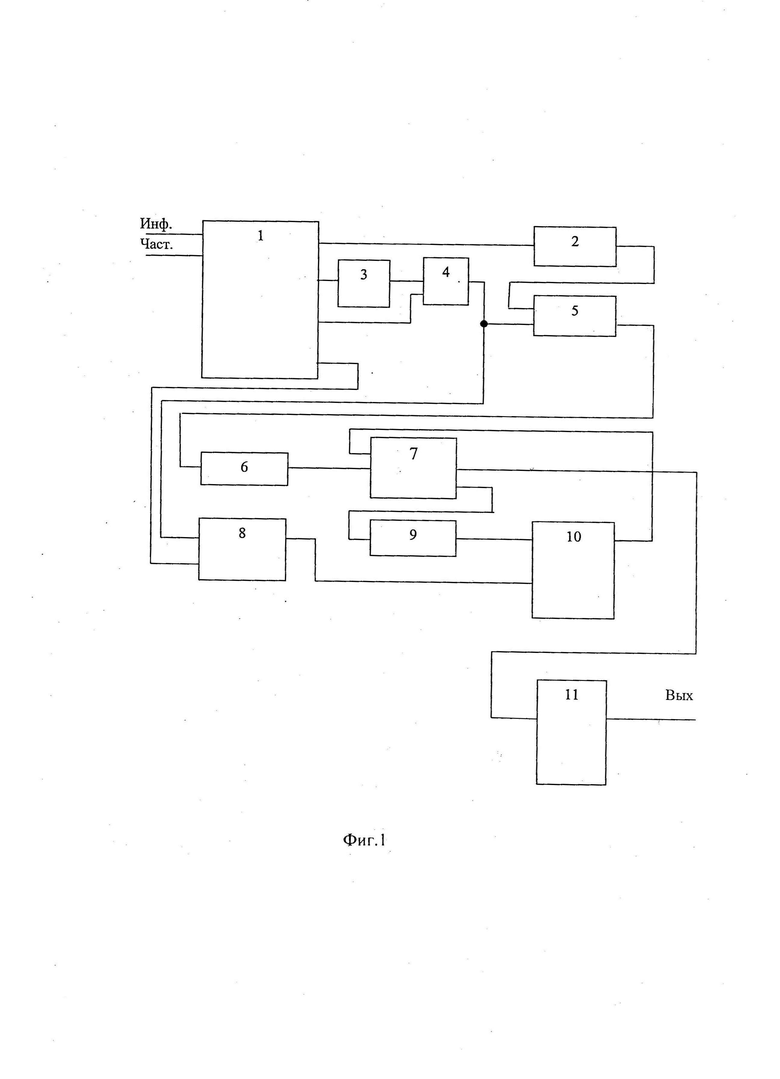

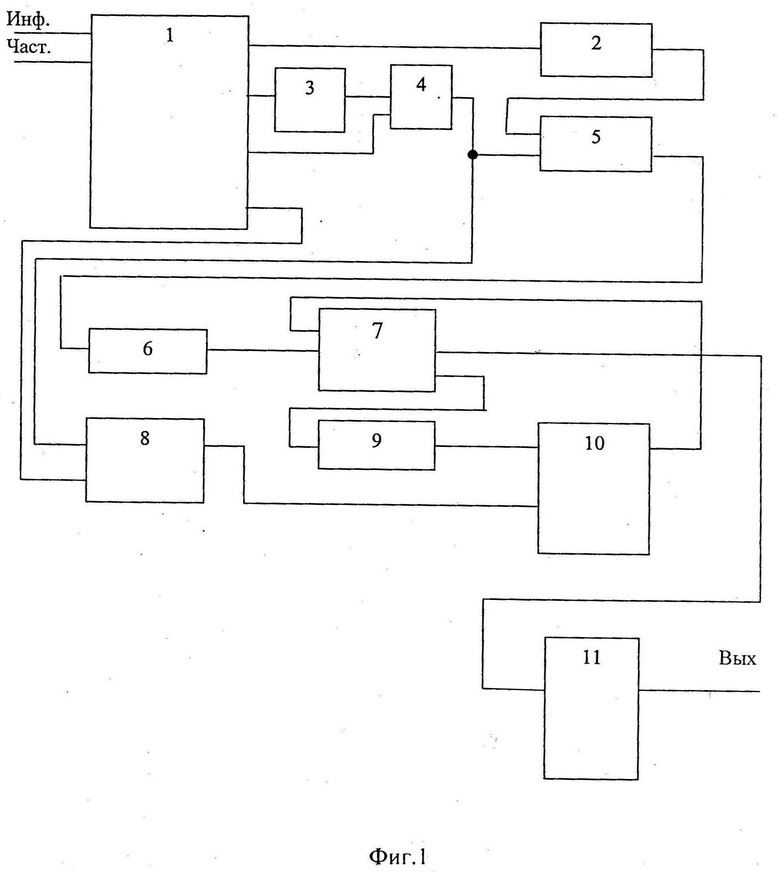

На фиг. 1 приведена структурная схема предлагаемого устройства декодирования с жесткими и мягкими решениями для двухступенчатого каскадного кода и модуляции по типу стыка С1-ФЛ.

Устройство декодирования с жесткими и мягкими решениями для двухступенчатого каскадного кода и модуляции по типу стыка С1-ФЛ содержит схему кодовой цикловой синхронизации 1, схему формирования векторов ошибок 2, постоянное запоминающее устройство (ПЗУ) 3, двухвходовой сумматор по модулю два 4, блок двухвходовых сумматоров по модулю два 5, блок демодуляторов биимпульсного кода БЧХ 6, блок декодеров кода БЧХ 7, ОЗУ 8, блок модуляторов кода БЧХ 9, схему определения слова кода БЧХ с наименьшим весом 10, контроллер декодера кода PC 11.

Устройство декодирования с жесткими и мягкими решениями для двухступенчатого каскадного кода и модуляции по типу стыка С1-ФЛ работает следующим образом.

На передающей стороне в качестве выходной информации формируют последовательность c1 ⊕ c2i ⊕ c3n представляющую собой поразрядную сумму по модулю два трех последовательностей: последовательности внутренних двоичных кодов каскадного кода c1, синхронизирующей двоичной последовательности с2=с21с22с23 … c2n и последовательности c3n=с3с3с3 … с3, нарушающей циклические свойства исходного кода и состоящей из повторяющихся циклических последовательностей, где n - число слов кода Боуза - Чоудхури - Хоквингема (БЧХ).

Для получения последовательности c1 на передающей стороне исходную информацию объемом k m-ичных (m>1) символов кодируют m-ичным помехоустойчивым кодом, например, m-ичным помехоустойчивым кодом Рида-Соломона (PC). Код PC является внешним кодом или кодом первой ступени помехоустойчивого каскадного кода.

В результате такого кодирования исходной информации получают блок из слов кода PC (n, k), информационная длина которого к и равна слову PC, а блоковая - n символов.

Далее блок информации, состоящий из слов PC, кодируют двоичным кодом, например двоичным кодом БЧХ с проверочным многочленом h1(х). Код БЧХ является внутренним кодом или кодом второй ступени помехоустойчивого каскадного кода. Слово кода БЧХ имеет следующие параметры: n1 - блоковая длина кода, k1 - информационная длина кода. В результате кодирования блока из слов PC кодом БЧХ получают блок из n двоичных слов кода БЧХ (n1, k1), представляющих собой последовательность c1.

Далее слова кода БЧХ суммируют по модулю два с синхронизирующей последовательностью c2i. В качестве синхронизирующей последовательности выбирают двоичный код с блоковой длиной n1 и информационной длиной k2, например, код Рида-Маллера (РМ) первого порядка (последовательность максимального периода) с проверочным многочленом h2(x). Информационная длина k2 кода РМ соответствует двоичной записи номеров слов кода БЧХ. Между номерами слов кода БЧХ в каскадном коде и информационной частью синхронизирующей последовательности устанавливают взаимно однозначное соответствие. Первое слово кода БЧХ суммируют по модулю два с последовательностью, полученной в результате кодирования двоичной записи первого номера слова кода БЧХ кодом РМ, второе слово кода БЧХ суммируют по модулю два с последовательностью, полученной в результате кодирования двоичной записи второго номера слова кода БЧХ кодом РМ и так далее. Такую операцию суммирования выполняют со всеми словами кода БЧХ.

Если проверочные многочлены h1(x) и h2(x) суммируемых кодов БЧХ и РМ взаимно просты и являются делителями двучлена xn+1, в результате суммирования будет получено n слов циклического кода БЧХ с длиной n1, и информационной длиной k1+k2. Этот код будет корректировать ошибки, число которых

е ≤ r / log2(n1 + 1),

где r=n1-k1-k2 - число проверочных символов кода.

Третья последовательность с3, с которой суммируют слова кода БЧХ, будет постоянной последовательностью длиной n1 бит для всех слов. Такой последовательностью может быть любая последовательность, не являющаяся кодовым словом кода БЧХ, например, последовательность 10000…000. В реальных каналах возможны помехи, которые можно рассматривать как последовательность с4, наличие единиц в которой соответствует размещению ошибок в словах. Для безошибочных слов последовательность с4 содержит только нули.

Информация, сформированная из четырех последовательностей в виде последовательности c1 ⊕ c2i ⊕ c3 модулированной по типу стыка С1-ФЛ, и последовательности ошибок с4, поступает на информационный вход схемы кодовой цикловой синхронизации 1. Вариант структурной схемы кодовой цикловой синхронизации с описанием ее функционирования приведен в [Патент РФ №2812964, МПК H04L 7/08. Забабурин А.Н., Трушин С.А. Приор. 03.07..2023, опубл. 06.02.2023]. Схема кодовой цикловой синхронизации определяет границы блоков информации и считывает информацию для операций ее обработки и декодирования. Из схемы кодовой цикловой синхронизации признаки наименее достоверных битов поступают в схему формирования векторов ошибок 2. Векторы ошибок формируют в соответствии с известным алгоритмом Чейза, метод 2 [Кларк Дж., мл., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. М,: Радио и связь, 1987 г., с. 161., Р. Морелос-Сарагоса. Искусство помехоустойчивого кодирования. Методы, алгоритмы, применение. / Пер. с англ. - М.; Техносфера, 2006 г., с. 210-213]. В предлагаемом устройстве комбинации векторов ошибок могут формировать на не более [d/2]+1 позициях наименее достоверных битов. Если слово кода БЧХ содержит более четырех наименее достоверных бит, то для варианта схемы шестнадцати векторов ошибок векторы ошибок формируют только для первых четырех позиций, а значения остальных битов, в том числе на местах наименее достоверных битов, остаются исходными. При модуляции по типу стыка С1-ФЛ каждому разряду слова кода БЧХ соответствует два бита, то есть тридцати одному разрядному слову кода БЧХ соответствует шестьдесят два бита модулированного слова кода БЧХ. Фрагмент схемы для формирования вариантов векторов ошибок и ее временная диаграмма приведены в работе [Ромачева И.А., Третьяков А.В., Трушин С.А. Устройство цикловой синхронизации с мягкими решениями. // Труды IX Российской научно-технической конференции «Новые информационные технологии в системах связи и управления». Калуга. 2010. с. 328-338, рис. 2].

Для исправления семи ошибок в предлагаемом устройстве на [d/2]+1 позициях для четырех наименее достоверных битов формируют пятнадцать ненулевых векторов ошибок, так как нулевой вектор формировать нет смысла, и еще до трех ошибок исправляют жесткими решениями после исправления четырех ошибок ненулевыми векторами ошибок. В предлагаемом устройстве для нулевого вектора ошибок при мягких решениях или только при жестких решениях исправление ошибок проводят по одному алгоритму с жестким исправлением не более трех ошибок в слове. На вход схемы формирования векторов ошибок поступает сигнал в виде логической «1» на позициях наименее достоверных битов, а на остальных позициях битов сигнал поступает в виде логического «0». Для пятнадцати векторов ошибок после поступления четырех бит с мягкими решениями формируют сигнал запрета, по которому на оставшихся позициях битов модулированного слова кода БЧХ, в том числе и для наименее достоверных битов, для вектора ошибок поступает сигнал в виде логического «0». Таким образом, для четырех битов с мягкими решениями формируют пятнадцать разных ненулевых векторов ошибок, которые для формирования мягких решений в блоке двухвходовых сумматоров 3 параллельно побитно суммируют по модулю два с принимаемой биимпульсной входной информацией без суммы модулированных последовательностей c2i и c3n, соответствующей модулированной последовательности слов кода БЧХ. Суммы модулированных последовательностей c2i и c3n хранятся в ПЗУ 3, с выхода которого они побитно поступают на один из входов двухвходового сумматора по модулю два 4. На другой вход двухвходового сумматора по модулю два 4 с выхода схемы кодовой цикловой синхронизации 1 поступает принимаемая биимпульсная входная информация. На выходе двухвходового сумматора по модулю два 4 формируют принимаемую биимпульсную входную информацию без суммы модулированных последовательностей c2i и c3n. С выхода блока двухвходовых сумматоров по модулю два 3 мягкие решения для входной информации без суммы модулированных последовательностей c2i и c3n и принимаемая биимпульсная входная информация, соответствующая нулевому вектору ошибок, поступают на вход блока демодуляторов биимпульсного кода БЧХ 6. С выходов блока демодуляторов биимпульсного кода БЧХ 6 информация поступает в блок декодеров кода БЧХ 7. В предлагаемом устройстве, в отличие от прототипа, в блоке декодеров кода БЧХ не требуются сумматоры и регистры с полиномами X5+X2+1 и X5+X4+X2+X+1 для снятия в словах последовательностей c2i и c3n, так как эти последовательности удаляют в двух-входовом сумматоре 4.

Вариант схемы декодера кода БЧХ и описание его функционирования приведены в работе [Ромачева И.А., Трушин С.А.. Устройство декодирования с мягкими решениями для двухступенчатого каскадного кода. // Труды IX Российской научно-технической конференции «Новые информационные технологии в системах связи и управления». Калуга, 2010. - С. 353-369, рис. 4.].

Декодер кода БЧХ исправляет независимые ошибки до трех штук в словах, порожденных полиномом

X16+X12+X11+X10+X9+X8+X6+X4+Х3+X2+X+1.

Процедура декодирования слов кода БЧХ предполагает циклические сдвиги принятой информации и для каждого сдвига вычисление весов Wi(x) между синдромом Si(x) и покрывающими комбинациями Qi(x). Если при полном циклическом сдвиге на каком-либо шаге выполняется неравенство Wi(x) = Si(x) - Qi(x) ≤ (d-1)/2,

где d - минимальное кодовое расстояние слов кода БЧХ, то для соответствующего шага i делается исправление и код считается декодированным. Если неравенство не выполняется, это означает, что обнаружена некорректируемая ошибка. В качестве покрывающих комбинаций применяют

Q1=α31+α15+α11+α10+α9+α8+α7+α5+α3+α2+α+1,

Q2=α23+α11+α8+α6+α5+α3+1.

Исправление ошибок проводят инвертированием соответствующих бит промежуточного регистра в момент срабатывания дешифратора и при завершении цикла записью результата декодирования в выходной регистр. Декодированные слова кода БЧХ поступают на входы блока модуляторов кода БЧХ 9. Чтобы сравнивать декодированные слова кода БЧХ с модулированной информацией, поступившей из канала, декодированные слова кода БЧХ надо снова промодулировать. Модулированная информация, поступившая из канала, содержит модулированные последовательности c2i и c3n, которые из этой информации удаляют в двухвходовом сумматоре 4, чтобы в схеме определения слова кода БЧХ с наименьшим весом 8 корректно сравнивать модулированные декодированные слова кода БЧХ с модулированной информацией, поступившей из канала без модулированных последовательностей c2i и c3n.

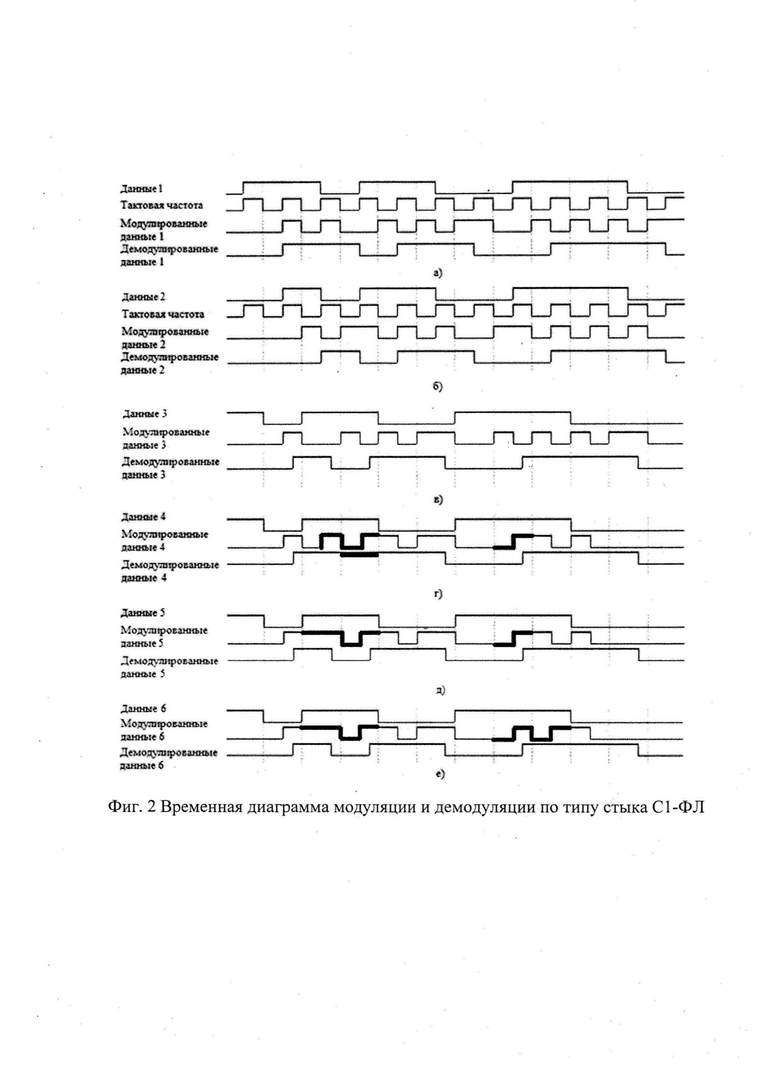

При модулировании по типу стыка С1-ФЛ порядок чередования полярности импульсов по сравнению с предыдущим тактовым интервалом не изменяется при передаче лог.1 и изменяется при передаче лог.0. Поэтому значения двух бит для первого разряда слова зависят от последнего бита разряда предыдущего слова. На фиг. 2 диаграммы а), б) приведен пример такой модуляции. Кроме того последний бит разряда предыдущего слова может исказиться в канале, поэтому сразу нельзя определить какому из двух возможных вариантов последнего бита предыдущего слова принадлежит последующее модулированное слово. Для более точного определения декодированного слова кода БЧХ с наименьшим весом сравнивают побитно их модулированное декодированное кодовое слово с двумя вариантами, прямым и инверсным, поступившей с выхода двухвходового сумматора 4 модулированной входной информации без модулированных последовательностей c2i и c3n и с учетом значений качества соответствующих битов. Сначала определяют веса вариантов, соответствующих модулированным декодированным словам кода БЧХ из блока модуляторов 7, относительно прямого и инверсного модулированного кодового слова, поступившего из ОЗУ 8. После сравнения модулированному декодированному слову кода БЧХ присваивают значение меньшего веса из двух вариантов. Затем полученный меньший вес каждого варианта декодированного модулированного слова кода БЧХ параллельно сравнивают с меньшими весами всех остальных вариантов декодированного модулированного слова кода БЧХ и определяют вариант декодированного слова кода БЧХ с наименьшим весом в 10.

В предлагаемом устройстве потребуется одновременно анализировать шестнадцать вариантов декодированных слов кода БЧХ для определения слова с наименьшим весом от принятого слова из канала. Если для данного номера нет декодированнго слова кода БЧХ, то данный номер с его словом не подлежат декодированию в контроллере декодера PC 11 и их игнорируют.

Для выбора декодированного слова кода БЧХ с наименьшим весом с выходов схемы определения слова кода БЧХ с наименьшим весом 10 поступает сигнал на входы блока декодеров кода БЧХ 7, которые подключают с выходов блока декодеров кода БЧХ соответствующее выбранное слово кода БЧХ, его номер и значение качества для их записи в ОЗУ контроллера декодера кода PC 11.

Контроллер декодера кода PC формирует сигналы начала и окончания процедуры декодирования кода PC.

В предлагаемом устройстве для декодирования кода PC применяют алгоритм с исправлением ошибок и стираний в пределах минимального кодового расстояния. В основе этого алгоритма лежит модифицированный алгоритм Гао [Квашенников В.В. Алгоритм декодирования кода Рида-Соломона с исправлением ошибок и стираний. // Труды XXII Российской межведомственной научно-технической конференции «Новые информационные технологии в системах связи и управления». Калуга, 2023. - С. 236-240.].

Для исправления ошибок используют четное число слов кода PC, поэтому одно нечетное слово в списке не используют.

Для снижения вероятности возможных трансформаций для декодирования надо использовать только наиболее достоверные слова кода PC. При нечетном числе слов PC надо стирать самое ненадежное слово, а для этого необходимо проводить процедуру сортировки. После завершения сортировки для выбора наиболее достоверных слов затем проводят окончательную процедуру декодирования. Стиранию подлежат также сова кода PC для недекодируемых слов кода БЧХ, которые при исправлении жесткими и мягкими решениями соответствуют синдрому с числом ошибок более трех.

При демодуляции ошибка в одном бите приводит к ошибке одного разряда в слове кода БЧХ. Для некоторых вариантов пачек ошибок битов при демодуляции происходит исправление ошибок в этих битах и получается правильный прием разрядов в слове кода БЧХ. При таких исправлениях повышается достоверность принимаемой информации. Пример функционирования при демодуляции безошибочной комбинации приведен на фиг. 2 диаграмма в). Примеры функционирования при демодуляции для комбинаций с ошибками приведены на фиг. 2 диаграммы г), д), е). Расположение ошибок в комбинациях на фиг. 2 диаграммы г), д), е) выделено жирным шрифтом.

По сравнению с прототипом новым является то, что в предлагаемом устройстве для повышения достоверности принимаемой информации применены усовершенствованные схема кодовой цикловой синхронизации, схема формирования векторов ошибок и схема определения слова кода БЧХ с наименьшим весом. Также в предлагаемое устройство добавлено ПЗУ, содержащее модулированные суммы фазирующей и нумерующей последовательностей, двухвходовой сумматор по модулю два, и блок модуляторов кода БЧХ. Для обеспечения высокой скорости обработки информации применяют параллельную и конвейерную обработку для вычислений.

В прототипе векторы ошибок формируют для наименее достоверных разрядов слов кода БЧХ, а после декодирования для выбора слова кода БЧХ с наименьшим весом сравнивают веса разрядов слов. В прототипе вероятность ошибки символа считается суммой двух метрик согласно работе. [Ромачева И.А, Трушин С.А. Устройство декодирования с мягкими решениями для двухступенчатого каскадного кода. // Труды IX Российской научно-технической конференции «Новые информационные технологии в системах связи и управления». Калуга, 2010. - С. 358, таблица 4.].

В предлагаемом устройстве векторы ошибок формируют для наименее достоверных бит модулированных слов кода БЧХ, а после декодирования для выбора слова кода БЧХ с наименьшим весом сравнивают веса для каждого бита модулированных слов кода БЧХ. В предлагаемом устройстве для бита точно определяют значение метрики для мягкого решения и этим обеспечивают более точное функционирование схемы определения слова кода БЧХ с наименьшим весом.

В прототипе формируют восемь векторов ошибок для наименее достоверных разрядов слов кода БЧХ, а в предлагаемом устройстве формируют шестнадцать векторов ошибок для наименее достоверных битов модулированных слов кода БЧХ, и поэтому при декодировании исправляют в слове кода БЧХ на одну ошибку больше.

Достигаемым техническим результатом предлагаемого устройства декодирования с жесткими и мягкими решениями и модуляции по типу стыка С1-ФЛ является повышение достоверности принимаемой информации в каналах с высоким уровнем помех.

Изобретение относится к системам передачи дискретной информации и может быть использовано в системах помехоустойчивой защиты информации. Техническим результатом, достигаемым при применении устройства, является повышение достоверности приема информации в каналах с высоким уровнем помех. Для этого предложено устройство декодирования с жесткими и мягкими решениями для двухступенчатого каскадного кода и модуляции типа стыка С1-ФЛ, которое содержит схему кодовой цикловой синхронизации, схему формирования векторов ошибок, блок двухвходовых сумматоров по модулю два для формирования мягких решений, ПЗУ, содержащее модулированные суммы фазирующей и нумерующей последовательностей, двухвходовой сумматор по модулю два, ОЗУ, блок демодуляторов биимпульсного кода БЧХ, блок декодеров кода БЧХ, блок модуляторов кода БЧХ, схему определения слов кода БЧХ с наименьшим весом, контроллер декодера кода PC. 2 ил.

Устройство декодирования с жесткими и мягкими решениями для двухступенчатого каскадного кода и модуляции по типу стыка С1-ФЛ, содержащее коррекционное устройство, вход Инф. которого является информационным входом устройства, а вход Част. которого является тактовым входом устройства, схему кодовой цикловой синхронизации с мягкими и жесткими решениями, блок сумматоров по модулю два, блок декодеров кода БЧХ, схему определения слов кода БЧХ с наименьшим весом, схему контроллера декодера кода PC, отличающееся тем, что в него введены схема кодовой цикловой синхронизации, где коррекционное устройство для каждого бита информации вычисляет его качество, по которому формируют признаки наименее достоверных битов и для наименее достоверных битов формируют векторы ошибок, ПЗУ, содержащее модулированные суммы фазирующей и нумерующей последовательностей, двухвходовой сумматор по модулю два, ОЗУ, блок модуляторов кода БЧХ, при этом в ОЗУ накопителя информации, содержащегося в схеме кодовой цикловой синхронизации, записывают биимпульсную последовательность, соответствующую входной последовательности из канала, качество ее битов и признаки наименее достоверных битов, далее при определении конца блока слов кода БЧХ, что соответствует правильному определению кодовой цикловой синхронизации, схема управления накопителя начинает запись последующей информации в другое ОЗУ накопителя информации, а из предыдущего ОЗУ начинает считывание информации для операций ее обработки и декодирования, при считывании информации из ОЗУ накопителя информации, содержащегося в схеме кодовой цикловой синхронизации, с ее выходов для формирования векторов ошибок для наименее достоверных битов поступают признаки наименее достоверных битов в схему формирования векторов ошибок, выход которой соединен с одним из входов блока двухвходовых сумматоров по модулю два, а другой вход блока сумматоров по модулю два соединен с выходом двухвходового сумматора по модулю два, по которому поступает биимпульсная последовательность, соответствующая модулированным словам кода БЧХ входной последовательности из канала, выход двухвходового сумматора по модулю два также соединен с входом ОЗУ, на другой вход ОЗУ поступает информация о качестве битов с выхода схемы кодовой цикловой синхронизации, один из входов двухвходового сумматора по модулю два соединен с выходом ПЗУ, вход ПЗУ для его управляющих сигналов соединен с выходом схемы кодовой цикловой синхронизации, другой вход двухвходового сумматора по модулю два соединен с выходом схемы кодовой цикловой синхронизации, по которому поступает биимпульсная последовательность, соответствующая входной последовательности из канала, выходы блока двухвходовых сумматоров по модулю два соединены с входами блока демодуляторов биимпульсного кода БЧХ, выходы демодуляторов биимпульсного кода БЧХ, на которых формируют разряды слов кода БЧХ, соединены с входами блока декодеров кода БЧХ, выходы блока декодеров кода БЧХ соединены с входами блока модуляторов кода БЧХ, выходы блока модуляторов кода БЧХ соединены с входами схемы определения слов кода БЧХ с наименьшим весом, другие входы схемы определения слов кода БЧХ с наименьшим весом соединены с выходом ОЗУ, по которому поступает биимпульная последовательность, соответствующая входной последовательности кода БЧХ, принятой из канала, и качество ее битов, выход схемы определения слов кода БЧХ с наименьшим весом для отбора декодированных слов кода БЧХ соединен с входом блока декодеров кода БЧХ, выход блока декодеров кода БЧХ для передачи слов кода БЧХ, их номеров и качества соединен с входом контроллера декодера кода PC, входы прерываний которого соединены с выходами для сигналов, определяющих начало и конец декодирования блоков кода PC, выход Вых. контроллера PC является информационным выходом устройства.

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА | 2012 |

|

RU2485683C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Колосоуборка | 1923 |

|

SU2009A1 |

Авторы

Даты

2025-02-17—Публикация

2024-08-05—Подача