Изобретение относится к технике электросвязи, в частности к устройствам определения оптимального маршрута передачи информации в системе связи на основе обобщенного показателя оценки эффективности информационного обмена (информационной эффективности), и может быть использовано при создании новых и совершенствовании существующих автоматизированных систем управления, сетей связи с коммутацией сообщений, сетей связи с коммутацией пакетов, в том числе с быстрой коммутацией пакетов.

Известно устройство для определения кратчайшего пути в графе [патент SU №842842 A1, G06G 7/122, 30.06.1981, Бюл. №24], которое содержит: матричную модель графа; блок управления; генератор тактовых импульсов; по числу строк и столбцов матричной модели графа: дифференцирующие цепочки и формирователи дуг, включающие триггеры и счетчики; по числу столбцов матричной модели графа: элементы ИЛИ, первую и вторую группу триггеров, группу элементов НЕ, первую, вторую, третью и четвертую группы элементов И, первую и вторую группы счетчиков, группу схем сравнения. Блок управления содержит первый и второй элемент И, блок пуска и останова, счетчик и дешифратор. Матричная модель графа представляет собой матрицу однородных ячеек формирователей весов дуг с дифференцирующими цепочками размером n×n, где n - максимальное число узлов моделируемого графа.

Недостатком данного устройства является то, что для определения кратчайших путей между узлами в графе используются вес дуг в виде значения времени прохождения дуги и критерий минимума времени прохождения от узла до узла, применение которых не позволяет найти кратчайший маршрут с учетом одновременного использования ресурсов системы связи по хранению и передаче информации.

Существует также устройство для определения минимальных путей в графах [патент SU №1242982 A1, G06F 15/20, 07.07.1986, Бюл. №25], содержащее матричную модель графа; по числу строк и столбцов матричной модели графа формирователи дуг; по числу столбцов матричной модели графа: первую и вторую группу элементов ИЛИ, группу триггеров, группу элементов НЕ, первую, вторую, третью и четвертую группы элементов И, регистрирующие счетчики, группу регистрирующих триггеров; блок вычисления кода максимального числа, блок памяти, дифференцирующую цепочку, генератор тактовых импульсов, элемент И-НЕ, два элемента И, элемент ИЛИ, элемент НЕ, первый и второй счетчики, первый и второй дешифраторы, вход запуска устройства. Формирователь дуги содержит первый и второй триггеры, первый и второй элементы И, дифференцирующую цепочку. Блок памяти по числу строк и столбцов матричной модели графа содержит: группу элементов И, группу триггеров, по числу столбцов матричной модели графа группу элементов ИЛИ, группу элементов НЕ.

Недостатками данного устройства являются: определяются не все маршруты от начального узла до конечного узла в графе, а лишь независимые пути на графе; невозможно определить оптимальный маршрут от начального узла до конечного узла в системе связи по заданному критерию.

Наиболее близким по технической сущности к заявляемому изобретению является устройство для определения путей в графе [патент SU №1292000 A1, G06F 15/20, 23.02.1987, Бюл. №7], содержащее: первый и второй блоки памяти; блок регистрации; первый, второй, третий, четвертый и пятый регистры; первый, второй, третий и четвертый блоки сравнения на равенство; первый, второй, третий, четвертый и пятый мультиплексоры; счетчики; накапливающий сумматор; блок сравнения на больше-меньше; элемент ИЛИ; генератор импульсов; блок регистров. В результате работы устройства в блоке регистрации формируются все пути в графе между его начальной и конечной вершинами и определяются веса этих путей.

Недостатками прототипа являются: отсутствуют при решении задачи маршрутизации одновременный учет возможностей системы связи по передаче и хранению информации; не определены процедуры нахождения оптимального маршрута в системе связи, снижающие среднюю временную задержку и потери пакетов.

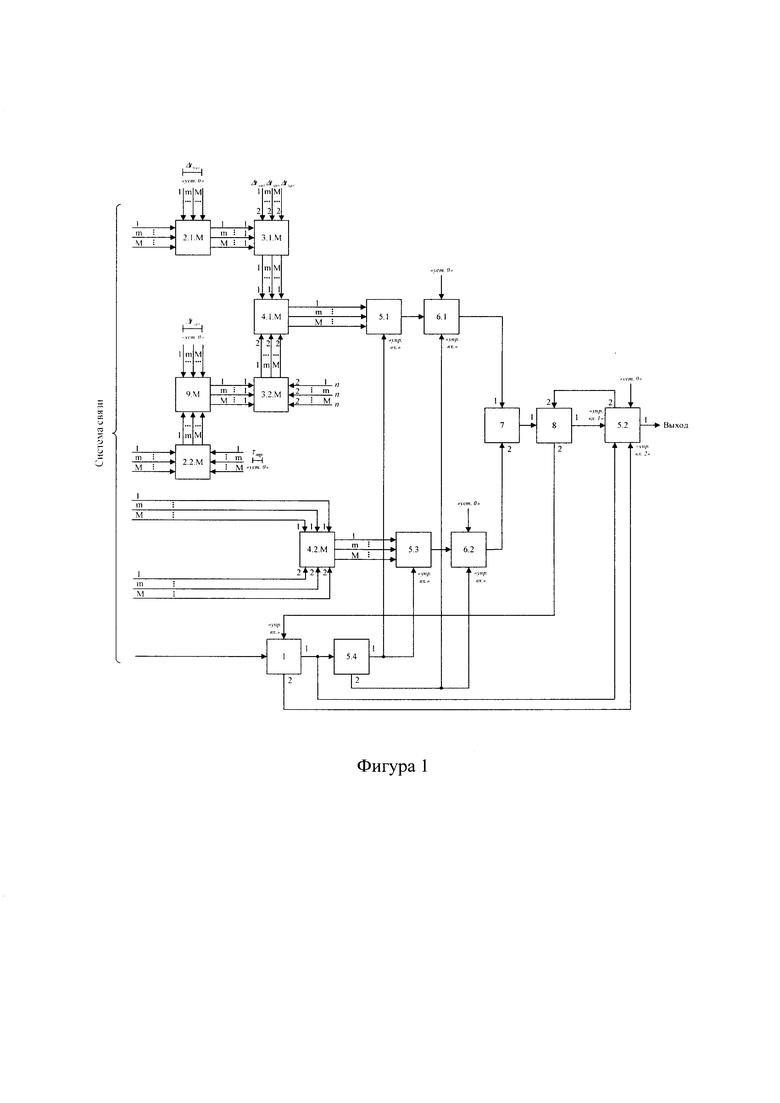

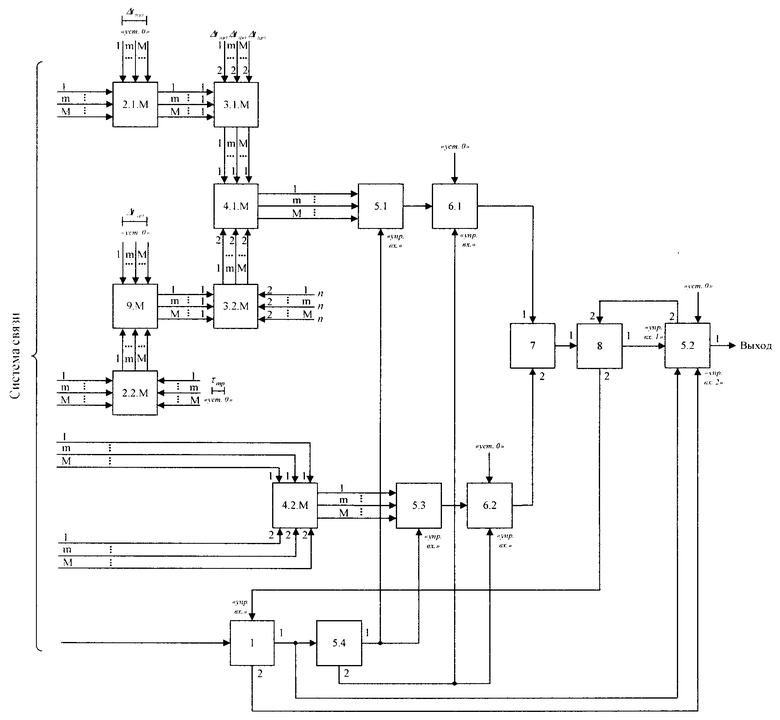

Техническим результатом предлагаемого устройства является уменьшение средней временной задержки и потерь пакетов за счет оптимального распределения информационных потоков в системе связи при передаче информации от узла-отправителя до узла-получателя путем определения оптимального маршрута на основе обобщенного показателя - коэффициента полезного действия (КПД) передачи информации.

Технический результат достигается тем, что в устройстве определения оптимального маршрута передачи информации в системе связи, содержащем блок измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя, согласно изобретению, дополнительно введены последовательно соединенные по количеству М интервалов системы связи первая группа счетчиков, первая группа делителей, на вторые входы которых подают значения заданного интервала времени измерений Δtзад, первая группа перемножителей, первое запоминающее устройство, первый сумматор, делитель, схема сравнения, второе запоминающее устройство, первый выход которого является выходом устройства; также дополнительно введены последовательно соединенные по количеству М интервалов системы связи вторая группа счетчиков, группа сумматоров, вторая группа делителей, на вторые входы которых подают значения количества измерений n, а выходы второй группы делителей соединены со вторыми входами первой группы перемножителей; кроме того, дополнительно введены четвертое запоминающее устройство и последовательно соединенные по числу М интервалов системы связи вторая группа перемножителей, третье запоминающее устройство, второй сумматор, выход которого соединен со вторым входом делителя; первый выход четвертого запоминающего устройства соединен с управляющими входами первого и третьего запоминающих устройств, а второй выход четвертого запоминающего устройства соединен с управляющими входами первого и второго сумматоров; первый выход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя соединен с входами второго и четвертого запоминающих устройств, а второй выход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя соединен со вторым управляющим входом второго запоминающего устройства, второй выход которого соединен со вторым входом схемы сравнения, второй выход которой соединен с управляющим входом блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя (фигура).

Отличительный признак, касающийся дополнительного введения: первой и второй групп счетчиков; первой и второй групп делителей; первой и второй групп перемножителей; группы сумматоров; первого, второго, третьего и четвертого запоминающих устройств; первого и второго сумматоров; делителя; схемы сравнения, поясняется следующим.

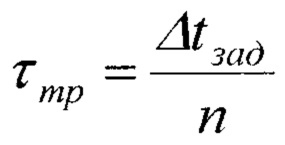

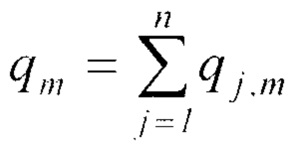

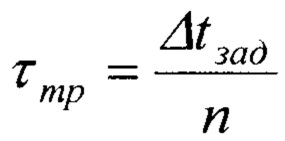

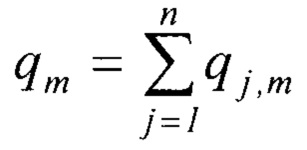

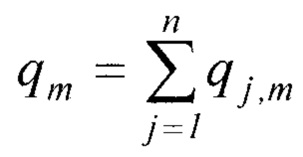

Через заданный интервал времени измерений Δtзад подают данные из системы связи для каждого m-го интервала связи (из совокупности всех интервалов связи m=1…М), состоящего из m-го буферного запоминающего устройства (БЗУ) и m-го канала связи (КС), на входы первой и второй групп счетчиков. В первой группе счетчиков для каждого m-го интервала связи выполняют операции подсчета количества информационных пакетов, переданных через каждый m-ый КС rm.Во второй группе счетчиков для каждого m-го интервала связи через требуемый период времени  , который равен значению заданного интервала времени измерений Δtзад деленному на значение количества измерений n, выполняют операции подсчета количества информационных пакетов qj,m, хранящихся в каждом m-ом БЗУ в текущий j-ый момент времени, которые выдают на соответствующие входы группы сумматоров, затем вторую группу счетчиков обнуляют («уст. 0» через τmp). В группе сумматоров для каждого m-го интервала связи осуществляют операции сложения поступающих текущих значений qj,m и вычисляют значения количества информационных пакетов

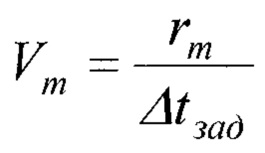

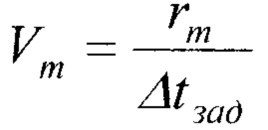

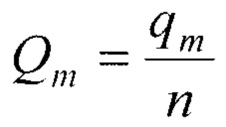

, который равен значению заданного интервала времени измерений Δtзад деленному на значение количества измерений n, выполняют операции подсчета количества информационных пакетов qj,m, хранящихся в каждом m-ом БЗУ в текущий j-ый момент времени, которые выдают на соответствующие входы группы сумматоров, затем вторую группу счетчиков обнуляют («уст. 0» через τmp). В группе сумматоров для каждого m-го интервала связи осуществляют операции сложения поступающих текущих значений qj,m и вычисляют значения количества информационных пакетов  , хранящихся в каждом m-ом БЗУ за заданный интервал времени измерений Δtзад. Далее через Δtзад с выходов первой группы счетчиков выдают значения rm на соответствующие первые входы первой группы делителей, на вторые входы которых подают значения заданного интервала времени измерений Δtзад. С выходов группы сумматоров выдают значения qm на соответствующие первые входы второй группы делителей, на вторые входы которых подают значения количества измерений n. После чего, группу сумматоров и первую группу счетчиков обнуляют («уст. 0» через Δtзад). В первой группе делителей осуществляют операции деления значений rm на значения Δtзад, вычисляя средние значения скорости передачи информации

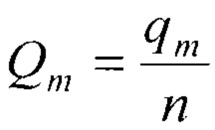

, хранящихся в каждом m-ом БЗУ за заданный интервал времени измерений Δtзад. Далее через Δtзад с выходов первой группы счетчиков выдают значения rm на соответствующие первые входы первой группы делителей, на вторые входы которых подают значения заданного интервала времени измерений Δtзад. С выходов группы сумматоров выдают значения qm на соответствующие первые входы второй группы делителей, на вторые входы которых подают значения количества измерений n. После чего, группу сумматоров и первую группу счетчиков обнуляют («уст. 0» через Δtзад). В первой группе делителей осуществляют операции деления значений rm на значения Δtзад, вычисляя средние значения скорости передачи информации  каждого m-го КС, которые выдают на соответствующие первые входы первой группы перемножителей. Во второй группе делителей осуществляют операции деления значений qm на значения n, вычисляя средние значения количества информационных пакетов

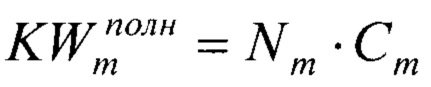

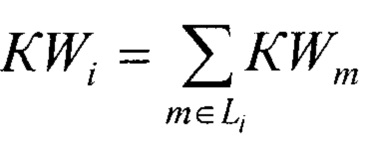

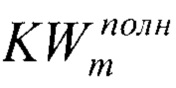

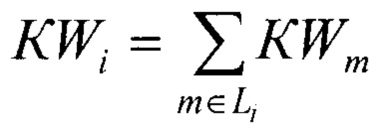

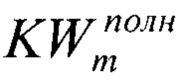

каждого m-го КС, которые выдают на соответствующие первые входы первой группы перемножителей. Во второй группе делителей осуществляют операции деления значений qm на значения n, вычисляя средние значения количества информационных пакетов  , хранящихся в каждом m-ом БЗУ, которые выдают на соответствующие вторые входы первой группы перемножителей. В первой группе перемножителей выполняют операции умножения значений Vm и Qm, определяя значения кибернетической мощности KWm=Vm⋅Qm каждого m-го интервала связи, которые выдают на входы первого запоминающего устройства, где их запоминают. Также через заданный интервал времени измерений Δtзад из системы связи для каждого т-го интервала связи подают значения емкости Nm каждого m-го БЗУ и пропускной способности Cm каждого m-го КС, соответственно, на первые и вторые входы второй группы перемножителей. Во второй группе перемножителей выполняют операции умножения значений Nm и Cm, определяя значения полной кибернетической мощности

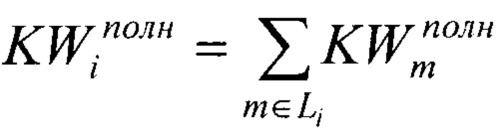

, хранящихся в каждом m-ом БЗУ, которые выдают на соответствующие вторые входы первой группы перемножителей. В первой группе перемножителей выполняют операции умножения значений Vm и Qm, определяя значения кибернетической мощности KWm=Vm⋅Qm каждого m-го интервала связи, которые выдают на входы первого запоминающего устройства, где их запоминают. Также через заданный интервал времени измерений Δtзад из системы связи для каждого т-го интервала связи подают значения емкости Nm каждого m-го БЗУ и пропускной способности Cm каждого m-го КС, соответственно, на первые и вторые входы второй группы перемножителей. Во второй группе перемножителей выполняют операции умножения значений Nm и Cm, определяя значения полной кибернетической мощности  каждого m-го интервала связи, которые выдают на входы третьего запоминающего устройства, где их запоминают.

каждого m-го интервала связи, которые выдают на входы третьего запоминающего устройства, где их запоминают.

При этом с учетом проведенных выше операций в первом и третьем запоминающих устройствах хранятся значения кибернетической мощности KWm и полной кибернетической мощности  , соответственно, для каждого m-го интервала связи системы связи, которые перезаписываются (обновляются) через заданный интервал времени измерений Δtзад.

, соответственно, для каждого m-го интервала связи системы связи, которые перезаписываются (обновляются) через заданный интервал времени измерений Δtзад.

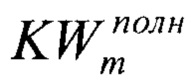

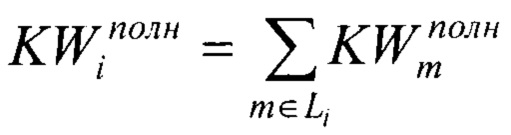

После чего, через Δtзад подают данные из системы связи на вход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя, выполненного по схеме, представленной в патенте [SU №1292000 A1, G06F 15/20, 23.02.1987, Бюл. №7], в котором запоминают все маршруты от узла-отправителя до узла-получателя (i=1…I) и проверяют наличие информации о возможных маршрутах. В случае наличия информации о возможных маршрутах с выхода блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя одновременно выдают информацию о текущем i-ом маршруте Li, состоящем из m-ых интервалов связи, на вход четвертого запоминающего устройства, в котором его запоминают, и на вход второго запоминающего устройства, в котором запоминают информацию о текущем i-ом маршруте Li при наличии сигнала на его первом управляющем входе. Далее с первого выхода четвертого запоминающего устройства последовательно выдают информацию о каждом m-ом интервале связи, входящем в текущий i-ый маршрут, на управляющие входы первого и третьего запоминающих устройств. По сигналам на управляющих входах первого и третьего запоминающих устройств с их выходов последовательно выдают значения кибернетической мощности KWm и полной кибернетической мощности  соответствующих m-ым интервалам связи, входящих в текущий i-ый маршрут, на входы первого и второго сумматоров, соответственно. Затем информацию об m-ых интервалах связи, входящих в текущий i-ый маршрут, в четвертом запоминающем устройстве удаляют. В первом и втором сумматорах выполняют операции сложения, соответственно, последовательно поступающих значений кибернетической мощности KWm и полной кибернетической мощности

соответствующих m-ым интервалам связи, входящих в текущий i-ый маршрут, на входы первого и второго сумматоров, соответственно. Затем информацию об m-ых интервалах связи, входящих в текущий i-ый маршрут, в четвертом запоминающем устройстве удаляют. В первом и втором сумматорах выполняют операции сложения, соответственно, последовательно поступающих значений кибернетической мощности KWm и полной кибернетической мощности  , определяя значения кибернетической мощности

, определяя значения кибернетической мощности  и полной кибернетической мощности

и полной кибернетической мощности  текущего i-го маршрута от узла-отправителя до узла-получателя, соответственно. После чего, как информация об m-ых интервалах связи, входящих в текущий i-ый маршрут, из четвертого запоминающего устройства выдана на управляющие входы первого и третьего запоминающих устройств, то в четвертом запоминающем устройстве формируют и направляют сигнал с его второго выхода на управляющие входы первого и второго сумматоров. По сигналам на управляющих входах первого и второго сумматоров с их выходов выдают значения KWi и

текущего i-го маршрута от узла-отправителя до узла-получателя, соответственно. После чего, как информация об m-ых интервалах связи, входящих в текущий i-ый маршрут, из четвертого запоминающего устройства выдана на управляющие входы первого и третьего запоминающих устройств, то в четвертом запоминающем устройстве формируют и направляют сигнал с его второго выхода на управляющие входы первого и второго сумматоров. По сигналам на управляющих входах первого и второго сумматоров с их выходов выдают значения KWi и  , соответственно, на первый и второй входы делителя. Затем первый и второй сумматоры обнуляют («уст. 0»).

, соответственно, на первый и второй входы делителя. Затем первый и второй сумматоры обнуляют («уст. 0»).

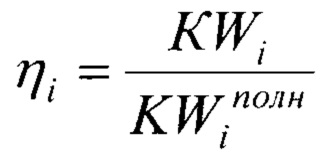

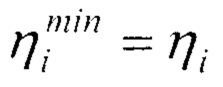

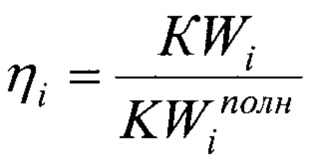

В делителе осуществляют операцию деления значения KWi на значение  , определяя значение КПД передачи информации

, определяя значение КПД передачи информации  текущего i-го маршрута от узла-отправителя до узла-получателя, которое с выхода делителя выдают на первый вход схемы сравнения, на второй вход которой подают текущее минимальное значение КПД передачи информации

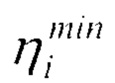

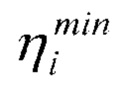

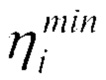

текущего i-го маршрута от узла-отправителя до узла-получателя, которое с выхода делителя выдают на первый вход схемы сравнения, на второй вход которой подают текущее минимальное значение КПД передачи информации  со второго выхода второго запоминающего устройства. Так как первоначально во втором запоминающем устройстве значение

со второго выхода второго запоминающего устройства. Так как первоначально во втором запоминающем устройстве значение  и информация о текущем оптимальном маршруте

и информация о текущем оптимальном маршруте  отсутствуют, то значение ηi с первого выхода схемы сравнения сразу подают на первый управляющий вход второго запоминающего устройства, где его запоминают

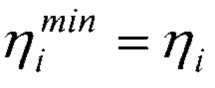

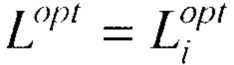

отсутствуют, то значение ηi с первого выхода схемы сравнения сразу подают на первый управляющий вход второго запоминающего устройства, где его запоминают  , а также запоминают информацию о текущем оптимальном маршруте

, а также запоминают информацию о текущем оптимальном маршруте  . При последующих вычислениях в делителе значения ηi в схеме сравнения сравнивают его с значением

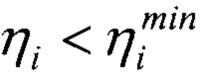

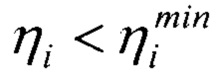

. При последующих вычислениях в делителе значения ηi в схеме сравнения сравнивают его с значением  , и если ηi<

, и если ηi< , то значение ηi с ее первого выхода подают на первый управляющий вход второго запоминающего устройства. По сигналу на первом управляющем входе второго запоминающего устройства запоминают (обновляют) текущее минимальное значение КПД передачи информации

, то значение ηi с ее первого выхода подают на первый управляющий вход второго запоминающего устройства. По сигналу на первом управляющем входе второго запоминающего устройства запоминают (обновляют) текущее минимальное значение КПД передачи информации  и текущий оптимальный маршрут

и текущий оптимальный маршрут  . Затем в схеме сравнения формируют и направляют сигнал с ее второго выхода на управляющий вход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя, в том числе, в случае не выполнения условия

. Затем в схеме сравнения формируют и направляют сигнал с ее второго выхода на управляющий вход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя, в том числе, в случае не выполнения условия  в схеме сравнения. По сигналу на управляющем входе блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя удаляют информацию о текущем i-ом маршруте Li и проверяют наличие информации о других возможных маршрутах от узла-отправителя до узла-получателя. В случае, если в блоке измерителе-вычислителе всех возможных маршрутов от узла-отправителя до узла-получателя имеется информация о другом возможном маршруте, то с его первого выхода выдают информацию о следующем текущем i-ом маршруте Li на входы четвертого и второго запоминающих устройств. В случае отсутствия информации о других возможных маршрутах в блоке измерителе-вычислителе всех возможных маршрутов от узла-отправителя до узла-получателя формируют и направляют сигнал с его второго выхода на второй управляющий вход второго запоминающего устройства. По сигналу на втором управляющем входе второго запоминающего устройства на его первый выход, являющийся выходом устройства, выдают информацию об оптимальном маршруте

в схеме сравнения. По сигналу на управляющем входе блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя удаляют информацию о текущем i-ом маршруте Li и проверяют наличие информации о других возможных маршрутах от узла-отправителя до узла-получателя. В случае, если в блоке измерителе-вычислителе всех возможных маршрутов от узла-отправителя до узла-получателя имеется информация о другом возможном маршруте, то с его первого выхода выдают информацию о следующем текущем i-ом маршруте Li на входы четвертого и второго запоминающих устройств. В случае отсутствия информации о других возможных маршрутах в блоке измерителе-вычислителе всех возможных маршрутов от узла-отправителя до узла-получателя формируют и направляют сигнал с его второго выхода на второй управляющий вход второго запоминающего устройства. По сигналу на втором управляющем входе второго запоминающего устройства на его первый выход, являющийся выходом устройства, выдают информацию об оптимальном маршруте  между узлом-отправителем и узлом-получателем. Затем через Δtзад второе запоминающее устройство обнуляют («уст. 0»). После чего продолжают представленные выше измерения и вычисления.

между узлом-отправителем и узлом-получателем. Затем через Δtзад второе запоминающее устройство обнуляют («уст. 0»). После чего продолжают представленные выше измерения и вычисления.

Проведенные исследования показывают, что определение оптимального маршрута от узла-отправителя до узла-получателя по критерию минимального значения КПД передачи информации на всех возможных маршрутах обеспечивает уменьшение средней временной задержки и потерь пакетов в системе связи за счет оптимального распределения информационных потоков при передаче информации. КПД передачи информации при решении задачи маршрутизации учитывает использование ресурсов системы связи при передаче и хранении информации по отношению к ее потенциальным возможностям на основе одновременной оценки скоростных характеристик (пропускных способностей) каналов связи и параметров загрузки (емкости) буферов на маршруте передачи информации [Межуев А.М., Коренной А.В. Оценка эффективности сетевых информационных систем обобщенным показателем // Радиотехника. 2021. №3. С. 65-77].

В дальнейшем изобретение поясняется описанием примеров его выполнения и прилагаемым чертежом, на котором фигура изображает схематический чертеж устройства определения оптимального маршрута передачи информации в системе связи, согласно изобретению.

Устройство определения оптимального маршрута передачи информации в системе связи (фигура) содержит:

блок измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1, выполненный по схеме, представленной в патенте [SU №1292000 A1, G06F 15/20, 23.02.1987, Бюл. №7], и предназначенный для: получения данных из системы связи через заданный интервал времени измерений Δtзад и запоминания всех маршрутов от узла-отправителя до узла-получателя; проверки информации о возможных маршрутах и в случае ее наличия одновременной выдачи информации о текущем i-ом маршруте Li с первого выхода на входы запоминающих устройств 5.2 и 5.4, а в случае отсутствия информации о возможных маршрутах - формирования и выдачи сигнала со второго выхода на второй управляющий вход запоминающего устройства 5.2; удаления информации о текущем i-ом маршруте Li и последующей проверки наличия информации о других возможных маршрутах по сигналу на управляющем входе;

группа счетчиков 2.1.М, предназначенная для получения данных из системы связи в течение заданного интервала времени измерений Δtзад и выполнения подсчета количества информационных пакетов rm, переданных через каждый m-ый КС, а также для выдачи через Δtзад значений rm на соответствующие первые входы группы делителей 3.1.М;

группа счетчиков 2.2.М, предназначенная для получения данных из системы связи в течение требуемого периода времени  (где n - количество измерений за время Δtзад ) и выполнения подсчета информационных пакетов qj,m, хранящихся в каждом m-ом БЗУ в текущий j-ый момент времени, а также для последовательной выдачи через τmp значений qj,m на соответствующие входы группы сумматоров 9.М;

(где n - количество измерений за время Δtзад ) и выполнения подсчета информационных пакетов qj,m, хранящихся в каждом m-ом БЗУ в текущий j-ый момент времени, а также для последовательной выдачи через τmp значений qj,m на соответствующие входы группы сумматоров 9.М;

группа делителей 3.1.М, предназначенная для: выполнения операций деления значений количества информационных пакетов rm, переданных через каждый m-ый КС за время Δtзад, на значения заданного интервала времени измерений Δtзад; вычисления средних значений скорости передачи информации  каждого m-го КС; выдачи значений Vm на соответствующие первые входы группы перемножителей 4.1.М;

каждого m-го КС; выдачи значений Vm на соответствующие первые входы группы перемножителей 4.1.М;

группа делителей 3.2.М, предназначенная для: выполнения операций деления значений количества информационных пакетов qm, хранящихся в каждом m-ом БЗУ за время Δtзад на значения количества измерений n; вычисления средних значений количества информационных пакетов  , хранящихся в каждом m-ом БЗУ; выдачи значений Qm на соответствующие вторые входы группы перемножителей 4.1.М;

, хранящихся в каждом m-ом БЗУ; выдачи значений Qm на соответствующие вторые входы группы перемножителей 4.1.М;

группа перемножителей 4.1.М, предназначенная для: выполнения операций умножения средних значений скорости передачи информации Vm каждого m-го КС и количества информационных пакетов Qm, хранящихся в каждом m-ом БЗУ; определения значений кибернетической мощности KWm каждого m-го интервала связи; выдачи значений KWm на входы запоминающего устройства 5.1;

группа перемножителей 4.2.М, предназначенная для: получения из системы связи значений емкости каждого m-го БЗУ Nm и пропускной способности каждого m-го КС Cm; выполнения операций умножения значений Nm и Cm; определения значений полной кибернетической мощности  каждого m-го интервала связи; выдачи значений

каждого m-го интервала связи; выдачи значений  на входы запоминающего устройства 5.3;

на входы запоминающего устройства 5.3;

запоминающее устройство 5.1, предназначенное для запоминания (обновления) через Δtзад значений кибернетической мощности KWm каждого m-го интервала связи, а также для последовательной выдачи значения кибернетической мощности KWm m-го интервала связи на вход сумматора 6.1 по сигналу на управляющем входе;

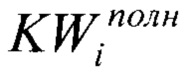

запоминающее устройство 5.2, предназначенное для: запоминания (обновления) текущего минимального значения КПД передачи информации  и информации о текущем оптимальном маршруте

и информации о текущем оптимальном маршруте  по сигналу на первом управляющем входе; выдачи значения

по сигналу на первом управляющем входе; выдачи значения  со второго выхода на второй вход схемы сравнения 8; выдачи информации об оптимальном маршруте Lopt между узлом-отправителем и узлом-получателем на первый выход, являющийся выходом устройства, по сигналу на втором управляющем входе;

со второго выхода на второй вход схемы сравнения 8; выдачи информации об оптимальном маршруте Lopt между узлом-отправителем и узлом-получателем на первый выход, являющийся выходом устройства, по сигналу на втором управляющем входе;

запоминающее устройство 5.3, предназначенное для запоминания (обновления) через Δtзад значений полной кибернетической мощности  каждого m-го интервала связи, а также для последовательной выдачи значения полной кибернетической мощности

каждого m-го интервала связи, а также для последовательной выдачи значения полной кибернетической мощности  m-го интервала связи на вход сумматора 6.3 по сигналу на управляющем входе;

m-го интервала связи на вход сумматора 6.3 по сигналу на управляющем входе;

запоминающее устройство 5.4, предназначенное для: запоминания информации о текущем i-ом маршруте Li; проверки информации об интервалах связи, входящих в Li, и в случае их наличия последовательной выдачи с первого выхода информации о каждом m-ом интервале связи на управляющие входы запоминающих устройств 5.1 и 5.3 с последующим удалением информации о текущем m-ом интервале связи, а в случае отсутствия информации об интервалах связи - формирования и выдачи сигнала со второго выхода на управляющие входы сумматоров 6.1 и 6.3;

сумматор 6.1, предназначенный для выполнения операций сложения значений кибернетической мощности KWm m-ых интервалов связи, последовательно поступающих на его вход, и для выдачи значения кибернетической мощности  текущего i-го маршрута на первый вход делителя 7 по сигналу на управляющем входе;

текущего i-го маршрута на первый вход делителя 7 по сигналу на управляющем входе;

сумматор 6.2, предназначенный для выполнения операций сложения значений полной кибернетической мощности  m-ых интервалов связи, последовательно поступающих на его вход, и для выдачи значения полной кибернетической мощности

m-ых интервалов связи, последовательно поступающих на его вход, и для выдачи значения полной кибернетической мощности  текущего i-го маршрута на второй вход делителя 7 по сигналу на управляющем входе;

текущего i-го маршрута на второй вход делителя 7 по сигналу на управляющем входе;

делитель 7, предназначенный для: выполнения операции деления значения кибернетической мощности KWi на значение полной кибернетической мощности  текущего i-го маршрута; определения значения КПД передачи информации

текущего i-го маршрута; определения значения КПД передачи информации  текущего i-го маршрута; выдачи значений ηi на первый вход схемы сравнения 8;

текущего i-го маршрута; выдачи значений ηi на первый вход схемы сравнения 8;

схема сравнения 8, предназначенная для: выдачи значения КПД передачи информации ηi с первого выхода на первый управляющий вход запоминающего устройства 5.2 при первом вычислении значения ηi в делителе 7, а также при выполнении неравенства  ; выполнения операции сравнения значения КПД передачи информации ηi текущего i-го маршрута и текущего минимального значения КПД передачи информации

; выполнения операции сравнения значения КПД передачи информации ηi текущего i-го маршрута и текущего минимального значения КПД передачи информации  при последующих вычислениях значения ηi в делителе 7; формирования и выдачи сигнала со второго выхода на управляющий вход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1;

при последующих вычислениях значения ηi в делителе 7; формирования и выдачи сигнала со второго выхода на управляющий вход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1;

группа сумматоров 9.М, предназначенная для: выполнения операции сложения последовательно поступающих на соответствующие входы значений количества информационных пакетов qj,m, хранящихся в каждом m-ом БЗУ в текущий j-ый момент времени; определения значений количества информационных пакетов  , хранящихся в каждом m-ом БЗУ за время Δtзад; выдачи через Δtзад значений qm на соответствующие первые входы группы делителей 3.2.М;

, хранящихся в каждом m-ом БЗУ за время Δtзад; выдачи через Δtзад значений qm на соответствующие первые входы группы делителей 3.2.М;

Все операции, выполняемые в блоках устройства, могут быть реализованы, например, на основе быстродействующих микроконтроллеров [Белов А.В. Самоучитель разработчика устройств на микроконтроллерах AVR. С.-Пб.: Наука и Техника, 2008. 544 с.; Микушин А.В., Сажнев A.M., Сединин В.И. Цифровые устройства и микропроцессоры. С.-Пб.: БХВ - Петербург, 2010. 832 с.].

Работа устройства (фигура) осуществляется следующим образом.

На основе данных, поступающих в течение заданного интервала времени измерений Δtзад из системы связи на входы групп счетчиков 2.1.М и 2.2.М, для каждого m-го интервала связи: в группе счетчиков 2.1.М выполняют операции подсчета количества информационных пакетов, переданных через каждый m-ый КС rm; в группе счетчиков 2.2.М за время Δtзад через требуемый период времени τmp выполняют операции подсчета количества информационных пакетов qj,m, хранящихся в каждом m-ом БЗУ в текущий j-ый момент времени. С выходов группы счетчиков 2.2.М значения qj,m через τmp выдают на соответствующие входы группы сумматоров 9.М, после чего, группу счетчиков 2.2.М обнуляют («уст. 0» через τmp). В группе сумматоров 9.М для каждого m-го интервала связи осуществляют операции сложения значений qj,m и вычисляют значения количества информационных пакетов  (где n - количество измерений), хранящихся в каждом m-ом БЗУ за Δtзад. Далее через Δtзад с выходов группы счетчиков 2.1.М выдают значения rm на соответствующие входы 1 группы делителей 3.1.М, на входы 2 которых подают значения Δtзад. С выходов группы сумматоров 9.М выдают значения qm на соответствующие входы 1 группы делителей 3.2.М, на входы 2 которых подают значения количества измерений n. После чего, группу сумматоров 9.М и группу счетчиков 2.1.М обнуляют («уст. 0» через Δtзад). В группе делителей 3.1.М осуществляют операции деления значений rm на значения Δtзад, вычисляя средние значения скорости передачи информации Vm каждого m-го КС, которые выдают на соответствующие входы 1 группы перемножителей 4.1.М. В группе делителей 3.2.М осуществляют операции деления значений qm на значения n, вычисляя средние значения количества информационных пакетов Qm, хранящихся в каждом m-ом БЗУ, которые выдают на соответствующие входы 2 группы перемножителей 4.1.М. В группе перемножителей 4.1.М выполняют операции умножения значений Vm и Qm, определяя значения кибернетической мощности KWm каждого m-го интервала связи, которые выдают на входы запоминающего устройства 5.1, где их запоминают. Также через Δtзад из системы связи для каждого m-го интервала связи подают значения емкости Nm каждого m-го БЗУ и пропускной способности Cm каждого m-го КС, соответственно, на входы 1 и 2 группы перемножителей 4.2.М. В группе перемножителей 4.2.М выполняют операции умножения значений Nm и Cm, определяя значения полной кибернетической мощности

(где n - количество измерений), хранящихся в каждом m-ом БЗУ за Δtзад. Далее через Δtзад с выходов группы счетчиков 2.1.М выдают значения rm на соответствующие входы 1 группы делителей 3.1.М, на входы 2 которых подают значения Δtзад. С выходов группы сумматоров 9.М выдают значения qm на соответствующие входы 1 группы делителей 3.2.М, на входы 2 которых подают значения количества измерений n. После чего, группу сумматоров 9.М и группу счетчиков 2.1.М обнуляют («уст. 0» через Δtзад). В группе делителей 3.1.М осуществляют операции деления значений rm на значения Δtзад, вычисляя средние значения скорости передачи информации Vm каждого m-го КС, которые выдают на соответствующие входы 1 группы перемножителей 4.1.М. В группе делителей 3.2.М осуществляют операции деления значений qm на значения n, вычисляя средние значения количества информационных пакетов Qm, хранящихся в каждом m-ом БЗУ, которые выдают на соответствующие входы 2 группы перемножителей 4.1.М. В группе перемножителей 4.1.М выполняют операции умножения значений Vm и Qm, определяя значения кибернетической мощности KWm каждого m-го интервала связи, которые выдают на входы запоминающего устройства 5.1, где их запоминают. Также через Δtзад из системы связи для каждого m-го интервала связи подают значения емкости Nm каждого m-го БЗУ и пропускной способности Cm каждого m-го КС, соответственно, на входы 1 и 2 группы перемножителей 4.2.М. В группе перемножителей 4.2.М выполняют операции умножения значений Nm и Cm, определяя значения полной кибернетической мощности  каждого m-го интервала связи, которые выдают на входы запоминающего устройства 5.3, где их запоминают.

каждого m-го интервала связи, которые выдают на входы запоминающего устройства 5.3, где их запоминают.

После чего, на основе данных, поступающих через Δtзад из системы связи на вход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1, выполненного по схеме, представленной в патенте [SU №1292000 A1, G06F 15/20, 23.02.1987, Бюл. №7], запоминают все маршруты от узла-отправителя до узла-получателя (i=1…I) и проверяют наличие информации о возможных маршрутах. В случае наличия информации о возможных маршрутах с выхода в блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1 одновременно выдают информацию Li о текущем i-ом маршруте на вход запоминающего устройства 5.4, в котором его запоминают, и на вход запоминающего устройства 5.2, в котором запоминают Li при наличии сигнала на «упр. вх. 1». Далее с выхода 1 запоминающего устройства 5.4 последовательно выдают информацию о каждом m-ом интервале, входящем в текущий i-ый маршрут, на «упр. вх.» запоминающих устройств 5.1 и 5.3. По сигналам на «упр. вх.» запоминающих устройств 5.1 и 5.3 с их выходов последовательно выдают значения KWm и  соответствующих m-ым интервалам связи, входящих в текущий i-ый маршрут, на входы сумматоров 6.1 и 6.2, соответственно. Затем информацию об m-ых интервалах связи, входящих в текущий i-ый маршрут, в запоминающем устройстве 5.4 удаляют. В сумматорах 6.1 и 6.2 выполняют операции сложения, соответственно, последовательно поступающих значений KWm и

соответствующих m-ым интервалам связи, входящих в текущий i-ый маршрут, на входы сумматоров 6.1 и 6.2, соответственно. Затем информацию об m-ых интервалах связи, входящих в текущий i-ый маршрут, в запоминающем устройстве 5.4 удаляют. В сумматорах 6.1 и 6.2 выполняют операции сложения, соответственно, последовательно поступающих значений KWm и  , определяя значения кибернетической мощности KWi и полной кибернетической мощности

, определяя значения кибернетической мощности KWi и полной кибернетической мощности  текущего i-го маршрута от узла-отправителя до узла-получателя, соответственно. После чего, как информация об m-ых интервалах связи, входящих в текущий i-ый маршрут, из запоминающего устройства 5.4 выдана на «упр. вх.» первого и третьего запоминающих устройств 5.1 и 5.3, то в запоминающем устройстве 5.4 формируют и направляют сигнал с его выхода 2 на «упр. вх.» сумматоров 6.1 и 6.2. По сигналам на «упр. вх.» сумматоров 6.1 и 6.2 с их выходов выдают значения KWi и

текущего i-го маршрута от узла-отправителя до узла-получателя, соответственно. После чего, как информация об m-ых интервалах связи, входящих в текущий i-ый маршрут, из запоминающего устройства 5.4 выдана на «упр. вх.» первого и третьего запоминающих устройств 5.1 и 5.3, то в запоминающем устройстве 5.4 формируют и направляют сигнал с его выхода 2 на «упр. вх.» сумматоров 6.1 и 6.2. По сигналам на «упр. вх.» сумматоров 6.1 и 6.2 с их выходов выдают значения KWi и  , соответственно, на входы 1 и 2 делителя 7. Затем сумматоры 6.1 и 6.2 обнуляют («уст. 0»).

, соответственно, на входы 1 и 2 делителя 7. Затем сумматоры 6.1 и 6.2 обнуляют («уст. 0»).

В делителе 7 для каждого i-го маршрута осуществляют операцию деления значений KWi на значения  , определяя значения КПД передачи информации ηi каждого i-го маршрута, которые с выхода делителя 7 выдают на вход 1 схемы сравнения 8, на вход 2 которой подают текущее минимальное значение КПД передачи информации

, определяя значения КПД передачи информации ηi каждого i-го маршрута, которые с выхода делителя 7 выдают на вход 1 схемы сравнения 8, на вход 2 которой подают текущее минимальное значение КПД передачи информации  с выхода 2 запоминающего устройства 5.2. Так как первоначально в запоминающем устройстве 5.2 значение

с выхода 2 запоминающего устройства 5.2. Так как первоначально в запоминающем устройстве 5.2 значение  и информация о текущем оптимальном маршруте

и информация о текущем оптимальном маршруте  отсутствуют, то значение ηi, с выхода 1 схемы сравнения 8 сразу подают на «упр. вх. 1» запоминающего устройства 5.2, где его запоминают

отсутствуют, то значение ηi, с выхода 1 схемы сравнения 8 сразу подают на «упр. вх. 1» запоминающего устройства 5.2, где его запоминают  , а также запоминают информацию о текущем оптимальном маршруте

, а также запоминают информацию о текущем оптимальном маршруте  . При последующих вычислениях в делителе 7 значения ηi в схеме сравнения 8 сравнивают его с значением

. При последующих вычислениях в делителе 7 значения ηi в схеме сравнения 8 сравнивают его с значением  , и если

, и если  , то значение ηi с ее выхода 1 подают на «упр. вх. 1» запоминающего устройства 5.2. По сигналу на «упр. вх. 1» запоминающего устройства 5.2 запоминают (обновляют) значение

, то значение ηi с ее выхода 1 подают на «упр. вх. 1» запоминающего устройства 5.2. По сигналу на «упр. вх. 1» запоминающего устройства 5.2 запоминают (обновляют) значение  и текущий оптимальный маршрут

и текущий оптимальный маршрут  . Затем в схеме сравнения 8 формируют и направляют сигнал с ее выхода 2 на «упр. вх.» блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1, в том числе, в случае не выполнения условия

. Затем в схеме сравнения 8 формируют и направляют сигнал с ее выхода 2 на «упр. вх.» блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1, в том числе, в случае не выполнения условия  в схеме сравнения 8. По сигналу на «упр. вх.» блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1 удаляют информацию о текущем i-ом маршруте Li и проверяют наличие информации о других возможных маршрутах. В случае, если в блоке измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1 имеется информация о другом возможном маршруте, то с его выхода 1 выдают информацию о следующем текущем i-ом маршруте Li на входы запоминающих устройств 5.2 и 5.4. В случае отсутствия информации о других возможных маршрутах в блоке измерителе-вычислителе всех возможных маршрутов от узла-отправителя до узла-получателя 1 формируют и направляют сигнал с его выхода 2 на «упр. вх. 2» запоминающего устройства 5.2. По сигналу на «упр. вх. 2» запоминающего устройства 5.2 на его выход 1, являющийся выходом устройства, выдают информацию об оптимальном маршруте

в схеме сравнения 8. По сигналу на «упр. вх.» блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1 удаляют информацию о текущем i-ом маршруте Li и проверяют наличие информации о других возможных маршрутах. В случае, если в блоке измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя 1 имеется информация о другом возможном маршруте, то с его выхода 1 выдают информацию о следующем текущем i-ом маршруте Li на входы запоминающих устройств 5.2 и 5.4. В случае отсутствия информации о других возможных маршрутах в блоке измерителе-вычислителе всех возможных маршрутов от узла-отправителя до узла-получателя 1 формируют и направляют сигнал с его выхода 2 на «упр. вх. 2» запоминающего устройства 5.2. По сигналу на «упр. вх. 2» запоминающего устройства 5.2 на его выход 1, являющийся выходом устройства, выдают информацию об оптимальном маршруте  между узлом-отправителем и узлом-получателем. Затем через Δtзад запоминающее устройство 5.2 обнуляют («уст. 0»). После чего продолжают представленные выше измерения и вычисления.

между узлом-отправителем и узлом-получателем. Затем через Δtзад запоминающее устройство 5.2 обнуляют («уст. 0»). После чего продолжают представленные выше измерения и вычисления.

Таким образом работа устройства определения оптимального маршрута передачи информации в системе связи реализована в полном объеме.

В результате работы устройства формируется сигнал на его выходе с информацией об оптимальном маршруте от узла-отправителя до узла-получателя по критерию минимального значения КПД передачи информации из всех возможных маршрутов от узла-отправителя до узла-получателя. Сигнал с выхода устройства может быть отображен, например, на типовых устройствах индикации с использованием микроконтроллеров [Прокопенко B.C. Программирование микроконтроллеров ATMEL на языке С. С.-Пб.: Корона-Век, 2012. с. 286-298].

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОПРЕДЕЛЕНИЯ ОПТИМАЛЬНОГО МАРШРУТА ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМЕ СВЯЗИ | 2024 |

|

RU2835571C1 |

| СПОСОБ ОЦЕНКИ ЭФФЕКТИВНОСТИ ИНФОРМАЦИОННОГО ОБМЕНА СИСТЕМЫ СВЯЗИ | 2020 |

|

RU2758261C1 |

| УСТРОЙСТВО ОЦЕНКИ ЭФФЕКТИВНОСТИ ИНФОРМАЦИОННОГО ОБМЕНА СИСТЕМЫ СВЯЗИ С УЧЕТОМ ИНФОРМАЦИОННЫХ ПОТЕРЬ | 2021 |

|

RU2785586C1 |

| СПОСОБ ОЦЕНКИ ЭФФЕКТИВНОСТИ ИНФОРМАЦИОННОГО ОБМЕНА СИСТЕМЫ СВЯЗИ С УЧЕТОМ ИНФОРМАЦИОННЫХ ПОТЕРЬ | 2021 |

|

RU2779503C1 |

| СПОСОБ ОЦЕНКИ ИНФОРМАЦИОННОЙ ЭФФЕКТИВНОСТИ СИСТЕМЫ СВЯЗИ | 2011 |

|

RU2477928C1 |

| СПОСОБ И УСТРОЙСТВО ГИБРИДНОЙ КОММУТАЦИИ РАСПРЕДЕЛЕННОЙ МНОГОУРОВНЕВОЙ ТЕЛЕКОММУНИКАЦИОННОЙ СИСТЕМЫ, БЛОК КОММУТАЦИИ И ГЕНЕРАТОР ИСКУССТВЕННОГО ТРАФИКА | 2014 |

|

RU2542906C1 |

| УСТРОЙСТВО ОЦЕНКИ ЭФФЕКТИВНОСТИ ИНФОРМАЦИОННОГО ОБМЕНА СИСТЕМЫ СВЯЗИ | 2017 |

|

RU2671623C1 |

| УСТРОЙСТВО ОЦЕНКИ ЭФФЕКТИВНОСТИ ИНФОРМАЦИОННОГО ОБМЕНА СИСТЕМЫ СВЯЗИ | 2020 |

|

RU2751077C1 |

| Устройство структурной адаптации системы связи | 2019 |

|

RU2713616C1 |

| УСТРОЙСТВО СТРУКТУРНОЙ АДАПТАЦИИ СИСТЕМЫ СВЯЗИ С УЧЕТОМ ИНФОРМАЦИОННЫХ ПОТЕРЬ | 2022 |

|

RU2796098C1 |

Изобретение относится к устройствам определения маршрута передачи информации. Технический результат заключается в снижении временной задержки и потерь пакетов и достигается за счет распределения информационных потоков. Устройство содержит блок измерителя-вычислителя возможных маршрутов (1), группы счетчиков (2.1.М) и делителей (3.1.М), на которые подают значения интервала времени измерений, группу перемножителей (4.1.М), запоминающее устройство (ЗУ) (5.1), сумматор (6.1), делитель (7), схему сравнения (8), второе ЗУ (5.2), выход которого является выходом устройства. Дополнительно введены вторые группы счетчиков (2.2.М), сумматоров (9.М) и делителей (3.2.М), на которые подают значения количества измерений n. Делители (3.2.М) соединены с группой перемножителей (4.1.М). Введены также третье (5.3) и четвертое (5.4) ЗУ, вторая группа перемножителей (4.2.М), второй сумматор (6.2), соединенный с делителем 7. ЗУ 5.4 соединено с управляющими входами ЗУ 5.1, ЗУ 5.3 сумматоров 6.1 и 6.2. Блок 1 соединен с ЗУ 5.2, ЗУ 5.4, и управляющим входом ЗУ 5.2. ЗУ 5.2 соединено со схемой сравнения 8, которая соединена с управляющим входом блока 1. 1 ил.

Устройство определения оптимального маршрута передачи информации в системе связи, содержащее блок измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя (1), отличающееся тем, что дополнительно введены последовательно соединенные по количеству М интервалов системы связи первая группа счетчиков (2.1.М), первая группа делителей (3.1.М), на вторые входы которых подают значения заданного интервала времени измерений Δtзад, первая группа перемножителей (4.1.М), первое запоминающее устройство (5.1), первый сумматор (6.1), делитель (7), схема сравнения (8), второе запоминающее устройство (5.2), первый выход которого является выходом устройства; также дополнительно введены последовательно соединенные по количеству М интервалов системы связи вторая группа счетчиков (2.2.М), группа сумматоров (9.М), вторая группа делителей (3.2.М), на вторые входы которых подают значения количества измерений n, а выходы второй группы делителей (3.2.М) соединены со вторыми входами первой группы перемножителей (4.1.М); кроме того, дополнительно введены четвертое запоминающее устройство (5.4) и последовательно соединенные по числу М интервалов системы связи вторая группа перемножителей (4.2.М), третье запоминающее устройство (5.3), второй сумматор (6.2), выход которого соединен со вторым входом делителя (7); первый выход четвертого запоминающего устройства (5.4) соединен с управляющими входами первого (5.1) и третьего (5.3) запоминающих устройств, а второй выход четвертого запоминающего устройства (5.4) соединен с управляющими входами первого (6.1) и второго (6.2) сумматоров; первый выход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя (1) соединен с входами второго (5.2) и четвертого (5.4) запоминающих устройств, а второй выход блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя (1) соединен со вторым управляющим входом второго запоминающего устройства (5.2), второй выход которого соединен со вторым входом схемы сравнения (8), второй выход которой соединен с управляющим входом блока измерителя-вычислителя всех возможных маршрутов от узла-отправителя до узла-получателя (1).

| 0 |

|

SU142581A1 | |

| УСТРОЙСТВО И СПОСОБ ДЛЯ КОММУТАЦИИ МНОЖЕСТВА СИГНАЛОВ С ПРИМЕНЕНИЕМ МНОГОСТУПЕНЧАТОЙ ОБРАБОТКИ ПРОТОКОЛА | 2002 |

|

RU2299529C2 |

| Устройство для определения путей в графе | 1984 |

|

SU1292000A1 |

| US 7321594 B2, 22.01.2008 | |||

| US 7016366 B2, 21.03.2006. | |||

Авторы

Даты

2025-02-19—Публикация

2024-04-17—Подача