(54) СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Компенсационный стабилизатор постоянного напряжения | 1981 |

|

SU922698A1 |

| Стабилизатор постоянного напряжения | 1983 |

|

SU1130842A2 |

| Амплитудно-временной преобразователь | 1974 |

|

SU849484A1 |

| Стабилизатор постоянного напряжения | 1979 |

|

SU828179A1 |

| Функциональный преобразователь | 1978 |

|

SU750516A1 |

| Стабилизатор постоянного напряжения | 1980 |

|

SU885982A1 |

| Стабилизатор постоянного напряжения с защитой | 1980 |

|

SU943676A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕКЛЮЧЕНИЯ ЗНАКОПЕРЕМЕННЫХ АНАЛОГОВЫХ СИГНАЛОВ | 1973 |

|

SU385287A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2616573C1 |

| БИБЛИОТЕКА I | 1971 |

|

SU299938A1 |

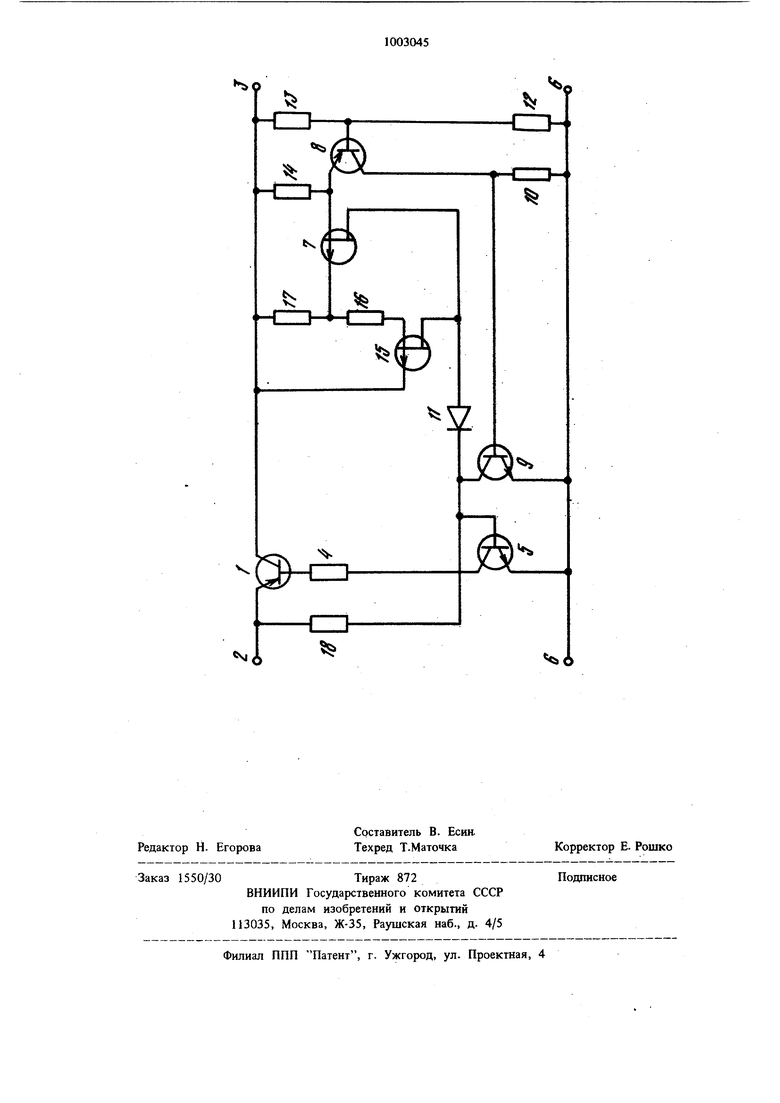

Изобретение относится к регуляторам напряжения постоянною тока. Известны стабилизаторы постоянного напряжения, содержащие регулирующий транзистор, согласующий транзистор, дифференциальный усилитель, делитель выходно1о напряжения и источник опорного напряжения 1 и 2. Наиболее близким по технической сущности и достигаемому результату к изобретению является стабилизатор постоянного напряжения, содержащий регулирующий транзистор, подключенный змиттером к входному, коллек тором - к выходному выводам, базой - к коллектору согласующего транзистора, эмиттер которого подключен к общей шине, а база - к выходу дифференциального усилителя, входы которого подключены к дели i елю выходного напряжения и источнику опор ного напряжения, состоящего из полевого тр зистора с токозадающим сопротивлением в цепи истока 2. Недостатком известных стабилизаторов является значительный ток потребления схемой обратной связи, который в основном определяется током источника опорного напряжения и составляет более 0,1 m А, что снижает КПД маломощных стабилизаторов напряжения. Целью изобретения является повыщение КПД путем уменьшения тока потребления схемой обратной связи. Поставленная цель достигается тем, что в стабилизаторе постоянного напряжения дифференциальный усилитель выполнен гибридным на полевом и биполярном транзисторах с активной коллекторной нагрузкой, причем Т1равляющий вход полевого транзистора дифференциального усилителя соединен с выходом источника опорного напряжения ,вход питания которого включен между выходным выводом стабилизатора и выходом дифференциального усилителя. На чертеже представлена принципиальная электрическая схема стабилизатора. Стабилизатор содержит регулирующий транзистор 1, подключенный эмиттером к входному 2, коллектором к выходному 3 выводам, базой через резистор 4 - к коллектору согласующего транзистора 5, который эмиттером подключен к общей щине 6, а базой - к выходу диффер)нциального усилителя, выполненного гибридным наполевом 7 и биполярном 8 транзисторах с активной коллекторной нагрузкой на биполярном транэисторе 9. Вход транзистора 9 включен в вы ходную коллекторную цепь транзистора 8 с резистором 10, а выход - в выходную сток вую цепь транзистора 7 через развяз.ывающий диод 11. База транзистора 8 соединена со средним выводом делителя выходного напряжения на резисторах 12 и 13, эмиттер транзистора 8 и исток транзистора 7 через резистор 14 подключены к выходному выводу 3, затвор транзистора 7 подключен к выходу источника опорного напряжения на полевом транзисторе Г5 с токозадающим сопротивлением на резисторах 16 и 17 в цепи истока. Необходимая величрша опорного напря жения снимается с резистора 17. Стабилизатор содержит также пусковой резистор 18. Вход питания источника опорного напряжения вкл чен между выходным выводом 3 и выходом дифференциального усилителя через упомянутый диод 11. Работа стабилизатора при наличии возмуща ющего воздействия происходит следующим об разом. Например, увеличение входного питающего напряжения приводит к з еличению тока кол лектора транзистора 1, в основном, за счет увеличения тока его базы, являющегося током коллектора согласующего транзистора 5, ток базы которого }гвеличнлся по цепи пускового резистора 18. Это вызывает увеличение напряжения на выходе стабилизатора, напряжения на входе транзистора 8 усилителя, тока коллектора транзистора 8, напряжения на pe3nctope 10 и входе транзистора 9. При этом уменьщается ток стока транзистора 7, увеличиваетсч ток коллектора транзистора 9, а ток базы транзистора 5 уменьщается, что приводит к уменьщению тока базы и коллек тора регулирующего транзистора I и, следовательно к восстановлению номинального значения выходного -напряжения. Благодаря выполнению дифференциального усилителя гибридным имеется возможность получить низкий температурный коэффициент (ТКИ) выходного напряжения путем компенсации отрицательного ТКН биполярного транзистора 8 положительным ТКН источника опорного напряжения на транзисторе 15 и усилителя на транзисторе 7, причем положительный ТКН каскадов иа транзисторах 7 и 15 связан с с положительным температурным коэффициентом тока стока (истока) полевых транзисторов, который имеет место при токах стока (истока) в единицы микроамп ер, что и позволяет резко снизить ток потребления источником опорного напряжения и усилителем. Кроме того, включение в коллекторную цепь транзистора 9 источника опорного напряжения позволяет улучшить режим работы транзистора 9 без введения дополнительной цепи смещения и тем самь1м также сократить ток потребления схемой обратной связи. Формула изобретения Стабилизатор постоянного напряжения, содержащий регулир)тощий транзистор, подключенный эмиттером к входному, коллектором - к выходному выводам, базой - к коллектору согласующего транзистора, эмиттер которого подключен к общей шине, а база - к выходу дифференциального усилителя, входы которого подключены к делителю выходного напряжения и источнику опорного напряжения, состоящего из полевого транзистора с токозадающим сопротивлением в цепи истока, отличающийся тем, что, с целью повышения КПД путем уменьшения тока потребления схемой обратной связи, дифференциальный усилитель выполнен гибридным на полевом и биполярном транзисторах с активной коллекторной нагрузкой, причем управляющий вход полевого транзистора дафференциального усилителя соединен с выходом источника опорного напряжения, вход питания которого включен между выходным выводом стабилизатора и выходом дифференциального усилителя. Источники информации, принятые во внимание при экспертизе 1.Патент Японии N« 52-44420,,кл.С 05 F 1/56, 1977. 2.Патент США № 3735242, кл. G 05 F 1/56, 1973.

6

Авторы

Даты

1983-03-07—Публикация

1980-11-12—Подача