Предлагаемое изобретение может найти применение в автоматике, измерительной, вычислительной и других областях техники. Оно предназначено для построения дифференциальных входных каскадов с большим входным сопротивлением и высоким коэффициентом подавления синфазных сигналов по разностному выходу.

Известны дифференциальные усилители, содержащие два входных транзистора, к коллекторам которых подключены резисторы нагрузки, а эмиттеры соединены между собой.

Однако такие дифференциальные каскады отличает незначительное подавление синфазных сигналов, в том случае, если транзисторы имеют не одинаковые параметры. Кроме того, параметры транзисторов сильно изменяются от температуры и во времени, вследствие чего коэффициент подавления синфазных сигналов также значительно уменьшается в течение времени и в зависимости от температуры. Это объясняется тем, что при подаче на входы дифференциального усилителя одинаковых сигналов изменяется потенциал эмиттеров входных транзисторов, а следовательно изменяется напряжение на эмиттерном двухполюснике нагрузки (резисторе, источнике стабильного тока), вследствие чего изменяетх;я суммарный ток, и при разных параметрах входных транзисторов он распределяется между ними не поровну и вызывает различные изменения напряжения на коллекторных нагрузках. Кроме того при изменении потенциала на эмиттерах входных

транзисторов изменяется также напряжение коллектор-эмиттер входных транзисторов, что также вызывает изменение параметров транзисторов и в конечном счете приводит к появлению разностного сигнала при синфазном

сигнале на входах.

Очевидно, что весьма трудно гарантировать высокий коэффициент режекции (коэффициент подавления синфазных сигналов) синфазных сигналов (отношение приведенного ко входу дифференциального сигнала на выходе к изменению синфазного сигнала на входах) даже при тш,ательном подборе транзисторов в широком диапазоне изменения температур и в течение длительного времени.

Это особенно касается дифференциальных каскадов на полевых транзисторах, так как они не обладают высоким выходным сопротивлением и изменение напряжения сток-исток приводит к появлению значительного

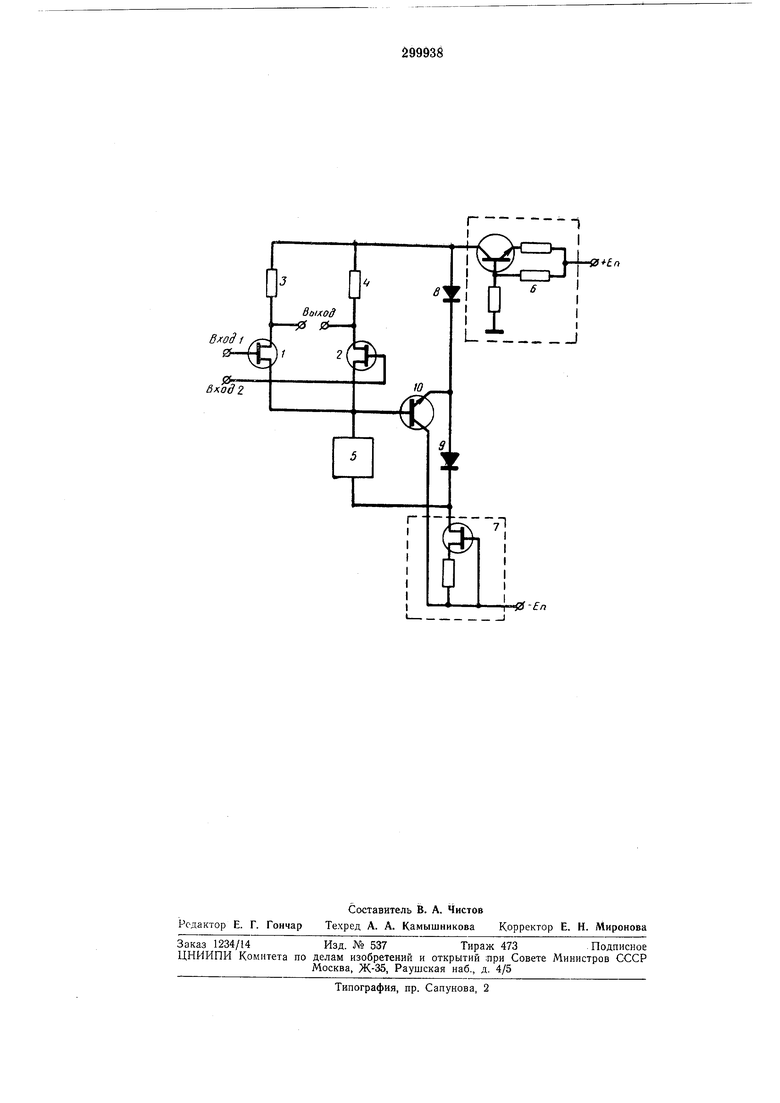

разностного сигнала на выходе при изменении синфазного сигнала на входах. Кроме того, полевые транзисторы сильно изменяют свои параметры от температуры, что также значительно снижает коэффициент режекции Horo каскада. В то же время балансные каскады на полевых транзисторах имеют очень большое входное сопротивление и дифференциальные усилители на них в некоторых случаях не могут быть заменены аналогичными усилителями на биполярных транзисторах. К таким устройствам следует отнести в первую очередь устройства сравнения автоматических цифровых вольтметров и операционные усилители. Целью настоящего изобретения являются увеличение коэффициента режекции синфазных сигналов и коэффициента режекции напряжения питания. Предлагаемый дифференциальный усилитель содержит два стабилитрона, два стабилизатора тока, входы которых подключены к соответствующим клеммам источника питания усилителя, а выходы соединены между собой через упомянутые стабилитроны, включенные последовательно, и транзистор, эмиттер которого подключен к точке соединения стабилитронов, коллектор к одному из источников питания, а база к эмиттерам входных транзисторов. В результате этого можно получить режекцию синфазных сигналов даже при не идентичных транзисторах более 100 дб. На чертеже представлена принципиальная схема предлагаемого дифференциального усилителя. Дифференциальный усилитель содержит входные полевые транзисторы / и 2, в стоки которых включены резисторы и - а истоки соединены между собой и двухполюсником нагрузки 5, последовательную цепь, состоящую из стабилизаторов тока 6 и 7, подключенных к источникам питания разной полярности, выходы стабилизаторов тока соединены между собой через два стабилитрона 8 и 9, и транзистор 10, коллектор которого подключен к одному из источников питания, эмиттер соединен с общей точкой соединения стабилитронов 8 и 9, а база подключена к истокам входных полевых транзисторов / и 2. Резисторы нагрузки 3, 4 н второй ввод двухполюсника нагрузки соединены с соответствующими выходами стабилизаторов тока 6 и 7. Как видно из принципиальной схемы при изменении синфазного сигнала на входах дифференциального каскада изменяется напряжение истоков входных транзисторов. Эти изменения напряжения через транзистор 10 и стабилитроны 8 и 9 передаются на выходы стабилизаторов тока 6 и 7. Однако при этом напряжение на двухполюснике нагрузки 5, определяемое стабилитроном 9 и переходом база-эмиттер транзистора 10, остается неизменным. Кроме того поддерживается неизменным также напряжение питания стоковой цепи входных транзисторов, которое определяется напряжением стабилизации стабилнтрона 8 и напряжением перехода база-эмиттер транзистора 10. Вследствие того, что при изменении синфазного сигнала напряжение питания дифференциального усилителя остается неизменным, не изменяются также параметры входных транзисторов и ток через них. Благодаря этому такая схема позволяет получить практически любой коэффициент режекции синфазных сигналов. Следует заметить, что здесь можно получить также больщой коэффициент режекции питающих напряжений, так как напрял ение питания в этой схеме определяется напряжением на стабилитронах 8 и 9. При усилении разностных сигналов принцип работы предлол енного усилителя не отличается от известных дифференциальных усилителей. Таким образом, предложенной дифференциальный усилитель обладает всеми положительными качествами известных усилителей этого типа и в то время позволяет получить коэффициент режекции синфазных сигналов более 100 дб без подбора транзисторов. В этой схеме значительно ослабляется также влияние питающих напряжений. Предмет изобретения Дифференциальный усилитель, содержащий два входных транзистора, к коллекторам которых подключены резисторы, а эмиттеры соединены между собой, отличающийся тем,, что с целью увеличения коэффициента подавления синфазной помехи, усилитель содержит два стабилитрона и два стабилизатора тока, входы которых подключены к соответствующим клеммам источника питания усилителя, а выходы соединены между собой через упомянутые стабилитроны, включенные последовательно, и транзистор, эмиттер которого подключен к точке соединения стабилитронов, коллектор к одному из источников питания, а база к эмиттерам входных транзисторов.

t

вход 2

r

r-0-f/7

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2016 |

|

RU2616570C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2621286C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2642337C1 |

| Дифференциальный усилитель | 1977 |

|

SU736358A1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2566964C1 |

| Стабилизатор постоянного напряжения | 1983 |

|

SU1130842A2 |

| Дифференциальный каскадный усилитель постоянного тока | 1975 |

|

SU896753A1 |

| Стабилизатор постоянного напряжения | 1979 |

|

SU828179A1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2568384C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374760C1 |

Даты

1971-01-01—Публикация