(54) ФОРМИРОВАТЕЛЬ ПИЛООБРАЗНОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь пилообразного напряжения | 1980 |

|

SU919069A1 |

| Операционный усилитель | 1983 |

|

SU1190467A1 |

| Пиковый детектор импульсов | 1985 |

|

SU1272259A1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| Стабилизатор напряжения постоянного тока | 1987 |

|

SU1529191A1 |

| Транзисторный усилитель с автоматической регулировкой усиления | 1982 |

|

SU1109878A1 |

| Управляемый фантастронный генератор | 1976 |

|

SU627571A1 |

| Формирователь электрического сигнала | 1980 |

|

SU951643A1 |

| Транзисторный ключ | 1991 |

|

SU1780179A1 |

| Устройство усиления | 1989 |

|

SU1617629A1 |

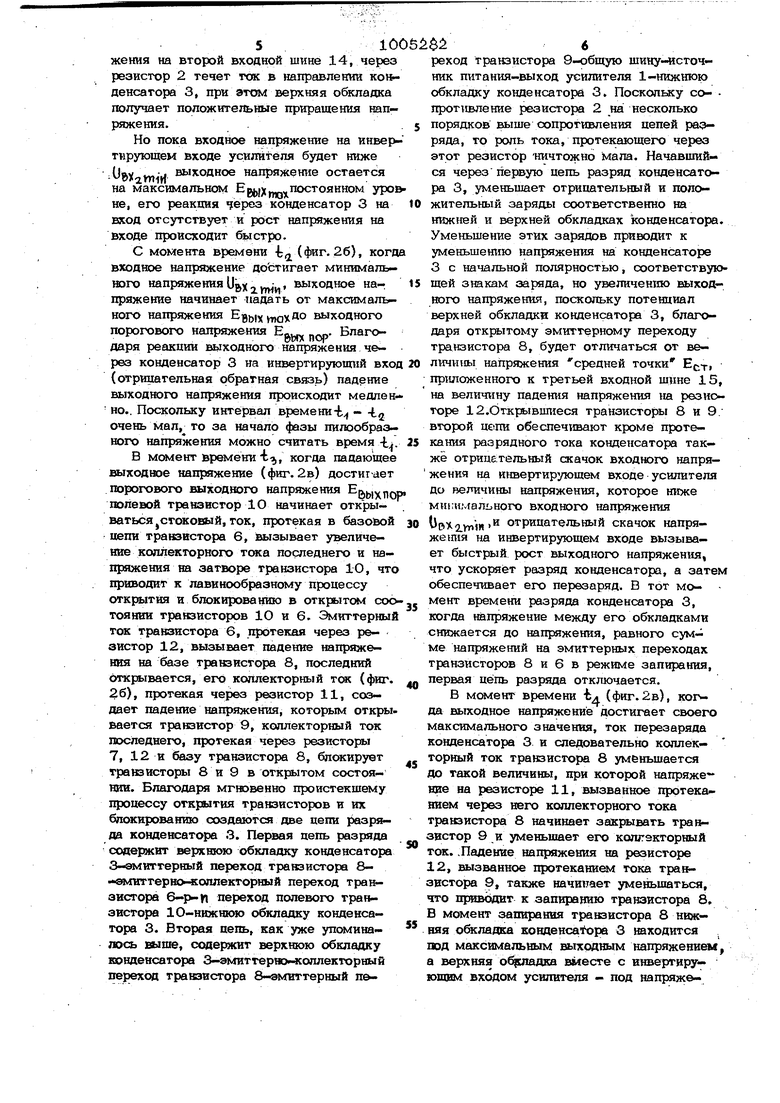

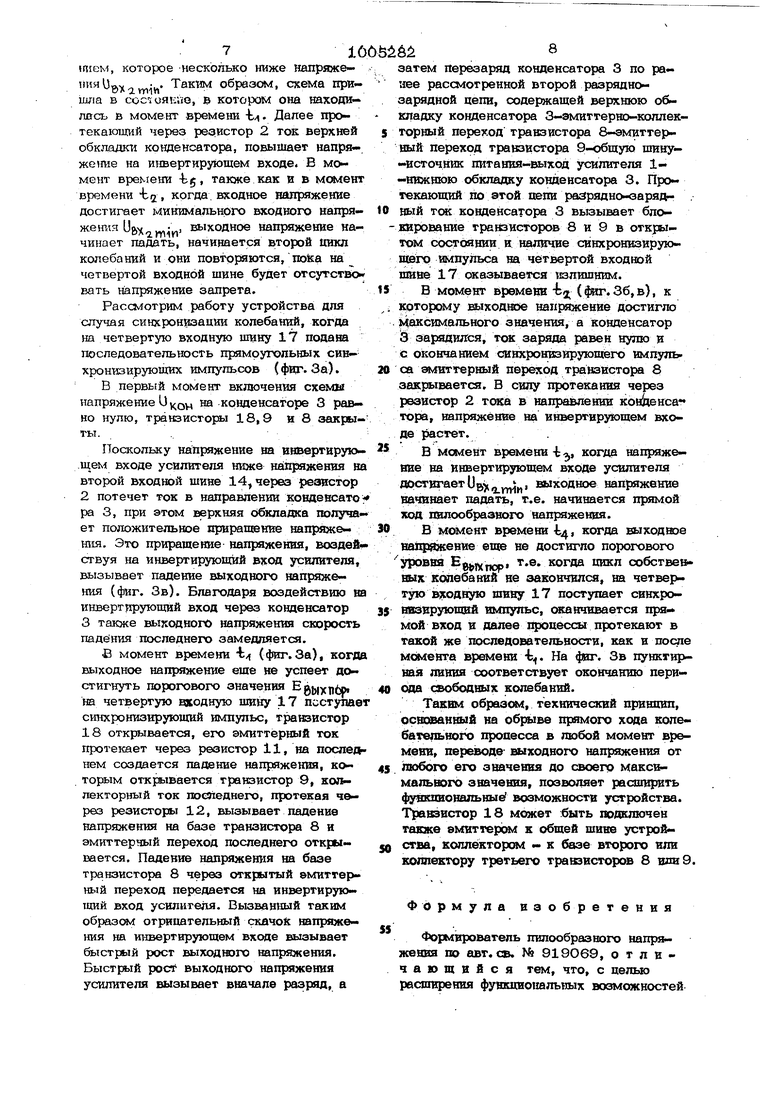

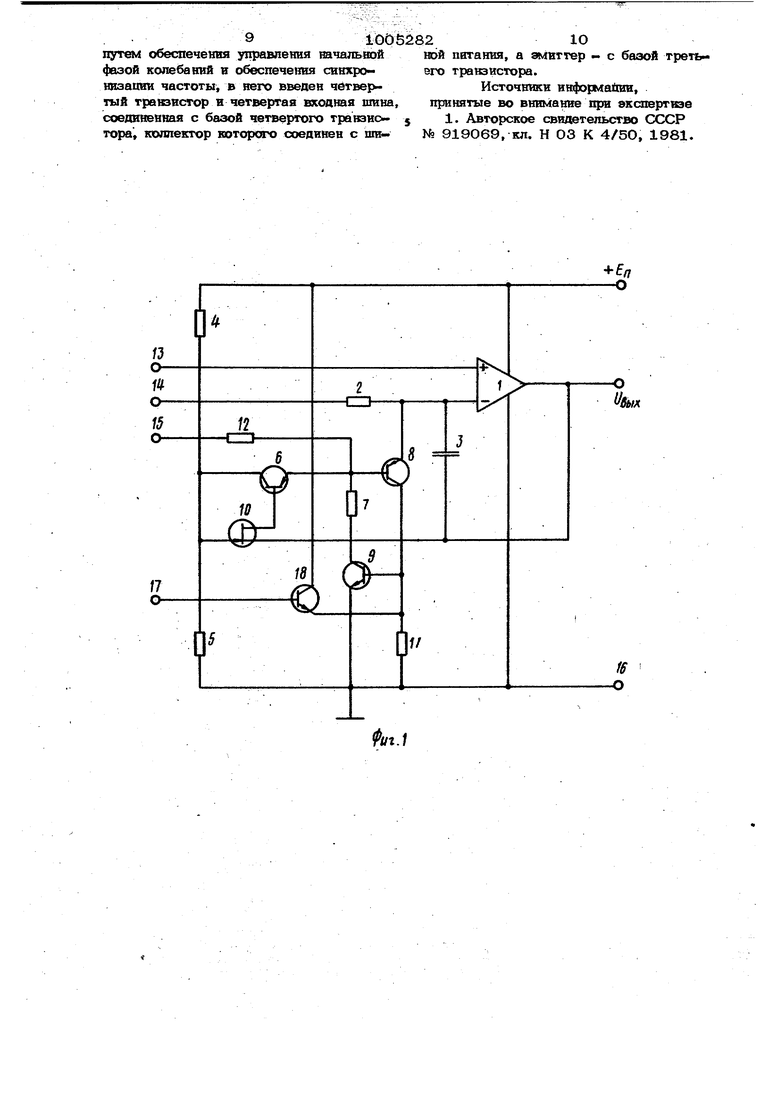

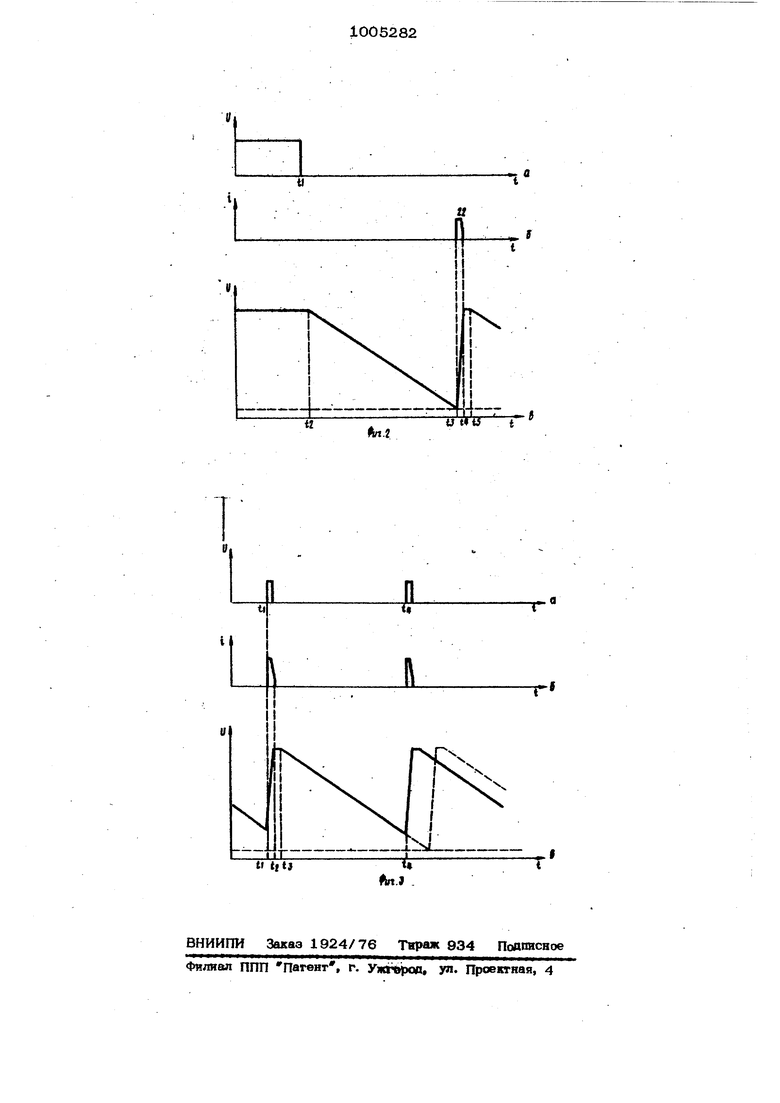

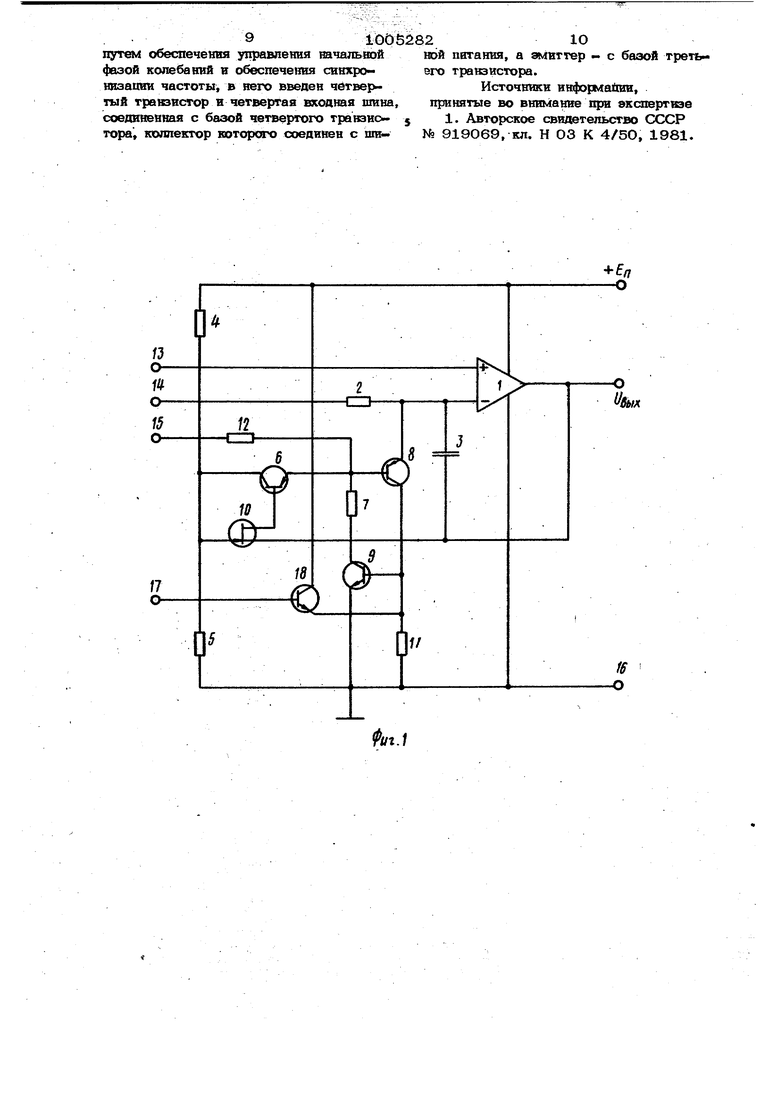

Изобретение относится к импупьсшэй техиике и может быть использовано, вапртлер, в поисковой системе фазовой авт подстройки частоты. По основному авт. св. № 919069 известен формирователь пкпообразного напряжения, содержащий дифферешгаальный усиля тепь, неинвертнрующий вход которого подключён к первой входной юяне устройства, инвертирующий вход через первый резистор соединен со второй входной шиной устройства, а через конденсатор - с выходом дифференциального усилителя, делитель напряжения, подклк ченный между шинами источника питания, первый транзистор, эмиттер которого подключен к базе второго транзистора и к одному из выводов второго резистора, третий транзистор, эмиттер которого поа кгаочен к общей шине устройства, полевой транзистор, третий и четвертый резисторы. С целью увеличения размаха формируемого напряжения при одновпеменном упрощении устройства коллектор первого тракзистора подключен к выходу делителя напряжения, база - к стоку полевого транзистора, затвор которого подключен к выходу делителя напряжения, исток - к выходу устройства, база третьего транзистора подключена к коллектору второго транзистора и через третий резистор к общей шине устройства, коллектор - к второму выводу BTopoixj резистора, эмиттер второго транзистора подключен к инвертирующему входу дифференциального усилителя, а база через четвертый резио. тор к третьей входной игане устройства l} Недостатком устройства яылется ограниченность функциональных возможностей, так как оно не обеспечивает управление начальной фасой колебаний и синхронизацию частоты. Целью изобретения является расширение функциональных возможностей уст ройства путем обеспечения управления начальной фазой Kone6EiHv и обеспечения синхронизации частоты. 310 Поставленная цель достигается тем, что в фоуыирователь тшообразного напряжешш, содержащий дифференциальный усилитель, неинвертируюпшй вход которого псдключен к первой входной шине устройства, инвертирующий вход через первый резистор соединен со второй входной шиной устройства, а через конденсатор с Еыходом дифференциального усилителя, делитель напряжения, подключенный межд шинами источника питания, первый транзистор, эмиттер которого подключен к базе второго транзистора и к одному из выводов второго резистора, третий тра зистор, эмиттер которого подключен к общей шине устройства, полевой травзис тор, третий и четвертый резисторы, коллектор первого транзистора подключен к выходу делителя напряжения, база - к стоку полевого травзистора, затвор которого подключен к выходу делителя напряжения, исток - к выходу устройства, база третьего транзистора подключена к коллектору второго транзистора и через третий резистор - к общей щине устройства, коллектор - к вторсйлу выводу второго резистора, эмиттер второго Tpat зистора подключен к инвертирующему вхо ду дифферетшального усилителя, а база через четвертый резистор - к третьей входной шине устройства, введен четве1 тый транзистор и четвертая входная шина, соединенная с базой четвертого транзистора, коллектор которого соединен с шиной питания, а эмиттер - с базой трет его транзистора. На фиг. 1 приведена принципиальная электрическая схема устройства; на фиг. 2 и 3 - эпюры, поясняющие работу , устройства. Устройство содержит диффереканальный усилитель 1, первый резистор 2, ко щевсатор 3, делитель напряжения на резисторах 4 и 5, первый транзистор 6, резистор 7, второй транзистор 8, третий транзистор 9, полевой травэистор 10, резисторы 11 и 12, входные шины 13, 14 и 15, общую шину 16, дополнительную четвертую входную шину 17, дополнительный транзистор 18. Напряжения на входных шинах 13, 14 и 15 равны напряжению средней точки источни ка сигнала (например фазового детектора Е приблизительно равно половине напряжения источника питания. Рассмотрим работу устройства для случая управлешга начальной фазой колебаний, когда йа четвертую входную шину 17 подано напряжениезапрета до мсме 824 та вкпючения скемы (фиг. 2а). В первый момент включения, схемы транзистор 18 под воздействием напряжения запрета оказывается открытым, а напряжение между обкладками конденсатора 3 равю нулю. Эмиттерный ток транзистора 18, протекая через резистор.11, создает положительный перепад напряжения на базе транзистора 9, коллекторный ток последнего, протекая через резисторы 7 и 12, создает отрипательный перепад на базе транзистора 8 и эмиттерный переход последнего открывается. Отрицательный гюрепвд напряжения на базе транзистора 8 через открытый эмиттерный переход передается на инвертирующий вход усилителя. Вызванный таким путем отрица тельный скачок напряжения на инвертирующем входе вызывает быстрый рост выходного напряжения усилителя, который вызывает заряд конденсатора 3 по цепи: верхняя обкладка конденсатора 3- -вмкттерно-коллекторный переход транзистора 8-эмиттерный переход травзиотора 9-общая шина 16-источник питания-выход усилителя 1-нижняя обкладка конденсатора 3. Протекающий по этой цепи ток конденсатора 3, на {эезисторе 11 совпадает с направлением эмиттерного тока транзиотора 18 и заблокирует транзисторы 9 и 8в открытом состоянии. После того, как отрииательнь1й скачок напряжения на инвертирующем входе усилителя достигает напряжения, которое ниже напряжения UB 8 выходное напряжение усилителя 1 достигает максимального значения )i,конденсатор 3 полностью зарядится, его ток, протекающий по второй разрядно-аарядной цепи, становится равным нулю, блокировка с транзисторов 9,8 снимается, но они остаются открытыми благодаря тому, что к базе транзистора 9приложен еще положительный перепад, вызванный эмиттерным током травзистора 18, вызванного напряжением запрета. В момент времени -kj (фиг.2а,в) напряжение запрета на четвертой входной шине 17 падает, транзистор 18 закрывается, поскольку конденсатор 3 полностью заряжен, его зарядный ток, протекающий через эмиттерный переход транзистора 9, равен нулю, транзисторы 9 и 8 также закрываются, но напряжение на инвертирую юием входе остается ниже минимального входного напряжения, благодаря электрик ческому заряду на обкладках конденсат{уре 3. Посг ольку напряжение на ивверп рукмцем входр усилителя 1 ниже напряжения на второй входной шине 14, через резистх)р 2 течет ток в направлетга кон денсатора 3, при этом верхняя обкпадка получает положительные приращения напряжения.. Но пока входное напряжение на инвер тирующей входе усилителя будет ниже упИ выходное напряжение остается на максимальном Eg|,|)(,постоянном уро не, его реакиия ёрез конденсатор 3 на вход отсутствует и рост напряжения на входе происходит быстро. С момента времени (фкг.26), когд входное напряжение достигает минимального напряжения Uftx2.НИИ Ь1ходное на-г пряжение начинает падать от максималь- ногч напряжения выходного порогового напряжения Е„.„ ,„,. Благодаря реакции выходного напряжения через конденсатор 3 на инвертирующий вхо (отрицательная обратная связь) падение выходного напряжения происходит медлен но.. Поскольку интервал времени-t - -t очень мал, то за начало фазы пилообразного напряжения можно считать время -tj В момент времени t-5, когда падающее выходное напряжение (фиг. 2в) достит-ает порогового выходного напряжения полевой транзистор 10 начинает открываться стоковый, ток, протекая в базовой цепи транзистора 6, вызывает увеличение коллекторного тока последнего и напряжения на затворе транзистора Ю, что приводит к лавинообразному процессу открытия и блокированшо в открытом соо тоянии транзисторов 1О и 6, иттерный ток транзистора 6, протекая через резистор 12, вызывает падение напряжения на базе транзистора 8, последний открывается, его коллекторный ток (фиг. 26), протекая через резистор 11, создает падение напряжения, которым откры вается транзистор 9, коллекторный ток последнего, протекая через резисторы 7, 12 и базу транзистора 8, блокирует транзисторы 8 и 9 в открытом состоянии. Благодаря мгновенно проистекшему процессу открытия транзисторов и их блокированию создаются две цепи разр51да конденсатора 3. Первая цепь разряда содержит верхнюю обкладку конденсатора 3-эмиттерный переход транзистора 8- -вмиттерно-коллекторный переход транзистора 6-1.|г| переход полевого транзистора 10-нижтаою обкладку конденсатора 3. Вторая цепь, как уже упоминалось выше, содержит верхнюю обкладку конденсатора 3-эмиттерно-коллекторный переход транзистора 8-эмиттерный п&реход транзистора 9-общую шину-источник питания-выход усилителя 1-нижнюю обкладку конденсатора 3. Поскольку со- противление резистора 2 на несколько порядков выше сопротивления цепей разряда, то роль тока, протекающего через этот рюзистор НИЧТОЖНО мала. Начавшийся через первую цепь разр5зд конденсатора 3, уменьшает отрицательный и положительный заряды соответственно на нижней и верхней обкладках конденсатора. Уменьшение этих зарядов приводит к уменьшению напряжения на конденсаторе 3 с начальной полярностью, соответствующей знакам заряда, но увеличешпо выходного напряжения, поскольку потенциал верхней обкладки конденсатора 3, благодаря открытому эмиттерному переходу транзистора 8, будет отличаться от величины напряжения средней точки приложенного к третьей входной шнне 15, на величину падения напряжения iia резисторе 12.Открывшиеся транзисторы 8 и 9 второй цепи обеспечивают кроме протекатш разрядного тока конденсатора также отрицательный скачок входного напряжения на инвертирующем входе усилителя до величины напряжения, которое ниже мнснмального входного напряжения Opuivnm отрицательный скачок напряжеш1я на инвертирующем входе вызывает быстрый рост выходного напряжения, что ускоряет разряд конденсатора, а затем обеспечивает его перезаряд. В тот момент времени разряда конденсатора 3, когда напряжение между его обкладками снижается до напряжения, равногчэ сумме напряжений на эмиттерных переходах транзисторов 8 и 6 в режиме запирания, первая цепь разряда отключается. В момент времени Ьл (фиг. 2в), когда выходное напряжение достигает своего максимального значения, ток перезаряда конденсатора 3 и следовательно коллекторный ток транзистора 8 уменьшается до такой величины, при которой напряжеtiHe на резисторе 11, вызванное протека.нием через нехх) коллекторного тока транзистора 8 начинает закрывать транзистор 9 и уменьшает его колгэкторный ток. .Падение напряжения на резисторе 12, вызванное протеканием тока транзистора 9, также начинает уменьшаться, что приводит к запиранию транзистора 8, В момент зашфання транзистора 8 нижняя обкладка конденсатора 3 находится под максимальным выходным напряжением, а верхняя о шадка вместе с инвертирующим входом усилителя - под напряж&inieM, которое несколько ниже Hanpsace- liiwUp, . TaKWvt образом, схема приС/А 2. yyiln

шла в сос1оя1г.ю, в котором она находились в момент времени -Ь. Далее протекакпций через резистор 2 ток верхней обкладки конденсатора, повышает напряжение на инвертирующем входе. В момент времени -feg. также как и в м Ж1ент времени t2, когда входное напряжение достигает минимальнргю входного напряжется Ugix jYiin °Д°® напряжение начинает падать, начинается второй цикл колебаний и они пов1Ч ряются, noisa на четвертой входной шине будет отсутство вать напряжение запрета.

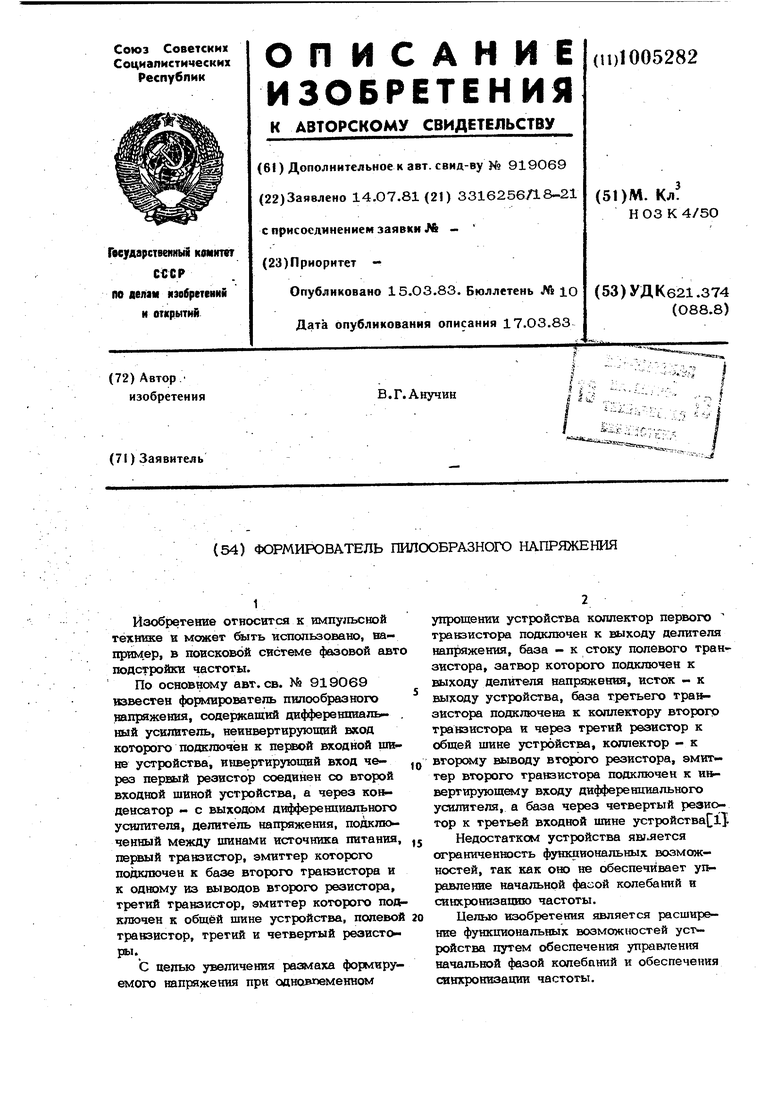

Рассмотрим работу устройства для случая синхронизации колебаний, когда на четвертую входную шину 17 подана последовательность прямоугольных сйн- хронизируюших импульсов (фщ. За).

В первый момент включения схемы напряжение Оцом на конденсаторе 3 равно нулю, транзисторы 18,9 и 8 закрыты.

Поскольку напряжение на инвертирующем входе усилителя ниже напряжения на второй входной шине 14 через резистор

2потечет ток в направлении конденсате ра 3, при этом верхняя обкладка получает положительное приращение напряжения. Это приращение напряжения, воздействуя на инвертирующий вход усилителя, вызывает падение выходнотю напряжения (фиг. Зв). Благодаря воздействию на инвертирующий вход через конденсатор

3также выходного напряжения скорость падения последнего замедляется.

В момент времени 4; (фиг.За), когда выходное напряжение еще не успеет достигнуть порогового значения Egt lxii6P на четвертую нкодную шииу 17 псступае синхронизирующий импульс, транзистор 18 открывается, его эмиттерный ток протекает через резистор 11, на последи нем создается падение напряжения, которым открывается транзистор 9, коп пекторвый ток последнего, протекая резисторы 12, вызывает падение напряжения на базе транзистора 8 и эмиттерный переход последнего открывается. Падение напряжешш на базе транзистора 8 через открытый эмиттерный переход передается на инвертируютций вход усилителя. Вызванный таким образсж отрицательный скачоК напряжет1я на инвертирующем входе вызывает быстрый рост выходного шпряжения. Быстрый рост выходного напряжения усилителя вызывает вначале разряд, а

затем перезаряд конденсатора 3 по раже рассмотренной второй разрядно зарядной цепи, содержащей верхнюю обкладку конденсатора 3-эмиттерно-коллекторный переход транзистора 8-эмиттерный переход транзистора 9-общую шину-источник питания-выход усилителя 1-нижнюю обкладку конденсатора 3. Протекающий по этой кепи разрядно-оаряА- , НЬ1Й т(ж конденсатора 3 вызывает бло- Кирование транзисторов 8 и 9 в открытом состсянии и наличие синхронизирующего импульса на четвертой входной шине 17 оказывается излишним.

В момент времени-feg (фиг.36,в), к , которому выходнсле напряжение достигло М Жсимального значения, а конденсатор is зарядился, ток заряда равен нулю и с окончанием синхронпавзируюпюго импупь. са гмнттерный переход транзистора 8 закрывается. В сипу протекания через резистор 2 тсжа в направлении тора, напряжение на инвертирующем входе jiacTeT..

В момент времени -Ь, когда напряжение на инвертирующем входе усилителя достигает и ву,„, выходное напряжение начинает падать, т.е. начинается прямой ход пилообразного напряжения.

В момент времеш Ц, когда выходное euie не достигло порогового уровня Е гхтюр т.е. когда цикл собствевных колебаний не закончился, на четве тую вводную шину 17 поступает синхронизирующий импульс, (жанчивается прямой вход и далее процессы протекают в такой же последовательности, как и после м 1ента времени -fc. На фиг. Зв пунктирная линия соответствует окончанию периода свободных колебаний.

Таким образом, технический принцип, основанный на прямого хода коле6атепьногч7 процесса в любой момент времени, переводе выходного напряжения от любого его значения до своего макс&мальвого значения, позволяет расширить фушзшональные возможности устройства. Транзистор 18 может .быть подключен также эмнттерсы к общей шине устройства, коллекторе - к &кэе второго или

коллектору третьего транзисторов 8 или 9.

Формула изобретения

Формирователь пилообразного напряжения по авт. св. № 919О69, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения управления начальной фазой колебаний и обес11ече1тя синхронизации частоты, в него введен чётве утый транзистор и четвертая входная шина, соединенная с базой четвертого тракзиотора, коллектор которого соединен с шн 16052 2 ной питания, а эмиттер - с базой треть- эго транзистора. Источники информации, принятые во внимание при эксперттае 1. Авторское свидетельство СССР № 919069, кл. Н 03 К 4/5О, 1981.

Авторы

Даты

1983-03-15—Публикация

1981-07-14—Подача