ров памяти и выходом третьего блока памяти, третий выход блока задания адреса соединен с .адресным входом первого блока памяти, четвертый и пятый выходы блока задания адреса соединены с управляющими входа1 1 соответственно; третьего и четвертого регистров памяти, первый и второй входы блока задания адреса соединены соответственно с выходами первого и второго дешифраторов , выход третьего регистра памяти соединен с первым входом второго делителя частоты, второй вход которого подключен к выходу первого генератор.а импульсов, а выход второго делителя частоты подключен к второму входу счетчика импульсов, выход четвертого регистра памяти соединен с первым входом третьего делителя частоты, второй вход которого подключен к выходу второго генератора импульсов, а выход третьего делителя частоты подключен к второму входу первого делителя частоты, информационный вход третьего блока памяти является информационным входом генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного импульсного процесса (его варианты) | 1983 |

|

SU1107121A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Генератор случайного процесса | 1985 |

|

SU1335991A1 |

| Генератор случайного процесса | 1982 |

|

SU1022161A1 |

| Генератор случайных процессов | 1980 |

|

SU957205A1 |

| Устройство для оценки свойств сенсорного внимания и памяти человека | 1986 |

|

SU1387987A1 |

| Генератор нестационарного случайного импульсного процесса | 1987 |

|

SU1587501A1 |

| Генератор случайного процесса | 1982 |

|

SU1087991A1 |

| Генератор случайных процессов | 1984 |

|

SU1309021A1 |

| Генератор случайного процесса | 1986 |

|

SU1432515A1 |

ГЕНЕРАТОР НЕСТАЦИОНАРНОГО СЛУЧАЙНОГО ИМПУЛЬСНОГО ПРОЦЕССА, содержащий первый блок памяти, выход которого соединен с первым входом датчика случайных чисел, первый выход которого соединен с информационным входом счетчика импульсов, блок эталонных напряжений, выход которого соединён с первым входом преобразователя код-напряжение, выход которо.го соединен с первым входом модулятора полярности, выход которого является выходом генератора, второй вход модулятора полярности подключен к первому выходу первого регистра памяти, выход второго регистра памяти подключен к первому входу делителя частоты, выход счетчика импульсов подключен к вхрду первого дешиф,.зтора, а выход первого дешифратора соединен с первым установочным входом триггера, вторым входом датчика случайных чисел и установочным входом счетчика адреса, входы первого и вто-. рого регистров памяти подключены со- . отве1;ственно к второму и третьему выходам датчика случайных чисел, инверсный и прямой выходы триггера под- i ключены соответственно к входам первого и второго генераторов импульсов, прямой выход триггера соединен с управляющим входом второго блока памя-: ти, второй установочный вход три.ггера подключен к выходу второго дешифратора, вход которого соединен с выходом счетчика., адреса, выход второго блока памяти соединен с первым входом блока умножения, второй вход которого подключен к второму входу первого регистра памяти, выход блока умножения соединен со вторым входом I преобразователя код-напряжение, выход первого делителя частоты подклюn чен к счетному входу счетчика адреса, отличающийся тем, что, с целью расширения области применения за счет воспроизведения нестационйр ного случайного импульсного процесса, он содержит блок задания адреса, третий блок памяти, коммутатор, третйй и четвертый регистры памяти, второй и третий делители частоты, причем управляющий вход блока за00 дания адреса является управляющим входом генератора, первый выход бло00 ка задания адреса соединен с адресг ным входом третьего блока памяти, второй выход блока задания адреса соединен с первым входом коммутатора, второй вход коммутатора соединен с выходом счетчика адреса, а выход коммутатора соеЬ нен с адресным входом второго блока памяти, информационный вход второго блока памяти соединен с информационными входами первого блока памяти, третьего и четвертого регист

1

Изобретение относится к вычислительной технике и может быть использовано при моделировании систем с учетом случайных внешних возмущений, при построении стохастических вычислительных и моделирующих устройств, ..а также при построении автоматизированных вычислительных комплексов.

Известен генератор случайных импульсных потоков, содержащий генератор тактовых импульсов, циклический регистр сдвига, дв.а элемента ИЛИ, интегратор, преобразователь код-напряжение и управляемый вероятностный элемент Л .

Однако данное устройство .не позволяет формировать импульсные со а1учайнЫ и параметрами, подчиняющимися заданным законам распределения, и имеющих сложную форму о

Известен генератор случайного импульсного процесса, содержащии блок памяти, датчик случайных чисел блок управления, первый генератор импульсов, счетчик импульсов, источник эталонных напряжений, первый и второй преобразователи код-напряжение и модулятор полярности выходного сигнала, второй регистр, реверси&ный счетчик, делитель частоты, второй генератор импульсов 2

Однако данное устройство не позволяет формировать нестационарный случайный импульсный процесс с произвольной формой сигнала.

Наиболее близким техническим решением к предлагаемому является генератор случайных процессов, содержащий блоки памяти, регистры памяти, триггер, счетчики, модулятор полярности, дешифраторы, датчик случайных чисел, блок эталонных напряжений, преобразователь код-напряжение, делитель частоты, блок умножения з.

Этот имитатор предназначен для формирования потока разнополярных импульсов произвольной программируемой формы. Но он не позволяет организовать перенастройку имитатора на воспроизведение иных законов распределения параметров процесса или изменить форму выходного сигнала без прерывания процесса формирования сигнала, что затрудняет его использование в автоматизированных системах испытаний или в вычислительно-моделирующих системах,

изобретения - расширение области применения генератора за счет организации загрузки, управляющей информации в память генератора без прерывания процесса формирования выходного сигнала, что позволяет фор|мировать нестационарные случайные процессы, представляя их как кусочно-стационарные воздействия.

Для достижения поставленной цели в известный генератор нестационарного случайного импульсного про- . цесса, содержащий первый блок памяти, выход которого соединен с первым входом датчика случайных чисел, первый выход которого соединен с информационным входом счетчика импульсов, блок эталонных напряжений, выход которого соединен с первым входом преобразователя код-на пряжение , выход которого соединен с первым входом модулятора полярности, выход которого является выходом генератора, второй вход модулятора полярности подключен к первому входу первого регистра памяти, выход второго ра памяти, подключен к первому входу делителя частоты, выход счетчика импульсов подключен к входу первого де шифратора, а выход первого дешифрато ра соединен с первым установочным входом триггера, вторым входом датчика случайных чисел и установочным входом счетчика адреса, входы первого и второго регистров памяти подключены соответственно к второму и третьему выходам датчика случайных чисел, инверсный и прямой выходы триггера подключены соответственно к входам первого и второго генераторов импульсов, прямой выход триггера соединен с управляющим уходом блока памяти, второй установочный вход три гера подключен к выходу второго дешифратора, вход -которого соединен с выходом счетчика адреса иадре ным входом второго блока памяти, выход второго блока памяти соединен с первым входом блока умножения второй вход которого подключен к второму вы ходу первого регистра памяти., выход блока умножения соединен с вторым входом преобразователя код-напряжение, выход делителя частоты подключен к счетному входу счетчика адреса, введены блок .задания адреса, тре тий блок памяти, коммутатора, третий и четвертый регистры памяти., второй и третий делители частоты, причем управляющий вход блока задания адреса является управляющим входом генератора, первый выход блока задания адреса соединен.;с адресным входом третьего блока памяти, второй выход блока задания адресов соединен с первым входом коммутатора, второй вход коммутатора соединен с выходом счетчика адреса, а выход коммутатора соединен с адресным входом второго блока памяти, информационный вход второго блока памяти соединен с информационными входами первого блока памяти, третьего и четвертого регистров памяти и с выходом третьего блока памяти. Третий выход бло

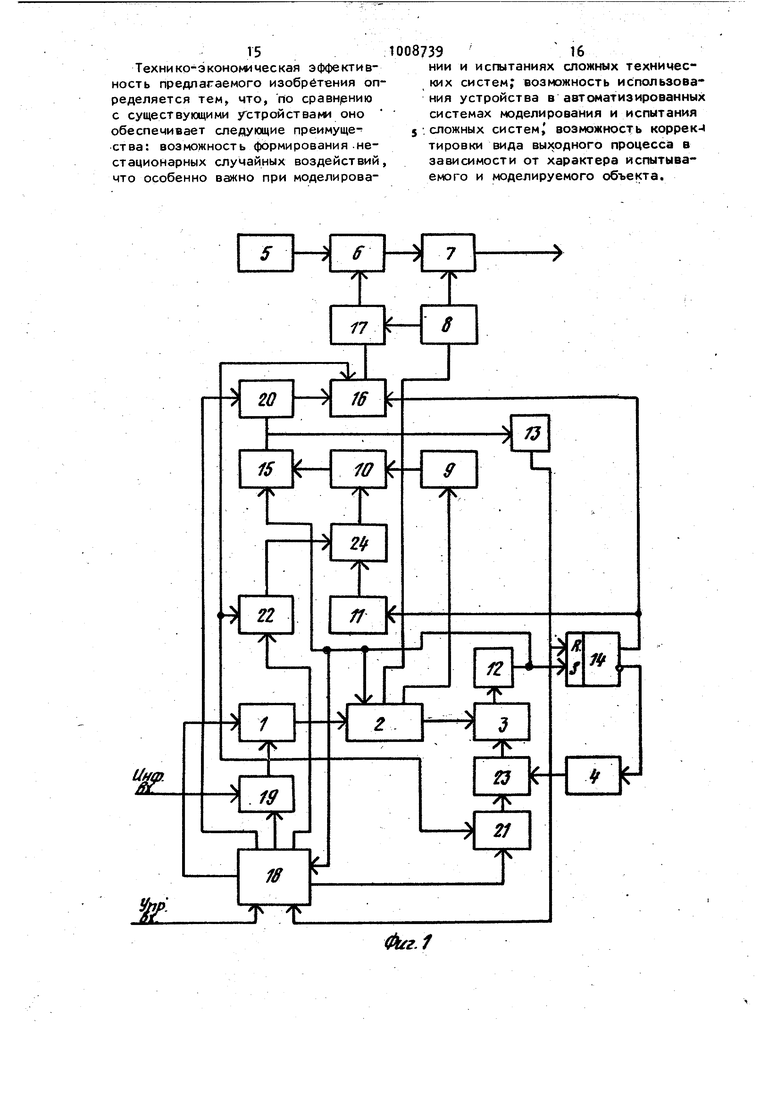

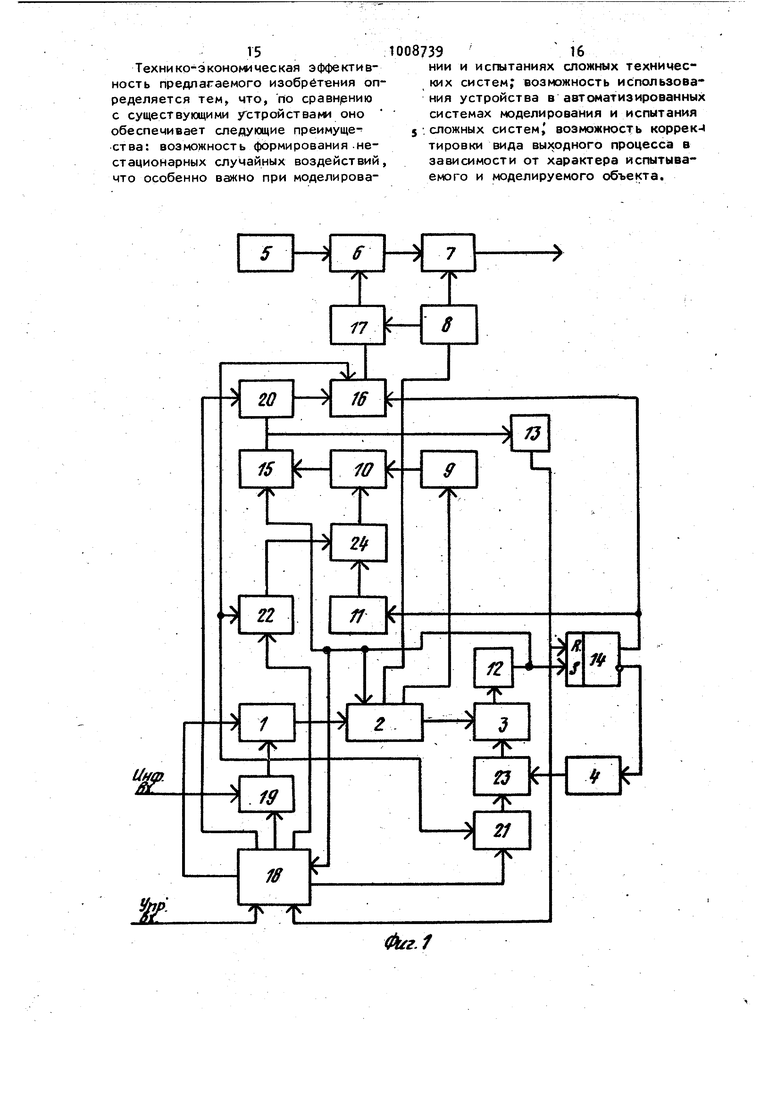

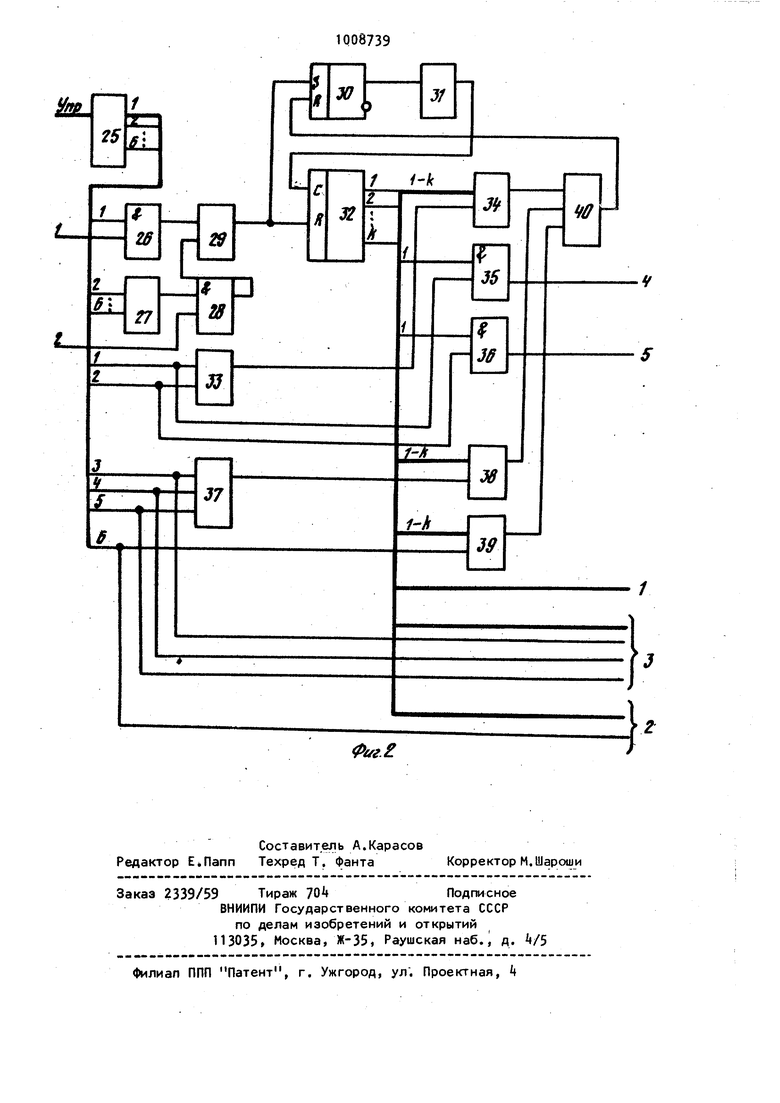

ка задания адреса соединен с адрес;ным входом первого блока памяти, четвертый и пятый выходы блока задания адреса соединены с управляющими входами соответственно третьего и четвертого регистров памяти, первый и второй входы блока задания адреса соединены соответственно с выходами первого и второго дешифраторов, выход регист-Ю; третьего регистра памяти соединен с первым входом второго делителя частоты, второй вход которого подключен к выходу первого генератора импульсов а выход второго делителя частоты подключен к второму входу счетчика импульсов,.выход четвертого регистра памяти соединен с первым входом третьего делителя частоты, второй вход которого подключен к выхоДУ второго генератора импульсов, а выход третьего делителя частоты подключен к второму входу первого делителя частоты, информационный вход третьего блока памяти является информационным входом генератора. Сущность изобретения заключается в том, что для организа1 1и перезаписи информации в тот или иной блок памяти используются те интервалы времени, в течение которых ный блок памяти не участвует в формировании выходного процесса. На фиг. 1 приведена блок-схема генератора; на фиг. 2 - схема блока задания адресов. Генератор содержит первый блок 1 памяти, датчик 2 случайных чисел, счетчик 3 импульсов, первый генератор импульсов, блок 5 эталонных напряжений, преобразователь 6 коднапряжение, модулятор 7 полярности, первый регистр 8 памяти, второй регистр 9 памяти, первый делитель 10 частоты, второй генератор 11 импульсов, первый дешифратор 12, второй дешифратор 13, триггер k, счетчик 15 адреса, второй блок 1б памяти, блок 17 умножения, блок 18 задания адре; са, третий блок 19. памяти, коммутатор 20, третий регистр 1 памяти, четвертый регистр 22 памяти, второй делитель 23 частоты, третий делитель 2А частоты. Блок 18 задания адреса (управления записью) содержит дешифратор 25, элемент И 26, элемент ИЛИ 27, элемент И 28, элеме1нт ИЛИ 29, триггер 30, генератор 31 импульсов, счетчик 32 адреса, элемент ИЛИ 33, дешифра5тор З, элементы И 35 и Зб, элемент ИЛИ 37, дешифраторы 38 и 39, элемент ИЛИ 40. Первый блок 1 памяти предназначе для хранения кодов, определяющих вид и числовые характеристики функций распределения вероятностей пара метров сигналов формируемого импуль ного случайного процесса. Датчик 2 случайных чисел предназ начен для формирования случайных ко дов амплитуды, длительности и инте вала между импульсами, подчиняющихся функциям распределения, коды которых хранятся в первом блоке 1 памяти. Счетчик 3 импульсов служит для запоминания случайного код, опреде ляющего интервал между импульсами формируемого процесса и для преобразования этого кода во временной и тервал. Первый генератор k импульсов пре назначен для формирования тактовых импульсов развертки интервала следо вания импульсов. Блок 5 эталонных напряжений служит для задания граничных значений амплитуд импульсных сигналов, форми pyewsix предлагаемым генератором. Преобразователь 6 код-напряжение предназначен для преобразования в напряжение кодов, последовательност которых определяет форму импульса на выходе генератора. Модулятор 7 полярности обеспечивает получение импульсных сигналов положительной или отрицательной полярностиПервый регистр 8 памяти служит д

запоминания кода, определяющего амплитуду и полярность очередного импульсного сигнала, второй регистр 9 памяти служит для зaпo мнaния кода, определяющего длительность очередного импульса.

Первый делитель 10 частоты предназначен для задания скорости заполнения тактовыми импульсами счетчика 15 адреса, а второй генератор 11 импульсов - для формирования тактовых импульсов развертки длительности случайного процесса.

Первый дешифратор 12 обеспечивает выработку сигнала, указывающего на окончание формирования интервала между импульсами,а второй дешифратор 13 -выработку сигнала,указывающегоHa окончание формирования импульсаимпульсной последовательности в. соответствии с масштабом времени при формировании длительности импульса.

Генератор работает следующим образом.

Каждый цикл работы начинается с формирования набора значений случайных параметров (длительности, амплитуды интервала между импульсами). Значения параметров процесса формируются по заданным законам распределения, коды которых хранятся в первом блоке 1 памяти. С выхода датчика 2 случайных чисел сформированные значения параметров поступают в счетчик 3 импульсов, регистры 8 и 9.

При формировании длительности импульса триггер 1 находится в единичном состоянии, разрешая тем самым ра39Триггер 1 предназначен для выработки сигналов разрешения работы первого генератора и второго генератора. 11:импульсов, счетчик адреса 15 вырабатывает последовательность адресов для считывания кодов из второго блока 1б памяти, а второй блок 1б памяти предназначен для хранения кодов ординат импульсного сигнала, требуемой формы. Блок 17 умножения вырабатывает коды, задающие значения импульсного сигнала в дискретные моменты времени, а блок 18 задания адреса предназначен для выработки управляющих сигналов занесения информации в блоки памяти устройства. Третий блок 19 памяти является буферным запоминающим устройством и предназначен для кратковременного хранения управляющей информации при изменении параметров генерируемого процесса. Коммутатор 20 предназначен для организации подключения к адресному входу второго блока 16 памяти кодов, вырабатываемых счетчиком 15 адреса или блоком 18,. а третий регистр 21 памяти - для хранения кода масштаба времени при формировании интервала между импульсами. Четвертый же регистр 22 памяти предназначен для хранения кода масштаба времени при формировании длительности импульса. Второй делитель 23 частоты обеспечивает формирование опорной импульс- ной последовательности в соответствии с масштабом времени при формировании интерваламежду импульсами , атретий делитель 2 частоты -формирование опорной боту второго генератора 11 импульсо и считывание информации из второго блока 16 памяти, при этом запрещается работа первого генератора k и пульсов. Выход второго генератора 11 импул сов подключен к второму входу треть го делиогеля 2 частоты В четвертом регистре 22 хранится код, определяющий частоту пересчета третьего делителя 2k частоты. Таким образом, код, записанный в четвертый регистр 22,определяет временной диапазон изменения длительности импульса. Значение случайного кода, записанного во второй регистр 3, опреде ляет коэффициент пересчета делителя 10 частоты Этим обеспечивается для каждого значения длительности импульса заполнение счетчика 15- адреса с соответствующей частотой, по лученной в результате деления частоты импульсного потока, поступающего от третьего делителя 2Ц частоты. Коды с выхода счетчика 15 адреса поступают на второй вход коммута тора 20, 1ри этом на управляющем вх де коммутатора 20 присутствует сиг нал, вырабатываемый блоком 18 и раз решающий поступление на выход коммутатора 20 кодов, вырабатываемых счетчиком 15 адреса. Таким образом, обеспечивается последовательное, считывание кодов ординат импульсного сигнала запрограммированной формы с частотой, обратно .пропорционал ной значению кодов длительности импульса и масштаба времени при форми ровании длительности импульсов. меннои диапазон с изменения длитель ностеи импульсов определяется соотношением. f .(l. -период следования импульс второго генератора 1 импульсов, - разрядность четвертого ре гистра 22; . -разрядность формируемых случайных кодов, определяющих длительность импул сов; .- емкость второго блока 16 памяти.. Коды, считанные .из второго блока 16 памяти поступают в качестве первого операнда на первый вход блока 39 17 умножения. На второй вход этого блока поступает код амплитуды формируемого импульса, занесенный в первый регистр 8. На выходе блока 17 умножения формируются значения ординат импульсного сигнала требуемой .формы, прямо пропорциональные значению амплитуды формируемого импульса. На выходе блока 5 эталонных напряжений уctaHавливается уровень напряжения, равный максимальной амплитуде формируемых импульсов. В соответствии с кодами, поступающими с выхода блока 17 умножения, на выходе преобразователя 6 код-напряжение формируется аналоговый сигнал требуемой фор1 с амплитудой, COOTветст.вующей коду амплитуды 0opNMpyeMoro импульса. Модулятор 7 полярности пропускает сигнал с выхода преобразователя 6 код-напряжение на выход устройства, либо сохраняя его поляр-, ность, либо изменяя ее на противоположную в соответствии с кодом амплитуды импульса, записанным в первом регистре 8.. По окончании формирования одного импульса (по достижении счетчиком ад-, реса значения т) на выходе второго дешифратора 13 вырабатывается сигнал окончания формирования импульса Этот сигнал устанавливает триггер 1 в нулевое состояние, при этом запрещается работа второго генератора 11 импульсов и считывание информации из второго блока 16 памяти. На инверсном выходе триггера 1 отрабатывается сигнал, разрешающий работу первого генератора Л импульсов и таким образом, начинается формирование интервала между импульсами. -Выход первого генератора k импульсов подключен к второму входу второго делителя ,23 частоты, В третьем регистре 21 хранится код, определяющий частоту пересчета второго делителя 23 частоты. Таким образа, код записанный в третий регистр 21 определяет временной диапазон длительности интервала между импульсами. Выход второго делителя 23 частоты подключен к первому входу счетчика 3 импульсов, в котором записан случайный код, определяющий значение интервала между импульсаг«1. По окончании формирования интервала при достижении счетчиком 3 импульсов нулевого состояния) на выходе первого дешифратора вырдоатывается сигнал окончания формирования интервала меж ду импульсамич, Диапазон измерения паузы между импульсами определяется соотношением 2 2,0 Т-9 период следования импульсов первого генератора импуль сов; разрядность третьего регист ра 21 J разрядность формируемых слу чайных кодов, определяющих интервал между импульсами. Сигнал окончания формирования интервала между импульсами поступает на второй управляющий вход датчика 2 случайных чисел. После этого происходит формирование и передача в ре гистры 8 и 9 и в счетчик 3 импульсов новых значений параметров процесса. Этот же сигнал устанавливает в нулевое состояние счетчик 15 адреса и в исходное (единичное) состояние триггер 1 - так .начинается следующий цикл формирования выходного случайного процесса. Для формирования нестационарного случайного процесса, представляемого как кусочно-стационарный процесс, достаточно в требуемые моменты времени ti, определяющие окончание i-ro интервала стационарности, записать в запоминающее устройство генератора новую управляющую информацию, при этом характер записываемой информаци может быть различным. Для изменения временного диапазона формируемого сигнала необход мо изменить коды, хр нимые в третьем 21 и четвертом 23 ре гистрах. Для изменения формы выходного сигнала необходимо переписать информацию, хранимую во втором блоке 16 памяти. Для изменения законов рас пределения параметров (или одного параметра) процесса перезаписывается информация, хранимая в первом блоке 1 памяти, причем перезапись информации осуществляется вте моменты времени, когда требуемый для перезаписи блок не участвует в формировании выходного процесса. Перезапись информации осуществляется при помощи блока 18 и третьего блока 19 памяти и происходит следующим образом . Предварительно информация заносится в третий блок 19 памяти. Управляющий сигнал, указывающий на вид изменяемой информации, поступает на управляющий вход устройства, подключенный к управляющему входу блока 18. Возможны четыре способа перезаписи информации, определяемые видом изменяемой информации. В первом случае изменению подвергается код, определяющий масштаб времени при формировании интервала между импульсами и хранимый в третьем регистре 21. При формировании.длительности импульса первый генератор k импульсов не участвует в формировании выходного процесса и изменение информации втретьем регистре 21 не вызовет прерывания в выходном процессе. При наличии соответствующего сигнала на управляющем входе блока 18 и при поступлении сигнала окончания формирования интервала между импульсами, поступающего на первый вход блока 18, на его четвертом выходе вырабатывается сигнал, поступающий на управляющий вход третьего регистра 21 и разрешающий запись информации в третий регистр 21. На информационный вход третьего регистра 21 поступает информация из третьего блока 19 памяти. Во втором случае изменению подвергается код, определяющий масштаб времени при формировании длительности импульса и хранимый в четвертом регистре 22. При формировании интервала между импульсами второй генератор 11 импульсов не участвует в формировании выходного процесса и изменение информации в четвертом регистре не вызывает прерывания в выходном процессе. При наличии соответствующего сигнала на управляющем входе блока 18 и при поступлении сигнала окончания формирования длительности импульса, поступающего на второй .вход блока 18, на пятом выходе этого блока вырабатывается сигнал, поступаю1ДИЙ на управляющий вход четвертого регистра 22 и разрешающий запись информации в четвертый регистр 22„ На информационный вход четвертого регистра 22 поступает информация из третьего блока 19 памяти. В третьем случае изменению подвергается информация, определяющая вид и числовые характеристики законов распределения параметров случайного импульсного процесса и хранимая в первом блоке 1 памяти, В этом случае изменяется одна из зон первого блока 1 памяти, соответствующая одному из законов распределения, параметров. При формировании интервала между .импульсами не происходит формирования случайных кодов, соответствующих значению параметров .процесса и изменение информации в .первом блоке 1 памяти не .вызывает прерывания ввыходном процессе. При наличии соответствующего сигнала на управляющем входе бло.ка 18 и при поступлении сигнала окончания длительности импульса,, поступающего на второй вход блока 18, .на третьем выходе блока 18-вырабатываются управляющие сигналы и адреса для запи си информации в пер.вый блок 1 памяти. На первом выходе блока 18 вырабатываются адреса, по оторым считывается информация, записанная в третьем блоке 19 памяти. Выработка адре сов на третьем и первом выходах блока 18 происходит синхронно, поэтому обеспечивается появление на выходе третьего блока 19 памяти информации, которая записывается в требуемую зону первого блока 1 памяти. Аналогично осуществляется перезапись информации во второй блок 1б па мяти. При наличии соответствующего сигнала на управляющем входе блока 18 и при поступленVW сигнала окончания формирования длительности импуль са на его втором выходе вырабатывают ся адреса, поступающие на второй вход коммутатора 20, и управляющий сигнал, разрешающий их поступление на выход с коммутатора 20 для записи информации во второй блок 16 памяти, тем самым реализуется четвертый случай. На, первом выходе блока 18 синхрон но с адресами на втором выходе этого блока вырабатывается адресная последовательность поступающая на адресный вход третьего блока 19 памяти, Блок 18 работает следующим образом. На управляющий вход блока 18 пост пает код, определяющий тип записыва емой информации. На выходе .третьего дешифратора 25 формируются сигналы, соответствующие каждому типу записываемой информации. Поступление управляющего кода, соответствующего изменению кода масштаба времени при формировании интервалов между импульсами, обуславливает появление сигнала на первом выходе третьего 1 39 дешифратора 25, при этом открывается по первому входу элемент И 2б. При поступлении на первый вход блока 18 управления записью сигнала окончания формирования интервала между импуль- сами на вход второго триггера 30 через элементы И 2б и ИЛИ 29 поступает сигнал, устанавливающий его в единичное состояние. Этот же сигнал устанавливает в исходное состояние второй счетчик 32 адреса. Единичное, состояние второго триггерах 30 разрешает работу третьего генератора 31 импульсов выход которого подключен к счетному входу второго счетчика 32 адреса. Сигнал с первого выхода третьего дешифратора 25 открывает по первому входу элемент И 35 и, пройдя через элемент ИЛИ 33, разрешает работу четвертого дешифратора ЗА. Если счетчик 32 находится в состоянии единицы (00...Q1), тона выходе элемента И 35, являющегося четвертым выходом блока 18 управления записью, появляется сигнал записи информации в третий регистр 21. При достижении вторым счетчиком 32 адреса состояния, соответствующего двум, срабатывает четвертый деши(йэатор 3, сигнал с выхода которого, пройдя через элемент ИЛИ kO, устанавливает в нулевое состояние второй триггер 30. Этим заканчивается цикл перезаписи информации. Поступление управляющего кода, v соответствующего изменению кода масштаба времени, при формировании длительностей импульсов, определяет появление сигнала на втором выходе третьего дешифратора 25. При; этом сигнал с второго выхода третьего дешифратора 25, пройдя через элемент ИЛИ 27, открывает по второму входу элемент И 28. При, поступлении на второй вход блока 18 сигнала окончания формирования длительности импульса на вход второго триггера 30 через элементы И 28 и ИЛИ 29 noQTyпает сигнал, устанавлиеакяций его в единичное состояние. ЭтЬт же а1гнал устанавливает в исходное состояние второй счетчик. 32 адреса. Единичное состояние второго триггера 30 разрешает работу третьего генератора 31 импульсов, выход которого подключен к счетному входу второго счетчика 32 адреса. Сигнал с второго выхода третьего дешифратора 25 откры-. вает по первому входу элемент И 36 и, пройдя через элемент ИЛИ 33 разрешает работу четвертого дешифратора 3. Если счетчик32 находится в состоянии единицы (00.. .Q ij , тона выхо де элемента И 36, являющегося пятым выходом блока 18, появляется сигнал записи информации в четвертый регистр 22. При достижении вторым счет чи.крм 32 адреса состояния, соответствующего двум (со...010), срабатыва . ет четвертый дешифратор 3, сигнал с выхода которого, пройдя через элемент ИЛИ 40, ycтaнaвливaet в нулевое состояние второй триггер 30. Этим заканчивается цикл перезаписи кода масштаба времени при формировании длительности импульсов. Поступление управляющих кодов, соответствующих изменению кодов одно го из законов распределения параметров формируемого импульсного процесса, обуславливает появление сигналов на третьем, четвертом или пятом выходах третьего дешифратора 25 Один из указанных сигналов, пройдя через элемент ИЛИ 27, открывает по второму входу элемент И 2-8. При поступлении на второй вход блока 18 управления записью сигнала .окончания формирования длительности импульса на вход второго триггера 30 через элементы И 28 и ИЛИ 29 поступает сигнал, устанавливающий его в единичное состояние. Этот же сигнал ; устанавливает в исходное состояние второй счетчик 32 адреса. Единичное состояние второго триггера 30 разрешает работу третьего генератора 31импульсов, выход которого подключен к счетному входу второго счетчик 32адреса. Один из сигналов с третье го, четвертого или пятого выходов третьего дешифратора 25, пройдя через элемент ИЛИ 37, разрешает работу пятого дешифратора 38, Выходы второго счетчика 32 адреса и третий, четвертый и пятый выходы третьего дешиф ратора 25 ЯВЛЯЮТ.СЯ третьим выходом блока 18 управления записью. При за полнении второго счетчика 32 адреса .на третьем выходе блока 18 управления записью появляется последовательность адресов и один из выходов третьего дешифратора 25 (третий, чет вертый или пятый) определяют зону первого блока 1 памяти, соответствующую выбранному параметру процесса. При достижении вторым счетчиком 32 адреса состояния, номер которого на единицу превышает объем перезаписываемой информации о законах распределения параметров, срабатывает пятый дешифратор 38 и сигнал с его выхода, пройдя через элемент ИЛИ 40, устанавливает в нулевое состояние второй триггер -.30. Этим заканчивается цикл перезаписи информации об одном из законов распределения параметров фор-мируемого процесса. Поступление управляющего кода, соответствующего изменению информации, определяющей формы выходного сигнала, определяет появление сигнала на шестом аыходе третьего дешифратора 25. Пройдя через элемент ИЛИ 27 он открывает по второму входу элемент И 28. При поступлении на второй вход блока 18 управления записью сигнала окончания, формирования длительности импульса на вход второго, триггера 30 через элементы И 28 и ИЛИ 29 поступает сигнал, устанавливающий его в единичное состояние. Этот же сигнал устанавливает, в исходное состояние второй счетчик 32 адреса. Единичное состояние второго триггера 30 разрешает работу третьего генератора 31 импульсов, выход, которого подключен к счетному входу второго c4eTL iKa 32 адреса. Сигнал с шестого выхода третьего дешифратора -25 разрешает работу шестого дешифратора 39. Выход второго счетчика 32 адреса и шестого выхода третьего дешифратора 25 являются вторым выходом блока 18 управления записью. При заполнении второго счетчика 32 адреса на втором выходе блока 18 появляется последовательность адресов и управляющий сигнал, разрешающий прием информации во второй блок 16 памяти. При достижении вторым счетчиком 32 адреса состояния, номер которого на единицу превышает объем записываемой информации во второй блок 16 памяти, срабатывает шестой дешифратор 39 и сигнал с его выхода , пройдя через элемент ИЛИ АО, устанавливает в нулевое состояние второй триггер 30. Этим заканчивается цикл перезаписи информации, определяющий форму выходного сигнала. При всех значениях кодов на управляющем входе блока 18 на первом его выходе формируется последователь ность адресов, поступающая на вход третьего блока 19 памяти.

15

Технико-экономическая эффективность предлагаемого изобретения определяется тем, что, по сравн/ению с существующими устройствами оно обеспечивает следующие преимущества: возможность формирования .нестационарных случайных воздействий, что особенно важно при моделирова1008739 16

НИИ и исгытаниях сложных технических систем; возможность использования устройства в автоматизированных системах моделирования и испытания 5 сложных систем возможность коррек-( тировки вида выходного процесса в зависимости от характера испытываемого и моделируемого объекта.

e.f

Авторы

Даты

1983-03-30—Публикация

1981-11-17—Подача