1

14325

; Изобретение относится к вычисли- т ельной технике и может быть исполь- 4овано при построении имитационно-мо- Делирующей аппаратуры для решения задач оптимизации сложных технических систем.

Цель изобретения - повышение быстродействия.

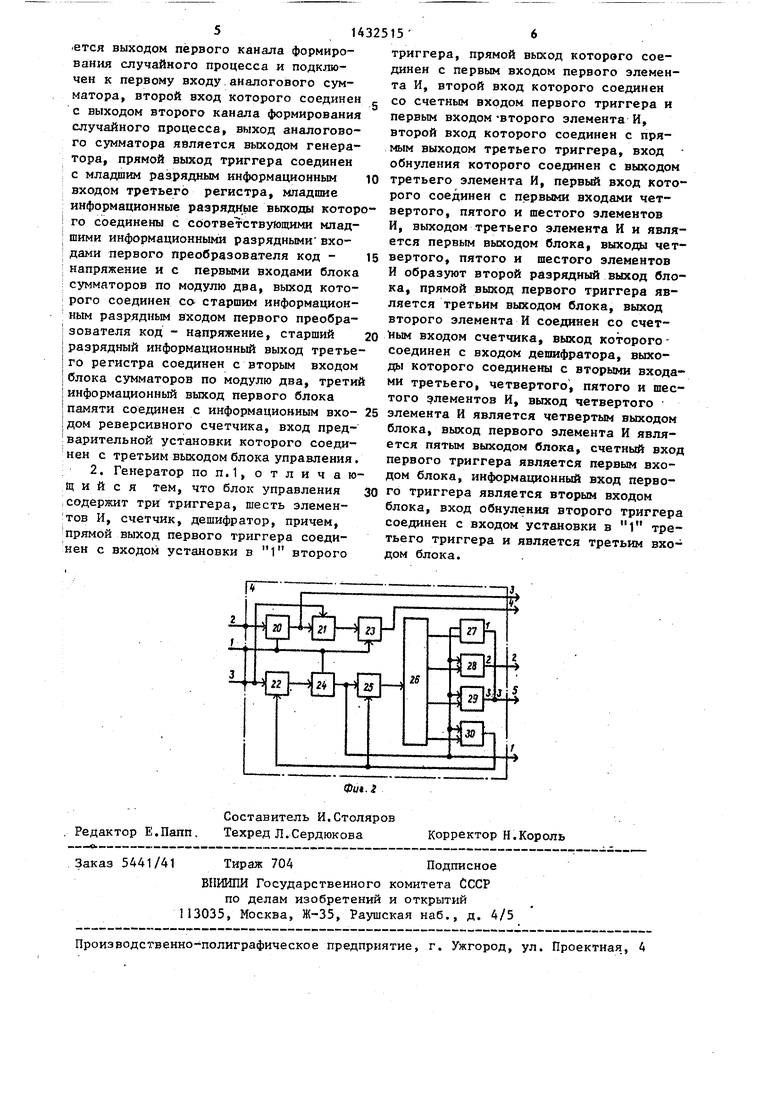

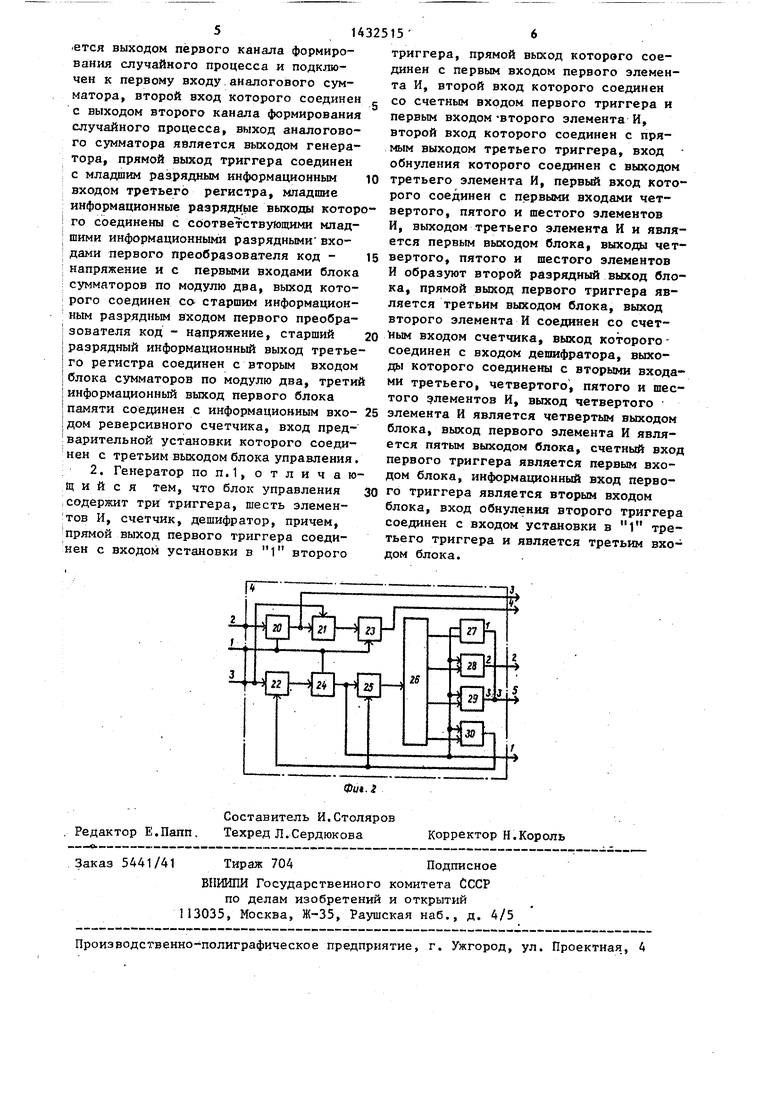

Еа фиг,1 представлена структурная с|;хема генератора случайного процесса; фиг.2 - структурная схема блока

правления.

Генератор содержит генератор 1 так if OBbix импульсов, аналоговьй сумматор

, два одинаковых канала 3 формирова- йия случайного процесса, каждый из которых содержит блок 4 управления, датчик 5 случайных чисел, блок 6 па- iliHTn,регистры 7-8, делитель 9 часто- ы, счетчик 10, реверсивный счетчик

1,, преобразователи 12 и 13 код-нап- )яжение, блок 14 памяти, элемент И 15, регистр 16J делитель 17 частоты, риггер- 18,блок 19 cyNJMaTopoB по мо

;ул10 два.

I Блок 4 управления содержит триггеры 20-22, элементы И 23-24, счетчик 25, дешифратор 26, элементы И 27-30.

Генератор работает следующим обра- ом.

К началу очередного цикла в блоке IP памяти записаны коды, определяющие параметры очередного импульса,а триггер |18 установлен в случайное равновероят- ;|ioe состояние .Предыдущий цикл работы за $санчивается при достижении реверсив- йым счетчиком 11 нулевого состояния. По следующему импульсу с выхода делителя 17 частоты на выходе реверсив- кого счетчика 11 формируется импульс, устанавливающий триггер 20 блока 4 управления в единичное состоя,иие, вследствие чего на третьем выходе блока 4 формируется единичный сигнал, no которому происходит считьшание кодов амплитуды, длительности и периода из блока 6 памяти и запись этих кодов соответственно в регистры 7-8 и реверсивный счетчик 11. Первый после установки в единицу триггера 19 блока 4 импульс, поступающий на первый вход блока 4 с выхода генератора 1 импульсов, устанавливает нулевое состояние триггера 20 блока 4, к этому моменту времени триггер 21 находится в единичном состоянии,в результате чего импульсы с выхода генератора 1, поступая на первый вход блока 4, проходят

152

через элемент И 23 блока 4 на информационный вход делителя 9 частоты. На выходе делителя 9 частоть формируется последовательность импульсов с частотой, определяемой кодом, хранящемся в регистре 7. По каждому из этих импульсов счетчик 10 увеличивает свое состояние на единицу, формируя следуюп ий адрес блока 14 памяти, и происходит считывание кода из блока 14 памяти по адресу, установленному предыдущим импульсом с выхода делителя 9 частоты и занесение этого кода в регистр 16, старший разряд которого устанавливается в соответствии с установленным ранее состоянием триг гера 18.

Преобразователи 12 и 13 код - нап ряжение осуществляют преобразование кодов, поступающих в регистр 16, в напряжение электрического сигнала в масштабе, определяемом кодом, хранящимся -в регистре 8, с полярностью,заданной состоянием триггера 18. Таким образом, в результате последовательного увеличения состояния счетчика 10 и чтения всех ячеек блока 14 памяти на выходе каждого канала 2 формируется импульс исходной формы, заданной последовательностью, записанной g блоке 14 памяти кодов, со спучай- ными длительностью, амплитудой и полярностью, определяемыми состоянием соответственно регистров 7 и 8 и триггера 18. При достил ении счетчиком 10 максимального значения на выходе элемента И 15 формируется импульс, устанавливающий в ноль счетчика 10 и ре- гист 16, в результате на выходе канала 2 устанавливается нулевой уровень. Кроме того, импульс с выхода элемента И 15 поступает на третий вход блока 4, в котором устанавливает единичное состояние триггера 22, в результате чего разрешается прохождение импульсов с первого входа блока 4 через элемент И 24 и устанавливает нулевое состояние триггера 21, в результате чего запрещается прохождение импульсов на пятый выход блока 4,

Импульсы с выхода элемента И 22 проходят на первый выход блока 4, на вход счетчика 25, на первые входы элементов И 27-30, -при этом происходит последовательное увеличение на единицу состояния счетчика 25, состояние которого дешифрируется дешиф3J

ратором 26, в результате чего последовательно разрешается прохождение импульсов через элементы И 27-30. Импульс с выхода элемента И 30 устанавливает нулевое состояние триггера 20 блока4 и счетчика 25, запрещая тем самым выработку управляющих сигналов до конца цикла.

По иьфаботанным на первом, втором и четвертом выходах блока 4 сигналам в генераторе происходит генерация трех случайных чисел, каждое из которых распределено по заданному закону запись этих чисел в соответствующие области блока 6 памяти и установка случайного состояния триггера 18.

Параллельно с описанным формированием импульса на выходе канала 2 и формированием параметров следующего цикла импульсами с выхода делителя 18 частоты происходит последовательное вычитание единиц из реверсивного счетчика 11, начальный код которого задает длительность периода следова- ПИЯ импульсов на выходе каналов 3. Вычитание происходит до тех пор,пока в реверсивном счетчике 11 не достигается нулевое состояние, в результате чего последующий импульс с выхода делителя 17 частоты вызывает появление на выходе реверсивного счетчика 10 импульса, сигнализирующего блоку 4 об окончании формирования очередного периода следования импульсов. После поступления импульса на второй вход блока 4 описанный цикл работы канала 3 повторяется. Случайные импульсные процессы обоих каналов 3 суммируются аналоговым сумматором 2, в результате чего на выходе генератора формируется импульсный процесс со случайными амплитудой, длительностью, периодом следования, полярностью и сложной формой

Формула изобретения

1. Генератор случайного процесса, содержащий генератор тактовых импуль- сов.упервьй канал формирования случай- ного процесса, который содержит первый регистр, блок управления, первый выход которого соединен с входом Он- рос датчика случайных чисел,второй разрядный выход блока управления сое- динен с входом разрешения записи первого блока памяти, третий выход блока управления соединен с входом синхронизации второго регистра,первый делител

15

частоты, счетчик, реверсивный счетчик, первый преобразователь код - напряжение, выход которого соединен с входом задания опорного напряжения второго преобразователя код - напряжение, отличающийся тем, что, с целью повышения быстродействия, в него введены аналоговьй сумматор, второй канал формирования случайного процесса, причем в каждый канал вве- . дены второй блок памяти, элемент И, третий регистр, второй делитель частоты, триггер, блок сумматоров по моулю два, причем, выход генератора тактовых импульсов соединен с первым входом блока управления и входом второго делитела частоты каждого канала формирования случайного процесса, выход вторго делителя частоты соединен с вычитающим входом реверсивного счетчика, выход переполнения которого соеинен с вторым входом блока управления, третий вход которго соединен с входом элемента И, входами обнуления счетчика и третьего регистра, третий выход блока управления соединен с входом синхронизации первого регистра и входом разрешения чтения первого блока памяти, информационный вход кото- рого соединен с выходом датчика случайных чисел, выход первого разряда которого соединен с информационным , входом триггера, вход синхронизации которого соединен с четвертым выходом блока управления, пятый выход которого соединен с входом задания коэффициента деления первого делителя частоты, выход которого соединен со счетным входом счетчика, входом разрешения чтения второго блока памяти и подключен к входу синхронизации третьего регистра, старшие информационные разрядные входы которого соединены с соответствующими разрядными входами торого блока памяти, разрядные адресые входы которого соединены с разрядыми выхода ш счетчика и входами эле- ен та И, первый информационный выход первого блока памяти соединен с инфор- ацтннным входом второго регистра, ыход которого соединен с информационным входом первого делителя частоты, второй информационный выход первого, блока соединен с информа- ционньгм входом первого регистра, выход которого саединен с информационным входом второго преобразователя код - напряжение, выход которогоявля514325

/ется выходом первого канала формирования случайного процесса и подключен к первому входу аналогового сумматора, второй вход которого соединен g с выходом второго канала формирования случайного процесса, выход аналогового сумматора является выходом генератора, прямой выход триггера соединен с младшим разрядным информационным Ю входом третьего регистра, младшие информационные разрядные выходы которого соединены с соответствующими младшими информационными разрядными входами первого преобразователя код - 15 напряжение и с первыми входами блока сумматоров по модулю два, выход которого соединен со- старшим информационным разрядным входом первого преобразователя код - напряжение, старший 20 разрядный информационный выход третье- I го регистра соединен с вторым входом j блока сумматоров по модулю два, третий I информационный выход первого блока I памяти соединен с информационным вхо- 25 I дом реверсивного счетчика, вход пред- :варительной установки которого соединен с третьим выходом блока управления. 2. Генератор поп.1,отличаю- щ и и с я тем, что блок управления 30 содержит три триггера, шесть элемен- тов И, счетчик, дешифратор, причем, прямой выход первого триггера соединен с входом установки в 1 второго

15-6

триггера, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединен со счетным входом первого триггера и первым входом-второго элемента И, второй вход которого соединен с прямым выходом третьего триггера, вход обнуления которого соединен с выходом третьего элемента И, первый вход которого соединен с первыми входами четвертого, пятого и шестого элементов И, выходом третьего элемента И и является первым выходом блока, выходы четвертого, пятого и шестого элементов И образуют второй разрядный выход блока, прямой выход первого триггера является третьим выходом блока, выход второго элемента И соединен со счет- /ным входом счетчика, выход которого- соединен с входом дешифратора, выходы которого соединены с вторыми входами третьего, четвертого, пятого и шестого элементов И, выход четвертого элемента И является четвертым выходом блока, выход первого элемента И является пятым выходом блока, счетный вход первого триггера является первым входом блока, информационный вход первого триггера является вторым входом блока, вход обнуления второго триггера соединен с входом установки в 1 третьего триггера и является третьим входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1986 |

|

SU1436113A1 |

| Генератор случайного процесса | 1986 |

|

SU1427365A1 |

| Устройство для моделирования систем человек-машина | 1986 |

|

SU1348848A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Генератор случайных процессов | 1981 |

|

SU955048A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Генератор случайного процесса | 1983 |

|

SU1100622A1 |

| Генератор случайного процесса | 1986 |

|

SU1429113A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении имитаци- онно-моделирующей аппаратуры для решения задач оптимизации сложных систем. Цель изобретения - повышение быстродействия генератора. Генератор содержит генератор 1 тактовых импульсов, аналоговый сумматор 2, два идентичных канала 3 формирования случайного процесса, каждый из которьк содержит блок 4 управления датчик 5 случайных чисел, блок 6 памяти, регистры 7,8, делитель 9 частоты, счетчик 10, реверсивный счетчик 11, преобразователи 12,13 код-напряжение, блок 14 памяти, элемент И 15, регистр 16, делитель 17 частоты, триггер 18, блок 19 сумматоров по модулю два. Поставленная цель достигается за счет введения новых блоков с соответствую-§ щими связями. 1 з.п. ф-лы, 2 ил. СЛ

J

г

8

| СПОСОБ ФОРМИРОВАНИЯ СЛУЧАЙНОГО ПРОЦЕССА С | 0 |

|

SU391577A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор случайного импульсного процесса | 1974 |

|

SU517018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1986-08-18—Подача